#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | 80C51                                                                        |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 40MHz                                                                        |

| Connectivity               | CANbus, SPI, UART/USART                                                      |

| Peripherals                | POR, PWM, WDT                                                                |

| Number of I/O              | 36                                                                           |

| Program Memory Size        | 64KB (64K x 8)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 2K x 8                                                                       |

| RAM Size                   | 2.25K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                    |

| Data Converters            | A/D 8x10b                                                                    |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 44-LQFP                                                                      |

| Supplier Device Package    | 44-VQFP (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at89c51cc03u-rdtim |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

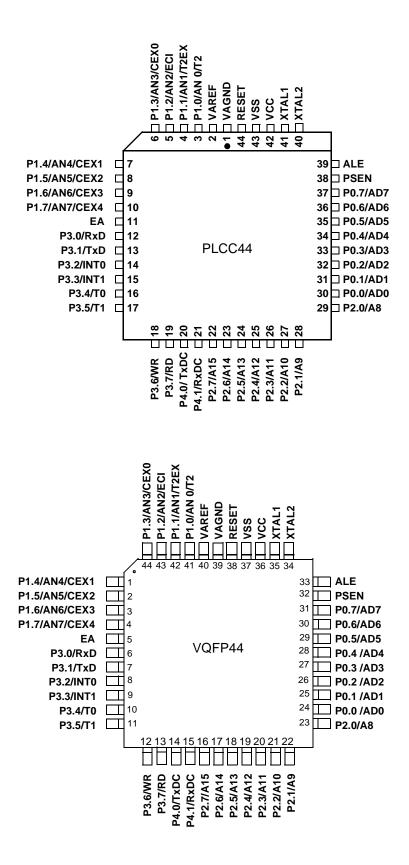

## **Pin Configuration**

### Table 1. SFR Mapping

|     | 0/8 <sup>(2)</sup> | 1/9                  | 2/A                  | 3/B                   | 4/C                  | 5/D                  | 6/E                   | 7/F                   |     |

|-----|--------------------|----------------------|----------------------|-----------------------|----------------------|----------------------|-----------------------|-----------------------|-----|

| F8h | IPL1<br>xxxx x000  | CH<br>0000 0000      | CCAP0H<br>0000 0000  | CCAP1H<br>0000 0000   | CCAP2H<br>0000 0000  | CCAP3H<br>0000 0000  | CCAP4H<br>0000 0000   |                       | FFh |

| F0h | B<br>0000 0000     |                      | ADCLK<br>xxx0 0000   | ADCON<br>x000 0000    | ADDL<br>0000 0000    | ADDH<br>0000 0000    | ADCF<br>0000 0000     | IPH1<br>xxxx x000     | F7h |

| E8h | IEN1<br>xxxx x000  | CL<br>0000 0000      | CCAP0L<br>0000 0000  | CCAP1L<br>0000 0000   | CCAP2L<br>0000 0000  | CCAP3L<br>0000 0000  | CCAP4L<br>0000 0000   |                       | EFh |

| E0h | ACC<br>0000 0000   |                      |                      |                       |                      |                      |                       |                       | E7h |

| D8h | CCON<br>0000 0000  | CMOD<br>00xx x000    | CCAPM0<br>x000 0000  | CCAPM1<br>x000 0000   | CCAPM2<br>x000 0000  | CCAPM3<br>x000 0000  | CCAPM4<br>x000 0000   |                       | DFh |

| D0h | PSW<br>0000 0000   | FCON<br>0000 0000    | EECON<br>xxxx xx00   | FSTA<br>xxxx xx00     | SPCON<br>0001 0100   | SPSCR<br>0000 0000   | SPDAT<br>xxxx xxxx    |                       | D7h |

| C8h | T2CON<br>0000 0000 | T2MOD<br>xxxx xx00   | RCAP2L<br>0000 0000  | RCAP2H<br>0000 0000   | TL2<br>0000 0000     | TH2<br>0000 0000     | CANEN1<br>x000 0000   | CANEN2<br>0000 0000   | CFh |

| C0h | P4<br>xxx1 1111    | CANGIE<br>xx00 000x  | CANIE1<br>x000 0000  | CANIE2<br>0000 0000   | CANIDM1<br>xxxx xxxx | CANIDM2<br>xxxx xxxx | CANIDM3<br>xxxx xxxx  | CANIDM4<br>xxxx xxxx  | C7h |

| B8h | IPL0<br>x000 0000  | SADEN<br>0000 0000   | CANSIT1<br>0000 0000 | CANSIT2<br>0000 0000  | CANIDT1<br>xxxx xxxx | CANIDT2<br>xxxx xxxx | CANIDT3<br>xxxx xxxx  | CANIDT4<br>xxxx xxxx  | BFh |

| B0h | P3<br>1111 1111    | CANPAGE<br>0000 0000 | CANSTCH<br>xxxx xxxx | CANCONCH<br>xxxx xxxx | CANBT1<br>xxxx xxxx  | CANBT2<br>xxxx xxxx  | CANBT3<br>xxxx xxxx   | IPH0<br>x000 0000     | B7h |

| A8h | IEN0<br>0000 0000  | SADDR<br>0000 0000   | CANGSTA<br>x0x0 0000 | CANGCON<br>0000 0x00  | CANTIML<br>0000 0000 | CANTIMH<br>0000 0000 | CANSTMPL<br>0000 0000 | CANSTMPH<br>0000 0000 | AFh |

| A0h | P2<br>1111 1111    | CANTCON<br>0000 0000 | AUXR1<br>xxxx 00x0   | CANMSG<br>xxxx xxxx   | CANTTCL<br>0000 0000 | CANTTCH<br>0000 0000 | WDTRST<br>1111 1111   | WDTPRG<br>xxxx x000   | A7h |

| 98h | SCON<br>0000 0000  | SBUF<br>0000 0000    |                      | CANGIT<br>0x00 0000   | CANTEC<br>0000 0000  | CANREC<br>0000 0000  |                       | CKCON1<br>xxxx xxx0   | 9Fh |

| 90h | P1<br>1111 1111    |                      |                      |                       |                      |                      |                       |                       | 97h |

| 88h | TCON<br>0000 0000  | TMOD<br>0000 0000    | TL0<br>0000 0000     | TL1<br>0000 0000      | TH0<br>0000 0000     | TH1<br>0000 0000     | AUXR<br>x001 0100     | CKCON0<br>0000 0000   | 8Fh |

| 80h | P0<br>1111 1111    | SP<br>0000 0111      | DPL<br>0000 0000     | DPH<br>0000 0000      |                      |                      |                       | PCON<br>00x1 0000     | 87h |

| L   | 0/8 <sup>(2)</sup> | 1/9                  | 2/A                  | 3/B                   | 4/C                  | 5/D                  | 6/E                   | 7/F                   | -   |

Reserved

Note: 1. Do not read or write Reserved Registers

These registers are bit-addressable. Sixteen addresses in the SFR space are both byte-addressable and bit-addressable. The bit-addressable SFR's are those whose address ends in 0 and 8. The bit addresses, in this area, are 0x80 through to 0xFF.

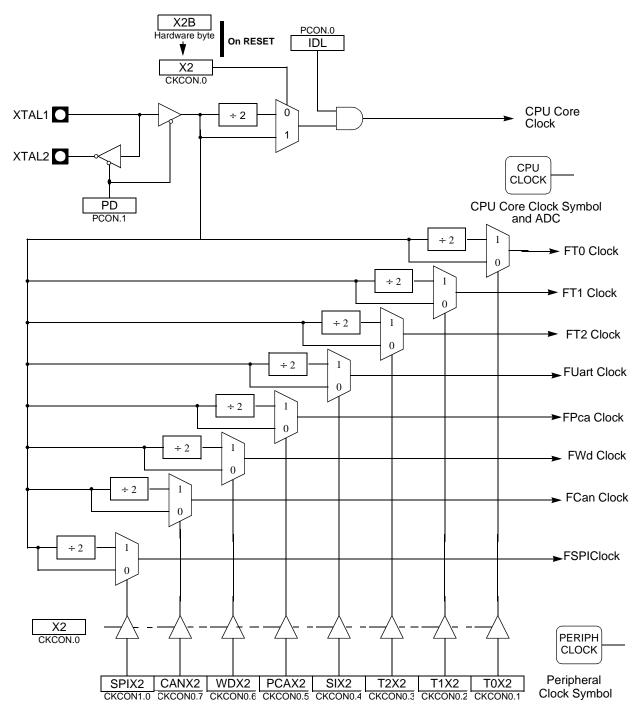

Figure 5. Clock CPU Generation Diagram

## **External Space**

#### **Memory Interface**

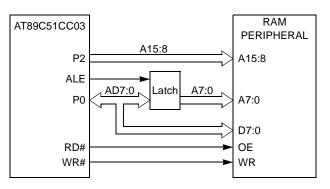

The external memory interface comprises the external bus (port 0 and port 2) as well as the bus control signals (RD#, WR#, and ALE).

Figure 10 shows the structure of the external address bus. P0 carries address A7:0 while P2 carries address A15:8. Data D7:0 is multiplexed with A7:0 on P0. Table 5 describes the external memory interface signals.

Figure 10. External Data Memory Interface Structure

| Table 5. | External Data | Memory | Interface | Signals |

|----------|---------------|--------|-----------|---------|

|----------|---------------|--------|-----------|---------|

| Signal<br>Name | Туре | Description                                                                                                   | Alternative<br>Function |

|----------------|------|---------------------------------------------------------------------------------------------------------------|-------------------------|

| A15:8          | 0    | Address Lines<br>Upper address lines for the external bus.                                                    | P2.7:0                  |

| AD7:0          | I/O  | Address/Data Lines<br>Multiplexed lower address lines and data for the external<br>memory.                    | P0.7:0                  |

| ALE            | 0    | Address Latch Enable<br>ALE signals indicates that valid address information are available<br>on lines AD7:0. | -                       |

| RD#            | 0    | <b>Read</b><br>Read signal output to external data memory.                                                    | P3.7                    |

| WR#            | 0    | Write<br>Write signal output to external memory.                                                              | P3.6                    |

#### **External Bus Cycles**

This section describes the bus cycles the AT89C51CC03 executes to read (see Figure 11), and write data (see Figure 12) in the external data memory.

External memory cycle takes 6 CPU clock periods. This is equivalent to 12 oscillator clock period in standard mode or 6 oscillator clock periods in X2 mode. For further information on X2 mode.

Slow peripherals can be accessed by stretching the read and write cycles. This is done using the M0 bit in AUXR register. Setting this bit changes the width of the RD# and WR# signals from 3 to 15 CPU clock periods.

For simplicity, the accompanying figures depict the bus cycle waveforms in idealized form and do not provide precise timing information. For bus cycle timing parameters refer to the Section "AC Characteristics" of the AT89C51CC03 datasheet.

| Power Down Request       | Before entering in Power Down (Set bit PD in PCON register) the user should check that<br>no write sequence is in progress (check BUSY=0), then check that the column latches<br>are reset (FLOAD=0 in FSTA register. Launch a reset column latches to clear FLOAD if<br>necessary. |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reading the Flash Spaces |                                                                                                                                                                                                                                                                                     |

| User                     | The following procedure is used to read the User space:                                                                                                                                                                                                                             |

|                          | <ul> <li>Read one byte in Accumulator by executing MOVC A,@A+DPTR with<br/>A+DPTR=read@.</li> </ul>                                                                                                                                                                                 |

|                          | Note: FCON is supposed to be reset when not needed.                                                                                                                                                                                                                                 |

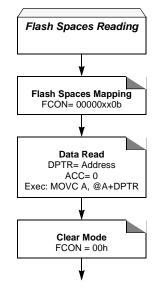

| Extra Row                | The following procedure is used to read the Extra Row space and is summarized in Figure 28:                                                                                                                                                                                         |

|                          | <ul> <li>Map the Extra Row space by writing 02h in FCON register.</li> </ul>                                                                                                                                                                                                        |

|                          | <ul> <li>Read one byte in Accumulator by executing MOVC A,@A+DPTR with A = 0 and<br/>DPTR = FF80h to FFFFh.</li> </ul>                                                                                                                                                              |

|                          | Clear FCON to unmap the Extra Row.                                                                                                                                                                                                                                                  |

| Hardware Security Byte   | The following procedure is used to read the Hardware Security space and is summarized in Figure 28:                                                                                                                                                                                 |

|                          | <ul> <li>Map the Hardware Security space by writing 04h in FCON register.</li> </ul>                                                                                                                                                                                                |

|                          | • Read the byte in Accumulator by executing MOVC A @A+DPTR with A = 0 and                                                                                                                                                                                                           |

Read the byte in Accumulator by executing MOVC A,@A+DPTR with A = 0 and DPTR = 0000h.

Figure 28. Clear FCON to unmap the Hardware Security Byte.Reading Procedure

### Flash Protection from Parallel Programming

The three lock bits in Hardware Security Byte (see "In-System Programming" section) are programmed according to Table 17 provide different level of protection for the onchip code and data located in FM0 and FM1.

The only way to write this bits are the parallel mode. They are set by default to level 4

## Table 31. TMOD Register

TMOD (S:89h) Timer/Counter Mode Control Register

| 7             | 6               | 5                                          | 4                                                                                                                                                                                  | 3                                                     | 2             | 1             | 0             |  |

|---------------|-----------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|---------------|---------------|---------------|--|

| GATE1         | C/T1#           | M11                                        | M01                                                                                                                                                                                | GATE0                                                 | C/T0#         | M10           | M00           |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                |                                                                                                                                                                                    |                                                       |               |               |               |  |

| 7             | GATE1           | Clear to enal                              | Timer 1 Gating Control Bit<br>Clear to enable Timer 1 whenever TR1 bit is set.<br>Set to enable Timer 1 only while INT1# pin is high and TR1 bit is set.                           |                                                       |               |               |               |  |

| 6             | C/T1#           | Clear for Tim                              | •                                                                                                                                                                                  | <b>elect Bit</b><br>Timer 1 count<br>Timer 1 count    |               |               |               |  |

| 5             | M11             |                                            | le Select Bit                                                                                                                                                                      |                                                       |               |               |               |  |

| 4             | M01             | <u>M11 M01</u><br>0 0<br>0 1<br>1 0<br>1 1 | M11<br>0M01<br>Operating mode000Mode 0: 8-bit Timer/Counter (TH1) with 5-bit prescaler (TL1).01010Mode 1: 16-bit Timer/Counter.10Mode 2: 8-bit auto-reload Timer/Counter (TL1) (1) |                                                       |               |               |               |  |

| 3             | GATE0           | Clear to enal                              |                                                                                                                                                                                    | <b>Bit</b><br>henever TR0 b<br>ter 0 only while       |               | high and TRC  | ) bit is set. |  |

| 2             | C/T0#           | Clear for Tim                              | •                                                                                                                                                                                  | <b>elect Bit</b><br>Timer 0 count<br>Timer 0 count    |               |               |               |  |

| 1             | M10             | <b>Timer 0 Mod</b><br>M10 M00<br>0 0       |                                                                                                                                                                                    | <u>mode</u><br>bit Timer/Cour<br>5-bit Timer/Cou      |               | 5-bit prescal | er (TL0).     |  |

| 0             | M00             | 1 0<br>1 1                                 | Mode 2: 8-<br>Mode 3: Tl                                                                                                                                                           | bit auto-reload<br>L0 is an 8-bit T<br>g Timer 1's TR | Timer/Counter |               |               |  |

1. Reloaded from TH1 at overflow.

2. Reloaded from TH0 at overflow.

Reset Value = 0000 0000b

## Registers

## Table 36. T2CON Register

T2CON (S:C8h) Timer 2 Control Register

| 7             | 6               | 5                                                          | 4                                                               | 3                                                                  | 2             | 1                        | 0        |

|---------------|-----------------|------------------------------------------------------------|-----------------------------------------------------------------|--------------------------------------------------------------------|---------------|--------------------------|----------|

| TF2           | EXF2            | RCLK                                                       | TCLK                                                            | EXEN2                                                              | TR2           | C/T2#                    | CP/RL2#  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                |                                                                 |                                                                    |               |                          |          |

| 7             | TF2             | Must be clea                                               | rflow Flag<br>et if RCLK=1 of<br>red by softwa<br>vare on timer | re.                                                                |               |                          |          |

| 6             | EXF2            | EXEN2=1.<br>Set to cause<br>is enabled.                    | apture or a re                                                  | eload is cause<br>ector to timer<br>re.                            | , ,           |                          |          |

| 5             | RCLK            |                                                            | timer 1 overfl                                                  | ow as receive<br>v as receive cl                                   |               | •                        |          |

| 4             | TCLK            |                                                            | timer 1 overfl                                                  | ow as transmi<br>v as transmit c                                   |               |                          |          |

| 3             | EXEN2           | Clear to igno<br>Set to cause                              | a capture or                                                    | <b>bit</b><br>T2EX pin for t<br>reload when a<br>used to clock t   | negative tran |                          | X pin is |

| 2             | TR2             | Timer 2 Run<br>Clear to turn<br>Set to turn of             |                                                                 |                                                                    |               |                          |          |

| 1             | C/T2#           | Clear for time                                             |                                                                 | <b>bit</b><br>input from inte<br>(input from T2                    |               | tem: F <sub>OSC</sub> ). |          |

| 0             | CP/RL2#         | If RCLK=1 of<br>timer 2 overf<br>Clear to auto<br>EXEN2=1. | low.<br>p-reload on tin                                         | <b>bit</b><br>P/RL2# is igno<br>ner 2 overflow<br>e transitions or | s or negative | transitions on           |          |

Reset Value = 0000 0000b Bit addressable

#### Table 39. TL2 Register

#### TL2 (S:CCh) Timer 2 Low Byte Register

| 7             | 6               | 5           | 4        | 3 | 2 | 1 | 0 |

|---------------|-----------------|-------------|----------|---|---|---|---|

| -             | -               | -           | -        | - | - | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description |          |   |   |   |   |

| 7-0           |                 | Low Byte of | Timer 2. |   |   |   |   |

Reset Value = 0000 0000b Not bit addressable

Table 40. RCAP2H Register

RCAP2H (S:CBh) Timer 2 Reload/Capture High Byte Register

| 7             | 6               | 5            | 4             | 3           | 2 | 1 | 0 |

|---------------|-----------------|--------------|---------------|-------------|---|---|---|

| -             | -               | -            | -             | -           | - | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description  |               |             |   |   |   |

| 7-0           |                 | High Byte of | Timer 2 Reloa | ad/Capture. |   |   |   |

Reset Value = 0000 0000b Not bit addressable

#### Table 41. RCAP2L Register

RCAP2L (S:CAн) TIMER 2 Reload/Capture Low Byte Register

| 7             | 6               | 5           | 4             | 3          | 2 | 1 | 0 |

|---------------|-----------------|-------------|---------------|------------|---|---|---|

| -             | -               | -           | -             | -          | - | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description |               |            |   |   |   |

| 7-0           |                 | Low Byte of | Timer 2 Reloa | d/Capture. |   |   |   |

Reset Value = 0000 0000b Not bit addressable

## Watchdog Timer During Power-down Mode and Idle

In Power-down mode the oscillator stops, which means the WDT also stops. While in Power-down mode, the user does not need to service the WDT. There are 2 methods of exiting Power-down mode: by a hardware reset or via a level activated external interrupt which is enabled prior to entering Power-down mode. When Power-down is exited with hardware reset, the Watchdog is disabled. Exiting Power-down with an interrupt is significantly different. The interrupt shall be held low long enough for the oscillator to stabilize. When the interrupt is brought high, the interrupt is serviced. To prevent the WDT from resetting the device while the interrupt pin is held low, the WDT is not started until the interrupt is pulled high. It is suggested that the WDT be reset during the interrupt service for the interrupt used to exit Power-down.

To ensure that the WDT does not overflow within a few states of exiting powerdown, it is best to reset the WDT just before entering powerdown.

In the Idle mode, the oscillator continues to run. To prevent the WDT from resetting AT89C51CC03 while in Idle mode, the user should always set up a timer that will periodically exit Idle, service the WDT, and re-enter Idle mode.

Register

Table 44. WDTPRG Register

#### WDTPRG (S:A7h)

Watchdog Timer Duration Programming Register

| 7             | 6               | 5                                | 4                                                                                    | 3                                | 2              | 1            | 0  |  |

|---------------|-----------------|----------------------------------|--------------------------------------------------------------------------------------|----------------------------------|----------------|--------------|----|--|

| -             | -               | -                                | -                                                                                    | -                                | S2             | S1           | S0 |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                      |                                                                                      |                                  |                |              |    |  |

| 7             | -               | Reserved<br>The value rea        | ad from this b                                                                       | it is indetermi                  | nate. Do not s | et this bit. |    |  |

| 6             | -               | <b>Reserved</b><br>The value rea | ad from this b                                                                       | it is indetermi                  | nate. Do not s | et this bit. |    |  |

| 5             | -               | <b>Reserved</b><br>The value rea | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.      |                                  |                |              |    |  |

| 4             | -               | Reserved<br>The value rea        | ad from this b                                                                       | it is indetermi                  | nate. Do not s | et this bit. |    |  |

| 3             | -               | Reserved<br>The value rea        | ad from this b                                                                       | it is indetermi                  | nate. Do not s | et this bit. |    |  |

| 2             | S2              | -                                | Watchdog Timer Duration selection bit 2<br>Work in conjunction with bit 1 and bit 0. |                                  |                |              |    |  |

| 1             | S1              | -                                | Watchdog Timer Duration selection bit 1<br>Work in conjunction with bit 2 and bit 0. |                                  |                |              |    |  |

| 0             | SO              |                                  | imer Duratio<br>unction with b                                                       | n selection b<br>it 1 and bit 2. | it O           |              |    |  |

Reset Value = XXXX X000b

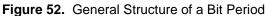

PHS2 = 3 and PHS1 = 3 so CANBT3 = 36h

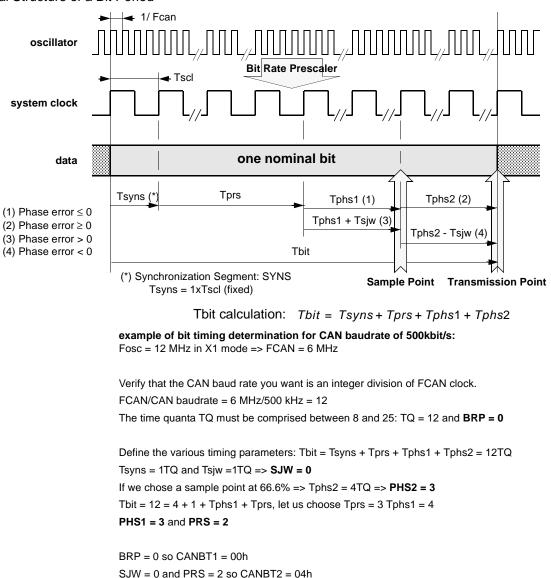

### Figure 66. SPI Interrupt Requests Generation

#### Registers

Serial Peripheral Control Register (SPCON)

- Three registers in the SPI module provide control, status and data storage functions. These registers are describe in the following paragraphs.

- The Serial Peripheral Control Register does the following:

- Selects one of the Master clock rates

- Configure the SPI Module as Master or Slave

- Selects serial clock polarity and phase

- Enables the SPI Module

- Frees the SS pin for a general-purpose

Table 92 describes this register and explains the use of each bit

#### Table 92. SPCON Register

SPCON - Serial Peripheral Control Register (0D4H)

| 7          | 6      | 5      | 4                                                                                                                                                                                                                                                                                        | 3    | 2    | 1    | 0    |  |

|------------|--------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|--|

| SPR2       | SPEN   | SSDIS  | MSTR                                                                                                                                                                                                                                                                                     | CPOL | СРНА | SPR1 | SPR0 |  |

| Bit Number | Bit Mn | emonic | Description                                                                                                                                                                                                                                                                              |      |      |      |      |  |

| 7          | SF     | PR2    | Serial Peripheral Rate 2<br>Bit with SPR1 and SPR0 define the clock rate (See bits SPR1 and<br>SPR0 for detail).                                                                                                                                                                         |      |      |      |      |  |

| 6          | SF     | PEN    | Serial Peripheral Enable<br>Cleared to disable the SPI interface (internal reset of the SPI).<br>Set to enable the SPI interface.                                                                                                                                                        |      |      |      |      |  |

| 5          | SS     | DIS    | $\overline{SS} \text{ Disable}$ Cleared to enable $\overline{SS}$ in both Master and Slave modes.<br>Set to disable $\overline{SS}$ in both Master and Slave modes. In Slave mode,<br>this bit has no effect if CPHA ='0'. When SSDIS is set, no MODF<br>interrupt request is generated. |      |      |      |      |  |

| 4          | MS     | STR    | Serial Peripheral Master<br>Cleared to configure the SPI as a Slave.<br>Set to configure the SPI as a Master.                                                                                                                                                                            |      |      |      |      |  |

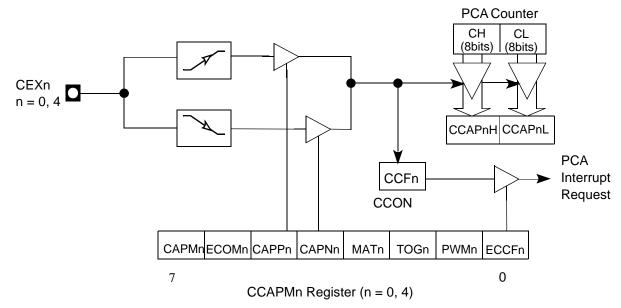

### Figure 69. PCA Capture Mode

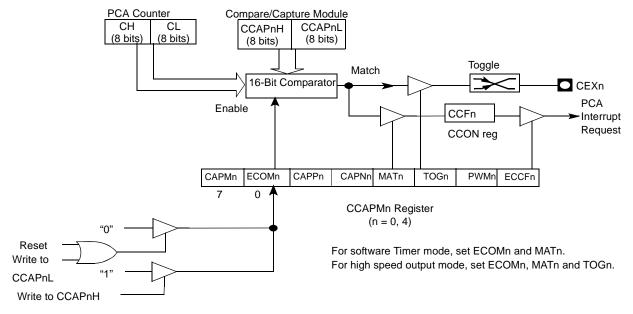

## 16-bit Software Timer Mode

The PCA modules can be used as software timers by setting both the ECOM and MAT bits in the modules CCAPMn register. The PCA timer will be compared to the module's capture registers and when a match occurs an interrupt will occur if the CCFn (CCON SFR) and the ECCFn (CCAPMn SFR) bits for the module are both set.

Figure 70. PCA 16-bit Software Timer and High Speed Output Mode

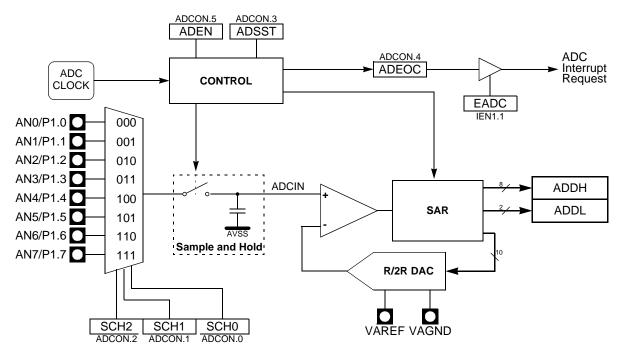

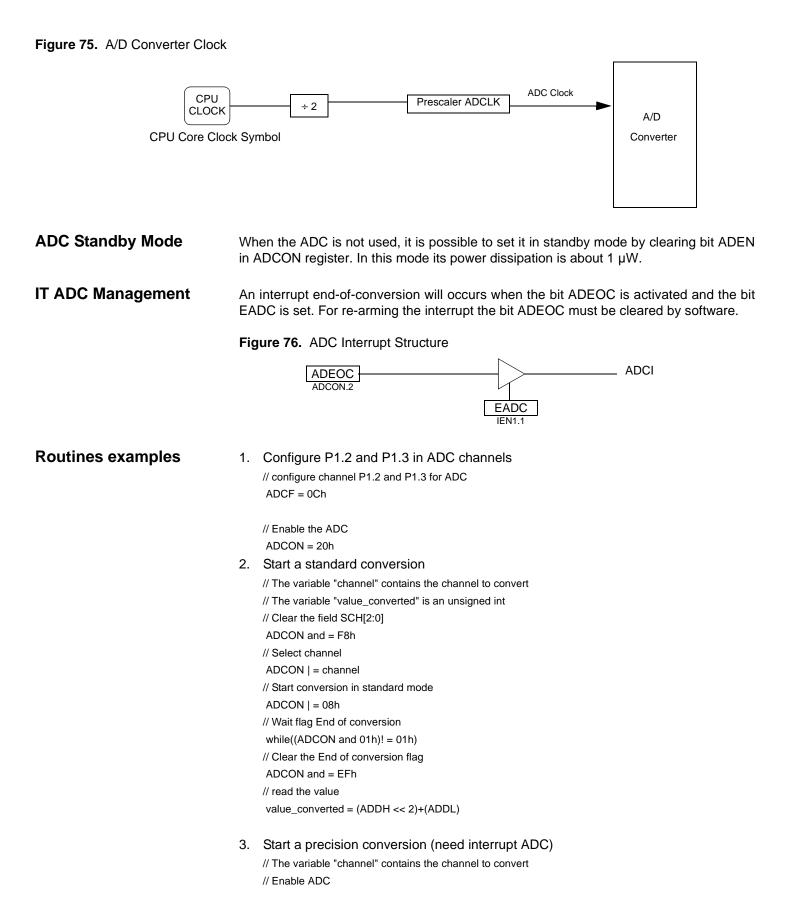

#### Figure 73. ADC Description

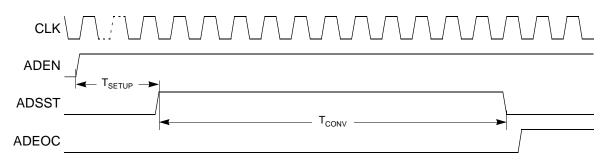

Figure 74 shows the timing diagram of a complete conversion. For simplicity, the figure depicts the waveforms in idealized form and do not provide precise timing information. For ADC characteristics and timing parameters refer to the Section "AC Characteristics" of the AT89C51CC03 datasheet.

#### Figure 74. Timing Diagram

Note: Tsetup min = 4 us

Tconv=11 clock ADC = 1sample and hold + 10 bit conversion The user must ensure that 4 us minimum time between setting ADEN and the start of the first conversion.

Each of the interrupt sources can be individually enabled or disabled by setting or clearing a bit in the Interrupt Enable register. This register also contains a global disable bit which must be cleared to disable all the interrupts at the same time.

Each interrupt source can also be individually programmed to one of four priority levels by setting or clearing a bit in the Interrupt Priority registers. The Table below shows the bit values and priority levels associated with each combination.

| IPH.x | IPL.x | Interrupt Level Priority |  |

|-------|-------|--------------------------|--|

| 0     | 0     | 0 (Lowest)               |  |

| 0     | 1     | 1                        |  |

| 1     | 0     | 2                        |  |

| 1     | 1     | 3 (Highest)              |  |

Table 108. Priority Level Bit Values

A low-priority interrupt can be interrupted by a high priority interrupt but not by another low-priority interrupt. A high-priority interrupt cannot be interrupted by any other interrupt source.

If two interrupt requests of different priority levels are received simultaneously, the request of the higher priority level is serviced. If interrupt requests of the same priority level are received simultaneously, an internal polling sequence determines which request is serviced. Thus within each priority level there is a second priority structure determined by the polling sequence, see Table 109.

| Interrupt Name                  | Interrupt Address Vector | Priority Number |

|---------------------------------|--------------------------|-----------------|

| external interrupt (INT0)       | 0003h                    | 1               |

| Timer0 (TF0)                    | 000Bh                    | 2               |

| external interrupt (INT1)       | 0013h                    | 3               |

| Timer1 (TF1)                    | 001Bh                    | 4               |

| PCA (CF or CCFn)                | 0033h                    | 5               |

| UART (RI or TI)                 | 0023h                    | 6               |

| Timer2 (TF2)                    | 002Bh                    | 7               |

| CAN (Txok, Rxok, Err or OvrBuf) | 003Bh                    | 8               |

| ADC (ADCI)                      | 0043h                    | 9               |

| CAN Timer Overflow (OVRTIM)     | 004Bh                    | 10              |

| SPI interrupt                   | 0053h                    | 11              |

Table 109.

Interrupt priority Within level

## External Program Memory Characteristics

## Table 118. Symbol Description

| Symbol            | Parameter                          |

|-------------------|------------------------------------|

| Т                 | Oscillator clock period            |

| T <sub>LHLL</sub> | ALE pulse width                    |

| T <sub>AVLL</sub> | Address Valid to ALE               |

| T <sub>LLAX</sub> | Address Hold After ALE             |

| T <sub>LLIV</sub> | ALE to Valid Instruction In        |

| T <sub>LLPL</sub> | ALE to PSEN                        |

| T <sub>PLPH</sub> | PSEN Pulse Width                   |

| T <sub>PLIV</sub> | PSEN to Valid Instruction In       |

| T <sub>PXIX</sub> | Input Instruction Hold After PSEN  |

| T <sub>PXIZ</sub> | Input Instruction Float After PSEN |

| T <sub>AVIV</sub> | Address to Valid Instruction In    |

| T <sub>PLAZ</sub> | PSEN Low to Address Float          |

## Table 119. AC Parameters for a Fix Clock (F = 40 MHz)

| Symbol            | Min | Мах | Units |

|-------------------|-----|-----|-------|

| Т                 | 25  |     | ns    |

| T <sub>LHLL</sub> | 40  |     | ns    |

| T <sub>AVLL</sub> | 10  |     | ns    |

| T <sub>LLAX</sub> | 10  |     | ns    |

| T <sub>LLIV</sub> |     | 70  | ns    |

| T <sub>LLPL</sub> | 15  |     | ns    |

| T <sub>PLPH</sub> | 55  |     | ns    |

| T <sub>PLIV</sub> |     | 35  | ns    |

| T <sub>PXIX</sub> | 0   |     | ns    |

| T <sub>PXIZ</sub> |     | 18  | ns    |

| T <sub>AVIV</sub> |     | 85  | ns    |

| T <sub>PLAZ</sub> |     | 10  | ns    |

| Symbol            | Туре | Standard<br>Clock | X2 Clock  | X parameter | Units |

|-------------------|------|-------------------|-----------|-------------|-------|

| T <sub>RLRH</sub> | Min  | 6 T - x           | 3 T - x   | 20          | ns    |

| T <sub>WLWH</sub> | Min  | 6 T - x           | 3 T - x   | 20          | ns    |

| T <sub>RLDV</sub> | Max  | 5 T - x           | 2.5 T - x | 25          | ns    |

| T <sub>RHDX</sub> | Min  | х                 | х         | 0           | ns    |

| T <sub>RHDZ</sub> | Max  | 2 T - x           | T - x     | 20          | ns    |

| T <sub>LLDV</sub> | Max  | 8 T - x           | 4T -x     | 40          | ns    |

| T <sub>AVDV</sub> | Max  | 9 T - x           | 4.5 T - x | 60          | ns    |

| T <sub>LLWL</sub> | Min  | 3 T - x           | 1.5 T - x | 25          | ns    |

| T <sub>LLWL</sub> | Max  | 3 T + x           | 1.5 T + x | 25          | ns    |

| T <sub>AVWL</sub> | Min  | 4 T - x           | 2 T - x   | 25          | ns    |

| T <sub>QVWX</sub> | Min  | T - x             | 0.5 T - x | 15          | ns    |

| T <sub>QVWH</sub> | Min  | 7 T - x           | 3.5 T - x | 25          | ns    |

| T <sub>WHQX</sub> | Min  | T - x             | 0.5 T - x | 10          | ns    |

| T <sub>RLAZ</sub> | Max  | х                 | х         | 0           | ns    |

| T <sub>WHLH</sub> | Min  | T - x             | 0.5 T - x | 15          | ns    |

| T <sub>WHLH</sub> | Max  | T + x             | 0.5 T + x | 15          | ns    |

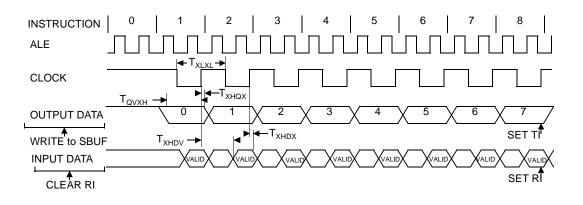

Table 123.

AC Parameters for a Variable Clock

| Symbol            | Min | Мах | Units |

|-------------------|-----|-----|-------|

| T <sub>XLXL</sub> | 300 |     | ns    |

| T <sub>QVHX</sub> | 200 |     | ns    |

| T <sub>XHQX</sub> | 30  |     | ns    |

| T <sub>XHDX</sub> | 0   |     | ns    |

| T <sub>XHDV</sub> |     | 117 | ns    |

#### Table 125. AC Parameters for a Fix Clock (F = 40 MHz)

### Table 126. AC Parameters for a Variable Clock

| Symbol            | Туре | Standard<br>Clock | X2 Clock | X parameter<br>for -M range | Units |

|-------------------|------|-------------------|----------|-----------------------------|-------|

| T <sub>XLXL</sub> | Min  | 12 T              | 6 T      |                             | ns    |

| T <sub>QVHX</sub> | Min  | 10 T - x          | 5 T - x  | 50                          | ns    |

| T <sub>XHQX</sub> | Min  | 2 T - x           | T - x    | 20                          | ns    |

| T <sub>XHDX</sub> | Min  | х                 | х        | 0                           | ns    |

| T <sub>XHDV</sub> | Max  | 10 T - x          | 5 T- x   | 133                         | ns    |

# Shift Register Timing Waveforms

#### External Clock Drive Characteristics (XTAL1)

### Table 127. AC Parameters

| Symbol                               | Parameter               | Min | Мах | Units |

|--------------------------------------|-------------------------|-----|-----|-------|

| T <sub>CLCL</sub>                    | Oscillator Period       | 25  |     | ns    |

| T <sub>CHCX</sub>                    | High Time               | 5   |     | ns    |

| T <sub>CLCX</sub>                    | Low Time                | 5   |     | ns    |

| T <sub>CLCH</sub>                    | Rise Time               |     | 5   | ns    |

| T <sub>CHCL</sub>                    | Fall Time               |     | 5   | ns    |

| T <sub>CHCX</sub> /T <sub>CLCX</sub> | Cyclic ratio in X2 mode | 40  | 60  | %     |

### **STANDARD NOTES FOR PLCC**

## 1/ CONTROLLING DIMENSIONS : INCHES

## 2/ DIMENSIONING AND TOLERANCING PER ANSI Y 14.5M - 1982.

3/ "D" AND "E1" DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTUSIONS. MOLD FLASH OR PROTUSIONS SHALL NOT EXCEED 0.20 mm (.008 INCH) PER SIDE.

## STANDARD NOTES FOR PQFP/ VQFP / TQFP / DQFP

1/ CONTROLLING DIMENSIONS : INCHES

2/ ALL DIMENSIONING AND TOLERANCING CONFORM TO ANSI Y 14.5M - 1982.

3/ "D1 AND E1" DIMENSIONS DO NOT INCLUDE MOLD PROTUSIONS. MOLD PROTUSIONS SHALL NOT EXCEED 0.25 mm (0.010 INCH). THE TOP PACKAGE BODY SIZE MAY BE SMALLER THAN THE BOTTOM PACKAGE BODY SIZE BY AS MUCH AS 0.15 mm.

4/ DATUM PLANE "H" LOCATED AT MOLD PARTING LINE AND COINCIDENT WITH LEAD, WHERE LEAD EXITS PLASTIC BODY AT BOTTOM OF PARTING LINE.

5/ DATUM "A" AND "D" TO BE DETERMINED AT DATUM PLANE H.

6/ DIMENSION " f " DOES NOT INCLUDE DAMBAR PROTUSION ALLOWABLE DAMBAR PROTUSION SHALL BE 0.08mm/.003" TOTAL IN EXCESS OF THE " f " DIMENSION AT MAXIMUM MATERIAL CONDITION . DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT.