#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | 80C51                                                                        |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 40MHz                                                                        |

| Connectivity               | CANbus, UART/USART                                                           |

| Peripherals                | POR, PWM, WDT                                                                |

| Number of I/O              | 36                                                                           |

| Program Memory Size        | 64KB (64K x 8)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 2K x 8                                                                       |

| RAM Size                   | 2.25K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                    |

| Data Converters            | A/D 8x10b                                                                    |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 44-LQFP                                                                      |

| Supplier Device Package    | 44-VQFP (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at89c51cc03u-rltim |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VSS      | GND  | Circuit ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| TESTI    | I    | Must be connected to VSS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| VCC      |      | Supply Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| VAREF    |      | Reference Voltage for ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| VAGND    |      | Reference Ground for ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| P0.0:7   | I/O  | <b>Port 0:</b><br>Is an 8-bit open drain bi-directional I/O port. Port 0 pins that have 1's written to them float, and in this state can be used as high-impedance inputs. Port 0 is also the multiplexed low-order address and data bus during accesses to external Program and Data Memory. In this application it uses strong internal pull-ups when emitting 1's.<br>Port 0 also outputs the code Bytes during program validation. External pull-ups are required during program verification.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| P1.0:7   | I/O  | Port 1:<br>Is an 8-bit bi-directional I/O port with internal pull-ups. Port 1 pins can be used for digital input/output or as analog inputs for<br>the Analog Digital Converter (ADC). Port 1 pins that have 1's written to them are pulled high by the internal pull-up transistors<br>and can be used as inputs in this state. As inputs, Port 1 pins that are being pulled low externally will be the source of current<br>(IL), see section "Electrical Characteristic") because of the internal pull-ups. Port 1 pins are assigned to be used as analog<br>inputs via the ADCCF register (in this case the internal pull-ups. Port 1 pins are assigned to be used as analog<br>inputs via the ADCCF register (in this case the internal pull-ups are disconnected).<br>As a secondary digital function, port 1 contains the Timer 2 external trigger and clock input; the PCA external clock input and<br>the PCA module I/O.<br>P1.0/AN0/T2<br>Analog input channel 0,<br>External clock input for Timer/counter2.<br>P1.1/AN1/T2EX<br>Analog input channel 1,<br>Trigger input for Timer/counter2.<br>P1.2/AN2/ECI<br>Analog input channel 2,<br>PCA external clock input.<br>P1.3/AN3/CEX0<br>Analog input channel 3,<br>PCA module 0 Entry of input/PWM output.<br>P1.4/AN4/CEX1<br>Analog input channel 4,<br>PCA module 1 Entry of input/PWM output.<br>P1.5/AN5/CEX2<br>Analog input channel 5,<br>PCA. Module 1 Entry of input/PWM output.<br>P1.5/ANS/CEX3<br>Analog input channel 6,<br>PCA module 2 Entry of input/PWM output. |

|          |      | P1.7/AN7/CEX4<br>Analog input channel 7,<br>PCA module 4 Entry ot input/PWM output.<br>Port 1 receives the low-order address byte during EPROM programming and program verification.<br>It can drive CMOS inputs without external pull-ups.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| P2.0:7   | I/O  | <b>Port 2:</b><br>Is an 8-bit bi-directional I/O port with internal pull-ups. Port 2 pins that have 1's written to them are pulled high by the internal pull-ups and can be used as inputs in this state. As inputs, Port 2 pins that are being pulled low externally will be a source of current (I <sub>IL</sub> , see section "Electrical Characteristic") because of the internal pull-ups. Port 2 emits the high-order address byte during accesses to the external Program Memory and during accesses to external Data Memory that uses 16-bit addresses (MOVX @DPTR). In this application, it uses strong internal pull-ups when emitting 1's. During accesses to external Data Memory that use 8 bit addresses (MOVX @Ri), Port 2 transmits the contents of the P2 special function register. It also receives high-order addresses and control signals during program validation. It can drive CMOS inputs without external pull-ups.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Pin Name | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P3.0:7   | I/O  | <b>Port 3:</b><br>Is an 8-bit bi-directional I/O port with internal pull-ups. Port 3 pins that have 1's written to them are pulled high by the internal pull-up transistors and can be used as inputs in this state. As inputs, Port 3 pins that are being pulled low externally will be a source of current (I <sub>IL</sub> , see section "Electrical Characteristic") because of the internal pull-ups.<br>The output latch corresponding to a secondary function must be programmed to one for that function to operate (except for TxD and WR). The secondary functions are assigned to the pins of port 3 as follows:                                                                                                                                                                                                                          |

|          |      | P3.0/RxD:<br>Receiver data input (asynchronous) or data input/output (synchronous) of the serial interface<br>P3.1/TxD:<br>Transmitter data output (asynchronous) or clock output (synchronous) of the serial interface<br>P3.2/INT0:<br>External interrupt 0 input/timer 0 gate control input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|          |      | P3.3/INT1:<br>External interrupt 1 input/timer 1 gate control input<br>P3.4/T0:<br>Timer 0 counter input<br>P3.5/T1/SS:<br>Timer 1 counter input<br>SPI Slave Select<br>P3.6/WR:<br>External Data Memory write strobe; latches the data byte from port 0 into the external data memory<br>P3.7/RD:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| P4.0:4   | I/O  | External Data Memory read strobe; Enables the external data memory.<br>It can drive CMOS inputs without external pull-ups.<br>Port 4:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ₩4.U:4   | 1/0  | Port 4:         Is an 2-bit bi-directional I/O port with internal pull-ups. Port 4 pins that have 1's written to them are pulled high by the internal pull-ups and can be used as inputs in this state. As inputs, Port 4 pins that are being pulled low externally will be a source of current (IIL, on the datasheet) because of the internal pull-up transistor.         The output latch corresponding to a secondary function RxDC must be programmed to one for that function to operate. The secondary functions are assigned to the two pins of port 4 as follows:         P4.0/TxDC:         Transmitter output of CAN controller         P4.1/RxDC:         Receiver input of CAN controller.         P4.2/MISO:         Master Input Slave Output of SPI controller         P4.4/MOSI:         Master Ouput Slave Input of SPI controller |

|          |      | It can drive CMOS inputs without external pull-ups.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

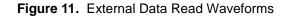

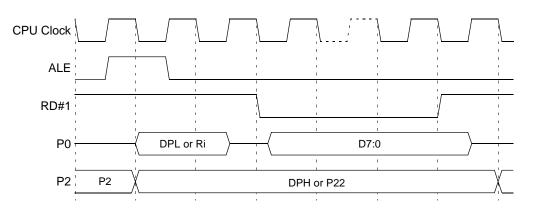

Notes: 1. RD# signal may be stretched using M0 bit in AUXR register.2. When executing MOVX @Ri instruction, P2 outputs SFR content.

## Registers

### Table 6. PSW Register

PSW (S:8Eh) Program Status Word Register

| 7             | 6               | 5                                                                                                             | 4                                                                  | 3           | 2  | 1  | 0 |  |

|---------------|-----------------|---------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-------------|----|----|---|--|

| CY            | AC              | F0                                                                                                            | RS1                                                                | RS0         | ov | F1 | Р |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                   |                                                                    |             |    |    |   |  |

| 7             | CY              | Carry Flag<br>Carry out fro                                                                                   | m bit 1 of ALL                                                     | J operands. |    |    |   |  |

| 6             | AC              | -                                                                                                             | Auxiliary Carry Flag<br>Carry out from bit 1 of addition operands. |             |    |    |   |  |

| 5             | F0              | User Defina                                                                                                   | ble Flag 0.                                                        |             |    |    |   |  |

| 4-3           | RS1:0           | -                                                                                                             | nk Select Bit<br>e 4 for bits de                                   |             |    |    |   |  |

| 2             | OV              |                                                                                                               | <b>Overflow Flag</b><br>Overflow set by arithmetic operations.     |             |    |    |   |  |

| 1             | F1              | User Defina                                                                                                   | User Definable Flag 1                                              |             |    |    |   |  |

| 0             | Р               | Parity Bit<br>Set when ACC contains an odd number of 1's.<br>Cleared when ACC contains an even number of 1's. |                                                                    |             |    |    |   |  |

Reset Value = 0000 0000b

## Table 7. AUXR Register

AUXR (S:8Eh) Auxiliary Register

| 7             | 6               | 5                                                                                                                                                                                            | 4                                                                                  | 3    | 2    | 1      | 0  |  |

|---------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|------|------|--------|----|--|

| -             | -               | MO                                                                                                                                                                                           | XRS2                                                                               | XRS1 | XRS0 | EXTRAM | A0 |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                  |                                                                                    |      |      |        |    |  |

| 7-6           | -               | Reserved<br>The value re                                                                                                                                                                     | Reserved<br>The value read from these bits are indeterminate. Do not set this bit. |      |      |        |    |  |

| 5             | MO              | Stretch MOVX control:         the RD/ and the WR/ pulse length is increased according to the value of M0.         M0       Pulse length in clock period         0       6         1       30 |                                                                                    |      |      |        |    |  |

| Mode                                 | Port 0   | Port 1 | Port 2 | Port 3 | Port 4 | ALE  | PSEN# |

|--------------------------------------|----------|--------|--------|--------|--------|------|-------|

| Reset                                | Floating | High   | High   | High   | High   | High | High  |

| Idle<br>(internal<br>code)           | Data     | Data   | Data   | Data   | Data   | High | High  |

| Idle<br>(external<br>code)           | Floating | Data   | Data   | Data   | Data   | High | High  |

| Power-<br>Down(inter<br>nal code)    | Data     | Data   | Data   | Data   | Data   | Low  | Low   |

| Power-<br>Down<br>(external<br>code) | Floating | Data   | Data   | Data   | Data   | Low  | Low   |

Table 9. Pin Conditions in Special Operating Modes

### Cross Flash Memory Access

|           |                 | Action            | FM0<br>(user Flash) | FM1<br>(boot Flash) |

|-----------|-----------------|-------------------|---------------------|---------------------|

|           |                 | Read              | ok                  | -                   |

| E         | FM0             | Load column latch | ok                  | -                   |

| ig from   | (user Flash)    | Write             | -                   | -                   |

| executing |                 | Read              | ok                  | ok                  |

|           |                 | Load column latch | ok                  | -                   |

| Code      | (boot Flash)    | Write             | ok                  | -                   |

|           | External memory | Read              | (a)                 | -                   |

|           |                 | Load column latch | -                   | -                   |

|           | EA = 0          | Write             | -                   | -                   |

(a) Depend upon general lock bit configuration.

## **Operation Cross Memory Access**

Space addressable in read and write are:

- RAM

- ERAM (Expanded RAM access by movx)

- XRAM (eXternal RAM)

- EEPROM DATA

- FM0 ( user flash )

- Hardware byte

- XROW

- Boot Flash

- Flash Column latch

The table below provide the different kind of memory which can be accessed from different code location.

Table 18. Cross Memory Access

|                             | Action | RAM | XRAM<br>ERAM | Boot FLASH | FM0               | E <sup>2</sup> Data | Hardware<br>Byte  | XROW              |

|-----------------------------|--------|-----|--------------|------------|-------------------|---------------------|-------------------|-------------------|

| boot FLASH                  | Read   |     |              | OK         | ОК                | ОК                  | ОК                | -                 |

| DOUL FLASH                  | Write  |     |              | -          | OK <sup>(1)</sup> | OK <sup>(1)</sup>   | OK <sup>(1)</sup> | OK <sup>(1)</sup> |

| EMO                         | Read   |     |              | ОК         | ОК                | ОК                  | ОК                | -                 |

| FMO                         | Write  |     |              | -          | OK (idle)         | OK <sup>(1)</sup>   | -                 | ОК                |

| External memory             | Read   |     |              | -          | -                 | ОК                  | -                 | -                 |

| EA = 0<br>or Code Roll Over | Write  |     |              | -          | -                 | OK <sup>(1)</sup>   | -                 | -                 |

Note: 1. RWW: Read While Write

|                       | Boot Loader Jump Bit (BLJB):<br>- This bit indicates if on RESET the user wants to jump to this application at address<br>@0000h on FM0 or execute the boot loader at address @F800h on FM1.<br>- BLJB = 0 on parts delivered with bootloader programmed.<br>- To read or modify this bit, the APIs are used. |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       | Boot Vector Address (SBV):<br>- This byte contains the MSB of the user boot loader address in FM0.<br>- The default value of SBV is FCh (no user boot loader in FM0).<br>- To read or modify this byte, the APIs are used.                                                                                    |

|                       | Extra Byte (EB) and Boot Status Byte (BSB):<br>- These Bytes are reserved for customer use.<br>- To read or modify these Bytes, the APIs are used.                                                                                                                                                            |

| Hardware Boot Process | At the falling edge of RESET, the bit ENBOOT in AUXR1 register is initialized with the value of Boot Loader Jump Bit (BLJB).                                                                                                                                                                                  |

|                       | Further at the falling edge of RESET if the following conditions (called Hardware condi-<br>tion) are detected:                                                                                                                                                                                               |

|                       | PSEN low,                                                                                                                                                                                                                                                                                                     |

|                       | EA high,                                                                                                                                                                                                                                                                                                      |

|                       | ALE high (or not connected).                                                                                                                                                                                                                                                                                  |

|                       | <ul> <li>After Hardware Condition the FCON register is initialized with the value 00h<br/>and the PC is initialized with F800h (FM1).</li> </ul>                                                                                                                                                              |

|                       | The Hardware condition makes the bootloader to be executed, whatever BLJB value is.                                                                                                                                                                                                                           |

|                       | If no hardware condition is detected, the FCON register is initialized with the value F0h.                                                                                                                                                                                                                    |

|                       | Check of the BLJB value.                                                                                                                                                                                                                                                                                      |

|                       | • If bit BLJB = 1:                                                                                                                                                                                                                                                                                            |

|                       | User application in FM0 will be started at @0000h (standard reset).                                                                                                                                                                                                                                           |

|                       | <ul> <li>If bit BLJB = 0:<br/>Boot loader will be started at @F800h in FM1.</li> </ul>                                                                                                                                                                                                                        |

|                       | <ol> <li>Note: 1. As PSEN is an output port in normal operating mode (running user applications or<br/>bootloader applications) after reset it is recommended to release PSEN after the fall-<br/>ing edge of Reset is signaled.</li> </ol>                                                                   |

The hardware conditions are sampled at reset signal Falling Edge, thus they can be released at any time when reset input is low.

2. To ensure correct microcontroller startup, the PSEN pin should not be tied to ground during power-on.

#### 4. Interrupt routine

// Save the current CANPAGE

// Find the first message object which generate an interrupt in CANSIT1 and CANSIT2

// Select the corresponding message object

// Analyse the CANSTCH register to identify which kind of interrupt is generated

// Manage the interrupt

// Clear the status register CANSTCH = 00h;

// if it is not a channel interrupt but a general interrupt// Manage the general interrupt and clear CANGIT register

// restore the old CANPAGE

## Table 54. CANEN1 Register

CANEN1 (S:CEh Read Only) CAN Enable Message Object Registers 1

| 7             | 6           | 5                                                                                                         | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3      | 2      | 1     | 0     |  |  |

|---------------|-------------|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|-------|-------|--|--|

| -             | ENCH14      | ENCH13                                                                                                    | ENCH12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ENCH11 | ENCH10 | ENCH9 | ENCH8 |  |  |

| Bit<br>Number | Bit Mnemoni | c Descriptio                                                                                              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |        |       |       |  |  |

| 7             | -           | <b>Reserved</b><br>The value                                                                              | Reserved<br>The values read from this bit is indeterminate. Do not set this bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |        |       |       |  |  |

| 6-0           | ENCH14:8    | These bits<br>It is set to<br>Once TXC<br>correspon<br>MOb in dia<br>0 - messa<br>reception.<br>1 - messa | Enable Message Object         These bits provide the availability of the MOb.         It is set to one when the MOb is enabled.         Once TXOK or RXOK is set to one (TXOK for automatic reply), the corresponding ENMOB is reset. ENMOB is also set to zero configuring the MOb in disabled mode, applying abortion or standby mode.         0 - message object disabled: MOb available for a new transmission or reception.         1 - message object enabled: MOb in use.         This bit is resetable by re-writing the CANCONCH of the corresponding |        |        |       |       |  |  |

Reset Value = x000 0000b **Table 55.** CANEN2 Register

CANEN2 (S:CFh Read Only) CAN Enable Message Object Registers 2

| 7             | 6            | 5                                                                                                         | 4                                                                                                                | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2                                                                             | 1                                            | 0                   |  |

|---------------|--------------|-----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|----------------------------------------------|---------------------|--|

| ENCH7         | ENCH6        | ENCH5                                                                                                     | ENCH4                                                                                                            | ENCH3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ENCH2                                                                         | ENCH1                                        | ENCH0               |  |

| Bit<br>Number | Bit Mnemonio | Description                                                                                               | Description                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                               |                                              |                     |  |

| 7-0           | ENCH7:0      | These bits<br>It is set to<br>Once TXC<br>correspon<br>MOb in dia<br>0 - messa<br>reception.<br>1 - messa | one when the<br>OK or RXOK is<br>ding ENMOB<br>sabled mode,<br>ge object disa<br>ge object ena<br>resetable by r | availability of the MOb is enable MOb is enables set to one (T is reset. ENM applying aborrubled: MOb av bled: MOb in the set to the | led.<br>XOK for autor<br>OB is also set<br>tion or standb<br>ailable for a ne | t to zero config<br>y mode.<br>ew transmissi | guring the<br>on or |  |

Reset Value = 0000 0000b

### **Error Conditions**

The following flags in the SPSCR register indicate the SPI error conditions:

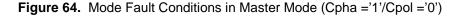

Mode Fault Error (MODF)

Mode Fault error in Master mode SPI indicates that the level on the Slave Select ( $\overline{SS}$ ) pin is inconsistent with the actual mode of the device.

• Mode fault detection in Master mode:

MODF is set to warn that there may be a multi-master conflict for system control. In this case, the SPI system is affected in the following ways:

- An SPI receiver/error CPU interrupt request is generated

- The SPEN bit in SPCON is cleared. This disables the SPI

- The MSTR bit in SPCON is cleared

Clearing the MODF bit is accomplished by a read of SPSCR register with MODF bit set, followed by a write to the SPCON register. SPEN Control bit may be restored to its original set state after the MODF bit has been cleared.

Mode fault detection in Slave mode

In slave mode, the MODF error is detected when SS goes high during a transmission. A transmission begins when SS goes low and ends once the incoming SCK goes back to its idle level following the shift of the eighteen data bit.

A MODF error occurs if a slave is selected (SS is low) and later unselected (SS is high) even if no SCK is sent to that slave.

At any time, a '1' on the SS pin of a slave SPI puts the MISO pin in a high impedance state and internal state counter is cleared. Also, the slave SPI ignores all incoming SCK clocks, even if it was already in the middle of a transmission. A new transmission will be performed as soon as SS pin returns low.

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4             | MODF            | Mode Fault         - Set by hardware to indicate that the SS pin is in inappropriate logic level (in both master and slave modes).         - Cleared by hardware when reading SPSCR         When MODF error occurred:         - In slave mode: SPI interface ignores all transmitted data while SS remains high.         A new transmission is perform as soon as SS returns low.         - In master mode: SPI interface is disabled (SPEN=0, see description for SPEN bit in SPCON register). |

| 3             | SPTE            | Serial Peripheral Transmit register Empty - Set by hardware when transmit register is empty (if needed, SPDAT can be loaded with another data) Cleared by hardware when transmit register is full (no more data should be loaded in SPDAT).                                                                                                                                                                                                                                                     |

| 2             | UARTM           | Serial Peripheral UART mode<br>Set and cleared by software:<br>- Clear: Normal mode, data are transmitted MSB first (default)<br>- Set: UART mode, data are transmitted LSB first.                                                                                                                                                                                                                                                                                                              |

| 1             | SPTEIE          | Interrupt Enable for SPTE<br>Set and cleared by software:<br>- Set to enable SPTE interrupt generation (when SPTE goes high, an interrupt is<br>generated).<br>- Clear to disable SPTE interrupt generation<br>Caution: When SPTEIE is set no interrupt generation occurred when SPIF flag<br>goes high. To enable SPIF interrupt again, SPTEIE should be cleared.                                                                                                                              |

| 0             | MODFIE          | Interrupt Enable for MODF<br>Set and cleared by software:<br>- Set to enable MODF interrupt generation<br>- Clear to disable MODF interrupt generation                                                                                                                                                                                                                                                                                                                                          |

Reset Value = 00X0 XXXXb

Not Bit addressable

Serial Peripheral DATa Register (SPDAT)

The Serial Peripheral Data Register (Table 94) is a read/write buffer for the receive data register. A write to SPDAT places data directly into the shift register. No transmit buffer is available in this model.

A Read of the SPDAT returns the value located in the receive buffer and not the content of the shift register.

### Table 94. SPDAT Register

SPDAT - Serial Peripheral Data Register (0D6H)

| 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|----|----|----|----|----|----|----|----|

| R7 | R6 | R5 | R4 | R3 | R2 | R1 | R0 |

Reset Value = Indeterminate

R7:R0: Receive data bits

SPCON, SPSTA and SPDAT registers may be read and written at any time while there is no on-going exchange. However, special care should be taken when writing to them while a transmission is on-going:

- Do not change SPR2, SPR1 and SPR0

- Do not change CPHA and CPOL

- Do not change MSTR

- Clearing SPEN would immediately disable the peripheral

- Writing to the SPDAT will cause an overflow.

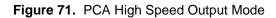

## High Speed Output Mode

In this mode the CEX output (on port 1) associated with the PCA module will toggle each time a match occurs between the PCA counter and the module's capture registers. To activate this mode the TOG, MAT, and ECOM bits in the module's CCAPMn SFR must be set.

# Pulse Width Modulator Mode

All the PCA modules can be used as PWM outputs. The output frequency depends on the source for the PCA timer. All the modules will have the same output frequency because they all share the PCA timer. The duty cycle of each module is independently variable using the module's capture register CCAPLn. When the value of the PCA CL SFR is less than the value in the module's CCAPLn SFR the output will be low, when it is equal to or greater than it, the output will be high. When CL overflows from FF to 00, CCAPLn is reloaded with the value in CCAPHn. the allows the PWM to be updated without glitches. The PWM and ECOM bits in the module's CCAPMn register must be set to enable the PWM mode.

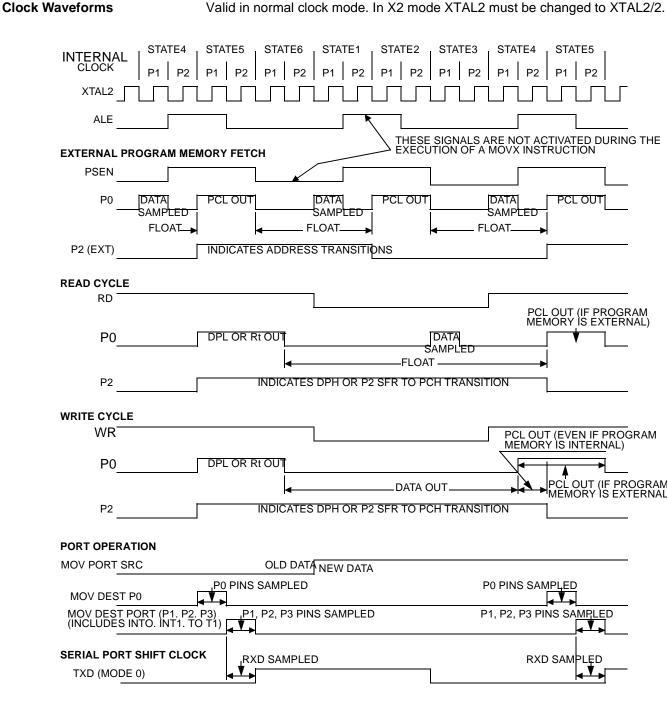

## External Program Memory Characteristics

## Table 118. Symbol Description

| Symbol            | Parameter                          |

|-------------------|------------------------------------|

| Т                 | Oscillator clock period            |

| T <sub>LHLL</sub> | ALE pulse width                    |

| T <sub>AVLL</sub> | Address Valid to ALE               |

| T <sub>LLAX</sub> | Address Hold After ALE             |

| T <sub>LLIV</sub> | ALE to Valid Instruction In        |

| T <sub>LLPL</sub> | ALE to PSEN                        |

| T <sub>PLPH</sub> | PSEN Pulse Width                   |

| T <sub>PLIV</sub> | PSEN to Valid Instruction In       |

| T <sub>PXIX</sub> | Input Instruction Hold After PSEN  |

| T <sub>PXIZ</sub> | Input Instruction Float After PSEN |

| T <sub>AVIV</sub> | Address to Valid Instruction In    |

| T <sub>PLAZ</sub> | PSEN Low to Address Float          |

## Table 119. AC Parameters for a Fix Clock (F = 40 MHz)

| Symbol            | Min | Мах | Units |

|-------------------|-----|-----|-------|

| Т                 | 25  |     | ns    |

| T <sub>LHLL</sub> | 40  |     | ns    |

| T <sub>AVLL</sub> | 10  |     | ns    |

| T <sub>LLAX</sub> | 10  |     | ns    |

| T <sub>LLIV</sub> |     | 70  | ns    |

| T <sub>LLPL</sub> | 15  |     | ns    |

| T <sub>PLPH</sub> | 55  |     | ns    |

| T <sub>PLIV</sub> |     | 35  | ns    |

| T <sub>PXIX</sub> | 0   |     | ns    |

| T <sub>PXIZ</sub> |     | 18  | ns    |

| T <sub>AVIV</sub> |     | 85  | ns    |

| T <sub>PLAZ</sub> |     | 10  | ns    |

This diagram indicates when signals are clocked internally. The time it takes the signals to propagate to the pins, however, ranges from 25 to 125 ns. This propagation delay is dependent on variables such as temperature and pin loading. Propagation also varies from output to output and component. Typically though ( $T_A=25^{\circ}C$  fully loaded) RD and WR propagation delays are approximately 50ns. The other signals are typically 85 ns. Propagation delays are incorporated in the AC specifications.

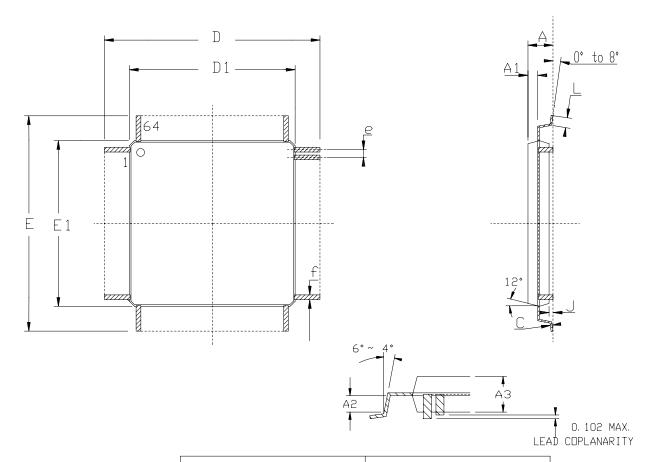

## VQFP64

|     | М      |        | INCH      |       |  |

|-----|--------|--------|-----------|-------|--|

|     | Min    | Ma×    | Min       | Ma×   |  |

| A   | _      | 1,60   | _         | , 063 |  |

| Α1  | 0.     | 64 REF | , 025 REF |       |  |

| A2  | 0.     | 64 REF | , 025 REF |       |  |

| АЗ  | 1, 35  | 1.45   | . 053     | , 057 |  |

| D   | 11, 75 | 12, 25 | , 463     | , 483 |  |

| D 1 | 9, 90  | 10, 10 | , 390     | , 398 |  |

| E   | 11, 75 | 12, 25 | , 463     | , 483 |  |

| E 1 | 9, 90  | 10.10  | , 390     | , 398 |  |

| J   | 0, 05  | _      | , 002     | _     |  |

| L   | 0, 45  | 0, 75  | . 018     | , 030 |  |

| e   | 0, 5   | O BSC  | ,0197 BSC |       |  |

| f   | 0, 2   | 5 BSC  | , O1O BSC |       |  |

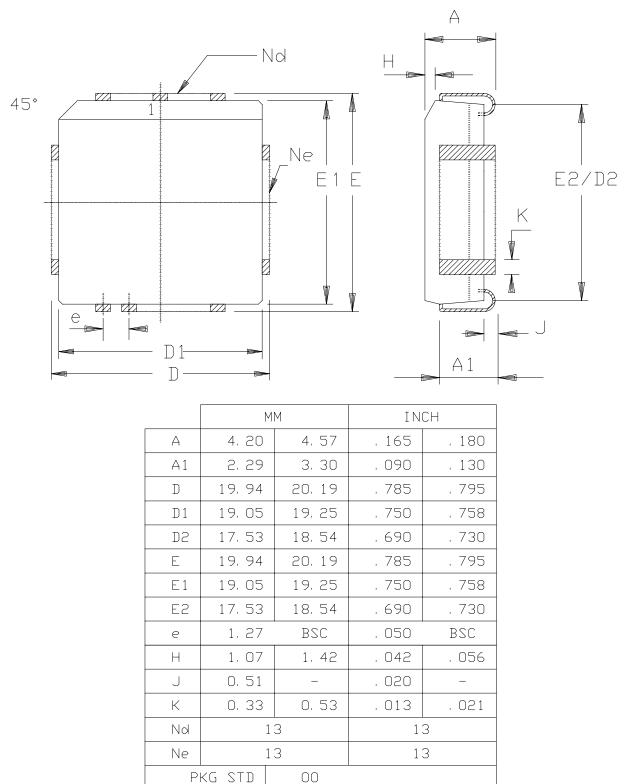

PLCC52

| I     | IT CAN Management                                     | . 94 |

|-------|-------------------------------------------------------|------|

| I     | Bit Timing and Baud Rate                              | 96   |

| I     | Fault Confinement                                     | . 98 |

|       | Acceptance Filter                                     | . 99 |

| I     | Data and Remote Frame                                 | 100  |

| -     | Time Trigger Communication (TTC) and Message Stamping | 101  |

| (     | CAN Autobaud and Listening Mode                       | 102  |

| I     | Routines Examples                                     | 102  |

| (     | CAN SFR's                                             | 105  |

| I     | Registers                                             | 106  |

| Seria | I Port Interface (SPI)                                | 129  |

|       | Features                                              |      |

|       | Signal Description                                    |      |

|       | Functional Description                                |      |

| Drog  |                                                       |      |

| -     | rammable Counter Array (PCA)                          |      |

|       | PCA Timer                                             |      |

|       | PCA Modules                                           |      |

|       | PCA Interrupt                                         |      |

|       | PCA Capture Mode                                      |      |

|       | 16-bit Software Timer Mode                            |      |

|       | High Speed Output Mode                                |      |

|       | Pulse Width Modulator Mode                            |      |

| I     | PCA WatchDog Timer                                    | 146  |

| I     | PCA Registers                                         | 147  |

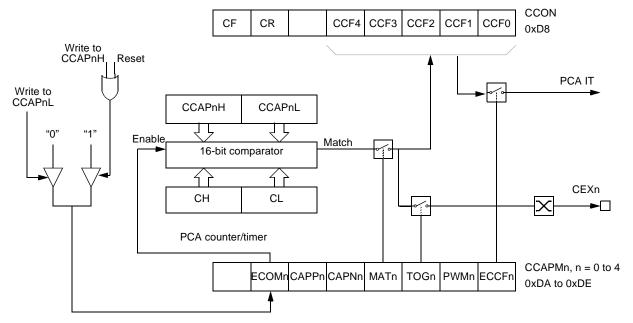

| Anal  | og-to-Digital Converter (ADC)                         | 152  |

|       | Features                                              | 152  |

|       | ADC Port1 I/O Functions                               | 152  |

|       | ADC Converter Operation                               | 154  |

|       | Voltage Conversion                                    |      |

|       | Clock Selection                                       |      |

|       | ADC Standby Mode                                      |      |

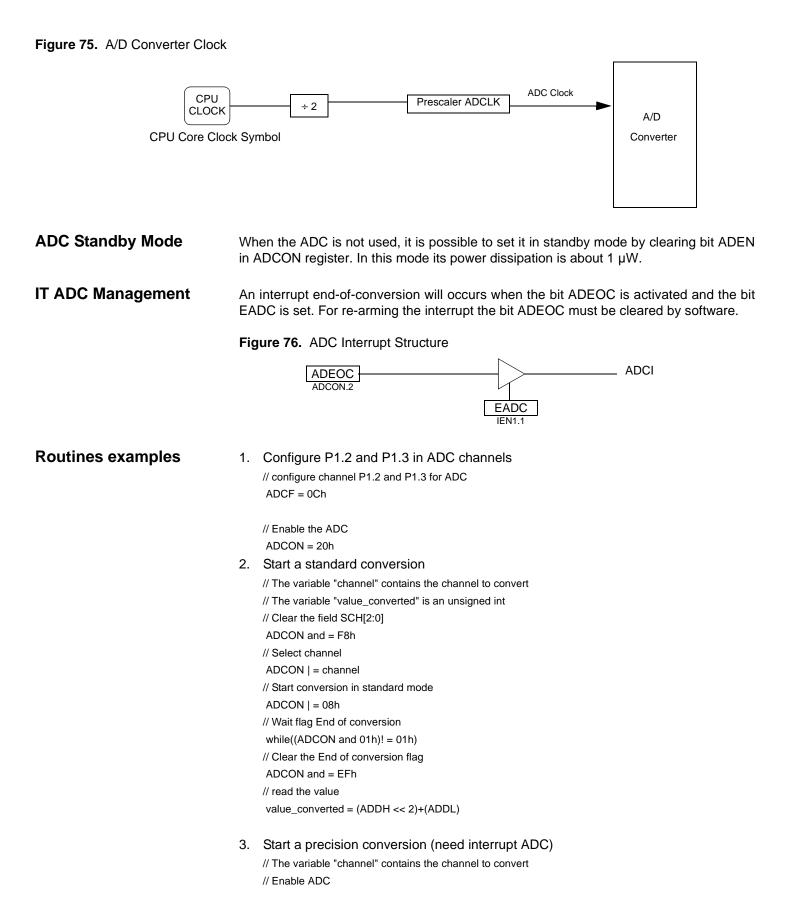

|       | IT ADC Management                                     |      |

|       | Routines examples                                     |      |

|       | Registers                                             |      |

| Intor | rupt System                                           | 160  |

|       | Introduction                                          |      |

|       | Registers                                             |      |

|       |                                                       |      |

|       | rical Characteristics                                 |      |

|       | Absolute Maximum Ratings                              |      |

|       | ICCOP Test Conditions                                 |      |

| I     | DC Parameters for Standard Voltage                    | 168  |