Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                                   |

|----------------------------|---------------------------------------------------------------------------------------|

| Core Processor             | V850ES                                                                                |

| Core Size                  | 32-Bit Single-Core                                                                    |

| Speed                      | 64MHz                                                                                 |

| Connectivity               | CSI, I <sup>2</sup> C, UART/USART                                                     |

| Peripherals                | DMA, LVD, PWM, WDT                                                                    |

| Number of I/O              | 44                                                                                    |

| Program Memory Size        | 128KB (128K x 8)                                                                      |

| Program Memory Type        | FLASH                                                                                 |

| EEPROM Size                | -                                                                                     |

| RAM Size                   | 8K x 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 3.5V ~ 5.5V                                                                           |

| Data Converters            | A/D 10x12b, 4x10b                                                                     |

| Oscillator Type            | External                                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                     |

| Mounting Type              | Surface Mount                                                                         |

| Package / Case             | 80-LQFP                                                                               |

| Supplier Device Package    | 80-LQFP (14x14)                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd70f3451gc-r-ubt-a |

|                            |                                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| O Timer/counter function:    | <ul> <li>16-bit interval timer M (TMM): 4 channels</li> <li>16-bit timer/event counter AA (TAA): 5 channels</li> <li>16-bit timer/event counter AB (TAB): 2 channels</li> <li>16-bit timer/event counter T (TMT): 2 channels</li> <li>Motor control function (uses timer TAB: 2 channels (TAB0, TAB1), TAA: 2 channels</li> <li>(TAA0, TAA1))</li> <li>16-bit accuracy 6-phase PWM function with deadtime: 2 channels</li> <li>High-impedance output control function</li> <li>A/D trigger generation by timer tuning operation function</li> <li>Arbitrary cycle setting function</li> <li>Arbitrary deadtime setting function</li> </ul> |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| O Serial interfaces:         | Asynchronous serial interface A (UARTA)<br>Asynchronous serial interface B (UARTB)<br>Clocked serial interface B (CSIB)<br>I <sup>2</sup> C bus interface (I <sup>2</sup> C)                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                              | UARTA0/CSIB0: 1 channel<br>UARTA1/I <sup>2</sup> C: 1 channel<br>UARTA2/CSIB1: 1 channel<br>UARTB/CSIB2: 1 channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| O A/D converter:             | <ul> <li>12-bit resolution A/D converters (A/D converters 0 and 1): 5 channels + 5 channels (2 units)</li> <li>The one A/D converter 0 channel and three A/D converter 1 channels are provided with an operational amplifier for input level amplification and a comparator for overvoltage detection.</li> <li>10-bit resolution A/D converter (A/D converter 2): 4 channels</li> </ul>                                                                                                                                                                                                                                                   |

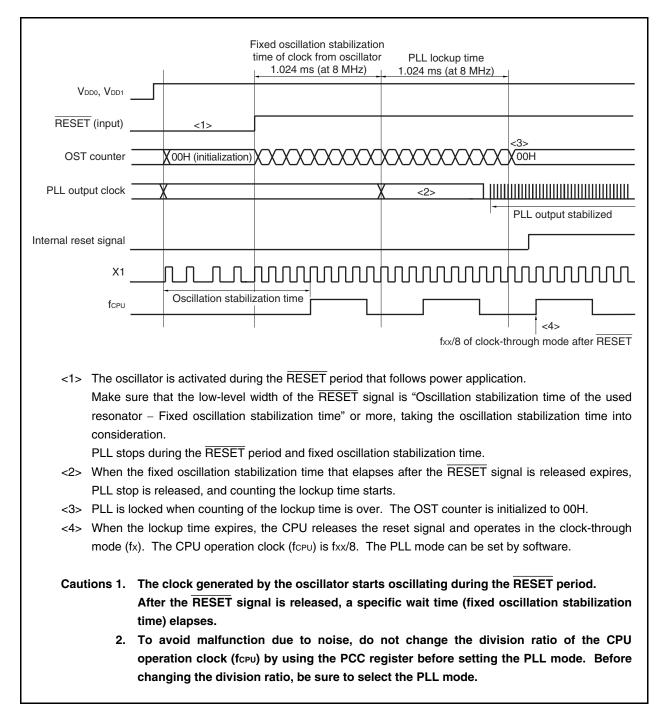

| O Clock generator:           | 4 to 8 MHz resonator connectable (external clock input prohibited)<br>Multiplication function by PLL clock synthesizer (fixed to multiplication by eight, fxx =<br>32 to 64 MHz)<br>CPU clock division function (fxx, fxx/2, fxx/4, fxx/8)                                                                                                                                                                                                                                                                                                                                                                                                 |

| O Power-save function:       | HALT/IDLE/STOP mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| O Power-on-clear function:   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| O Low-voltage detection func | otion:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| O Package:                   | 80-pin plastic LQFP (14 $\times$ 14)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| O Operation supply voltage:  | VDD0 = VDD1 = EVDD0 = EVDD1 = AVDD0 = AVDD1 = AVDD2 = 4.0 to 5.5 V<br>(when A/D converter 0, 1 or 2 is operating)<br>VDD0 = VDD1 = EVDD0 = EVDD1 = AVDD0 = AVDD1 = AVDD2 = 3.5 to 5.5 V<br>(when none of A/D converters 0 to 2 is operating)                                                                                                                                                                                                                                                                                                                                                                                               |

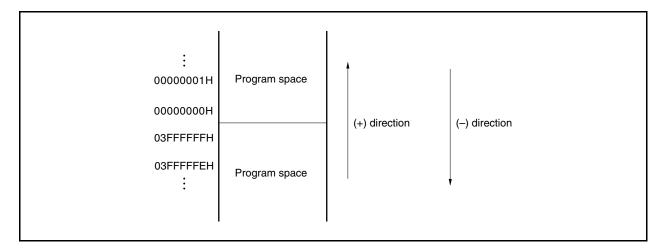

## 3.4.3 Wraparound of CPU address space

## (1) Program space

Of the 32 bits of the PC (program counter), the higher 6 bits are fixed to 0, and only the lower 26 bits are valid. Even if a carry or borrow occurs from bit 25 to 26 as a result of a branch address calculation, the higher 6 bits ignore the carry or borrow.

Therefore, the upper-limit address of the program space, address 03FFFFFFH, and the lower-limit address 00000000H become contiguous addresses. Wraparound refers to a situation like this whereby the lower-limit address and upper-limit address become contiguous.

Caution The 4 KB area of 03FFF000H to 03FFFFFH can be seen as an image of 0FFFF000H to 0FFFFFFH. This area is access-prohibited. Therefore, do not execute any branch address calculation in which the result will reside in any part of this area.

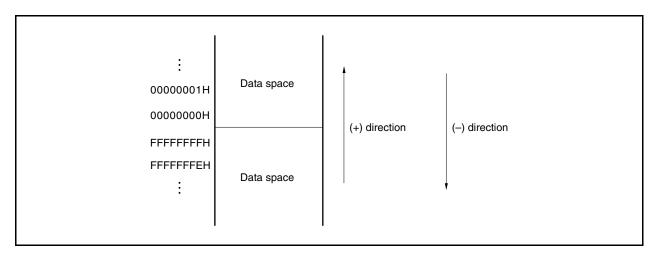

## (2) Data space

The result of an operand address calculation that exceeds 32 bits is ignored.

Therefore, the upper-limit address of the program space, address FFFFFFFH, and the lower-limit address 00000000H are contiguous addresses, and the data space is wrapped around at the boundary of these addresses.

#### (1/14)R/W After Reset Address Function Register Name Symbol Bit Units for Manipulation 1 8 16 FFFFF004H PDL R/W $\sqrt{}$ Undefined Port DL register FFFFF004H PDLL $\sqrt{}$ $\sqrt{}$ Undefined Port DLL register $\sqrt{}$ $\sqrt{}$ FFFFF005H PDLH Undefined Port DLH register $\sqrt{}$ FFFFH PMDL FFFFF024H Port DL mode register FFFFF024H Port DL mode register L PMDLL $\sqrt{}$ $\sqrt{}$ FFH FFFFF025H PMDLH $\sqrt{}$ $\sqrt{}$ FFH Port DL mode register H $\sqrt{}$ PMCDL 0000H FFFFF044H Port DL mode control register FFFFF044H PMCDLL $\sqrt{}$ $\sqrt{}$ 00H Port DL mode control register L FFFFF045H PMCDLH $\sqrt{}$ $\sqrt{}$ Port DL mode control register H 00H $\sqrt{}$ BSC FFFFF066H Bus size configuration register 5555H FFFFF06EH vswc $\sqrt{}$ 77H System wait control register FFFFF080H DMA source address register 0L DSA0L $\sqrt{}$ Undefined $\sqrt{}$ FFFFF082H DMA source address register 0H DSA0H Undefined $\sqrt{}$ FFFFF084H DDA0L Undefined DMA destination address register 0L FFFFF086H **DDA0H** $\sqrt{}$ Undefined DMA destination address register 0H FFFFF088H DMA source address register 1L DSA1L $\sqrt{}$ Undefined FFFFF08AH DSA1H $\sqrt{}$ DMA source address register 1H Undefined DDA1L FFFFF08CH DMA destination address register 1L $\sqrt{}$ Undefined $\sqrt{}$ FFFFF08EH DMA destination address register 1H DDA1H Undefined $\sqrt{}$ DSA2L FFFFF090H DMA source address register 2L Undefined FFFFF092H DSA2H $\sqrt{}$ Undefined DMA source address register 2H FFFFF094H DDA2L $\sqrt{}$ Undefined DMA destination address register 2L FFFFF096H DDA2H $\sqrt{}$ Undefined DMA destination address register 2H FFFFF098H DSA3I $\sqrt{}$ Undefined DMA source address register 3L $\sqrt{}$ FFFFF09AH DSA3H Undefined DMA source address register 3H $\sqrt{}$ **DDA3L** Undefined FFFFF09CH DMA destination address register 3L FFFFF09EH DMA destination address register 3H DDA3H $\sqrt{}$ Undefined DBC0 $\sqrt{}$ FFFFF0C0H DMA transfer count register 0 Undefined $\sqrt{}$ DBC1 FFFFF0C2H DMA transfer count register 1 Undefined FFFFF0C4H DBC2 $\sqrt{}$ Undefined DMA transfer count register 2 FFFFF0C6H DBC3 $\sqrt{}$ Undefined DMA transfer count register 3 $\sqrt{}$ DADC0 0000H **FFFFF0D0H** DMA addressing control register 0 DADC1 $\sqrt{}$ FFFFF0D2H DMA addressing control register 1 0000H FFFFF0D4H DMA addressing control register 2 DADC2 $\sqrt{}$ 0000H $\sqrt{}$ 0000H FFFFF0D6H DMA addressing control register 3 DADC3 **FFFFF0E0H** $\sqrt{}$ $\sqrt{}$ DCHC0 00H DMA channel control register 0 $\sqrt{}$ $\sqrt{}$ FFFFF0E2H DMA channel control register 1 DCHC1 00H $\sqrt{}$ $\sqrt{}$ FFFFF0E4H DMA channel control register 2 DCHC2 00H $\sqrt{}$ $\sqrt{}$ FFFFF0E6H DMA channel control register 3 DCHC3 00H

## 3.4.7 On-chip peripheral I/O registers

## 5.5.3 Operation timing

# (1) Power on (power-on reset)

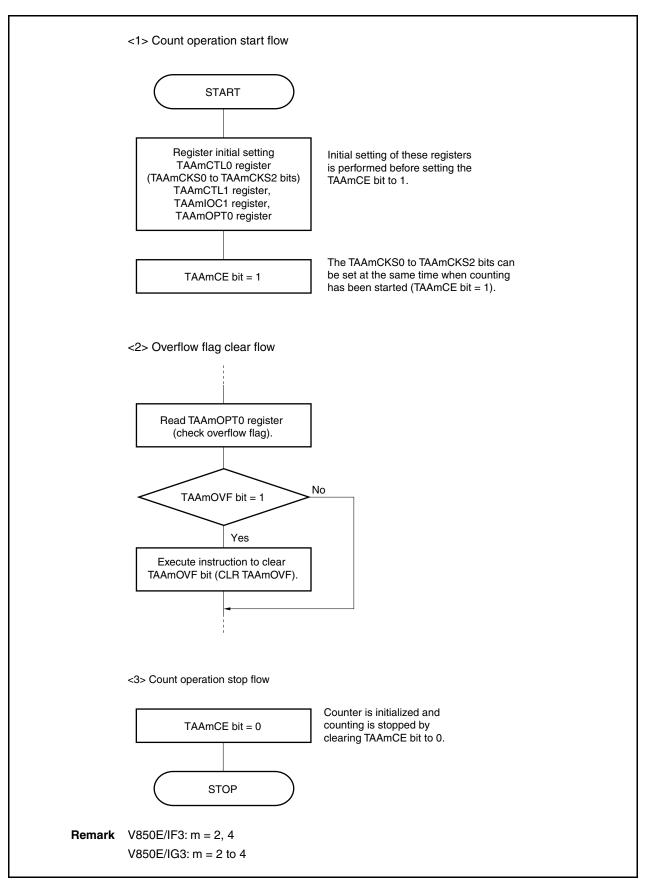

# 7.5 Timer Output Operations

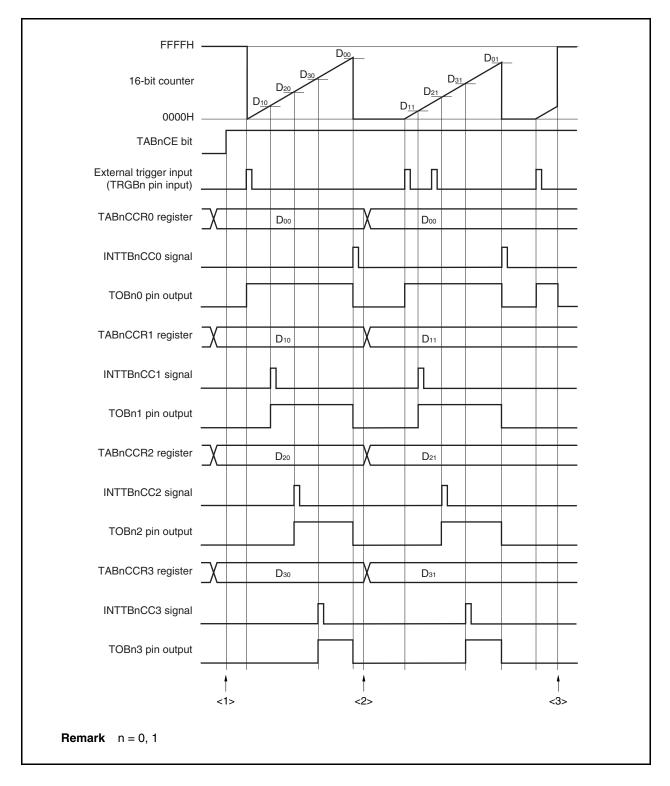

The following table shows the operations and output levels of the TOBn0 to TOBn3 pins.

| Operation Mode                     | TOBn0 Pin                                       | TOBn1 Pin                | TOBn2 Pin                     | TOBn3 Pin                     |  |  |

|------------------------------------|-------------------------------------------------|--------------------------|-------------------------------|-------------------------------|--|--|

| Interval timer mode                | PWM output                                      |                          |                               |                               |  |  |

| External event count mode          | None                                            |                          |                               |                               |  |  |

| External trigger pulse output mode | al trigger pulse output PWM output 6            |                          | External trigger pulse output | External trigger pulse output |  |  |

| One-shot pulse output mode         |                                                 | One-shot pulse<br>output | One-shot pulse<br>output      | One-shot pulse<br>output      |  |  |

| PWM output mode                    |                                                 | PWM output               | PWM output                    | PWM output                    |  |  |

| Free-running timer mode            | PWM output (only when compare function is used) |                          |                               |                               |  |  |

| Pulse width measurement mode       | None                                            |                          |                               |                               |  |  |

# Table 7-6. Timer Output Control in Each Mode

## **Remark** n = 0, 1

## Table 7-7. Truth Table of TOBn0 to TOBn3 Pins Under Control of Timer Output Control Bits

| TABnIOC0.TABnOLa Bit | TABnIOC0.TABnOEa Bit | TABnCTL0.TABnCE bit | Level of TOBna Pin                                                          |

|----------------------|----------------------|---------------------|-----------------------------------------------------------------------------|

| 0                    | 0                    | ×                   | Low-level output                                                            |

|                      | 1                    | 0                   | Low-level output                                                            |

|                      |                      | 1                   | Low level immediately before counting, high level after counting is started |

| 1                    | 0                    | ×                   | High-level output                                                           |

|                      | 1                    | 0                   | High-level output                                                           |

|                      |                      | 1                   | High level immediately before counting, low level after counting is started |

**Remark** n = 0, 1

a = 0 to 3

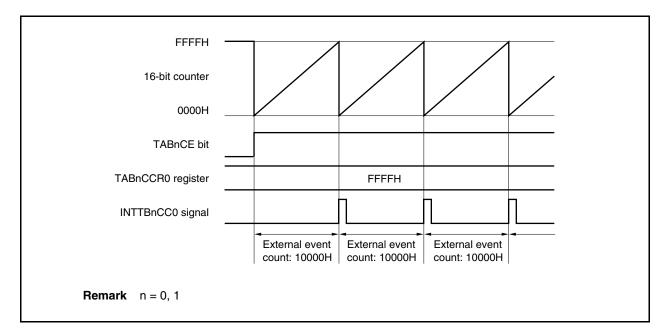

# (b) Operation if TABnCCR0 register is set to FFFFH

If the TABnCCR0 register is set to FFFFH, the 16-bit counter counts to FFFFH each time the valid edge of the external event count signal has been detected. The 16-bit counter is cleared to 0000H in synchronization with the next count-up timing, and the INTTBnCC0 signal is generated. At this time, the TABnOPT0.TABnOVF bit is not set.

## (1) Operation flow in one-shot pulse output mode

Figure 7-27. Software Processing Flow in One-Shot Pulse Output Mode (1/2)

## (e) Generation timing of compare match interrupt request signal (INTTTEQCm1)

The timing of generation of the INTTTEQCm1 signal in the external trigger pulse output mode differs from the timing of INTTTEQCm1 signals in other mode; the INTTTEQCm1 signal is generated when the count value of the 16-bit counter matches the value of the TTmCCR1 register.

| Count clock              |                                |                      |

|--------------------------|--------------------------------|----------------------|

| 16-bit counter           | D1-2 D1-1                      | D1 D1 + 1 D1 + 2     |

| TTmCCR1 register         |                                | D1                   |

| TOTm1 pin output         |                                | Note                 |

| INTTTEQCm1 signal        |                                | Note                 |

| <b>Note</b> The timing i | is actually delayed by one ope | erating clock (fxx). |

| Remark V850E/I           | F3: m = 1                      |                      |

| V850E/I                  | G3: m = 0, 1                   |                      |

Usually, the INTTTEQCm1 signal is generated in synchronization with the next count-up, after the count value of the 16-bit counter matches the value of the TTmCCR1 register.

In the external trigger pulse output mode, however, it is generated one clock earlier. This is because the timing is changed to match the timing of changing the output signal of the TOTm1 pin.

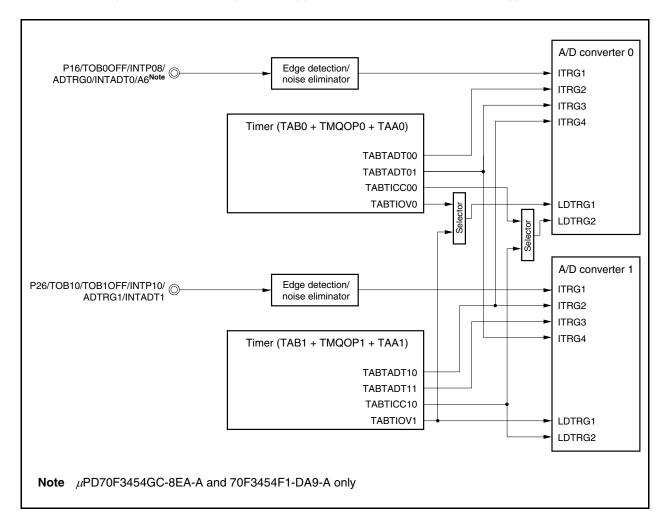

Figure 12-6. Block Diagram of Trigger Source Selector in Hardware Trigger Mode

### (6) A/D converter n trigger select register (ADnTSEL)

The ADnTSEL register is a register that specifies trigger in the hardware trigger mode and conversion channel specification mode, and trigger (selection trigger 1, selection trigger 2, selection load trigger 1, and selection load trigger 2) in the extension buffer mode.

This register can be read or written in 8-bit or 1-bit units.

Reset sets this register to 10H.

|                       | 7                   | 6           | 5                               | 4                                                                  | 3                             | 2         | 1               | 0               |

|-----------------------|---------------------|-------------|---------------------------------|--------------------------------------------------------------------|-------------------------------|-----------|-----------------|-----------------|

| ADnTSEL<br>(n = 0, 1) | ADn Note<br>LDTSEL2 | 0           | ADn <sup>Note</sup><br>TRGSEL21 | ADn Note<br>TRGSEL20                                               | ADn <sup>№te</sup><br>LDTSEL1 | 0         | ADn<br>TRGSEL11 | ADn<br>TRGSEL10 |

|                       |                     |             |                                 |                                                                    |                               |           |                 |                 |

|                       | ADnLDTSEL2          | Specificat  | ion of seled                    | ction load tr                                                      | igger 2 for                   | ADnECR3   | , ADnECR        | 4 registers     |

|                       | 0                   | LDTRG1      |                                 |                                                                    |                               |           |                 |                 |

|                       | 1                   | LDTRG2      |                                 |                                                                    |                               |           |                 |                 |

|                       |                     |             |                                 |                                                                    |                               |           |                 |                 |

|                       | ADnTRGSEL21         | ADnTRGSEL20 | Specificatio                    | on of selectic                                                     | on trigger 2 f                | or ADnECF | R3, ADnECF      | R4 registers    |

|                       | 0                   | 0           | ITRG1                           |                                                                    |                               |           |                 |                 |

|                       | 0                   | 1           | ITRG2                           |                                                                    |                               |           |                 |                 |

|                       | 1                   | 0           | ITRG3                           |                                                                    |                               |           |                 |                 |

|                       | 1                   | 1           | ITRG4                           |                                                                    |                               |           |                 |                 |

|                       |                     |             |                                 |                                                                    |                               |           |                 |                 |

|                       | ADnLDTSEL1          | Specificati | on of selec                     | tion load trig                                                     | gger 1 for A                  | DnECR0 t  | o ADnECR        | 2 registers     |

|                       | 0                   | LDTRG1      |                                 |                                                                    |                               |           |                 |                 |

|                       | 1                   | LDTRG2      |                                 |                                                                    |                               |           |                 |                 |

|                       |                     |             |                                 |                                                                    |                               |           |                 |                 |

|                       | ADnTRGSEL11         | ADnTRGSEL10 | Trigger sp<br>In expans         | re trigger mo<br>becification<br>ion buffer mo<br>ion of selection | ode:                          |           |                 |                 |

|                       | 0                   | 0           | ITRG1                           |                                                                    |                               |           |                 |                 |

|                       | 0                   | 1           | ITRG2                           |                                                                    |                               |           |                 |                 |

|                       | 1                   | 0           | ITRG3                           |                                                                    |                               |           |                 |                 |

|                       | 1                   | 1           | ITRG4                           |                                                                    |                               |           |                 |                 |

- **Note** Be sure to set bits 3, 5, and 7 to "0" and set bit 4 to "1" in the hardware trigger mode and conversion channel specification mode.

- Caution Set the ADnTSEL register when the ADnSCM.ADnCE bit = 0 (conversion operation is stopped) (the same value can be written to the register when the ADnCE bit = 1 (conversion operation is enabled)).

# (17) Comparator n control register 0 (CMPnCTL0)

The CMPnCTL0 register is a register that controls the operation of the overvoltage detection comparator. This register can be read or written in 8-bit units.

Reset sets this register to 00H.

|          | 7              | 6                             | 5             | 4                            | 3          | 2              | 1             | 0             |  |  |

|----------|----------------|-------------------------------|---------------|------------------------------|------------|----------------|---------------|---------------|--|--|

| CMP0CTL0 | 0              | 0                             | 0             | CMP0FEN                      | 0          | 0              | 0             | CMPOLEN       |  |  |

|          |                |                               |               |                              |            |                |               |               |  |  |

|          | CMP0FEN        |                               |               |                              |            |                |               |               |  |  |

|          | 0              | Operation disabled (not used) |               |                              |            |                |               |               |  |  |

|          | 1              | Operation                     | n enabled     | (used)                       |            |                |               |               |  |  |

|          | <b>CMP0LEN</b> | Oper                          | ation conti   | rol of compara               | ator 0 (lo | w range) fo    | or A/D con    | verter 0      |  |  |

|          | 0              | Operatio                      | n disabled    | (not used)                   |            |                |               |               |  |  |

|          | 1              | Operatio                      | n enabled     | (used)                       |            |                |               |               |  |  |

| CMP1CTL0 | 7              | 6<br>CMP12FEN                 | 5<br>CMP11FEN | 4<br>CMP10FEN                | 3<br>0     | 2<br>CMP12LEN  | 1<br>CMP11LEN | 0<br>CMP10LEN |  |  |

|          |                |                               |               |                              |            |                |               |               |  |  |

|          | CMP12FEN<br>0  | •                             |               | rol of compara<br>(not used) | ator 2 (fu | III range) for | r A/D conv    | erter 1       |  |  |

|          | 1              |                               | n enabled     |                              |            |                |               |               |  |  |

|          |                | Operation                     | renableu      | (useu)                       |            |                |               |               |  |  |

|          | CMP11FEN       | Oper                          | ation conti   | rol of compara               | ator 1 (fu | II range) fo   | r A/D conv    | verter 1      |  |  |

|          | 0              | Operation                     | n disabled    | (not used)                   |            |                |               |               |  |  |

|          | 1              | Operation                     | n enabled     | (used)                       |            |                |               |               |  |  |

|          | CMP10FEN       | Oper                          | ation cont    | rol of compara               | ator 0 (fu | Ill range) fo  | r A/D conv    | verter 1      |  |  |

|          | 0              | Operatio                      | n disabled    | (not used)                   |            |                |               |               |  |  |

|          | 1              | Operation                     | n enabled     | (used)                       |            |                |               |               |  |  |

|          | CMP12LEN       | Oper                          | ation contr   | ol of compara                | ator 2 (lo | w range) fo    | or A/D conv   | verter 1      |  |  |

|          | 0              | Operatio                      | n disabled    | (not used)                   |            |                |               |               |  |  |

|          | 1              | Operation                     | n enabled     | (used)                       |            |                |               |               |  |  |

|          | CMP11LEN       | Oper                          | ation contr   | ol of compara                | ator 1 (lo | w range) fo    |               | verter 1      |  |  |

|          | 0              |                               |               | (not used)                   |            | w runge/ io    |               |               |  |  |

|          | 1              |                               | n enabled     |                              |            |                |               |               |  |  |

|          |                |                               |               | (/                           |            |                |               |               |  |  |

|          | CMP10LEN       | Oper                          | ation conti   | rol of compara               | ator 0 (Ic | w range) fo    | or A/D con    | verter 1      |  |  |

|          | 0              |                               |               | (not used)                   |            |                |               |               |  |  |

(1/2)

Therefore, the maximum baud rate that can be received at the transfer destination is as follows.

$$\mathsf{BRmax} = (\mathsf{FLmin}/11)^{-1} = \frac{22k}{21k+2}$$

Brate

Similarly, the maximum allowable value can be obtained as follows.

$$\frac{10}{11} \times FLmax = 11 \times FL - \frac{k+2}{2 \times k} \times FL = \frac{21k-2}{2 \times k} FL$$

$$FLmax = \frac{21k-2}{20k} FL \times 11$$

Therefore, the minimum baud rate that can be received at the transfer destination is as follows.

$$\mathsf{BRmin} = (\mathsf{FLmax}/11)^{-1} = \frac{20k}{21k-2} \mathsf{Brate}$$

The allowable baud rate error of UARTB and the transfer destination can be obtained as follows from the expressions described above for computing the minimum and maximum baud rate values.

| Division Ratio (k) | Maximum Allowable Baud Rate Error | Minimum Allowable Baud Rate Error |

|--------------------|-----------------------------------|-----------------------------------|

| 4                  | +2.33 %                           | -2.44                             |

| 8                  | +3.53 %                           | -3.61                             |

| 16                 | +4.14 %                           | -4.19                             |

| 32                 | +4.45 %                           | -4.48                             |

| 64                 | +4.61 %                           | -4.62                             |

| 128                | +4.68 %                           | -4.69                             |

| 256                | +4.72 %                           | -4.73                             |

| 512                | +4.74 %                           | -4.74                             |

| 1024               | +4.75 %                           | -4.75                             |

| 2048               | +4.76 %                           | -4.76                             |

| 4096               | +4.76 %                           | -4.76                             |

| 8192               | +4.76 %                           | -4.76                             |

| 16384              | +4.76 %                           | -4.76                             |

| 32768              | +4.76 %                           | -4.76                             |

| 65535              | +4.76 %                           | -4.76                             |

Table 15-6. Maximum and Minimum Allowable Baud Rate Error

- Remarks 1. The reception precision depends on the number of bits in one frame, the base clock frequency, and the division ratio (k). The higher the base clock frequency and the larger the division ratio (k), the higher the precision.

- 2. k: UBCTL2 set value

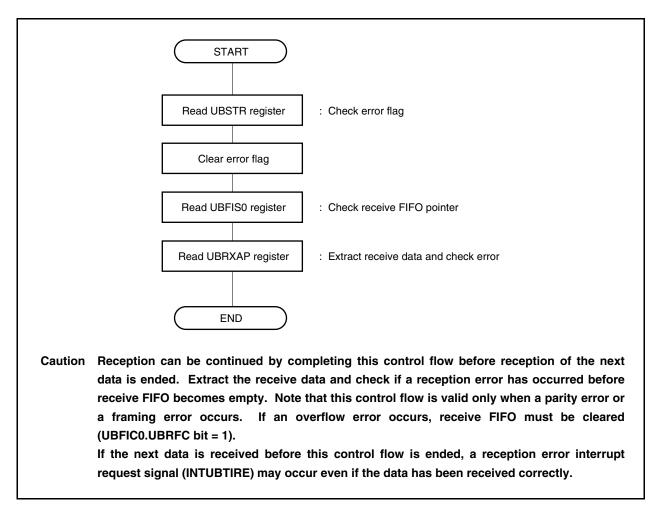

(11) Example of reception error processing flow in FIFO mode (2)

#### 17.6.2 Addresses

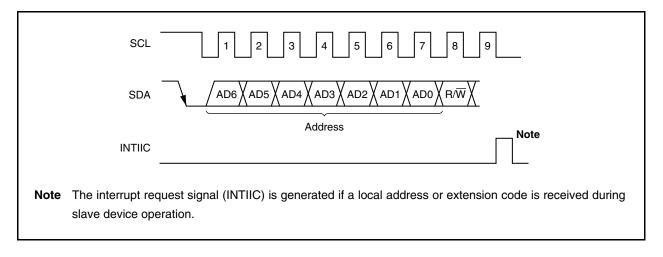

The 7 bits of data that follow the start condition are defined as an address.

An address is a 7-bit data segment that is output in order to select one of the slave devices that are connected to the master device via bus lines. Therefore, each slave device connected via the bus lines must have a unique address.

The slave devices include hardware that detects the start condition and checks whether or not the 7-bit address data matches the data values stored in the SVA0 register. If the address data matches the SVA0 values, the slave device is selected and communicates with the master device until the master device generates a start condition or stop condition.

The slave address and the eighth bit, which specifies the transfer direction as described in **17.6.3** Transfer direction specification below, are together written to the IIC0 register and are then output. Received addresses are written to the IIC0 register.

The slave address is assigned to the higher 7 bits of the IIC0 register.

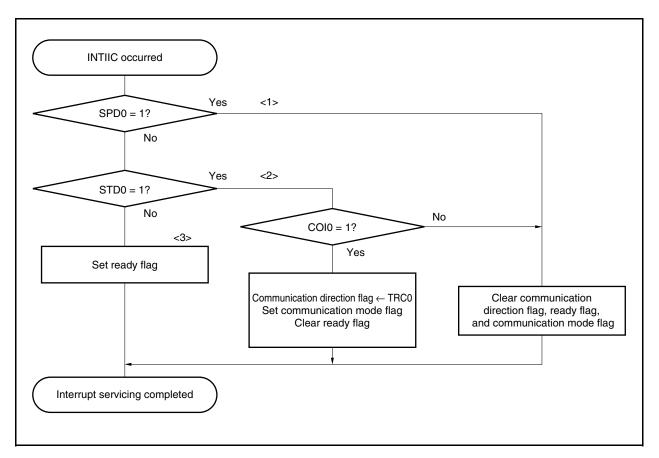

The following shows an example of the processing of the slave device by an INTIIC interrupt (it is assumed that no extension codes are used here). During an INTIIC interrupt, the status is confirmed and the following steps are executed.

- <1> When a stop condition is detected, communication is terminated.

- <2> When a start condition is detected, the address is confirmed. If the address does not match, communication is terminated. If the address matches, the communication mode is set and wait is released, and operation returns from the interrupt (the ready flag is cleared).

- <3> For data transmission/reception, when the ready flag is set, operation returns from the interrupt while the I<sup>2</sup>C bus remains in the wait status.

Remark <1> to <3> in the above correspond to <1> to <3> in Figure 17-20 Slave Operation Flowchart (2).

Figure 17-20. Slave Operation Flowchart (2)

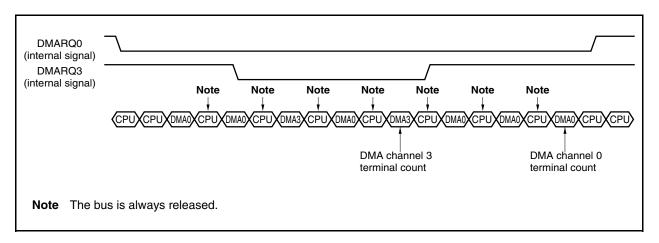

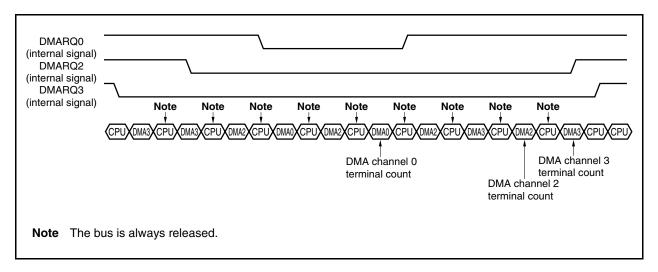

Figure 19-3 is an example of single transfer where a DMA transfer request with a lower priority is issued one clock after single transfer has been completed. DMA channels 0 and 3 are used for single transfer. If two DMA transfer request signals become active at the same time, two DMA transfer operations are alternately executed.

Figure 19-4 is an example of single transfer where two or more DMA transfer requests with a lower priority are issued one clock after single transfer has been completed. DMA channels 0, 2, and 3 are used for single transfer. If three or more DMA transfer request signals become active at the same time, two DMA transfer operations are alternately executed, starting from the one with the highest priority.

# CHAPTER 26 ON-CHIP DEBUG FUNCTION

The on-chip debug function of the V850E/IF3 and V850E/IG3 can be realized in the following two ways.

- Debugging using DCU (debug control unit) (using MINICUBE) By using the DRST, DCK, DMS, DDI, and DDO pins as debug interface pins, on-chip debugging is realized by the internal DCU of the V850E/IG3<sup>Note</sup>.

- Debugging without using DCU (using MINICUBE2) On-chip debugging is realized by MINICUBE2 without using the DCU but by using the user resources.

Note The V850E/IF3 does not have an internal DCU.

The following table shows the features of the two on-chip debug functions.

|                                                              |                   | Debugging Using DCU            | Debugging Without Using DCU                                                                                          |  |  |

|--------------------------------------------------------------|-------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------|--|--|

| Target product                                               |                   | V850E/IG3                      | V850E/IF3, V850E/IG3                                                                                                 |  |  |

| Debug interface pins                                         |                   | DRST, DCK, DMS, DDI, DDO       | <ul> <li>When UARTA0 is used<br/>RXDA0, TXDA0</li> <li>When CSIB0 is used<br/>SIB0, SOB0, SCKB0, HS (P43)</li> </ul> |  |  |

| Securing of user                                             | resources         | Not required                   | Required                                                                                                             |  |  |

| Hardware break                                               | function          | 2 points                       | 2 points (V850E/IG3 only)                                                                                            |  |  |

| Software break                                               | Internal ROM area | 4 points                       | 4 points                                                                                                             |  |  |

| function                                                     | RAM area          | 2000 points                    | 2000 points                                                                                                          |  |  |

| Real-time RAM monitor function <sup>Note 1</sup>             |                   | Available                      | Available                                                                                                            |  |  |

| Dynamic memory modification (DMM) function <sup>Note 2</sup> |                   | Available                      | Available                                                                                                            |  |  |

| Mask function                                                |                   | Reset, INTWDT, WAITNote 3      | RESET, WAIT <sup>Note 3</sup>                                                                                        |  |  |

| ROM security function                                        |                   | 10-byte ID code authentication | 10-byte ID code authentication                                                                                       |  |  |

| Hardware used                                                |                   | MINICUBE                       | MINICUBE2                                                                                                            |  |  |

| Trace function                                               |                   | Not supported                  | Not supported                                                                                                        |  |  |

| Debug interrupt interface function<br>(DBINT)                |                   | Not supported                  | Not supported                                                                                                        |  |  |

## Table 26-1. On-Chip Debug Function Features

**Notes 1.** This is a function which reads out memory contents during program execution.

- 2. This is a function which rewrites RAM contents during program execution.

- **3.** μPD70F3454GC-8EA-A and 70F3454F1-DA9-A only

## 27.9.2 Features

## (1) Flash memory self programming

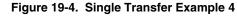

Flash memory self programming is used to erase or write the flash memory by calling the flash function from a program stored in an area other than the flash memory area to be erased or written. To store the program that implements self programming in the area to be erased or written, copy the program to the internal RAM area, execute the program at the copy destination, and call the flash function.

To call the flash function, change the mode from the normal operation mode to the self programming mode by using the flash programming mode control register.

### Figure 27-3. Self Programming

## (a) Boot swap cluster

The contents of the boot swap cluster of the lower address side (00000H to 0FFFFH) and the boot swap cluster of the higher address side (10000H to 1FFFFH) can be interchanged while flash memory programming is performed.

### (b) Boot block cluster

By specifying the boot block cluster from 00000H in 2 KB units, the contents of the boot block cluster can be protected from rewriting.