# E·X Renesas Electronics America Inc - <u>UPD70F3454F1(R)-DA9-A Datasheet</u>

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                                   |

|----------------------------|---------------------------------------------------------------------------------------|

| Core Processor             | V850ES                                                                                |

| Core Size                  | 32-Bit Single-Core                                                                    |

| Speed                      | 64MHz                                                                                 |

| Connectivity               | CSI, EBI/EMI, I <sup>2</sup> C, UART/USART                                            |

| Peripherals                | DMA, LVD, PWM, WDT                                                                    |

| Number of I/O              | 64                                                                                    |

| Program Memory Size        | 256KB (256K x 8)                                                                      |

| Program Memory Type        | FLASH                                                                                 |

| EEPROM Size                | -                                                                                     |

| RAM Size                   | 12K x 8                                                                               |

| Voltage - Supply (Vcc/Vdd) | 3.5V ~ 5.5V                                                                           |

| Data Converters            | A/D 10x12b, 8x10b                                                                     |

| Oscillator Type            | External                                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                     |

| Mounting Type              | Surface Mount                                                                         |

| Package / Case             | 161-LFBGA                                                                             |

| Supplier Device Package    | -                                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd70f3454f1-r-da9-a |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.2.2 Application fields (V850E/IF3)

- Consumer equipment (such as inverter air conditioners, washing machines, driers, refrigerators, etc.)

- Industrial equipment (such as motor control, general-purpose inverters, etc.)

#### 1.2.3 Ordering information (V850E/IF3)

| Part Number             | Package                              | Internal ROM          |

|-------------------------|--------------------------------------|-----------------------|

| μPD70F3451GC-UBT-A      | 80-pin plastic LQFP (14 $\times$ 14) | Flash memory (128 KB) |

| $\mu$ PD70F3452GC-UBT-A | 80-pin plastic LQFP (14 $\times$ 14) | Flash memory (256 KB) |

**Remark** The V850E/IF3 microcontrollers are lead-free products.

(d) Port 0 function control register (PFC0)

| After res                                                                                                                                | et: 00H               | R/W                   | Address: F            | FFFF460H              | ł                     |                       |       |       |  |

|------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-------|-------|--|

|                                                                                                                                          | 7                     | 6                     | 5                     | 4                     | 3                     | 2                     | 1     | 0     |  |

| PFC0                                                                                                                                     | PFC07 <sup>Note</sup> | PFC06 <sup>Note</sup> | PFC05 <sup>Note</sup> | PFC04 <sup>Note</sup> | PFC03 <sup>Note</sup> | PFC02 <sup>Note</sup> | PFC01 | PFC00 |  |

| Note Valid only in the V850E/IG3.<br>With the V850E/IF3, be sure to set these bits to 0.                                                 |                       |                       |                       |                       |                       |                       |       |       |  |

| <b>Remark</b> For the specifications of alternate functions, see <b>4.3.1 (1) (f)</b> Settings of alternate functions of port <b>0</b> . |                       |                       |                       |                       |                       |                       |       |       |  |

# (e) Port 0 function control expansion register (PFCE0)

| After res                                                                                                                                                                                                                                                                                                                                                                                                                                      | et: 00H | R/W                    | Address: F             | FFFF700F               | 1                      |                        |        |        |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------------------|------------------------|------------------------|------------------------|------------------------|--------|--------|--|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7       | 6                      | 5                      | 4                      | 3                      | 2                      | 1      | 0      |  |  |

| PFCE0                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0       | PFCE06 <sup>Note</sup> | PFCE05 <sup>Note</sup> | PFCE04 <sup>Note</sup> | PFCE03 <sup>Note</sup> | PFCE02 <sup>Note</sup> | PFCE01 | PFCE00 |  |  |

| PFCE0       0       PFCE06 <sup>Note</sup> PFCE03 <sup>Note</sup> PFCE03 <sup>Note</sup> PFCE02 <sup>Note</sup> PFCE01       PFCE00         Note       Valid only in the V850E/IG3.       With the V850E/IF3, be sure to set these bits to 0.       With the V850E/IF3, be sure to set these bits to 0.         Remark       For the specifications of alternate functions, see 4.3.1 (1) (f)       Settings of alternate functions of port 0. |         |                        |                        |                        |                        |                        |        |        |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |                        |                        |                        |                        | ,g                     |        |        |  |  |

# (e) Interrupt operation

TAAn generates the following three types of interrupt request signals.

- INTTAnCC0 interrupt: This signal functions as a match interrupt request signal of the CCR0 buffer register and as a capture interrupt request signal to the TAAnCCR0 register.

- INTTAnCC1 interrupt: This signal functions as a match interrupt request signal of the CCR1 buffer

- register and as a capture interrupt request signal to the TAAnCCR1 register.

- INTTAnOV interrupt: This signal functions as an overflow interrupt request signal.

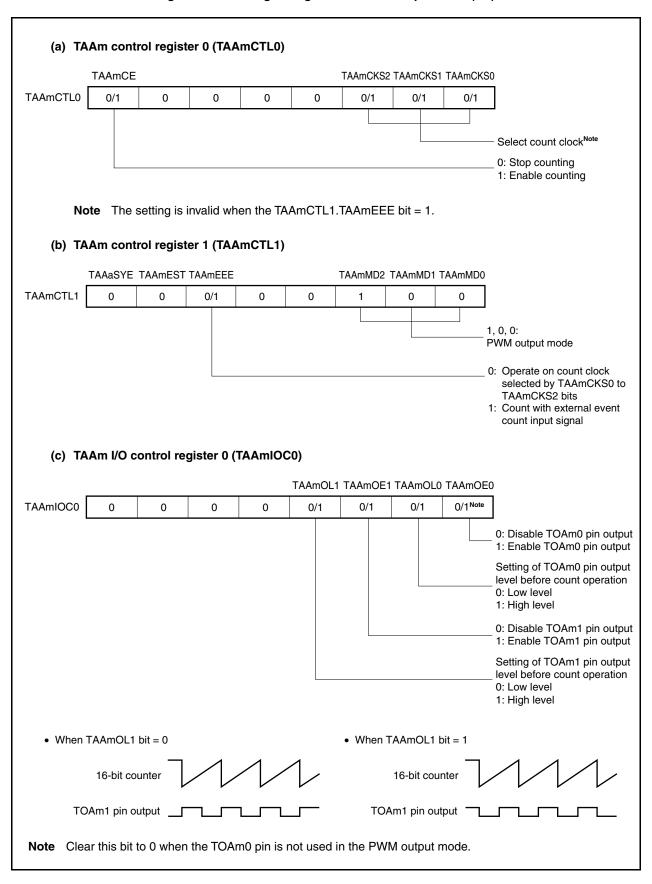

Figure 6-34. Setting of Registers in PWM Output Mode (1/2)

#### (a) Function as compare register

The TABnCCR0 register can be rewritten even when the TABnCTL0.TABnCE bit = 1.

The set value of the TABnCCR0 register is transferred to the CCR0 buffer register. When the value of the 16-bit counter matches the value of the CCR0 buffer register, a compare match interrupt request signal (INTTBnCC0) is generated. If TOBn0 pin output is enabled at this time, the output of the TOBn0 pin is inverted.

When the TABnCCR0 register is used as a cycle register in the interval timer mode, external event count mode, external trigger pulse output mode, one-shot pulse output mode, or PWM output mode, the value of the 16-bit counter is cleared (0000H) if its count value matches the value of the CCR0 buffer register. The compare register is not cleared by setting the TABnCTL0.TABnCE bit to 0.

#### (b) Function as capture register

When the TABnCCR0 register is used as a capture register in the free-running timer mode, the count value of the 16-bit counter is stored in the TABnCCR0 register if the valid edge of the capture trigger input pin (TIBn0 pin) is detected. In the pulse-width measurement mode, the count value of the 16-bit counter is stored in the TABnCCR0 register and the 16-bit counter is cleared (0000H) if the valid edge of the capture trigger input pin (TIBn0 pin) is detected.

Even if the capture operation and reading the TABnCCR0 register conflict, the correct value of the TABnCCR0 register can be read.

The capture register is cleared by setting the TABnCTL0.TABnCE bit = 0.

The following table shows the functions of the capture/compare register in each mode, and how to write data to the compare register.

| Operation Mode                | Capture/Compare Register | How to Write Compare Register |

|-------------------------------|--------------------------|-------------------------------|

| Interval timer                | Compare register         | Anytime write                 |

| External event counter        | Compare register         | Anytime write                 |

| External trigger pulse output | Compare register         | Batch write <sup>Note</sup>   |

| One-shot pulse output         | Compare register         | Anytime write                 |

| PWM output                    | Compare register         | Batch write <sup>Note</sup>   |

| Free-running timer            | Capture/compare register | Anytime write                 |

| Pulse width measurement       | Capture register         | None                          |

#### Table 7-2. Function of Capture/Compare Register in Each Mode and How to Write Compare Register

Note Writing to the TABnCCR1 register is the trigger.

Remark For anytime write and batch write, see 7.6 (2) Anytime write and batch write.

#### Figure 7-15. Register Setting for Operation in External Event Count Mode (2/2)

#### (f) TABn capture/compare registers 1 to 3 (TABnCCR1 to TABnCCR3)

The TABnCCR1 to TABnCCR3 registers are not used in the external event count mode. However, the set value of the TABnCCR1 to TABnCCR3 registers are transferred to the CCR1 to CCR3 buffer registers. When the count value of the 16-bit counter matches the value of the CCR1 to CCR3 buffer registers, compare match interrupt request signals (INTTBnCC1 to INTTBnCC3) are generated. When the TABnCCR1 to TABnCCR3 registers are not used, it is recommended to set their values to FFFFH. Also mask the registers by the interrupt mask flags (TABnCCIC1.TABnCCMK1 to TABnCCIC3.TABnCCMK3).

#### Caution Set the TABnIOC0 register to 00H.

**Remarks 1.** TABn I/O control register 1 (TABnIOC1) and TABn option register 0 (TABnOPT0) are not used in the external event count mode.

**2.** n = 0, 1

#### Figure 8-9. Register Setting for Interval Timer Mode Operation (2/2)

```

(d) TMTn counter read buffer register (TTnCNT)

By reading the TTnCNT register, the count value of the 16-bit counter can be read.

(e) TMTn capture/compare register 0 (TTnCCR0)

If the TTnCCR0 register is set to D<sub>0</sub>, the interval is as follows.

Interval = (D_0 + 1) \times Count clock cycle

(f) TMTn capture/compare register 1 (TTnCCR1)

The TTnCCR1 register is not used in the interval timer mode. However, the set value of the TTnCCR1

register is transferred to the CCR1 buffer register. When the count value of the 16-bit counter matches

the value of the CCR1 buffer register, the TOTm1 pin output is inverted and a compare match interrupt

request signal (INTTTEQCn1) is generated.

By setting this register to the same value as the value set in the TTnCCR0 register, a PWM waveform

with a duty factor of 50% can be output from the TOTm1 pin.

When the TTnCCR1 register is not used, it is recommended to set its value to FFFFH. Also mask the

register by the interrupt mask flag (TTnCCIC1.TTnCCMK1).

Remarks 1. TMTm control register 2 (TTmCTL2), TMTm I/O control register 1 (TTmIOC1), TMTm I/O

control register 2 (TTmIOC2), TMTm I/O control register 3 (TTmIOC3), TMTn option

register 0 (TTnOPT0), TMTm option register 1 (TTmOPT1), TMTm capture input select

register (TTISLm), and TMTm counter write register (TTmTCW) are not used in the

interval timer mode.

2. V850E/IF3: m = 1, n = 0, 1

V850E/IG3: m = 0, 1, n = 0, 1

```

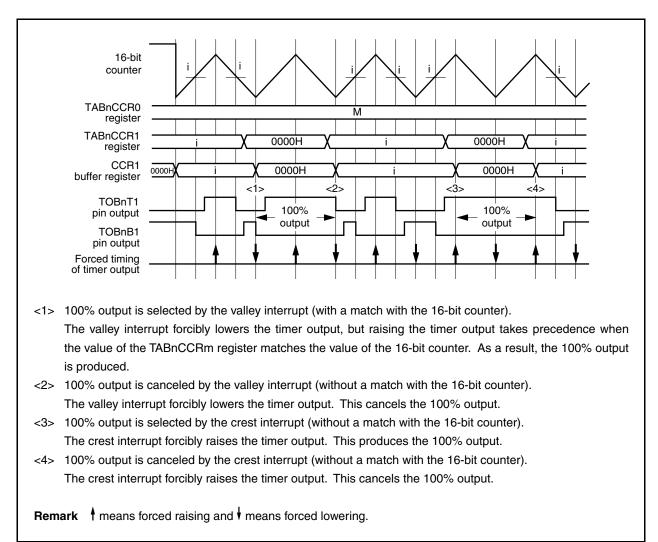

Figure 10-10. 100% PWM Output Waveform (With Dead Time)

| Selection trigger 1                                                                                        | ſ        | (7)        | (12)      | (18)      |          |           | (33)        |           |

|------------------------------------------------------------------------------------------------------------|----------|------------|-----------|-----------|----------|-----------|-------------|-----------|

| Selection trigger 2                                                                                        | (2)      |            |           |           |          | (27)      |             |           |

| Selection load trigger 1                                                                                   |          |            |           |           | (24)     |           |             |           |

| Selection load trigger 2                                                                                   |          |            |           |           |          |           |             | (39)      |

| Analog input pin selection                                                                                 | ANIO2    |            |           | AN        | 100      |           | ANI05       |           |

| AD0TRGCH12 to AD0TRGCH10 bits                                                                              |          | 8)         | (·        | 19)       |          |           |             | $\square$ |

| AD0TRGCH16 to AD0TRGCH14 bits                                                                              | ANI05    | ·····(1    | 3)        |           |          |           | (34)        | $\square$ |

| AD0TRGCH22 to AD0TRGCH20 bits                                                                              | (3)ANI02 |            |           |           |          |           |             | $\square$ |

| AD0TRGCH26 to AD0TRGCH24 bits                                                                              | ANI03    |            |           |           |          | (28)      |             | $\square$ |

| A/D conversion result signals 11 to 0                                                                      |          |            |           | X _       | R3       |           | <b>Ж</b> 85 |           |

| Buffer register 0                                                                                          |          | (9) R1     | (15) F    | 72 (21    | )        | R3 /      | (36         | ) R5      |

| Buffer register 1                                                                                          |          | _X         | (14) F    | R1 X(20   | )        | R2        | X (35       | ) R3      |

| Buffer register 2                                                                                          |          | <u> </u>   | X_        | X(20      | )        | R1        | (35         | ) R2      |

| Buffer register 3                                                                                          | (4)      |            | R         | 0         |          |           | (30) R4     |           |

| Buffer register 4                                                                                          | X        |            |           |           |          |           | (29) R0     |           |

| AD0ECR0 register                                                                                           |          |            |           |           | (25)     |           | R3          |           |

| AD0ECR1 register                                                                                           |          |            |           |           | (25)     |           | R2          |           |

| AD0ECR2 register                                                                                           |          |            |           |           | (25)     |           | R1          |           |

| AD0ECR3 register                                                                                           |          |            |           |           |          |           |             | (40)R4    |

| AD0ECR4 register                                                                                           |          |            |           |           |          |           |             | (40)R0    |

| INTAD0 signal                                                                                              | (6)      | (11)       | (17       | ) (2      | 3)       |           | (32) (3     | 8)        |

| <ul> <li>Remarks 1. Buffer registers 0 to</li> <li>2. R0 to R6: Conversion</li> <li>3. n = 0, 1</li> </ul> |          | sion resul | t extensi | ion buffe | er regis | ters 0 to | 9 4         |           |

# Figure 12-22. Example of Operation in Extension Buffer Mode: A/D Converter 0 (1/2)

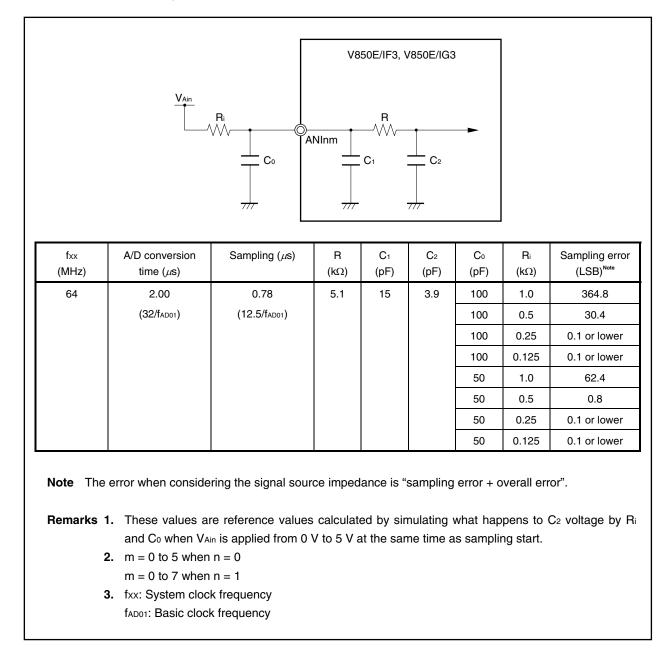

An example of calculating an overall error of A/D converters 0 and 1 is shown below.

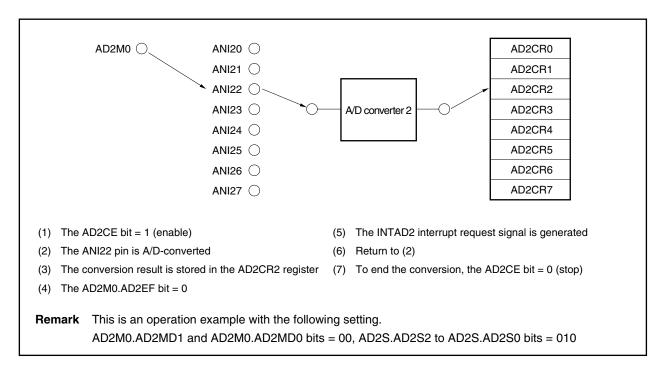

#### 13.5 Operation in Software Trigger Mode

When the AD2M0.AD2CE bit is set to 1, A/D conversion is started.

When A/D conversion is started, the AD2M0.AD2EF bit = 1 (conversion in progress).

If the AD2M0 and AD2S registers are written during A/D conversion, the conversion is stopped and executed again from the beginning.

#### (1) Operation in software trigger continuous select mode

In this mode, one analog input pin (ANI2n) specified by the AD2S register is A/D-converted once. The conversion results are stored in one AD2CRn register. The ANI2n pin and AD2CRn register correspond one to one.

Each time an A/D conversion is executed, an A/D2 conversion end interrupt request signal (INTAD2) is generated and A/D conversion ends. After A/D conversion ends, the conversion is repeated again unless the AD2M0.AD2CE bit is set to 0.

It is not necessary to set (1) the AD2M0.AD2CE bit to restart A/D conversion<sup>Note</sup>.

**Note** In the software trigger continuous select mode, the A/D conversion operation is not stopped unless the AD2M0.AD2CE bit is set to 0. If the AD2CRn register is not read before the next A/D conversion ends, it is overwritten.

This mode is suitable for applications in which the A/D conversion value of one analog input pin is read.

| Analog Input Pin | A/D Conversion Result Register |

|------------------|--------------------------------|

| ANI2n            | AD2CRn                         |

Remark V850E/IF3: n = 0 to 3 V850E/IG3: n = 0 to 7

#### (4) Baud rate

The baud rate is obtained by the following equation.

Baud rate =

$$\frac{f_{UCLK}}{2 \times k}$$

[bps]

Frequency of base clock selected by the UAnCTL1.UAnCKS3 to UAnCTL1.UAnCKS0 bits

k: Value set using the UAnCTL2.UAnBRS7 to UAnCTL2.UAnBRS0 bits (k = 4, 5, 6, ..., 255)

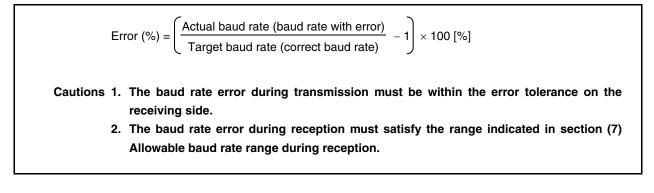

#### (5) Baud rate error

The baud rate error is obtained by the following equation.

```

ExamplePeripheral clock frequency = 32 MHz = 32,000,000 HzSet value of UAnCTL1.UAnCKS3 to UAnCTL1.UAnCKS0 bits = 0000B (fuclk = 16,000,000 Hz)Set value of UAnCTL2.UAnBRS7 to UAnCTL2.UAnBRS0 bits = 00110100B (k = 52)Target baud rate = 153,600

```

Baud rate = 16,000,000/ (2 × 52) = 153,846 [bps]

$\begin{array}{l} {\sf Error} \ = \ (153,846/153,600-1) \times 100 \\ \\ = \ 0.160 \ [\%] \end{array}$

#### (2) UARTB status register (UBSTR)

The UBSTR register indicates the transfer status and reception error contents while UARTB is transmitting data.

The status flag that indicates the transfer status during transmission indicates the data retention status of the transmit shift register and transmit data register (the UBTX register in the single mode or transmit FIFO in the FIFO mode). The status flag that indicates a reception error holds its status until it is cleared to 0. This register can be read or written in 8-bit or 1-bit units.

Reset sets this register to 00H.

# Caution When the UBCTL0.UBPWR bit or UBCTL0.UBRXE bit is set to 0, or when 0 is written to the UBSTR register, the UBSTR.UBOVF, UBSTR.UBPE, UBSTR.UBFE, and UBSTR.UBOVE bits are cleared to 0.

| After re | set: 00H   | R/W                                                                                                                                      | Address: I                                          | FFFFA4      | 4H              |                                           |            |          |  |  |  |

|----------|------------|------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-------------|-----------------|-------------------------------------------|------------|----------|--|--|--|

|          | <7>        | 6                                                                                                                                        | 5                                                   | 4           | 3               | <2>                                       | <1>        | <0>      |  |  |  |

| UBSTR    | UBTSF      | 0                                                                                                                                        | 0                                                   | 0           | UBOVF           | UBPE                                      | UBFE       | UBOVE    |  |  |  |

|          |            |                                                                                                                                          |                                                     |             |                 |                                           |            |          |  |  |  |

|          | UBTSF      | Transfer status flag                                                                                                                     |                                                     |             |                 |                                           |            |          |  |  |  |

|          | 0          | <ul> <li>In sing</li> </ul>                                                                                                              | le mode (U                                          | BFIC0.UE    | MOD bit = $0$   | )                                         |            |          |  |  |  |

|          |            | Data t                                                                                                                                   | o be transfe                                        | rred to the | e transmit shi  | ft register                               | and UBTX   | register |  |  |  |

|          |            |                                                                                                                                          |                                                     | • •         | vhen UBCTL      | 0.UBPWR                                   | bit = 0 or |          |  |  |  |

|          |            |                                                                                                                                          | L0.UBTXE k                                          | ,           |                 |                                           |            |          |  |  |  |

|          |            |                                                                                                                                          | ```                                                 |             | MOD bit = 1)    |                                           |            |          |  |  |  |

|          |            |                                                                                                                                          |                                                     |             | e transmit shi  | •                                         |            | nit FIFO |  |  |  |

|          |            |                                                                                                                                          |                                                     | . ,         | /hen UBCTL      | 0.UBPWR                                   | bit = 0 or |          |  |  |  |

|          | <u> </u>   | UBCTL0.UBTXE bit = 0).                                                                                                                   |                                                     |             |                 |                                           |            |          |  |  |  |

|          | 1          | In single mode (UBFIC0.UBMOD bit = 0)                                                                                                    |                                                     |             |                 |                                           |            |          |  |  |  |

|          |            | Data to be transferred to the transmit shift register or UBTX register                                                                   |                                                     |             |                 |                                           |            |          |  |  |  |

|          |            | exists (transmission in progress).                                                                                                       |                                                     |             |                 |                                           |            |          |  |  |  |

|          |            | <ul> <li>In FIFO mode (UBFIC0.UBMOD bit = 1)</li> <li>Data to be transferred to the transmit shift register and transmit FIFO</li> </ul> |                                                     |             |                 |                                           |            |          |  |  |  |

|          |            |                                                                                                                                          |                                                     |             |                 | it register                               | anu transn |          |  |  |  |

|          | The yellu  |                                                                                                                                          | (transmissic                                        |             | ,               | er two periods of fxx have elapsed, after |            |          |  |  |  |

|          |            |                                                                                                                                          |                                                     |             | register. The   |                                           |            |          |  |  |  |

|          |            |                                                                                                                                          |                                                     |             | data has be     |                                           |            |          |  |  |  |

|          | L          | 0                                                                                                                                        |                                                     |             |                 |                                           |            | 0        |  |  |  |

|          | UBOVF      |                                                                                                                                          |                                                     |             | Overflow fla    | g                                         |            |          |  |  |  |

|          | 0          | Overflow                                                                                                                                 | / did not occ                                       | ur.         |                 |                                           |            |          |  |  |  |

|          | 1          | Overflow                                                                                                                                 | occurred (                                          | during rec  | eption).        |                                           |            |          |  |  |  |

|          | The U      | UBOVF bit is valid only in the FIFO mode (when UBFIC0.UBMOD bit = 1),                                                                    |                                                     |             |                 |                                           |            |          |  |  |  |

|          | and inv    | alid in the                                                                                                                              | lid in the single mode (when UBFIC0.UBMOD bit = 0). |             |                 |                                           |            |          |  |  |  |

|          | • If an ov | verflow oc                                                                                                                               | curs, the rea                                       | ceived dat  | a is not writte | en to recei                               | ve FIFO b  | ut       |  |  |  |

(3/3)

| ACKD0                                             | De                                                                                                                                                                           | Detection of ACK                                                                         |  |  |  |  |  |  |

|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 0                                                 | ACK was not detected.                                                                                                                                                        | ACK was not detected.                                                                    |  |  |  |  |  |  |

| 1                                                 | ACK was detected.                                                                                                                                                            |                                                                                          |  |  |  |  |  |  |

| Condition f                                       | for clearing (ACKD0 bit = 0)                                                                                                                                                 | Condition for setting (ACKD0 bit = 1)                                                    |  |  |  |  |  |  |

| <ul> <li>At the ris</li> <li>Cleared I</li> </ul> | stop condition is detected<br>ing edge of the next byte's first clock<br>by the LREL0 bit = 1 (exit from communications)<br>e IICE0 bit changes from 1 to 0 (operation stop) | After the SDA pin is set to low level at the rising edge of<br>the SCL pin's ninth clock |  |  |  |  |  |  |

| STD0                                                            | Detection of start condition                                                                                                                                                                        |                                      |  |  |  |  |  |

|-----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--|--|--|--|--|

| 0                                                               | Start condition was not detected.                                                                                                                                                                   |                                      |  |  |  |  |  |

| 1                                                               | Start condition was detected. This indicates that the address transfer period is in effect                                                                                                          |                                      |  |  |  |  |  |

| Condition f                                                     | or clearing (STD0 bit = 0)                                                                                                                                                                          | Condition for setting (STD0 bit = 1) |  |  |  |  |  |

| <ul> <li>At the ris<br/>address t</li> <li>Cleared b</li> </ul> | stop condition is detected<br>sing edge of the next byte's first clock following<br>gransfer<br>by the LREL0 bit = 1 (exit from communications)<br>e IICE0 bit changes from 1 to 0 (operation stop) | • When a start condition is detected |  |  |  |  |  |

| SPD0                 | Detection of stop condition                                                                                                                                     |                                      |  |  |  |  |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--|--|--|--|

| 0                    | Stop condition was not detected.                                                                                                                                |                                      |  |  |  |  |

| 1                    | Stop condition was detected. The master device's communication is terminated and the bus is released.                                                           |                                      |  |  |  |  |

| Condition            | for clearing (SPD0 bit = 0)                                                                                                                                     | Condition for setting (SPD0 bit = 1) |  |  |  |  |

| clock foll condition | ising edge of the address transfer byte's first<br>lowing setting of this bit and detection of a start<br>n<br>e IICE0 bit changes from 1 to 0 (operation stop) | When a stop condition is detected    |  |  |  |  |

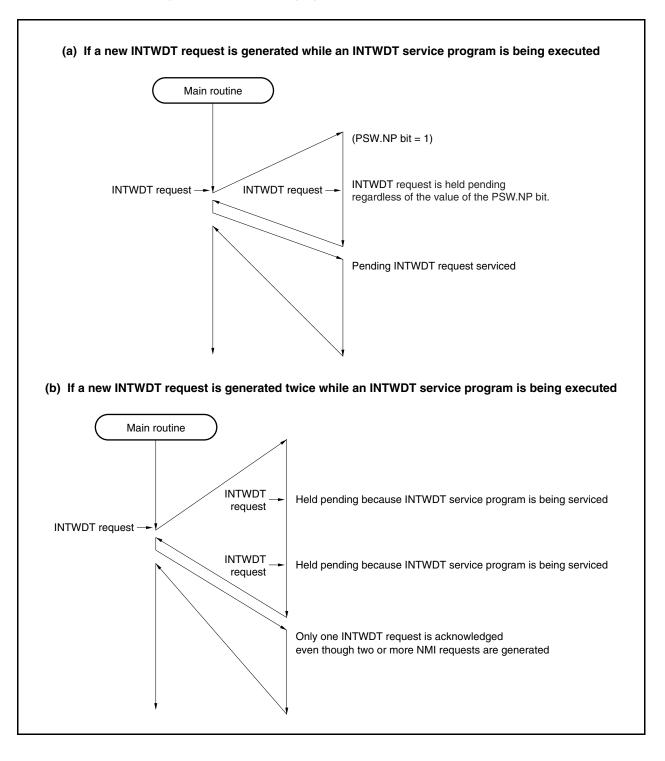

#### Figure 20-2. Acknowledging Non-Maskable Interrupt Request

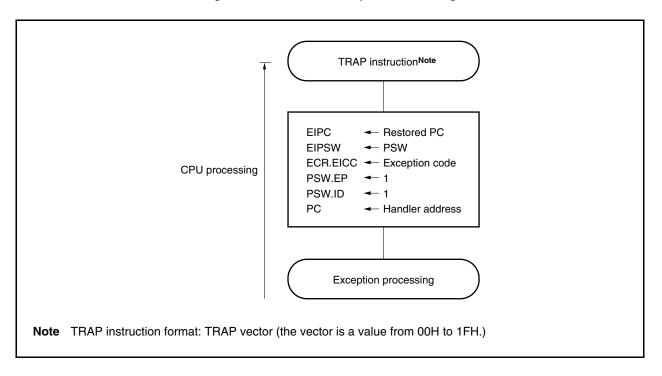

#### 20.5 Software Exception

A software exception is generated when the CPU executes the TRAP instruction, and can always be acknowledged.

#### 20.5.1 Operation

If a software exception occurs, the CPU performs the following processing, and transfers control to the handler routine.

- <1> Saves the restored PC to EIPC.

- <2> Saves the current PSW to EIPSW.

- <3> Writes an exception code to the lower 16 bits (EICC) of ECR (interrupt source).

- <4> Sets the PSW.EP and PSW.ID bits (1).

- <5> Sets the handler address (00000040H or 00000050H) corresponding to the software exception to the PC, and transfers control.

The processing of a software exception is shown below.

#### Figure 20-8. Software Exception Processing

The handler address is determined by the TRAP instruction's operand (vector). If the vector is 00H to 0FH, it becomes 00000040H, and if the vector is 10H to 1FH, it becomes 00000050H.

# 21.2 Control Registers

# (1) Power save control register (PSC)

The PSC register is an 8-bit register that controls the standby function. The STB bit of this register is used to specify the standby mode. This register is a special register (see **3.4.8 Special registers**). This register can be written only by a combination of specific sequences.

This register can be read or written in 8-bit or 1-bit units.

Reset sets this register to 00H.

| After                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | reset: 00H | R/W                                                                                                                                              | Address:    | FFFFF1FE   | EH          |         |     |   |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------|-------------|---------|-----|---|--|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7          | 6                                                                                                                                                | 5           | <4>        | 3           | 2       | <1> | 0 |  |  |

| PSC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0          | 0                                                                                                                                                | 0           | INTM       | 0           | 0       | STB | 0 |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | INTM<br>0  | Standby mode control <sup>Note 2</sup> by maskable interrupt request (INTxx <sup>Note 1</sup> )<br>Standby mode release by INTxx request enabled |             |            |             |         |     |   |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1          | -                                                                                                                                                |             | se by INTX | •           |         |     |   |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | '          | Standby                                                                                                                                          | inode relea | Se by INTA | k request u | ISabled |     |   |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | STB        |                                                                                                                                                  |             | Sets       | operation   | mode    |     |   |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0          | Normal n                                                                                                                                         | node        |            |             |         |     |   |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1          | Standby                                                                                                                                          | mode        |            |             |         |     |   |  |  |

| 1       Standby mode         Notes 1. For details, see Table 20-1 Interrupt Source List.         2. The setting is valid only in the IDLE mode and STOP mode.         Cautions 1. Be sure to set bits 0, 2, 3, and 5 to 7 to "0".         2. Before setting a standby mode by setting the STB bit to 1, be sure to set the PCC register to 03H and then set the STB bit to 1. Otherwise, the standby mode may not be set or released. After releasing the standby mode, change the value of the PCC register to the desired value.         3. To set the IDLE mode or STOP mode, set the PCC register to 03H, and the PSMR.PSM0 bit in that order and then set the STB bit to 1. |            |                                                                                                                                                  |             |            |             |         |     |   |  |  |

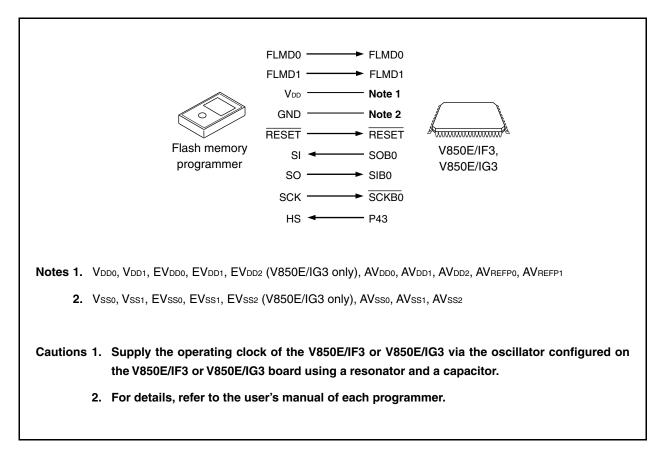

# (3) CSIB0 communication method supporting handshake

Transfer rate: Up to 2.5 Mbps (MSB first)

The flash memory programmer outputs the transfer clock, and the V850E/IF3 or V850E/IG3 operates as a slave. When the PG-FP4 or PG-FP5 is used, it sends the following signals to the V850E/IF3 or V850E/IG3. For details, refer to the **PG-FP4 User's Manual (U15260E)** or **PG-FP5 User's Manual (U18865E)**.

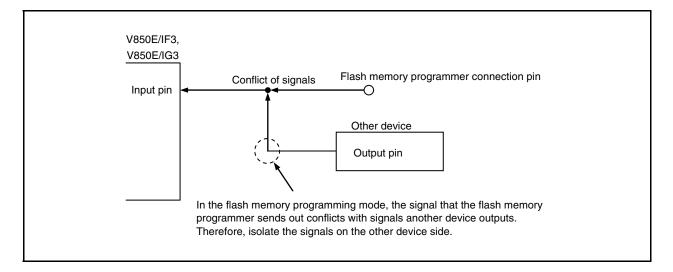

#### (1) Conflict of signals

When the flash memory programmer (output) is connected to an interface pin (input) that is connected to another device (output), a conflict of signals occurs. To avoid the conflict of signals, isolate the connection to the other device or set the other device to the output high-impedance status.

Published by: NEC Electronics Corporation (http://www.necel.com/) Contact: http://www.necel.com/support/