## E. Renesas Electronics America Inc - UPD78F0431GB-GAG-AX Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detalls                    |                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------|

| Product Status             | Active                                                                               |

| Core Processor             | 78K/0                                                                                |

| Core Size                  | 8-Bit                                                                                |

| Speed                      | 10MHz                                                                                |

| Connectivity               | 3-Wire SIO, LINbus, UART/USART                                                       |

| Peripherals                | LCD, LVD, POR, PWM, WDT                                                              |

| Number of I/O              | 34                                                                                   |

| Program Memory Size        | 16KB (16K x 8)                                                                       |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 768 x 8                                                                              |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                          |

| Data Converters            | A/D 6x10b                                                                            |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 52-LQFP                                                                              |

| Supplier Device Package    | -                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f0431gb-gag-ax |

|                            |                                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Address      | Special Function Register (SFR) Name               | Symbol | R/W | Mani         |              |              | After |

|--------------|----------------------------------------------------|--------|-----|--------------|--------------|--------------|-------|

|              |                                                    |        |     | 1 Bit        | 8 Bits       | 16 Bits      | Reset |

| FF00H        | Receive buffer register 6                          | RXB6   | R   | _            |              | _            | FFH   |

| FF01H        | Port register 1                                    | P1     | R/W |              |              | -            | 00H   |

| FF02H        | Port register 2                                    | P2     | R/W | $\checkmark$ | $\checkmark$ | -            | 00H   |

| FF03H        | Port register 3                                    | P3     | R/W | $\checkmark$ | $\checkmark$ | -            | 00H   |

| FF04H        | Port register 4                                    | P4     | R/W | $\checkmark$ | $\checkmark$ | -            | 00H   |

| FF05H        | Transmit buffer register 6                         | TXB6   | R/W | _            | $\checkmark$ | -            | FFH   |

| FF06H        | A/D conversion result register <sup>Note</sup>     | ADCR   | R   | _            | _            | $\checkmark$ | 0000H |

| FF07H        | A/D conversion result register (H) <sup>Note</sup> | ADCRH  | R   | _            | $\checkmark$ | _            | 00H   |

| FF08H        | Port register 8                                    | P8     | R/W | $\checkmark$ | $\checkmark$ | -            | 00H   |

| FF0AH        | Port register 10                                   | P10    | R/W | $\checkmark$ | $\checkmark$ | -            | 00H   |

| <b>FF0BH</b> | Port register 11                                   | P11    | R/W | $\checkmark$ | $\checkmark$ | -            | 00H   |

| FF0CH        | Port register 12                                   | P12    | R/W | $\checkmark$ | $\checkmark$ | -            | 00H   |

| FF0EH        | Port register 14                                   | P14    | R/W | $\checkmark$ | $\checkmark$ | -            | 00H   |

| <b>FF0FH</b> | Port register 15                                   | P15    | R/W | $\checkmark$ | $\checkmark$ | -            | 00H   |

| FF10H        | 16-bit timer counter 00                            | ТМ00   | R   | _            | -            | $\checkmark$ | 0000H |

| FF11H        |                                                    |        |     |              |              |              |       |

| FF12H        | 16-bit timer capture/compare register 000          | CR000  | R/W | -            | -            |              | 0000H |

| FF13H        |                                                    |        |     |              |              |              |       |

| FF14H        | 16-bit timer capture/compare register 010          | CR010  | R/W | _            | -            |              | 0000H |

| FF15H        |                                                    |        |     |              |              |              |       |

| FF16H        | 8-bit timer counter 50                             | TM50   | R   | _            | $\checkmark$ | -            | 00H   |

| FF17H        | 8-bit timer compare register 50                    | CR50   | R/W | -            | $\checkmark$ | -            | 00H   |

| FF18H        | 8-bit timer H compare register 00                  | CMP00  | R/W | -            | $\checkmark$ | -            | 00H   |

| FF19H        | 8-bit timer H compare register 10                  | CMP10  | R/W | _            | $\checkmark$ | _            | 00H   |

| FF1AH        | 8-bit timer H compare register 01                  | CMP01  | R/W | _            | $\checkmark$ | -            | 00H   |

| FF1BH        | 8-bit timer H compare register 11                  | CMP11  | R/W | _            | $\checkmark$ | -            | 00H   |

| FF1FH        | Serial I/O shift register 10                       | SIO10  | R   | _            | $\checkmark$ | -            | 00H   |

| FF20H        | Port function register 1                           | PF1    | R/W | $\checkmark$ | $\checkmark$ | -            | 00H   |

| FF21H        | Port mode register 1                               | PM1    | R/W | $\checkmark$ | $\checkmark$ | -            | FFH   |

| FF22H        | Port mode register 2                               | PM2    | R/W | $\checkmark$ | $\checkmark$ | -            | FFH   |

| FF23H        | Port mode register 3                               | PM3    | R/W | $\checkmark$ | $\checkmark$ | _            | FFH   |

| FF24H        | Port mode register 4                               | PM4    | R/W | $\checkmark$ | $\checkmark$ | -            | FFH   |

| FF28H        | Port mode register 8                               | PM8    | R/W | $\checkmark$ | $\checkmark$ | -            | FFH   |

| FF2AH        | Port mode register 10                              | PM10   | R/W | $\checkmark$ | $\checkmark$ | -            | FFH   |

| FF2BH        | Port mode register 11                              | PM11   | R/W | $\checkmark$ | $\checkmark$ | -            | FFH   |

| FF2CH        | Port mode register 12                              | PM12   | R/W | $\checkmark$ | $\checkmark$ | _            | FFH   |

| FF2EH        | Port mode register 14                              | PM14   | R/W | $\checkmark$ | $\checkmark$ | _            | FFH   |

| FF2FH        | Port mode register 15                              | PM15   | R/W | $\checkmark$ | $\checkmark$ | -            | FFH   |

| Table 3-6.     | Special | Function | <b>Register List</b> | (1/5) |

|----------------|---------|----------|----------------------|-------|

| 1 4 5 1 5 6 61 | opeenai |          |                      | (     |

**Note**  $\mu$ PD78F043x only.

#### 6.3 Registers Controlling 16-Bit Timer/Event Counter 00

Registers used to control 16-bit timer/event counter 00 are shown below.

- 16-bit timer mode control register 00 (TMC00)

- Capture/compare control register 00 (CRC00)

- 16-bit timer output control register 00 (TOC00)

- Prescaler mode register 00 (PRM00)

- Input switch control register (ISC)

- Port mode register 3 (PM3)

- Port register 3 (P3)

#### (1) 16-bit timer mode control register 00 (TMC00)

TMC00 is an 8-bit register that sets the 16-bit timer/event counter 00 operation mode, TM00 clear mode, and output timing, and detects an overflow.

Rewriting TMC00 is prohibited during operation (when TMC003 and TMC002 = other than 00). However, it can be changed when TMC003 and TMC002 are cleared to 00 (stopping operation) and when OVF00 is cleared to 0. TMC00 can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation sets TMC00 to 00H.

Caution 16-bit timer/event counter 00 starts operation at the moment TMC002 and TMC003 are set to values other than 00 (operation stop mode), respectively. Set TMC002 and TMC003 to 00 to stop the operation.

#### (5) Input switch control register (ISC)

The input source to TI000 becomes the input signal from the P33/TI000 pin, by setting ISC1 to 0. ISC can be set by a 1-bit or 8-bit memory manipulation instruction. Reset signal generation sets ISC to 00H.

#### Figure 6-10. Format of Input Switch Control Register (ISC)

Address: FF4FH After reset: 00H R/W

Symbol 5 0 7 6 4 3 2 1 ISC 0 0 ICS5 ICS4 ICS3 ICS2 ICS1 ICS0

| ICS5             | ICS4 | TxD6, RxD6 input source selection |

|------------------|------|-----------------------------------|

| 0                | 0    | TxD6:P112, RxD6: P113             |

| 1                | 0    | TxD6:P13, RxD6: P12               |

| Other than above |      | Setting prohibited                |

| ISC3 | RxD6/P113 input enabled/disabled |

|------|----------------------------------|

| 0    | RxD6/P113 input disabled         |

| 1    | RxD6/P113 input enabled          |

| ISC2 | TI52 input source control                               |

|------|---------------------------------------------------------|

| 0    | No enable control of TI52 input (P34)                   |

| 1    | Enable controlled of TI52 input (P34) <sup>Note 1</sup> |

| ISC1 | TI000 input source selection          |

|------|---------------------------------------|

| 0    | TI000 (P33)                           |

| 1    | RxD6 (P12 or P113 <sup>Note 2</sup> ) |

| ISC0 | INTP0 input source selection          |

|------|---------------------------------------|

| 0    | INTP0 (P120)                          |

| 1    | RxD6 (P12 or P113 <sup>Note 2</sup> ) |

Notes 1. TI52 input is controlled by TOH2 output signal.

2. TI000 and INTP0 inputs are selected by ISC5 and ISC4.

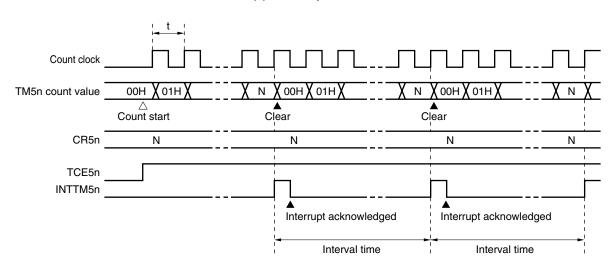

#### 7.4 Operations of 8-Bit Timer/Event Counters 50, 51, and 52

#### 7.4.1 Operation as interval timer

8-bit timer/event counter 5n operates as an interval timer that generates interrupt requests repeatedly at intervals of the count value preset to 8-bit timer compare register 5n (CR5n).

When the count value of 8-bit timer counter 5n (TM5n) matches the value set to CR5n, counting continues with the TM5n value cleared to 0 and an interrupt request signal (INTTM5n) is generated.

The count clock of TM5n can be selected with bits 0 to 2 (TCL5n0 to TCL5n2) of timer clock selection register 5n (TCL5n).

#### Setting

<1> Set the registers.

- TCL5n: Select the count clock.

- CR5n: Compare value

- TMC5n: Stop the count operation

$(TMC50 = 0000 \times \times 0B, TMC51 = TMC52 = 00000000B \times = Don't care)$

- <2> After TCE5n = 1 is set, the count operation starts.

- <3> If the values of TM5n and CR5n match, INTTM5n is generated (TM5n is cleared to 00H).

- <4> INTTM5n is generated repeatedly at the same interval.

Set TCE5n to 0 to stop the count operation.

#### Caution Do not write other values to CR5n during operation.

**Remarks 1.** For how to enable the INTTM5n signal interrupt, see **CHAPTER 19 INTERRUPT FUNCTIONS**. **2.** n = 0 to 2

#### Figure 7-14. Interval Timer Operation Timing (1/2)

#### (a) Basic operation

**Remark** Interval time =  $(N + 1) \times t$ N = 01H to FFH n = 0 to 2

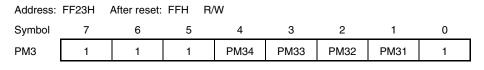

#### (2) Port mode register 3 (PM3)

This register sets port 3 input/output in 1-bit units.

When using the P33/TI000/RTCDIV/RTCCL/BUZ/INTP2 pin for buzzer output, clear PM33 and the output latches of P33 to 0.

PM3 is set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation sets PM3 to FFH.

#### Figure 11-3. Format of Port Mode Register 3 (PM3)

| PM3n | P3n pin I/O mode selection (n = 1 to 4) |

|------|-----------------------------------------|

| 0    | Output mode (output buffer on)          |

| 1    | Input mode (output buffer off)          |

#### **11.4 Operations of Buzzer Output Controller**

The buzzer frequency is output as the following procedure.

- <1> Select the buzzer output frequency with bits 5 and 6 (BCS0, BCS1) of the clock output selection register (CKS) (buzzer output in disabled status).

- <2> Set bit 7 (BZOE) of CKS to 1 to enable buzzer output.

#### (7) 8-bit A/D conversion result register (ADCRH)

The A/D conversion result is loaded from the successive approximation register to this register each time A/D conversion is completed, and the ADCRH register stores the higher 8 bits of the A/D conversion result.

# Caution When data is read from ADCR and ADCRH, a wait cycle is generated. Do not read data from ADCR and ADCRH when the CPU is operating on the subsystem clock and the peripheral hardware clock is stopped. For details, see CHAPTER 31 CAUTIONS FOR WAIT.

#### (8) Controller

This circuit controls the conversion time of an input analog signal that is to be converted into a digital signal, as well as starting and stopping of the conversion operation. When A/D conversion has been completed, this controller generates INTAD.

#### (9) AVREF pin

This pin inputs an analog power/reference voltage to the A/D converter. When using at least one port of port 2 as a digital port or for segment output, set it to the same potential as the V<sub>DD</sub> pin.

The signal input to ANI0 to ANI5 is converted into a digital signal, based on the voltage applied across AV<sub>REF</sub> and AV<sub>SS</sub>.

#### (10) AVss pin

This is the ground potential pin of the A/D converter. Always use this pin at the same potential as that of the Vss pin even when the A/D converter is not used.

#### (11) A/D converter mode register (ADM)

This register is used to set the conversion time of the analog input signal to be converted, and to start or stop the conversion operation.

#### (12) A/D port configuration register 0 (ADPC0)

This register switches the ANI0/P20 to ANI5/P25 pins to analog input of 10-bit successive approximation type A/D converter or digital I/O of port.

#### (13) Analog input channel specification register (ADS)

This register is used to specify the port that inputs the analog voltage to be converted into a digital signal.

#### (14) Port mode register 2 (PM2)

This register switches the ANI0/P20 to ANI5/P25 pins to input or output.

#### (15) Port function register 2 (PF2)

This register switches the ANI0/P20 to ANI5/P25 pins to I/O of port, analog input of A/D converter, or segment output.

| Address: | FF8FH                                                           | After reset: C | 8H R/W |              |              |              |              |              |              |

|----------|-----------------------------------------------------------------|----------------|--------|--------------|--------------|--------------|--------------|--------------|--------------|

| Symbol   | 7                                                               | 6              | 5      | 4            | 3            |              | 2            | 1            | 0            |

| ADPC0    | 0                                                               | 0              | 0      | 0            | 0            | ADF          | PC02 A       | DPC01        | ADPC00       |

|          |                                                                 |                |        |              |              |              |              |              |              |

|          | ADPC02 ADPC01 ADPC00 Digital I/O (D)/analog input (A) switching |                |        |              |              |              |              |              |              |

|          |                                                                 |                |        | P25/<br>ANI5 | P24/<br>ANI4 | P23/<br>ANI3 | P22/<br>ANI2 | P21/<br>ANI1 | P20/<br>ANI0 |

|          | 0                                                               | 0              | 0      | А            | А            | A            | А            | A            | А            |

|          | 0                                                               | 0              | 1      | А            | А            | А            | А            | A            | D            |

|          | 0                                                               | 1              | 0      | А            | A            | A            | Α            | D            | D            |

|          | 0                                                               | 1              | 1      | А            | A            | A            | D            | D            | D            |

|          | 1                                                               | 0              | 0      | А            | A            | D            | D            | D            | D            |

|          | 1                                                               | 0              | 1      | А            | D            | D            | D            | D            | D            |

#### Figure 12-9. Format of A/D Port Configuration Register 0 (ADPC0)

Cautions 1. Set the channel used for A/D conversion to the input mode by using port mode register 2 (PM2).

Setting prohibited

2. Do not set the pin set by ADPC0 as digital I/O by ADS, ADDS1, or ADDS0.

D

0

3. If data is written to ADPC0, a wait cycle is generated. Do not write data to ADPC0 when the CPU is operating on the subsystem clock and the peripheral hardware clock is stopped. For details, see CHAPTER 31 CAUTIONS FOR WAIT.

D

D

D

D

D

4. If pins ANI0/P20/SEG23 to ANI5/P25/SEG18 are set to segment output pins via the PF2 register, output is set to segment output, regardless of the ADPC0 setting.

1

1

Other than above

#### (1) Receive buffer register 0 (RXB0)

This 8-bit register stores parallel data converted by receive shift register 0 (RXS0).

Each time 1 byte of data has been received, new receive data is transferred to this register from receive shift register 0 (RXS0).

If the data length is set to 7 bits the receive data is transferred to bits 0 to 6 of RXB0 and the MSB of RXB0 is always 0.

If an overrun error (OVE0) occurs, the receive data is not transferred to RXB0.

RXB0 can be read by an 8-bit memory manipulation instruction. No data can be written to this register. Reset signal generation and POWER0 = 0 set this register to FFH.

#### (2) Receive shift register 0 (RXS0)

This register converts the serial data input to the RxD0 pin into parallel data. RXS0 cannot be directly manipulated by a program.

#### (3) Transmit shift register 0 (TXS0)

This register is used to set transmit data. Transmission is started when data is written to TXS0, and serial data is transmitted from the TxD0 pins.

TXS0 can be written by an 8-bit memory manipulation instruction. This register cannot be read. Reset signal generation, POWER0 = 0, and TXE0 = 0 set this register to FFH.

#### Cautions 1. Set transmit data to TXS0 at least one base clock (fxcLK0) after setting TXE0 = 1.

2. Do not write the next transmit data to TXS0 before the transmission completion interrupt signal (INTST0) is generated.

#### 14.4.4 Calculation of baud rate

#### (1) Baud rate calculation expression

The baud rate can be calculated by the following expression.

• Baud rate =  $\frac{f_{XCLK6}}{2 \times k}$  [bps]

fxclk6: Frequency of base clock selected by TPS63 to TPS60 bits of CKSR6 register

k: Value set by MDL67 to MDL60 bits of BRGC6 register (k = 4, 5, 6, ..., 255)

| TPS63 | TPS62      | TPS61    | TPS60 |                        | Base Clock (fxcLK6) Selection <sup>Note 1</sup> |                 |                             |                              |  |  |

|-------|------------|----------|-------|------------------------|-------------------------------------------------|-----------------|-----------------------------|------------------------------|--|--|

|       |            |          |       |                        | f <sub>PRS</sub> =<br>2 MHz                     | fprs =<br>5 MHz | f <sub>PRS</sub> =<br>8 MHz | f <sub>PRS</sub> =<br>10 MHz |  |  |

| 0     | 0          | 0        | 0     | fprs <sup>Note 2</sup> | 2 MHz                                           | 5 MHz           | 8 MHz                       | 10 MHz                       |  |  |

| 0     | 0          | 0        | 1     | fprs/2                 | 1 MHz                                           | 2.5 MHz         | 4 MHz                       | 5 MHz                        |  |  |

| 0     | 0          | 1        | 0     | fprs/2 <sup>2</sup>    | 500 kHz                                         | 1.25 MHz        | 2 MHz                       | 2.5 MHz                      |  |  |

| 0     | 0          | 1        | 1     | fprs/2 <sup>3</sup>    | 250 kHz                                         | 625 kHz         | 1 MHz                       | 1.25 MHz                     |  |  |

| 0     | 1          | 0        | 0     | fprs/2 <sup>4</sup>    | 125 kHz                                         | 312.5 kHz       | 500 kHz                     | 625 kHz                      |  |  |

| 0     | 1          | 0        | 1     | fprs/2⁵                | 62.5 kHz                                        | 156.25 kHz      | 250 kHz                     | 312.5 kHz                    |  |  |

| 0     | 1          | 1        | 0     | fprs/2 <sup>6</sup>    | 31.25 kHz                                       | 78.13 kHz       | 125 kHz                     | 156.25 kHz                   |  |  |

| 0     | 1          | 1        | 1     | fprs/27                | 15.625 kHz                                      | 39.06 kHz       | 62.5 kHz                    | 78.13 kHz                    |  |  |

| 1     | 0          | 0        | 0     | fprs/2 <sup>8</sup>    | 7.813 kHz                                       | 19.53 kHz       | 31.25 kHz                   | 39.06 kHz                    |  |  |

| 1     | 0          | 0        | 1     | fprs/2 <sup>9</sup>    | 3.906 kHz                                       | 9.77 kHz        | 15.625 kHz                  | 19.53 kHz                    |  |  |

| 1     | 0          | 1        | 0     | fprs/2 <sup>10</sup>   | 1.953 kHz                                       | 4.88 kHz        | 7.813 kHz                   | 9.77 kHz                     |  |  |

| 1     | 0          | 1        | 1     | TM50 or                | utput <sup>Note 3</sup>                         |                 |                             |                              |  |  |

|       | Other that | an above |       | Setting                | prohibited                                      |                 |                             |                              |  |  |

Table 14-4. Set Value of TPS63 to TPS60

- **Notes 1.** If the peripheral hardware clock (fPRs) operates on the high-speed system clock (fXH) (XSEL = 1), the fPRs operating frequency varies depending on the supply voltage.

- VDD = 2.7 to 5.5 V: fPRs  $\leq$  10 MHz

- VDD = 1.8 to 2.7 V: fprs  $\leq$  5 MHz

- 2. If the peripheral hardware clock (fPRS) operates on the internal high-speed oscillation clock (fRH) (XSEL = 0), when 1.8 V ≤ VDD < 2.7 V, the setting of TPS63 = TPS62 = TPS61 = TPS60 = 0 (base clock: fPRS) is prohibited.</p>

- **3.** When selecting the TM50 output as the base clock, start the operation of 8-bit timer/event counter 50 first and then enable the timer F/F inversion operation (TMC501 = 1).

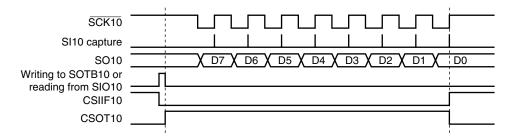

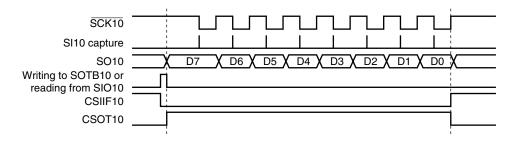

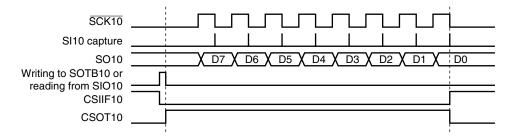

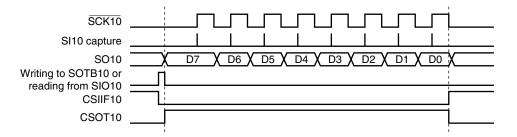

#### Figure 15-7. Timing of Clock/Data Phase

#### (a) Type 1: CKP10 = 0, DAP10 = 0, DIR10 = 0

#### (b) Type 2: CKP10 = 0, DAP10 = 1, DIR10 = 0

#### (c) Type 3: CKP10 = 1, DAP10 = 0, DIR10 = 0

#### (d) Type 4: CKP10 = 1, DAP10 = 1, DIR10 = 0

#### (3) LCD clock control register (LCDC0)

LCDC0 specifies the LCD source clock and LCD clock. The frame frequency is determined according to the LCD clock and the number of time slices. LCDC0 is set using a 1-bit or 8-bit memory manipulation instruction. Reset signal generation sets LCDC0 to 00H.

#### Figure 16-4. Format of LCD Clock Control Register

| Address | Address: FFB2H After reset: 00H |      | 0H R/W  |       |   |       |       |       |   |

|---------|---------------------------------|------|---------|-------|---|-------|-------|-------|---|

| Symbol  | 7                               | 6    | 5       | 4     | 3 | 2     | 1     | 0     |   |

| LCDC0   | 0                               | LCDC | 6 LCDC5 | LCDC4 | 0 | LCDC2 | LCDC1 | LCDC0 | 1 |

| LCDC6          | LCDC5 | LCDC4 | LCD source clock (fLCD) selection |

|----------------|-------|-------|-----------------------------------|

| 0              | 0     | 0     | fхт (32.768 kHz)                  |

| 0              | 0     | 1     | fprs/2 <sup>6</sup>               |

| 0              | 1     | 0     | fprs/2 <sup>7</sup>               |

| 0              | 1     | 1     | fprs/2 <sup>8</sup>               |

| 1              | 0     | 0     | f <sub>RL</sub> /2 <sup>3</sup>   |

| Other than abo | ove   |       | Setting prohibited                |

| LCDC2          | LCDC1 | LCDC0 | LCD clock (LCDCL) selection |

|----------------|-------|-------|-----------------------------|

| 0              | 0     | 0     | fLCD/2 <sup>4</sup>         |

| 0              | 0     | 1     | fLCD/2 <sup>5</sup>         |

| 0              | 1     | 0     | fLCD/2 <sup>6</sup>         |

| 0              | 1     | 1     | flcd/2 <sup>7</sup>         |

| 1              | 0     | 0     | fLCD/2 <sup>8</sup>         |

| 1              | 0     | 1     | fLCD/2º                     |

| Other than abo | ove   |       | Setting prohibited          |

#### Caution Bits 3 and 7 must be set to 0.

- Remarks 1. fxT: XT1 clock oscillation frequency

- 2. fPRS: Peripheral hardware clock frequency

- 3. fr.L: Internal low-speed oscillation clock frequency

#### **18.4 Operation of Remote Controller Receiver**

The following remote controller reception mode is used for this remote controller receiver.

• Type A reception mode with guide pulse (half clock)

#### 18.4.1 Format of type A reception mode

Figure 18-6 shows the data format for type A.

#### 0.6 ms 1.8 ms 2.4 ms 2 ms RIN Data Data Data Data Data Data Data Data Data Guide pulse "0' "0' "0" "0 "0" "0" "O INTRIN INTGP INTDFULL INTREND RMDLL RMER

#### Figure 18-6. Example of Type A Data Format

#### 18.4.2 Operation flow of type A reception mode

Figure 18-7 shows the operation flow.

- Cautions 1. When INTRERR is generated, RMSR and RMSCR are automatically cleared immediately.

- 2. When data has been set to all the bits of RMSR, the following processing is automatically performed.

- The value of RMSR is transferred to RMDR.

- INTDFULL is generated.

- RMSR is cleared.

RMDR must then be read before the next data is set to all the bits of RMSR.

- 3. When INTREND has been generated, read RMSCR first followed by RMSR. When RMSR has been read, RMSCR and RMSR are automatically cleared. If INTREND is generated, the next data cannot be received until RMSR is read.

- 4. RMSR, RMSCR, and RMDR are cleared simultaneously to operation termination (RMEN = 0).

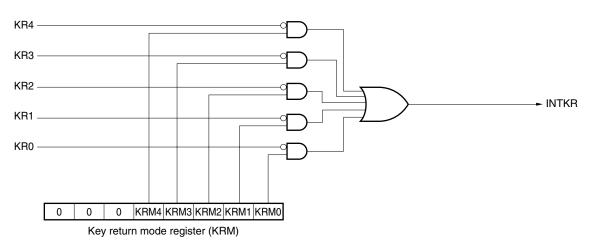

#### CHAPTER 20 KEY INTERRUPT FUNCTION

#### 20.1 Functions of Key Interrupt

A key interrupt (INTKR) can be generated by setting the key return mode register (KRM) and inputting a falling edge to the key interrupt input pins (KR0 to KR4).

| Flag | Description                         |

|------|-------------------------------------|

| KRM0 | Controls KR0 signal in 1-bit units. |

| KRM1 | Controls KR1 signal in 1-bit units. |

| KRM2 | Controls KR2 signal in 1-bit units. |

| KRM3 | Controls KR3 signal in 1-bit units. |

| KRM4 | Controls KR4 signal in 1-bit units. |

Table 20-1. Assignment of Key Interrupt Detection Pins

#### 20.2 Configuration of Key Interrupt

The key interrupt includes the following hardware.

Table 20-2. Configuration of Key Interrupt

| Item             | Configuration                  |

|------------------|--------------------------------|

| Control register | Key return mode register (KRM) |

| Release Source                | MK×× | PR×× | IE | ISP | Operation                          |

|-------------------------------|------|------|----|-----|------------------------------------|

| Maskable interrupt<br>request | 0    | 0    | 0  | ×   | Next address instruction execution |

|                               | 0    | 0    | 1  | ×   | Interrupt servicing execution      |

|                               | 0    | 1    | 0  | 1   | Next address                       |

|                               | 0    | 1    | ×  | 0   | instruction execution              |

|                               | 0    | 1    | 1  | 1   | Interrupt servicing execution      |

|                               | 1    | ×    | ×  | ×   | HALT mode held                     |

| Reset                         | -    | _    | ×  | ×   | Reset processing                   |

Table 21-2. Operation in Response to Interrupt Request in HALT Mode

×: don't care

#### 21.2.2 STOP mode

#### (1) STOP mode setting and operating statuses

The STOP mode is set by executing the STOP instruction, and it can be set only when the CPU clock before the setting was the main system clock.

Caution Because the interrupt request signal is used to clear the standby mode, if there is an interrupt source with the interrupt request flag set and the interrupt mask flag reset, the standby mode is immediately cleared if set. Thus, the STOP mode is reset to the HALT mode immediately after execution of the STOP instruction and the system returns to the operating mode as soon as the wait time set using the oscillation stabilization time select register (OSTS) has elapsed.

The operating statuses in the STOP mode are shown below.

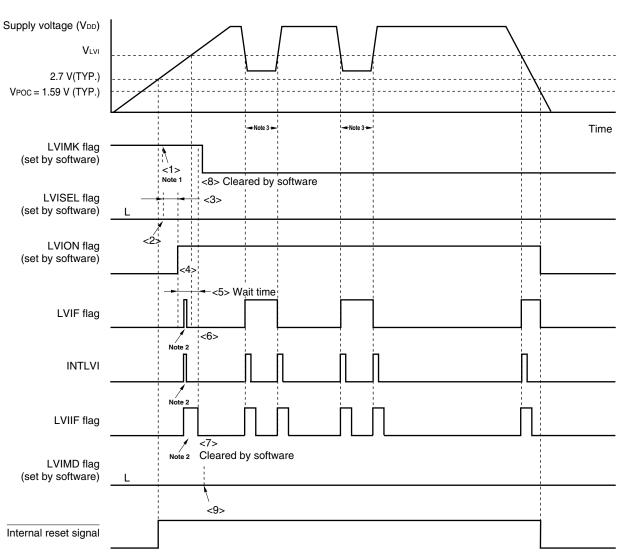

Figure 24-7. Timing of Low-Voltage Detector Interrupt Signal Generation (Detects Level of Supply Voltage (VDD)) (2/2)

Notes 1. The LVIMK flag is set to "1" by reset signal generation.

- 2. The interrupt request signal (INTLVI) is generated and the LVIF and LVIIF flags may be set (1).

- **3.** If LVION is cleared (0) in a state below the LVI detection voltage, an INTLVI signal is generated and LVIIF becomes 1.

- **Remark** <1> to <9> in Figure 24-7 above correspond to <1> to <9> in the description of "When starting operation" in **24.4.2 (1) When detecting level of supply voltage (V**<sub>DD</sub>).

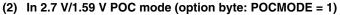

Figure 26-3. Example of Wiring Adapter for Flash Memory Writing in UART (UART6) Mode

**Note** The above figure illustrates an example of wiring when using the clock output from the PG-FP4 or FL-PR4. When using the clock output from the PG-FPL3 or FP-LITE3, connect CLK to X1/P121 (pin 12), and connect its inverted signal to X2/EXCLK/P122 (pin 11).

#### 28.3 Instructions Listed by Addressing Type

#### (1) 8-bit instructions

MOV, XCH, ADD, ADDC, SUB, SUBC, AND, OR, XOR, CMP, MULU, DIVUW, INC, DEC, ROR, ROL, RORC, ROLC, ROR4, ROL4, PUSH, POP, DBNZ

| Second Operand<br>First Operand     | #byte                                                        | A                                                            | r <sup>Note</sup>                                           | sfr        | saddr                                                       | !addr16                                                     | PSW | [DE]       | [HL]                                                        | [HL+byte]<br>[HL + B]<br>[HL + C]                           | \$addr16 | 1                          | None         |

|-------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------|-------------------------------------------------------------|------------|-------------------------------------------------------------|-------------------------------------------------------------|-----|------------|-------------------------------------------------------------|-------------------------------------------------------------|----------|----------------------------|--------------|

| A                                   | ADD<br>ADDC<br>SUB<br>SUBC<br>AND<br>OR<br>XOR<br>CMP        |                                                              | MOV<br>XCH<br>ADD<br>SUB<br>SUBC<br>AND<br>OR<br>XOR<br>CMP | MOV<br>XCH | MOV<br>XCH<br>ADD<br>SUB<br>SUBC<br>AND<br>OR<br>XOR<br>CMP | MOV<br>XCH<br>ADD<br>SUB<br>SUBC<br>AND<br>OR<br>XOR<br>CMP | MOV | MOV<br>XCH | MOV<br>XCH<br>ADD<br>SUB<br>SUBC<br>AND<br>OR<br>XOR<br>CMP | MOV<br>XCH<br>ADD<br>SUB<br>SUBC<br>AND<br>OR<br>XOR<br>CMP |          | ROR<br>ROL<br>RORC<br>ROLC |              |

| r                                   | MOV                                                          | MOV<br>ADD<br>ADDC<br>SUB<br>SUBC<br>AND<br>OR<br>XOR<br>CMP |                                                             |            |                                                             |                                                             |     |            |                                                             |                                                             |          |                            | INC<br>DEC   |

| B, C                                |                                                              |                                                              |                                                             |            |                                                             |                                                             |     |            |                                                             |                                                             | DBNZ     |                            |              |

| sfr                                 | MOV                                                          | MOV                                                          |                                                             |            |                                                             |                                                             |     |            |                                                             |                                                             |          |                            |              |

| saddr                               | MOV<br>ADD<br>ADDC<br>SUB<br>SUBC<br>AND<br>OR<br>XOR<br>CMP | MOV                                                          |                                                             |            |                                                             |                                                             |     |            |                                                             |                                                             | DBNZ     |                            | INC<br>DEC   |

| !addr16                             |                                                              | MOV                                                          |                                                             |            |                                                             |                                                             |     |            |                                                             |                                                             |          |                            |              |

| PSW                                 | MOV                                                          | MOV                                                          |                                                             |            |                                                             |                                                             |     |            |                                                             |                                                             |          |                            | PUSH<br>POP  |

| [DE]                                |                                                              | MOV                                                          |                                                             |            |                                                             |                                                             |     |            |                                                             |                                                             |          |                            |              |

| [HL]                                |                                                              | MOV                                                          |                                                             |            |                                                             |                                                             |     |            |                                                             |                                                             |          |                            | ROR4<br>ROL4 |

| [HL + byte]<br>[HL + B]<br>[HL + C] |                                                              | MOV                                                          |                                                             |            |                                                             |                                                             |     |            |                                                             |                                                             |          |                            |              |

| х                                   |                                                              |                                                              |                                                             |            |                                                             |                                                             |     |            |                                                             |                                                             |          |                            | MULU         |

| С                                   |                                                              |                                                              |                                                             |            |                                                             |                                                             |     |            |                                                             |                                                             |          |                            | DIVUW        |

Standard products

#### X1 Oscillator Characteristics

#### $(T_A = -40 \text{ to } +85^{\circ}C, 1.8 \text{ V} \le \text{V}_{DD} \le 5.5 \text{ V}, \text{V}_{SS} = \text{AV}_{SS} = 0 \text{ V})$

| Resonator            | Recommended Circuit | Parameter                                                 | Conditions                                                | MIN. | TYP. | MAX. | Unit |

|----------------------|---------------------|-----------------------------------------------------------|-----------------------------------------------------------|------|------|------|------|

| Ceramic<br>resonator |                     | X1 clock<br>oscillation<br>frequency (fx) <sup>Note</sup> | $2.7~V \leq V_{\text{DD}} \leq 5.5~V$                     | 2.0  |      | 10.0 | MHz  |

|                      |                     |                                                           | $1.8 \text{ V} \leq \text{V}_{\text{DD}} < 2.7 \text{ V}$ | 2.0  |      | 5.0  |      |

| Crystal<br>resonator |                     | X1 clock<br>oscillation<br>frequency (fx) <sup>Note</sup> | $2.7~V \leq V_{\text{DD}} \leq 5.5~V$                     | 2.0  |      | 10.0 | MHz  |

|                      |                     |                                                           | $1.8 \text{ V} \leq \text{V}_{\text{DD}} < 2.7 \text{ V}$ | 2.0  |      | 5.0  |      |

Note Indicates only oscillator characteristics. Refer to AC Characteristics for instruction execution time.

### Cautions 1. When using the X1 oscillator, wire as follows in the area enclosed by the broken lines in the above figures to avoid an adverse effect from wiring capacitance.

- Keep the wiring length as short as possible.

- Do not cross the wiring with the other signal lines.

- Do not route the wiring near a signal line through which a high fluctuating current flows.

- Always make the ground point of the oscillator capacitor the same potential as Vss.

- Do not ground the capacitor to a ground pattern through which a high current flows.

- Do not fetch signals from the oscillator.

- 2. Since the CPU is started by the internal high-speed oscillation clock after a reset release, check the X1 clock oscillation stabilization time using the oscillation stabilization time counter status register (OSTC) by the user. Determine the oscillation stabilization time of the OSTC register and oscillation stabilization time select register (OSTS) after sufficiently evaluating the oscillation stabilization time with the resonator to be used.

- **Remark** For the resonator selection and oscillator constant, customers are requested to either evaluate the oscillation themselves or apply to the resonator manufacturer for evaluation.

#### Standard products

#### (c) CSI10 (Master mode, SCK10... internal clock output)

| Parameter                                        | Symbol        | Conditions                                                   | MIN.                              | TYP. | MAX. | Unit |

|--------------------------------------------------|---------------|--------------------------------------------------------------|-----------------------------------|------|------|------|

| SCK10 cycle time                                 | tkcy1         | $2.7~V \leq V_{\text{DD}} \leq 5.5~V$                        | 250                               |      |      | ns   |

|                                                  |               | $1.8~V \leq V_{\text{DD}} < 2.7~V$                           | 500                               |      |      | ns   |

| SCK10 high-/low-level width                      | tкнı,<br>tк∟ı | $2.7 \text{ V} \leq \text{V}_{\text{DD}} \leq 5.5 \text{ V}$ | tkcy1/2 –<br>25 <sup>Note 1</sup> |      |      | ns   |

|                                                  |               | $1.8 \text{ V} \le \text{V}_{\text{DD}} < 2.7 \text{ V}$     | tkCY1/2 -<br>50 <sup>Note 1</sup> |      |      | ns   |

| SI10 setup time (to SCK10↑)                      | tsik1         | $2.7~V \leq V_{\text{DD}} \leq 5.5~V$                        | 80                                |      |      | ns   |

|                                                  |               | $1.8~V \leq V_{\text{DD}} < 2.7~V$                           | 170                               |      |      | ns   |

| SI10 hold time (from $\overline{\text{SCK10}}$ ) | tksi1         |                                                              | 30                                |      |      | ns   |

| Delay time from SCK10↓ to<br>SO10 output         | tkso1         | $C = 50 \text{ pF}^{Note 2}$                                 |                                   |      | 40   | ns   |

Notes 1. This value is when high-speed system clock (fxH) is used.

**2.** C is the load capacitance of the  $\overline{SCK10}$  and SO10 output lines.

#### (d) CSI10 (Slave mode, SCK10... external clock input)

| Parameter                                              | Symbol | C         | onditions                             | MIN.    | TYP. | MAX. | Unit |

|--------------------------------------------------------|--------|-----------|---------------------------------------|---------|------|------|------|

| SCK10 cycle time                                       | tKCY2  |           |                                       | 400     |      |      | ns   |

| SCK10 high-/low-level width                            | tкн2,  |           |                                       | tксү2/2 |      |      | ns   |

|                                                        | tĸ∟2   |           |                                       |         |      |      |      |

| SI10 setup time (to $\overline{\text{SCK10}}$ )        | tsik2  |           |                                       | 80      |      |      | ns   |

| SI10 hold time (from SCK10↑)                           | tksi2  |           |                                       | 50      |      |      | ns   |

| Delay time from $\overline{\text{SCK10}}\downarrow$ to | tĸso2  | C = 50 pF | $2.7~V \leq V_{\text{DD}} \leq 5.5~V$ |         |      | 120  | ns   |

| SO10 output                                            |        | Note      | $1.8~V \leq V_{\text{DD}} < 2.7~V$    |         |      | 165  | ns   |

Note C is the load capacitance of the SO10 output line.

#### Standard products

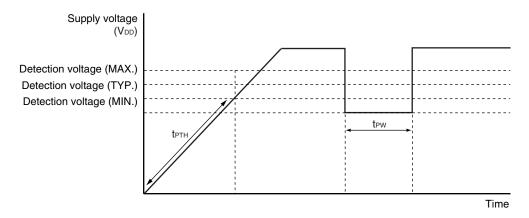

#### 1.59 V POC Circuit Characteristics (T<sub>A</sub> = -40 to +85°C, Vss = 0 V)

| Parameter                             | Symbol | Conditions                                                                        | MIN. | TYP. | MAX. | Unit |

|---------------------------------------|--------|-----------------------------------------------------------------------------------|------|------|------|------|

| Detection voltage                     | VPOC   |                                                                                   | 1.44 | 1.59 | 1.74 | V    |

| Power supply voltage rise inclination | tртн   | $V_{\text{DD}}\text{: }0V\rightarrow \text{change inclination of }V_{\text{POC}}$ | 0.5  |      |      | V/ms |

| Minimum pulse width                   | tew    |                                                                                   | 200  |      |      | μs   |

#### **POC Circuit Timing**

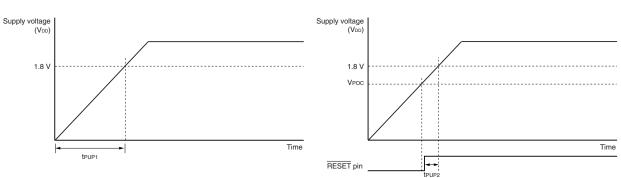

#### Supply Voltage Rise Time (T<sub>A</sub> = -40 to +85°C, V<sub>SS</sub> = 0 V)

| Parameter                                                                                                                                                              | Symbol        | Conditions                                                                       | MIN. | TYP. | MAX. | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----------------------------------------------------------------------------------|------|------|------|------|

| Maximum time to rise to 1.8 V (V_{DD} (MIN.)) (V_{DD}: 0 V \rightarrow 1.8 V)                                                                                          | <b>t</b> pup1 | POCMODE (option byte) = 0,<br>when RESET input is not used                       |      |      | 3.6  | ms   |

| $\begin{array}{l} \mbox{Maximum time to rise to 1.8 V (V_{DD} (MIN.))} \\ \mbox{(releasing $\overline{\mbox{RESET}}$ input $\rightarrow$ V_{DD}$: 1.8 V)} \end{array}$ | tpup2         | POCMODE (option byte) = 0,<br>when $\overrightarrow{\text{RESET}}$ input is used |      |      | 1.9  | ms   |

#### Supply Voltage Rise Time Timing

• When RESET pin input is used

#### 2.7 V POC Circuit Characteristics (TA = -40 to +85°C, Vss = 0 V)

| Parameter                                          | Symbol | Conditions               | MIN. | TYP. | MAX. | Unit |

|----------------------------------------------------|--------|--------------------------|------|------|------|------|

| Detection voltage on application of supply voltage | VDDPOC | POCMODE (option bye) = 1 | 2.50 | 2.70 | 2.90 | V    |