# E. Renesas Electronics America Inc - UPD78F0432GB-GAG-AX Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------|

| Product Status             | Active                                                                               |

| Core Processor             | 78K/0                                                                                |

| Core Size                  | 8-Bit                                                                                |

| Speed                      | 10MHz                                                                                |

| Connectivity               | 3-Wire SIO, LINbus, UART/USART                                                       |

| Peripherals                | LCD, LVD, POR, PWM, WDT                                                              |

| Number of I/O              | 34                                                                                   |

| Program Memory Size        | 24KB (24K x 8)                                                                       |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 1K x 8                                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                          |

| Data Converters            | A/D 6x10b                                                                            |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 52-LQFP                                                                              |

| Supplier Device Package    | -                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f0432gb-gag-ax |

|                            |                                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# INTRODUCTION

| Readers                 | This manual is intended for user engineers who wish to understand the functions of th 78K0/LD3 and design and develop application systems and programs for these device. The target products are as follows. |                                                                                                          |                                                                                                                  |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

|                         | 78K0/LD3: μPD78F0420, 7<br>μPD78F0430, 7                                                                                                                                                                     |                                                                                                          |                                                                                                                  |

| Purpose                 | This manual is intended to g<br>Organization below.                                                                                                                                                          | give users an ur                                                                                         | nderstanding of the functions described in the                                                                   |

| Organization            | The 78K0/LD3 manual is sedition (common to the 78K                                                                                                                                                           | -                                                                                                        | two parts: this manual and the instructions ers).                                                                |

|                         | 78K0/LD3<br>User's Manua<br>(This Manual                                                                                                                                                                     |                                                                                                          | 78K/0 Series<br>User's Manual<br>Instructions                                                                    |

|                         | <ul> <li>Pin functions</li> <li>Internal block functions</li> <li>Interrupts</li> <li>Other on-chip peripheral</li> <li>Electrical specifications</li> </ul>                                                 | functions                                                                                                | <ul><li> CPU functions</li><li> Instruction set</li><li> Explanation of each instruction</li></ul>               |

| How to Read This Manual | It is assumed that the rea<br>engineering, logic circuits, a                                                                                                                                                 |                                                                                                          | anual have general knowledge of electrical<br>llers.                                                             |

|                         | reserved word in th<br>#pragma sfr directive<br>• To know details of the 78                                                                                                                                  | he order of the o<br>ster format:<br>nclosed in ang<br>e RA78K0, an<br>in the CC78K0.<br>8K0 microcontro | CONTENTS.<br>Ile brackets, the bit name is defined as a<br>d is defined as an sfr variable using the             |

| Conventions             | Data significance:<br>Active low representations:<br>Note:<br>Caution:<br>Remark:<br>Numerical representations:                                                                                              | xxx (overscore<br>Footnote for ite<br>Information ree<br>Supplementary                                   | em marked with <b>Note</b> in the text<br>quiring particular attention<br>y information<br>xxxx or xxxxB<br>xxxx |

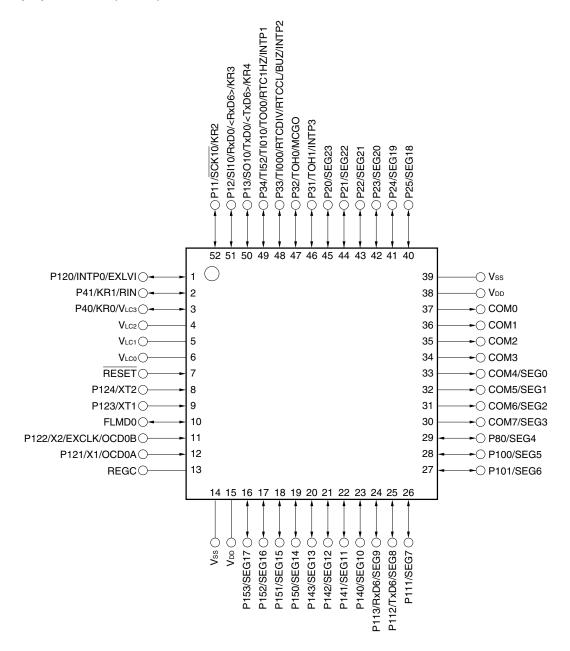

# 1.4 Pin Configuration (Top View)

# (1) *µ*PD78F0420, 78F0421, 78F0422, 78F0423

• 52-pin plastic LQFP ( $10 \times 10$ )

- Only the bottom side pins (pin numbers 24 and 25) correspond to the UART6 pins (RxD6 and TxD6) when writing by a flash memory programmer. Writing cannot be performed by the top side pins (pin numbers 51 and 50).

- 3. Make VDD (pin number 15) and VDD (pin number 38), Vss (pin number 14) and Vss (pin number 39) the same potential.

**Remark** The functions within arrowheads (< >) can be assigned by setting the input switch control register (ISC).

| Address | Special Function Register (SFR) Name                      | Symbol | R/W | Manipulatable Bit Unit |              |         | After                 |

|---------|-----------------------------------------------------------|--------|-----|------------------------|--------------|---------|-----------------------|

|         |                                                           |        |     | 1 Bit                  | 8 Bits       | 16 Bits | Reset                 |

| FF99H   | Watchdog timer enable register                            | WDTE   | R/W | -                      | $\checkmark$ | -       | Note 1<br>1AH/9AH     |

| FF9AH   | Remote controller receive control register                | RMCN   | R/W | $\checkmark$           | $\checkmark$ | -       | 00H                   |

| FF9BH   | Remote controller receive data register                   | RMDR   | R   | _                      | $\checkmark$ | _       | 00H                   |

| FF9CH   | Remote controller shift register receive counter register | RMSCR  | R   | -                      | V            | -       | 00H                   |

| FF9FH   | Clock operation mode select register                      | OSCCTL | R/W | $\checkmark$           | $\checkmark$ | -       | 00H                   |

| FFA0H   | Internal oscillation mode register                        | RCM    | R/W | $\checkmark$           | $\checkmark$ | -       | 80H <sup>Note 2</sup> |

| FFA1H   | Main clock mode register                                  | MCM    | R/W | $\checkmark$           | $\checkmark$ | -       | 00H                   |

| FFA2H   | Main OSC control register                                 | MOC    | R/W | $\checkmark$           | $\checkmark$ | -       | 80H                   |

| FFA3H   | Oscillation stabilization time counter status register    | OSTC   | R   | $\checkmark$           | $\checkmark$ | _       | 00H                   |

| FFA4H   | Oscillation stabilization time select register            | OSTS   | R/W | -                      | $\checkmark$ | -       | 05H                   |

| FFA5H   | Remote controller receive GPHS compare register           | RMGPHS | R/W | -                      | V            | -       | 00H                   |

| FFA6H   | Remote controller receive GPHL compare register           | RMGPHL | R/W | -                      | V            | -       | 00H                   |

| FFA7H   | Remote controller receive DLS compare register            | RMDLS  | R/W | -                      | V            | -       | 00H                   |

| FFA8H   | Remote controller receive DLL compare register            | RMDLL  | R/W | _                      | $\checkmark$ | -       | 00H                   |

| FFA9H   | Remote controller receive DH0S compare register           | RMDH0S | R/W | -                      | V            | -       | 00H                   |

| FFAAH   | Remote controller receive DH0L compare register           | RMDH0L | R/W | -                      | V            | -       | 00H                   |

| FFABH   | Remote controller receive shift register                  | RMSR   | R   | _                      | $\checkmark$ | _       | 00H                   |

| FFACH   | Reset control flag register                               | RESF   | R   | _                      | $\checkmark$ | _       | 00H <sup>Note 3</sup> |

| FFADH   | Remote controller receive DH1S compare register           | RMDH1S | R/W | -                      | $\checkmark$ | _       | 00H                   |

| FFAEH   | Remote controller receive DH1L compare register           | RMDH1L | R/W | -                      | V            | -       | 00H                   |

| FFAFH   | Remote controller receive end width select register       | RMER   | R/W | _                      | $\checkmark$ | _       | 00H                   |

| Table 3-6. | Special | Function | Register | List (4 | /5) |

|------------|---------|----------|----------|---------|-----|

|------------|---------|----------|----------|---------|-----|

**Notes 1.** The reset value of WDTE is determined by the setting of the option byte.

- 2. The value of this register is 00H immediately after a reset release but automatically changes to 80H after oscillation accuracy stabilization of high-speed internal oscillator has been waited.

- 3. The reset value of RESF varies depending on the reset source.

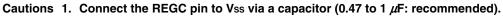

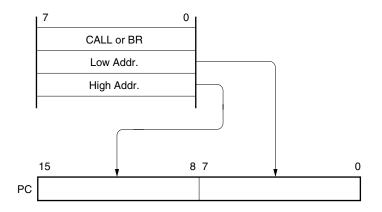

# 3.3.2 Immediate addressing

# [Function]

Immediate data in the instruction word is transferred to the program counter (PC) and branched.

This function is carried out when the CALL !addr16 or BR !addr16 or CALLF !addr11 instruction is executed. CALL !addr16 and BR !addr16 instructions can be branched to the entire memory space. The CALLF !addr11 instruction is branched to the 0800H to 0FFFH area.

## [Illustration]

In the case of CALL laddr16 and BR laddr16 instructions

In the case of CALLF !addr11 instruction

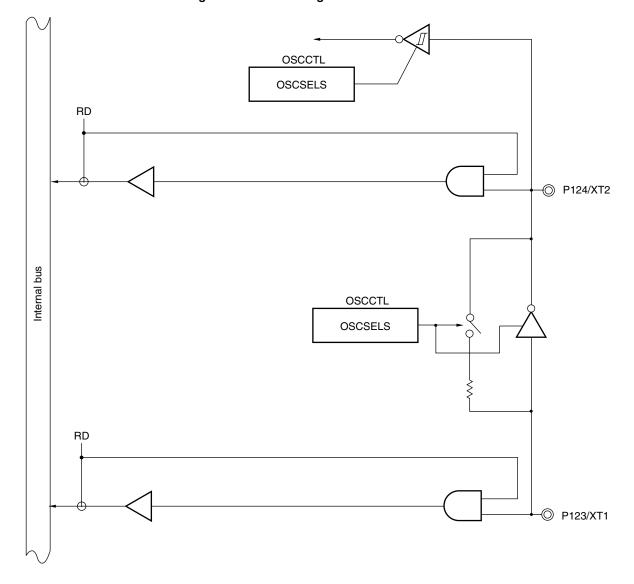

Figure 4-17. Block Diagram of P123 and P124

OSCCTL: Clock operation mode select register RD: Read signal

# 5.4 System Clock Oscillator

#### 5.4.1 X1 oscillator

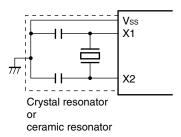

The X1 oscillator oscillates with a crystal resonator or ceramic resonator (2 to 10 MHz) connected to the X1 and X2 pins.

An external clock can also be input. In this case, input the clock signal to the EXCLK pin. Figure 5-10 shows an example of the external circuit of the X1 oscillator.

#### Figure 5-10. Example of External Circuit of X1 Oscillator

#### (a) Crystal or ceramic oscillation

(b) External clock

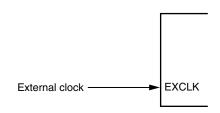

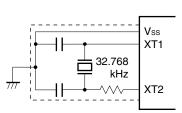

#### 5.4.2 XT1 oscillator

The XT1 oscillator oscillates with a crystal resonator (standard: 32.768 kHz) connected to the XT1 and XT2 pins. Figure 5-11 shows an example of the external circuit of the XT1 oscillator.

# Figure 5-11. Example of External Circuit of XT1 Oscillator

#### (a) Crystal oscillation

- Caution 1. When using the X1 oscillator and XT1 oscillator, wire as follows in the area enclosed by the broken lines in the Figures 5-10 and 5-11 to avoid an adverse effect from wiring capacitance.

- Keep the wiring length as short as possible.

- Do not cross the wiring with the other signal lines. Do not route the wiring near a signal line through which a high fluctuating current flows.

- Always make the ground point of the oscillator capacitor the same potential as Vss. Do not ground the capacitor to a ground pattern through which a high current flows.

- Do not fetch signals from the oscillator.

Note that the XT1 oscillator is designed as a low-amplitude circuit for reducing power consumption.

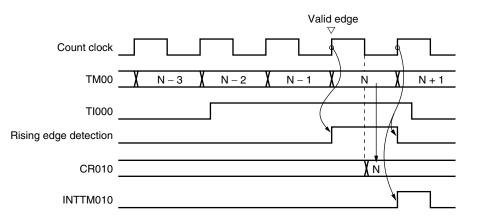

# Figure 6-7. Example of CR010 Capture Operation (When Rising Edge Is Specified)

# (3) 16-bit timer output control register 00 (TOC00)

TOC00 is an 8-bit register that controls TO00 output.

TOC00 can be rewritten while only OSPT00 is operating (when TMC003 and TMC002 = other than 00). Rewriting the other bits is prohibited during operation.

However, TOC004 can be rewritten during timer operation as a means to rewrite CR010 (see **6.5.1 Rewriting CR010 during TM00 operation**).

TOC00 can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation clears TOC00 to 00H.

#### Caution Be sure to set TOC00 using the following procedure.

<1> Set TOC004 and TOC001 to 1.

<2> Set only TOE00 to 1.

<3> Set either of LVS00 or LVR00 to 1.

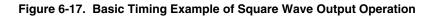

#### 6.4.2 Square wave output operation

When 16-bit timer/event counter 00 operates as an interval timer (see **6.4.1**), a square wave can be output from the TO00 pin by setting the 16-bit timer output control register 00 (TOC00) to 03H.

When TMC003 and TMC002 are set to 11 (count clear & start mode entered upon a match between TM00 and CR000), the counting operation is started in synchronization with the count clock.

When the value of TM00 later matches the value of CR000, TM00 is cleared to 0000H, an interrupt signal (INTTM000) is generated, and TO00 output is inverted. This TO00 output that is inverted at fixed intervals enables TO00 to output a square wave.

#### Remarks 1. For the setting of I/O pins, see 6.3 (6) Port mode register 3 (PM3).

2. For how to enable the INTTM000 signal interrupt, see CHAPTER 19 INTERRUPT FUNCTIONS.

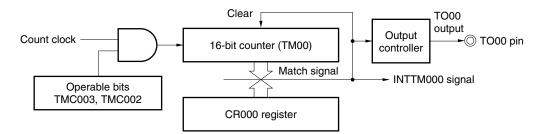

Figure 6-16. Block Diagram of Square Wave Output Operation

A pulse width can be measured in the following three ways.

- Measuring the pulse width by using two input signals of the TI000 and TI010 pins (free-running timer mode)

- Measuring the pulse width by using one input signal of the TI000 pin (free-running timer mode)

- Measuring the pulse width by using one input signal of the TI000 pin (clear & start mode entered by the TI000 pin valid edge input)

Caution Do not select the TI000 valid edge as the count clock when measuring the pulse width.

Remarks 1. For the setting of the I/O pins, see 6.3 (6) Port mode register 3 (PM3).

- 2. For how to enable the INTTM000 signal interrupt, see CHAPTER 19 INTERRUPT FUNCTIONS.

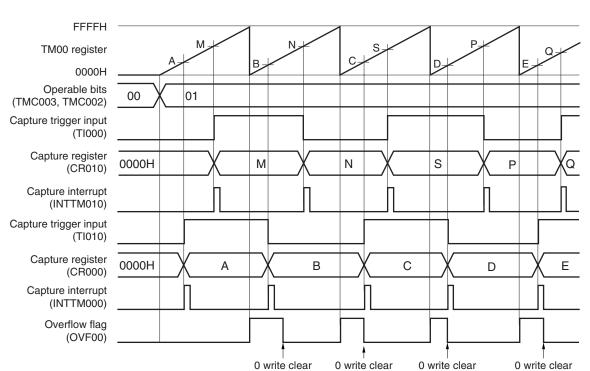

- (1) Measuring the pulse width by using two input signals of the TI000 and TI010 pins (free-running timer mode)

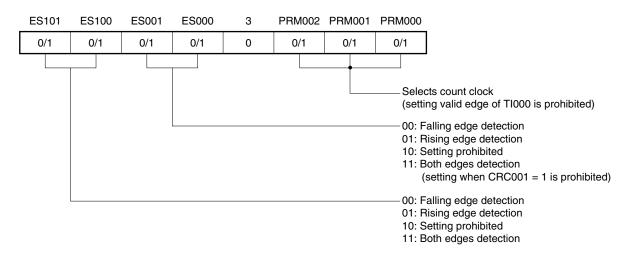

Set the free-running timer mode (TMC003 and TMC002 = 01). When the valid edge of the TI000 pin is detected, the count value of TM00 is captured to CR010. When the valid edge of the TI010 pin is detected, the count value of TM00 is captured to CR000. Specify detection of both the edges of the TI000 and TI010 pins.

By this measurement method, the previous count value is subtracted from the count value captured by the edge of each input signal. Therefore, save the previously captured value to a separate register in advance.

If an overflow occurs, the value becomes negative if the previously captured value is simply subtracted from the current captured value and, therefore, a borrow occurs (bit 0 (CY) of the program status word (PSW) is set to 1). If this happens, ignore CY and take the calculated value as the pulse width. In addition, clear bit 0 (OVF00) of 16-bit timer mode control register 00 (TMC00) to 0.

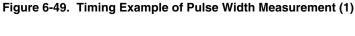

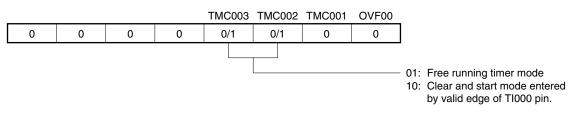

• TMC00 = 04H, PRM00 = F0H, CRC00 = 05H

# Figure 6-52. Example of Register Settings for Pulse Width Measurement (1/2)

# (a) 16-bit timer mode control register 00 (TMC00)

# (b) Capture/compare control register 00 (CRC00)

# (c) 16-bit timer output control register 00 (TOC00)

|   | OSPT00 | OSPE00 | TOC004 | LVS00 | LVR00 | TOC001 | TOE00 |

|---|--------|--------|--------|-------|-------|--------|-------|

| 0 | 0      | 0      | 0      | 0     | 0     | 0      | 0     |

#### (d) Prescaler mode register 00 (PRM00)

# (7) Operation of OVF00 flag

# (a) Setting OVF00 flag (1)

The OVF00 flag is set to 1 in the following case, as well as when TM00 overflows.

Select the clear & start mode entered upon a match between TM00 and CR000.

Set CR000 to FFFFH.

$\downarrow$

↓

When TM00 matches CR000 and TM00 is cleared from FFFFH to 0000H

| Count pulse |       |       |                          | 1 |

|-------------|-------|-------|--------------------------|---|

| CR000       | FFFFH |       |                          |   |

| ТМ00        | FFFEH | Xfffh | <u>Х 0000н X 0001н X</u> |   |

| OVF00       |       |       |                          |   |

| INTTM000    |       |       |                          |   |

# Figure 6-61. Operation Timing of OVF00 Flag

# (b) Clearing OVF00 flag

Even if the OVF00 flag is cleared to 0 after TM00 overflows and before the next count clock is counted (before the value of TM00 becomes 0001H), it is set to 1 again and clearing is invalid.

#### (8) One-shot pulse output

One-shot pulse output operates correctly in the free-running timer mode or the clear & start mode entered by the TI000 pin valid edge. The one-shot pulse cannot be output in the clear & start mode entered upon a match between TM00 and CR000.

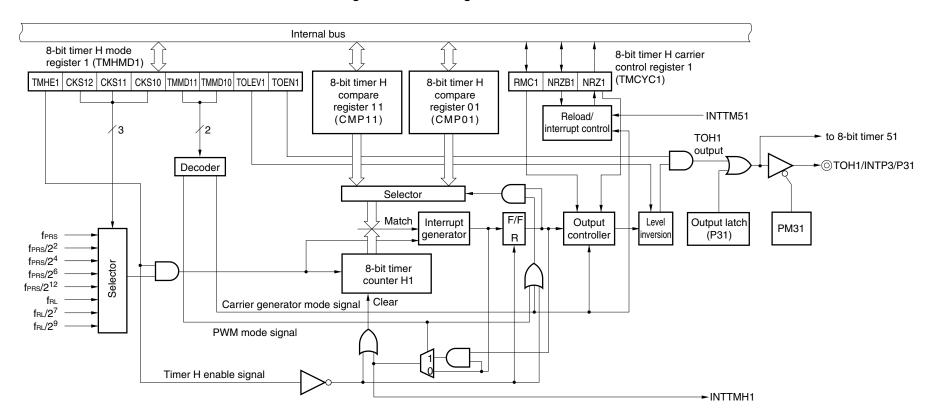

CHAPTER 8 8-BIT TIMERS H0, H1, AND H2

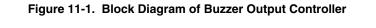

# CHAPTER 11 BUZZER OUTPUT CONTROLLER

# **11.1 Functions of Buzzer Output Controller**

The buzzer output is intended for square-wave output of buzzer frequency selected with CKS. Figure 11-1 shows the block diagram of buzzer output controller.

# (d) Continuous transmission

The next transmit data can be written to transmit buffer register 6 (TXB6) as soon as transmit shift register 6 (TXS6) has started its shift operation. Consequently, even while the INTST6 interrupt is being serviced after transmission of one data frame, data can be continuously transmitted and an efficient communication rate can be realized. In addition, the TXB6 register can be efficiently written twice (2 bytes) without having to wait for the transmission time of one data frame, by reading bit 0 (TXSF6) of asynchronous serial interface transmission status register 6 (ASIF6) when the transmission completion interrupt has occurred.

To transmit data continuously, be sure to reference the ASIF6 register to check the transmission status and whether the TXB6 register can be written, and then write the data.

- Cautions 1. The TXBF6 and TXSF6 flags of the ASIF6 register change from "10" to "11", and to "01" during continuous transmission. To check the status, therefore, do not use a combination of the TXBF6 and TXSF6 flags for judgment. Read only the TXBF6 flag when executing continuous transmission.

- 2. When the device is use in LIN communication operation, the continuous transmission function cannot be used. Make sure that asynchronous serial interface transmission status register 6 (ASIF6) is 00H before writing transmit data to transmit buffer register 6 (TXB6).

| TXBF6 | Writing to TXB6 Register |

|-------|--------------------------|

| 0     | Writing enabled          |

| 1     | Writing disabled         |

Caution To transmit data continuously, write the first transmit data (first byte) to the TXB6 register. Be sure to check that the TXBF6 flag is "0". If so, write the next transmit data (second byte) to the TXB6 register. If data is written to the TXB6 register while the TXBF6 flag is "1", the transmit data cannot be guaranteed.

The communication status can be checked using the TXSF6 flag.

| TXSF6 | Transmission Status          |  |

|-------|------------------------------|--|

| 0     | Transmission is completed.   |  |

| 1     | Transmission is in progress. |  |

- Cautions 1. To initialize the transmission unit upon completion of continuous transmission, be sure to check that the TXSF6 flag is "0" after generation of the transmission completion interrupt, and then execute initialization. If initialization is executed while the TXSF6 flag is "1", the transmit data cannot be guaranteed.

- 2. During continuous transmission, the next transmission may complete before execution of INTST6 interrupt servicing after transmission of one data frame. As a countermeasure, detection can be performed by developing a program that can count the number of transmit data and by referencing the TXSF6 flag.

#### 16.7 Display Modes

COM0

Select

Deselect

# 16.7.1 Static display example

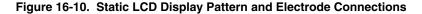

Figure 16-11 shows how the three-digit LCD panel having the display pattern shown in Figure 16-10 is connected to the segment signals (SEG0 to SEG23) and the common signal (COM0) of the 78K0/LD3 chip. This example displays data "12.3" in the LCD panel. The contents of the display data memory (FA40H to FA57H) correspond to this display.

The following description focuses on numeral "2." ( ⊇.) displayed in the second digit. To display "2." in the LCD panel, it is necessary to apply the select or deselect voltage to the SEG8 to SEG15 pins according to Table 16-5 at the timing of the common signal COM0; see **Figure 16-10** for the relationship between the segment signals and LCD segments.

Segment SEG8 SEG9 SEG10 SEG11 SEG12 SEG13 SEG14 SEG15 Common

Select

Table 16-5. Select and Deselect Voltages (COM0)

According to Table 16-5, it is determined that the bit-0 pattern of the display data memory locations (FA48H to FA4FH) must be 10110111.

Select

Deselect

Select

Select

Select

Figure 16-12 shows the LCD drive waveforms of SEG11 and SEG12, and COM0. When the select voltage is applied to SEG11 at the timing of COM0, an alternate rectangle waveform, +VLCD/-VLCD, is generated to turn on the corresponding LCD segment.

COM1 to COM3 are supplied with the same waveform as for COM0. So, COM0 to COM3 may be connected together to increase the driving capacity.

Remark n = 0 to 2

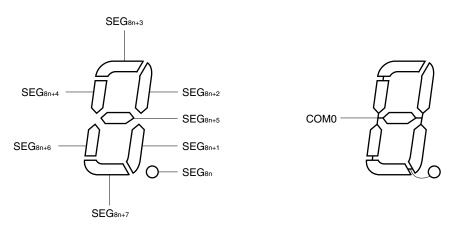

# (4) Remote controller receive GPHS compare register (RMGPHS)

This register is used to detect the high level of a remote controller guide pulse (short side). RMGPHS is set with an 8-bit memory manipulation instruction. Reset signal generation sets RMGPHS to 00H.

# (5) Remote controller receive GPHL compare register (RMGPHL)

This register is used to detect the high level of a remote controller guide pulse (long side). RMGPHL is set with an 8-bit memory manipulation instruction. Reset signal generation sets RMGPHL to 00H.

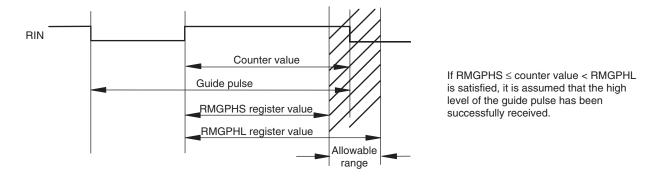

# (6) Remote controller DLS compare register (RMDLS)

This register is used to detect the low level of a remote controller data (short side). RMDLS is set with an 8-bit memory manipulation instruction. Reset signal generation sets RMDLS to 00H.

# (7) Remote controller receive DLL compare register (RMDLL)

This register is used to detect the low level of a remote controller data (long side). RMDLL is set with an 8-bit memory manipulation instruction. Reset signal generation sets RMDLL to 00H.

If RMDLS  $\leq$  counter value < RMDLL is satisfied, it is assumed that the low level of data 0 or data 1 has been successfully received.

#### **19.4 Interrupt Servicing Operations**

#### 19.4.1 Maskable interrupt acknowledgment

A maskable interrupt becomes acknowledgeable when the interrupt request flag is set to 1 and the mask (MK) flag corresponding to that interrupt request is cleared to 0. A vectored interrupt request is acknowledged if interrupts are in the interrupt enabled state (when the IE flag is set to 1). However, a low-priority interrupt request is not acknowledged during servicing of a higher priority interrupt request (when the ISP flag is reset to 0).

The times from generation of a maskable interrupt request until vectored interrupt servicing is performed are listed in Table 19-4 below.

For the interrupt request acknowledgment timing, see Figures 19-8 and 19-9.

|                      | Minimum Time | Maximum Time <sup>Note</sup> |

|----------------------|--------------|------------------------------|

| When $\times$ PR = 0 | 7 clocks     | 32 clocks                    |

| When ××PR = 1        | 8 clocks     | 33 clocks                    |

|  | Table 19-4. | Time from Generation | of Maskable Interr | upt Until Servicing |

|--|-------------|----------------------|--------------------|---------------------|

|--|-------------|----------------------|--------------------|---------------------|

Note If an interrupt request is generated just before a divide instruction, the wait time becomes longer.

Remark 1 clock: 1/fcpu (fcpu: CPU clock)

If two or more maskable interrupt requests are generated simultaneously, the request with a higher priority level specified in the priority specification flag is acknowledged first. If two or more interrupts requests have the same priority level, the request with the highest default priority is acknowledged first.

An interrupt request that is held pending is acknowledged when it becomes acknowledgeable.

Figure 19-7 shows the interrupt request acknowledgment algorithm.

If a maskable interrupt request is acknowledged, the contents are saved into the stacks in the order of PSW, then PC, the IE flag is reset (0), and the contents of the priority specification flag corresponding to the acknowledged interrupt are transferred to the ISP flag. The vector table data determined for each interrupt request is the loaded into the PC and branched.

Restoring from an interrupt is possible by using the RETI instruction.

#### 19.4.4 Interrupt request hold

There are instructions where, even if an interrupt request is issued for them while another instruction is being executed, request acknowledgment is held pending until the end of execution of the next instruction. These instructions (interrupt request hold instructions) are listed below.

- MOV PSW, #byte

- MOV A, PSW

- MOV PSW, A

- MOV1 PSW. bit, CY

- MOV1 CY, PSW. bit

- AND1 CY, PSW. bit

- OR1 CY, PSW. bit

- XOR1 CY, PSW. bit

- SET1 PSW. bit

- CLR1 PSW. bit

- RETB

- RETI

- PUSH PSW

- POP PSW

- BT PSW. bit, \$addr16

- BF PSW. bit, \$addr16

- BTCLR PSW. bit, \$addr16

- El

- DI

- Manipulation instructions for the IF0L, IF0H, IF1L, IF1H, MK0L, MK0H, MK1L, MK1H, PR0L, PR0H, PR1L, and PR1H registers.

- Caution The BRK instruction is not one of the above-listed interrupt request hold instructions. However, the software interrupt activated by executing the BRK instruction causes the IE flag to be cleared. Therefore, even if a maskable interrupt request is generated during execution of the BRK instruction, the interrupt request is not acknowledged.

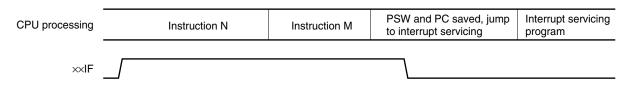

Figure 19-11 shows the timing at which interrupt requests are held pending.

#### Figure 19-11. Interrupt Request Hold

Remarks 1. Instruction N: Interrupt request hold instruction

- 2. Instruction M: Instruction other than interrupt request hold instruction

- 3. The XXPR (priority level) values do not affect the operation of XXIF (interrupt request).

# **CHAPTER 25 OPTION BYTE**

# 25.1 Functions of Option Bytes

The flash memory at 0080H to 0084H of the 78K0/LD3 is an option byte area. When power is turned on or when the device is restarted from the reset status, the device automatically references the option bytes and sets specified functions. When using the product, be sure to set the following functions by using the option bytes.

When the boot swap operation is used during self-programming, 0080H to 0084H are switched to 1080H to 1084H. Therefore, set values that are the same as those of 0080H to 0084H to 1080H to 1084H in advance.

# Caution Be sure to set 00H to 0082H and 0083H (0082H/1082H and 0083H/1083H when the boot swap function is used).

#### (1) 0080H/1080H

- O Internal low-speed oscillator operation

- · Can be stopped by software

- Cannot be stopped

- O Watchdog timer interval time setting

- O Watchdog timer counter operation

- Enabled counter operation

- Disabled counter operation

- O Watchdog timer window open period setting

# Caution Set a value that is the same as that of 0080H to 1080H because 0080H and 1080H are switched during the boot swap operation.

#### (2) 0081H/1081H

- O Selecting POC mode

- During 2.7 V/1.59 V POC mode operation (POCMODE = 1)

The device is in the reset state upon power application and until the supply voltage reaches 2.7 V (TYP.). It is released from the reset state when the voltage exceeds 2.7 V (TYP.). After that, POC is not detected at 2.7 V but is detected at 1.59 V (TYP.).

If the supply voltage rises to 1.8 V after power application at a pace slower than 0.5 V/ms (MIN.), use of the 2.7 V/1.59 V POC mode is recommended.

• During 1.59 V POC mode operation (POCMODE = 0)

The device is in the reset state upon power application and until the supply voltage reaches 1.59 V (TYP.). It is released from the reset state when the voltage exceeds 1.59 V (TYP.). After that, POC is detected at 1.59 V (TYP.), in the same manner as on power application.

Caution POCMODE can only be written by using a dedicated flash memory programmer. It cannot be set during self-programming or boot swap operation during self-programming (at this time, 1.59 V POC mode (default) is set). However, because the value of 1081H is copied to 0081H during the boot swap operation, it is recommended to set a value that is the same as that of 0081H to 1081H when the boot swap function is used.

## 26.5 Connection of Pins on Board

To write the flash memory on-board, connectors that connect the dedicated flash memory programmer must be provided on the target system. First provide a function that selects the normal operation mode or flash memory programming mode on the board.

When the flash memory programming mode is set, all the pins not used for programming the flash memory are in the same status as immediately after reset. Therefore, if the external device does not recognize the state immediately after reset, the pins must be handled as described below.

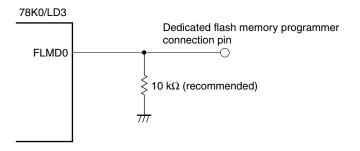

#### 26.5.1 FLMD0 pin

In the normal operation mode, 0 V is input to the FLMD0 pin. In the flash memory programming mode, the V<sub>DD</sub> write voltage is supplied to the FLMD0 pin. An FLMD0 pin connection example is shown below.

Figure 26-7. FLMD0 Pin Connection Example

#### 26.5.2 Serial interface pins

The pins used by each serial interface are listed below.

| Table 26-4. | Pins Used by Each Serial Interface |

|-------------|------------------------------------|

|             |                                    |

| Serial Interface | Pins Used         |

|------------------|-------------------|

| CSI10            | SO10, SI10, SCK10 |

| UART6            | TxD6, RxD6        |

To connect the dedicated flash memory programmer to the pins of a serial interface that is connected to another device on the board, care must be exercised so that signals do not collide or that the other device does not malfunction.