# E·XFL

#### NXP USA Inc. - MKL15Z128VLH4 Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                      |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 48MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, TSI, UART/USART                        |

| Peripherals                | Brown-out Detect/Reset, DMA, LVD, POR, PWM, WDT                       |

| Number of I/O              | 54                                                                    |

| Program Memory Size        | 128KB (128K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 16K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                          |

| Data Converters            | A/D 16x16b; D/A 1x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-LQFP                                                               |

| Supplier Device Package    | 64-LQFP (10x10)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mkl15z128vlh4 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1 | Orde | ering pa | ırts                                       | 3  |

|---|------|----------|--------------------------------------------|----|

|   | 1.1  | Determ   | nining valid orderable parts               | 3  |

| 2 | Part | identifi | cation                                     | 3  |

|   | 2.1  | Descri   | otion                                      | 3  |

|   | 2.2  | Format   | t                                          | 3  |

|   | 2.3  | Fields.  |                                            | 3  |

|   | 2.4  | Examp    | le                                         | 4  |

| 3 | Terr | ninolog  | y and guidelines                           | 4  |

|   | 3.1  | Definiti | on: Operating requirement                  | 4  |

|   | 3.2  | Definiti | on: Operating behavior                     | 4  |

|   | 3.3  | Definiti | on: Attribute                              | 5  |

|   | 3.4  | Definiti | on: Rating                                 | 5  |

|   | 3.5  | Result   | of exceeding a rating                      | 6  |

|   | 3.6  | Relatio  | nship between ratings and operating        |    |

|   |      | require  | ments                                      | 6  |

|   | 3.7  | Guideli  | nes for ratings and operating requirements | 7  |

|   | 3.8  | Definiti | on: Typical value                          | 7  |

|   | 3.9  | Typica   | Value Conditions                           | 8  |

| 4 | Rati | ngs      |                                            | 8  |

|   | 4.1  | Therma   | al handling ratings                        | 8  |

|   | 4.2  | Moistu   | re handling ratings                        | 9  |

|   | 4.3  | ESD h    | andling ratings                            | 9  |

|   | 4.4  | Voltage  | e and current operating ratings            | 9  |

| 5 | Gen  | eral     |                                            | 9  |

|   | 5.1  | AC ele   | ctrical characteristics                    | 9  |

|   | 5.2  | Nonsw    | itching electrical specifications          | 10 |

|   |      | 5.2.1    | Voltage and current operating requirements | 10 |

|   |      | 5.2.2    | LVD and POR operating requirements         | 11 |

|   |      | 5.2.3    | Voltage and current operating behaviors    | 12 |

|   |      | 5.2.4    | Power mode transition operating behaviors  | 13 |

|   |      | 5.2.5    | Power consumption operating behaviors      | 13 |

|   |      | 5.2.6    | EMC radiated emissions operating behaviors | 20 |

|   |      | 5.2.7    | Designing with radiated emissions in mind  | 21 |

|   |      | 5.2.8    | Capacitance attributes                     | 21 |

|   | 5.3  | Switch   | ing specifications21                          |

|---|------|----------|-----------------------------------------------|

|   |      | 5.3.1    | Device clock specifications21                 |

|   |      | 5.3.2    | General Switching Specifications22            |

|   | 5.4  | Therma   | al specifications22                           |

|   |      | 5.4.1    | Thermal operating requirements22              |

|   |      | 5.4.2    | Thermal attributes                            |

| 6 | Peri | pheral c | operating requirements and behaviors23        |

|   | 6.1  | Core m   | nodules23                                     |

|   |      | 6.1.1    | SWD Electricals23                             |

|   | 6.2  | System   | n modules25                                   |

|   | 6.3  | Clock r  | nodules25                                     |

|   |      | 6.3.1    | MCG specifications25                          |

|   |      | 6.3.2    | Oscillator electrical specifications27        |

|   | 6.4  | Memor    | ies and memory interfaces29                   |

|   |      | 6.4.1    | Flash electrical specifications29             |

|   | 6.5  | Securit  | y and integrity modules30                     |

|   | 6.6  | Analog   |                                               |

|   |      | 6.6.1    | ADC electrical specifications31               |

|   |      | 6.6.2    | CMP and 6-bit DAC electrical specifications35 |

|   |      | 6.6.3    | 12-bit DAC electrical characteristics         |

|   | 6.7  | Timers   |                                               |

|   | 6.8  | Comm     | unication interfaces                          |

|   |      | 6.8.1    | SPI switching specifications                  |

|   |      | 6.8.2    | I2C43                                         |

|   |      | 6.8.3    | UART43                                        |

|   | 6.9  | Humar    | n-machine interfaces (HMI)44                  |

|   |      | 6.9.1    | TSI electrical specifications44               |

| 7 | Dim  | ensions  |                                               |

|   | 7.1  | Obtain   | ing package dimensions44                      |

| B | Pinc | out      |                                               |

|   | 8.1  | KL15 S   | Signal Multiplexing and Pin Assignments44     |

|   | 8.2  | KL15 F   | Pinouts47                                     |

| 9 | Rev  | ision Hi | story51                                       |

|   |      |          |                                               |

# 1 Ordering parts

### 1.1 Determining valid orderable parts

Valid orderable part numbers are provided on the web. To determine the orderable part numbers for this device, go to www.freescale.com and perform a part number search for the following device numbers: PKL15 and MKL15

# 2 Part identification

### 2.1 Description

Part numbers for the chip have fields that identify the specific part. You can use the values of these fields to determine the specific part you have received.

# 2.2 Format

Part numbers for this device have the following format:

Q KL## A FFF R T PP CC N

# 2.3 Fields

This table lists the possible values for each field in the part number (not all combinations are valid):

| Field | Description               | Values                                                                                         |

|-------|---------------------------|------------------------------------------------------------------------------------------------|

| Q     | Qualification status      | <ul> <li>M = Fully qualified, general market flow</li> <li>P = Prequalification</li> </ul>     |

| KL##  | Kinetis family            | • KL15                                                                                         |

| A     | Key attribute             | • Z = Cortex-M0+                                                                               |

| FFF   | Program flash memory size | <ul> <li>32 = 32 KB</li> <li>64 = 64 KB</li> <li>128 = 128 KB</li> <li>256 = 256 KB</li> </ul> |

Table continues on the next page ....

# 3.2 Definition: Operating behavior

An *operating behavior* is a specified value or range of values for a technical characteristic that are guaranteed during operation if you meet the operating requirements and any other specified conditions.

### 3.2.1 Example

This is an example of an operating behavior, which is guaranteed if you meet the accompanying operating requirements:

| Symbol          | Description                                  | Min. | Max. | Unit |

|-----------------|----------------------------------------------|------|------|------|

| I <sub>WP</sub> | Digital I/O weak pullup/<br>pulldown current | 10   | 130  | μΑ   |

# 3.3 Definition: Attribute

An *attribute* is a specified value or range of values for a technical characteristic that are guaranteed, regardless of whether you meet the operating requirements.

### 3.3.1 Example

This is an example of an attribute:

| Symbol | Description                        | Min. | Max. | Unit |

|--------|------------------------------------|------|------|------|

| CIN_D  | Input capacitance:<br>digital pins | —    | 7    | pF   |

# 3.4 Definition: Rating

A *rating* is a minimum or maximum value of a technical characteristic that, if exceeded, may cause permanent chip failure:

- Operating ratings apply during operation of the chip.

- *Handling ratings* apply when the chip is not powered.

# 3.9 Typical Value Conditions

Typical values assume you meet the following conditions (or other conditions as specified):

| Symbol          | Description          | Value | Unit |

|-----------------|----------------------|-------|------|

| T <sub>A</sub>  | Ambient temperature  | 25    | ٦°   |

| V <sub>DD</sub> | 3.3 V supply voltage | 3.3   | V    |

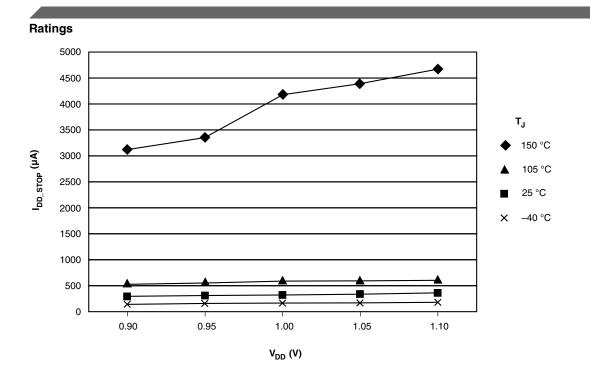

# 4 Ratings

# 4.1 Thermal handling ratings

| Symbol           | Description                   | Min. | Max. | Unit | Notes |

|------------------|-------------------------------|------|------|------|-------|

| T <sub>STG</sub> | Storage temperature           | -55  | 150  | °C   | 1     |

| T <sub>SDR</sub> | Solder temperature, lead-free | _    | 260  | °C   | 2     |

1. Determined according to JEDEC Standard JESD22-A103, High Temperature Storage Life.

2. Determined according to IPC/JEDEC Standard J-STD-020, Moisture/Reflow Sensitivity Classification for Nonhermetic Solid State Surface Mount Devices.

### 4.2 Moisture handling ratings

| Symbol | Description                | Min. | Max. | Unit | Notes |

|--------|----------------------------|------|------|------|-------|

| MSL    | Moisture sensitivity level | _    | 3    | _    | 1     |

1. Determined according to IPC/JEDEC Standard J-STD-020, *Moisture/Reflow Sensitivity Classification for Nonhermetic Solid State Surface Mount Devices*.

# 4.3 ESD handling ratings

| Symbol           | Description                                           | Min.  | Max.  | Unit | Notes |

|------------------|-------------------------------------------------------|-------|-------|------|-------|

| V <sub>HBM</sub> | Electrostatic discharge voltage, human body model     | -2000 | +2000 | V    | 1     |

| V <sub>CDM</sub> | Electrostatic discharge voltage, charged-device model | -500  | +500  | V    | 2     |

| I <sub>LAT</sub> | Latch-up current at ambient temperature of 105°C      | -100  | +100  | mA   |       |

- 1. Determined according to JEDEC Standard JESD22-A114, *Electrostatic Discharge (ESD) Sensitivity Testing Human Body Model (HBM)*.

- 2. Determined according to JEDEC Standard JESD22-C101, Field-Induced Charged-Device Model Test Method for Electrostatic-Discharge-Withstand Thresholds of Microelectronic Components.

# 4.4 Voltage and current operating ratings

| Symbol           | Description                                                               | Min.                  | Max.                  | Unit |

|------------------|---------------------------------------------------------------------------|-----------------------|-----------------------|------|

| V <sub>DD</sub>  | Digital supply voltage                                                    | -0.3                  | 3.8                   | V    |

| I <sub>DD</sub>  | Digital supply current                                                    | —                     | 120                   | mA   |

| V <sub>DIO</sub> | Digital pin input voltage (except RESET)                                  | -0.3                  | 3.6                   | V    |

| V <sub>AIO</sub> | Analog pins <sup>1</sup> and RESET pin input voltage                      | -0.3                  | V <sub>DD</sub> + 0.3 | V    |

| Ι <sub>D</sub>   | Instantaneous maximum current single pin limit (applies to all port pins) | -25                   | 25                    | mA   |

| V <sub>DDA</sub> | Analog supply voltage                                                     | V <sub>DD</sub> – 0.3 | V <sub>DD</sub> + 0.3 | V    |

1. Analog pins are defined as pins that do not have an associated general purpose I/O port function.

# 5 General

General

# 5.1 AC electrical characteristics

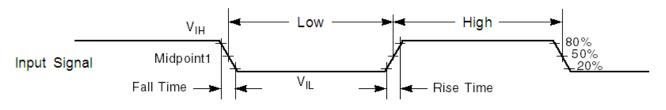

Unless otherwise specified, propagation delays are measured from the 50% to the 50% point, and rise and fall times are measured at the 20% and 80% points, as shown in the following figure.

The midpoint is  $V_{IL}$  +  $(V_{IH} - V_{IL})/2$ .

### Figure 1. Input signal measurement reference

All digital I/O switching characteristics, unless otherwise specified, assumes:

- 1. output pins

- have  $C_L=30$  pF loads,

- are slew rate disabled, and

- are normal drive strength

# 5.2 Nonswitching electrical specifications

### 5.2.1 Voltage and current operating requirements

Table 1. Voltage and current operating requirements

| Symbol             | Description                                                  | Min.                 | Max.                 | Unit | Notes |

|--------------------|--------------------------------------------------------------|----------------------|----------------------|------|-------|

| V <sub>DD</sub>    | Supply voltage                                               | 1.71                 | 3.6                  | V    |       |

| V <sub>DDA</sub>   | Analog supply voltage                                        | 1.71                 | 3.6                  | V    |       |

| $V_{DD} - V_{DDA}$ | V <sub>DD</sub> -to-V <sub>DDA</sub> differential voltage    | -0.1                 | 0.1                  | V    |       |

| $V_{SS} - V_{SSA}$ | V <sub>SS</sub> -to-V <sub>SSA</sub> differential voltage    | -0.1                 | 0.1                  | V    |       |

| V <sub>IH</sub>    | Input high voltage                                           |                      |                      |      |       |

|                    | • $2.7 \text{ V} \le \text{V}_{\text{DD}} \le 3.6 \text{ V}$ | $0.7 \times V_{DD}$  | —                    | V    |       |

|                    | • $1.7 \text{ V} \le \text{V}_{\text{DD}} \le 2.7 \text{ V}$ | $0.75 \times V_{DD}$ | _                    | V    |       |

| V <sub>IL</sub>    | Input low voltage                                            |                      |                      |      |       |

|                    | • $2.7 \text{ V} \le \text{V}_{\text{DD}} \le 3.6 \text{ V}$ | —                    | $0.35 \times V_{DD}$ | V    |       |

|                    | • $1.7 \text{ V} \le \text{V}_{\text{DD}} \le 2.7 \text{ V}$ | _                    | $0.3 \times V_{DD}$  | V    |       |

| V <sub>HYS</sub>   | Input hysteresis                                             | $0.06 \times V_{DD}$ | —                    | V    |       |

Table continues on the next page...

| Symbol              | Description                                                                                                                                                                                                                                              | Min.     | Max.    | Unit | Notes |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------|------|-------|

| I <sub>ICDIO</sub>  | Digital pin negative DC injection current — single pin<br>• V <sub>IN</sub> < V <sub>SS</sub> -0.3V                                                                                                                                                      | -5       | _       | mA   | 1     |

| I <sub>ICAIO</sub>  | <ul> <li>Analog<sup>2</sup> pin DC injection current — single pin</li> <li>V<sub>IN</sub> &lt; V<sub>SS</sub>-0.3V (Negative current injection)</li> <li>V<sub>IN</sub> &gt; V<sub>DD</sub>+0.3V (Positive current injection)</li> </ul>                 | -5       | <br>+5  | mA   | 3     |

| I <sub>ICcont</sub> | <ul> <li>Contiguous pin DC injection current —regional limit, includes sum of negative injection currents or sum of positive injection currents of 16 contiguous pins</li> <li>Negative current injection</li> <li>Positive current injection</li> </ul> | -25<br>— | <br>+25 | mA   |       |

| V <sub>RAM</sub>    | V <sub>DD</sub> voltage required to retain RAM                                                                                                                                                                                                           | 1.2      | —       | V    |       |

#### Table 1. Voltage and current operating requirements (continued)

- All digital I/O pins are internally clamped to V<sub>SS</sub> through a ESD protection diode. There is no diode connection to V<sub>DD</sub>. If V<sub>IN</sub> greater than V<sub>DIO\_MIN</sub> (=V<sub>SS</sub>-0.3V) is observed, then there is no need to provide current limiting resistors at the pads. If this limit cannot be observed then a current limiting resistor is required. The negative DC injection current limiting resistor is calculated as R=(V<sub>DIO\_MIN</sub>-V<sub>IN</sub>)/|I<sub>IC</sub>|.

- 2. Analog pins are defined as pins that do not have an associated general purpose I/O port function.

- 3. All analog pins are internally clamped to  $V_{SS}$  and  $V_{DD}$  through ESD protection diodes. If  $V_{IN}$  is greater than  $V_{AIO\_MIN}$  (= $V_{SS}$ -0.3V) and  $V_{IN}$  is less than  $V_{AIO\_MAX}$ (= $V_{DD}$ +0.3V) is observed, then there is no need to provide current limiting resistors at the pads. If these limits cannot be observed then a current limiting resistor is required. The negative DC injection current limiting resistor is calculated as R=( $V_{AIO\_MIN}$ - $V_{IN}$ )/II<sub>IC</sub>I. The positive injection current limiting resistor is calculated as R=( $V_{AIO\_MIN}$ - $V_{IN}$ )/II<sub>IC</sub>I. The positive injection current limiting resistor is calculated as R=( $V_{IN}$ - $V_{AIO\_MAX}$ )/II<sub>IC</sub>I. Select the larger of these two calculated resistances.

### 5.2.2 LVD and POR operating requirements

| Symbol             | Description                                                 | Min. | Тур. | Max. | Unit | Notes |

|--------------------|-------------------------------------------------------------|------|------|------|------|-------|

| V <sub>POR</sub>   | Falling VDD POR detect voltage                              | 0.8  | 1.1  | 1.5  | V    |       |

| V <sub>LVDH</sub>  | Falling low-voltage detect threshold — high range (LVDV=01) | 2.48 | 2.56 | 2.64 | V    |       |

|                    | Low-voltage warning thresholds — high range                 |      |      |      |      | 1     |

| V <sub>LVW1H</sub> | Level 1 falling (LVWV=00)                                   | 2.62 | 2.70 | 2.78 | V    |       |

| V <sub>LVW2H</sub> | Level 2 falling (LVWV=01)                                   | 2.72 | 2.80 | 2.88 | V    |       |

| V <sub>LVW3H</sub> | Level 3 falling (LVWV=10)                                   | 2.82 | 2.90 | 2.98 | V    |       |

| V <sub>LVW4H</sub> | Level 4 falling (LVWV=11)                                   | 2.92 | 3.00 | 3.08 | V    |       |

| V <sub>HYSH</sub>  | Low-voltage inhibit reset/recover hysteresis — high range   | _    | ±60  | _    | mV   |       |

| V <sub>LVDL</sub>  | Falling low-voltage detect threshold — low range (LVDV=00)  | 1.54 | 1.60 | 1.66 | V    |       |

Table continues on the next page...

| Symbol                | Description                                                                | Min. | Тур.       | Max.         | Unit | Notes |

|-----------------------|----------------------------------------------------------------------------|------|------------|--------------|------|-------|

| I <sub>DD_VLLS0</sub> | Very low-leakage stop mode 0 current<br>(SMC_STOPCTRL[PORPO] = 0) at 3.0 V |      | 001        | 0.40         | nA   |       |

|                       | at 25 °C                                                                   |      | 381<br>956 | 943<br>11760 |      |       |

|                       | at 50 °C                                                                   | _    | 2370       | 13260        |      |       |

|                       | at 70 °C                                                                   | _    | 4800       | 15700        |      |       |

|                       | at 85 °C                                                                   | _    | 12410      | 23480        |      |       |

|                       | at 105 °C                                                                  |      |            |              |      |       |

| I <sub>DD_VLLS0</sub> | Very low-leakage stop mode 0 current<br>(SMC_STOPCTRL[PORPO] = 1) at 3.0 V | _    | 176        | 860          |      | 6     |

|                       | at 25 °C                                                                   | _    | 760        | 3577         | nA   |       |

|                       | at 50 °C                                                                   | _    | 2120       | 11660        |      |       |

|                       | at 70 °C                                                                   | _    | 4500       | 18450        |      |       |

|                       | at 85 °C                                                                   | _    | 12130      | 22441        |      |       |

|                       | at 105 °C                                                                  |      |            |              |      |       |

#### Table 5. Power consumption operating behaviors (continued)

1. The analog supply current is the sum of the active or disabled current for each of the analog modules on the device. See each module's specification for its supply current.

- 2. MCG configured for PEE mode. CoreMark benchmark compiled using Keil 4.54 with optimization level 3, optimized for time.

- 3. MCG configured for FEI mode.

- 4. Incremental current consumption from peripheral activity is not included.

- 5. MCG configured for BLPI mode.

- 6. No brownout

#### Table 6. Low power mode peripheral adders — typical value

| Symbol        | Description                                                                                                      |     | Temperature (°C) |     |     |     |     | Unit |

|---------------|------------------------------------------------------------------------------------------------------------------|-----|------------------|-----|-----|-----|-----|------|

|               |                                                                                                                  | -40 | 25               | 50  | 70  | 85  | 105 |      |

| IIREFSTEN4MHz | 4 MHz internal reference clock (IRC)<br>adder. Measured by entering STOP or<br>VLPS mode with 4 MHz IRC enabled. | 56  | 56               | 56  | 56  | 56  | 56  | μA   |

| IREFSTEN32KHz | 32 kHz internal reference clock (IRC)<br>adder. Measured by entering STOP<br>mode with the 32 kHz IRC enabled.   | 52  | 52               | 52  | 52  | 52  | 52  | μA   |

| IEREFSTEN4MHz | External 4MHz crystal clock adder.<br>Measured by entering STOP or VLPS<br>mode with the crystal enabled.        | 206 | 228              | 237 | 245 | 251 | 258 | uA   |

Table continues on the next page ...

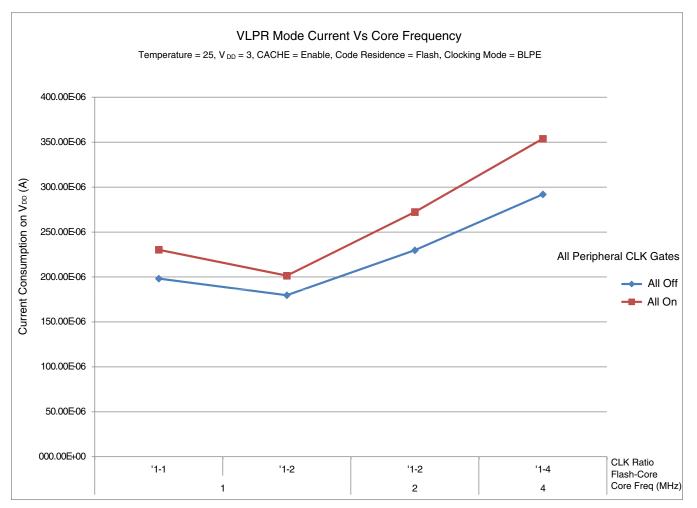

#### General

Figure 3. VLPR mode current vs. core frequency

### 5.2.6 EMC radiated emissions operating behaviors

# Table 7. EMC radiated emissions operating behaviors for 64-pin LQFP package

| Symbol           | Description                        | Frequency<br>band (MHz) | Тур. | Unit | Notes |

|------------------|------------------------------------|-------------------------|------|------|-------|

| V <sub>RE1</sub> | Radiated emissions voltage, band 1 | 0.15–50                 | 13   | dBµV | 1, 2  |

| V <sub>RE2</sub> | Radiated emissions voltage, band 2 | 50–150                  | 15   | dBµV |       |

| V <sub>RE3</sub> | Radiated emissions voltage, band 3 | 150–500                 | 12   | dBµV |       |

| V <sub>RE4</sub> | Radiated emissions voltage, band 4 | 500–1000                | 7    | dBµV |       |

| $V_{RE\_IEC}$    | IEC level                          | 0.15–1000               | М    | —    | 2, 3  |

Determined according to IEC Standard 61967-1, Integrated Circuits - Measurement of Electromagnetic Emissions, 150 kHz to 1 GHz Part 1: General Conditions and Definitions and IEC Standard 61967-2, Integrated Circuits - Measurement of Electromagnetic Emissions, 150 kHz to 1 GHz Part 2: Measurement of Radiated Emissions – TEM Cell and Wideband TEM Cell Method. Measurements were made while the microcontroller was running basic application code. The reported emission level is the value of the maximum measured emission, rounded up to the next whole number, from among the measured orientations in each frequency range.

### 5.4.2 Thermal attributes

| Board type        | Symbol            | Description                                                                                              | 80<br>LQFP | 64<br>LQFP | 48 QFN | 32 QFN | Unit | Notes |

|-------------------|-------------------|----------------------------------------------------------------------------------------------------------|------------|------------|--------|--------|------|-------|

| Single-layer (1S) | R <sub>θJA</sub>  | Thermal resistance, junction<br>to ambient (natural<br>convection)                                       | 70         | 71         | 84     | 92     | °C/W | 1     |

| Four-layer (2s2p) | R <sub>θJA</sub>  | Thermal resistance, junction<br>to ambient (natural<br>convection)                                       | 53         | 52         | 28     | 33     | °C/W |       |

| Single-layer (1S) | R <sub>θJMA</sub> | Thermal resistance, junction<br>to ambient (200 ft./min. air<br>speed)                                   | _          | 59         | 69     | 75     | °C/W |       |

| Four-layer (2s2p) | R <sub>θJMA</sub> | Thermal resistance, junction<br>to ambient (200 ft./min. air<br>speed)                                   | _          | 46         | 22     | 27     | °C/W |       |

| _                 | R <sub>θJB</sub>  | Thermal resistance, junction to board                                                                    | 34         | 34         | 10     | 12     | °C/W | 2     |

| _                 | R <sub>θJC</sub>  | Thermal resistance, junction to case                                                                     | 15         | 20         | 2.0    | 1.8    | °C/W | 3     |

|                   | $\Psi_{JT}$       | Thermal characterization<br>parameter, junction to<br>package top outside center<br>(natural convection) | 0.6        | 5          | 5.0    | 8      | °C/W | 4     |

Table 10. Thermal attributes

- 1. Determined according to JEDEC Standard JESD51-2, Integrated Circuits Thermal Test Method Environmental Conditions —Natural Convection (Still Air), or EIA/JEDEC Standard JESD51-6, Integrated Circuit Thermal Test Method Environmental Conditions—Forced Convection (Moving Air).

- 2. Determined according to JEDEC Standard JESD51-8, Integrated Circuit Thermal Test Method Environmental Conditions —Junction-to-Board.

- 3. Determined according to Method 1012.1 of MIL-STD 883, *Test Method Standard, Microcircuits*, with the cold plate temperature used for the case temperature. The value includes the thermal resistance of the interface material between the top of the package and the cold plate.

- 4. Determined according to JEDEC Standard JESD51-2, Integrated Circuits Thermal Test Method Environmental Conditions —Natural Convection (Still Air).

# 6 Peripheral operating requirements and behaviors

### 6.1 Core modules

### 6.1.1 SWD Electricals

#### Table 11. SWD full voltage range electricals

| Symbol | Description       | Min. | Max. | Unit |

|--------|-------------------|------|------|------|

|        | Operating voltage | 1.71 | 3.6  | V    |

Table continues on the next page...

#### Peripheral operating requirements and behaviors

| Symbol                   | Description                                                                      |                                                                                      | Min.   | Тур.      | Max.                                                          | Unit     | Notes |

|--------------------------|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--------|-----------|---------------------------------------------------------------|----------|-------|

| f <sub>dco_t_DMX32</sub> | DCO output<br>frequency                                                          | Low range (DRS = 00)<br>732 × f <sub>fll_ref</sub>                                   | —      | 23.99     | -                                                             | MHz      | 5, 6  |

|                          |                                                                                  | Mid range (DRS = 01)<br>1464 $\times f_{fll ref}$                                    | _      | 47.97     | -                                                             | MHz      | -     |

| J <sub>cyc_fll</sub>     | FLL period jitter<br>• f <sub>VCO</sub> = 48 M                                   | _                                                                                    | _      | 180       | -                                                             | ps       | 7     |

| t <sub>fll_acquire</sub> |                                                                                  | ncy acquisition time                                                                 | _      | _         | 1                                                             | ms       | 8     |

|                          |                                                                                  | PL                                                                                   | L      |           |                                                               |          |       |

| f <sub>vco</sub>         | VCO operating fre                                                                | quency                                                                               | 48.0   | _         | 100                                                           | MHz      |       |

| I <sub>pll</sub>         | PLL operating cur<br>PLL at 96 M<br>MHz, VDIV                                    | rent<br>Hz ( $f_{osc_{hi_1}} = 8 \text{ MHz}, f_{pll_{ref}} = 2$<br>multiplier = 48) | _      | 1060      | -                                                             | μΑ       | 9     |

| I <sub>pll</sub>         | PLL operating cur<br>PLL at 48 M<br>MHz, VDIV                                    | rent<br>Hz ( $f_{osc_{hi_1}} = 8 \text{ MHz}, f_{pll_{ref}} = 2$<br>multiplier = 24) | _      | 600       | -                                                             | μΑ       | 9     |

| f <sub>pll_ref</sub>     | PLL reference free                                                               | quency range                                                                         | 2.0    | —         | 4.0                                                           | MHz      |       |

| J <sub>cyc_pll</sub>     | PLL period jitter (F<br>• f <sub>vco</sub> = 48 MH<br>• f <sub>vco</sub> = 100 M | lz                                                                                   | _      | 120<br>50 | _                                                             | ps<br>ps | 10    |

| J <sub>acc_pll</sub>     | PLL accumulated<br>• f <sub>vco</sub> = 48 MH                                    | jitter over 1µs (RMS)<br>Iz                                                          |        | 1350      | _                                                             | ps       | 10    |

|                          | • f <sub>vco</sub> = 100 M                                                       | Hz                                                                                   | _      | 600       | _                                                             | ps       |       |

| D <sub>lock</sub>        | Lock entry frequer                                                               | ncy tolerance                                                                        | ± 1.49 | —         | ± 2.98                                                        | %        |       |

| D <sub>unl</sub>         | Lock exit frequence                                                              | y tolerance                                                                          | ± 4.47 | —         | ± 5.97                                                        | %        |       |

| t <sub>pll_lock</sub>    | Lock detector dete                                                               | ection time                                                                          | _      | —         | 150 × 10 <sup>-6</sup><br>+ 1075(1/<br>f <sub>pll_ref</sub> ) | S        | 11    |

#### Table 12. MCG specifications (continued)

- 1. This parameter is measured with the internal reference (slow clock) being used as a reference to the FLL (FEI clock mode).

- 2. The deviation is relative to the factory trimmed frequency at nominal  $V_{DD}$  and 25 °C,  $f_{ints_{-}ft}$ .

- 3. These typical values listed are with the slow internal reference clock (FEI) using factory trim and DMX32 = 0.

- The resulting system clock frequencies must not exceed their maximum specified values. The DCO frequency deviation (Δf<sub>dco t</sub>) over voltage and temperature must be considered.

- 5. These typical values listed are with the slow internal reference clock (FEI) using factory trim and DMX32 = 1.

- 6. The resulting clock frequency must not exceed the maximum specified clock frequency of the device.

- 7. This specification is based on standard deviation (RMS) of period or frequency.

- 8. This specification applies to any time the FLL reference source or reference divider is changed, trim value is changed, DMX32 bit is changed, DRS bits are changed, or changing from FLL disabled (BLPE, BLPI) to FLL enabled (FEI, FEE, FBE, FBI). If a crystal/resonator is being used as the reference, this specification assumes it is already running.

9. Excludes any oscillator currents that are also consuming power while PLL is in operation.

- 10. This specification was obtained using a Freescale developed PCB. PLL jitter is dependent on the noise characteristics of each PCB and results will vary.

- 11. This specification applies to any time the PLL VCO divider or reference divider is changed, or changing from PLL disabled (BLPE, BLPI) to PLL enabled (PBE, PEE). If a crystal/resonator is being used as the reference, this specification assumes it is already running.

Peripheral operating requirements and behaviors

### 6.4.1.2 Flash timing specifications — commands Table 16. Flash command timing specifications

| Symbol                | Description                                   | Min. | Тур. | Max. | Unit | Notes |

|-----------------------|-----------------------------------------------|------|------|------|------|-------|

| t <sub>rd1sec1k</sub> | Read 1s Section execution time (flash sector) | _    | —    | 60   | μs   | 1     |

| t <sub>pgmchk</sub>   | Program Check execution time                  | _    | —    | 45   | μs   | 1     |

| t <sub>rdrsrc</sub>   | Read Resource execution time                  | _    | —    | 30   | μs   | 1     |

| t <sub>pgm4</sub>     | Program Longword execution time               | _    | 65   | 145  | μs   |       |

| t <sub>ersscr</sub>   | Erase Flash Sector execution time             | _    | 14   | 114  | ms   | 2     |

| t <sub>rd1all</sub>   | Read 1s All Blocks execution time             | _    | —    | 1.8  | ms   |       |

| t <sub>rdonce</sub>   | Read Once execution time                      | _    | —    | 25   | μs   | 1     |

| t <sub>pgmonce</sub>  | Program Once execution time                   | _    | 65   | _    | μs   |       |

| t <sub>ersall</sub>   | Erase All Blocks execution time               | _    | 62   | 500  | ms   | 2     |

| t <sub>vfykey</sub>   | Verify Backdoor Access Key execution time     | _    | —    | 30   | μs   | 1     |

1. Assumes 25MHz flash clock frequency.

2. Maximum times for erase parameters based on expectations at cycling end-of-life.

#### 6.4.1.3 Flash high voltage current behaviors Table 17. Flash high voltage current behaviors

| Symbol              | Description                                                           | Min. | Тур. | Max. | Unit |

|---------------------|-----------------------------------------------------------------------|------|------|------|------|

| I <sub>DD_PGM</sub> | Average current adder during high voltage flash programming operation | —    | 2.5  | 6.0  | mA   |

| I <sub>DD_ERS</sub> | Average current adder during high voltage flash erase operation       |      | 1.5  | 4.0  | mA   |

### 6.4.1.4 Reliability specifications

#### Table 18. NVM reliability specifications

| Symbol                  | Description                            | Min.    | Typ. <sup>1</sup> | Max. | Unit   | Notes |

|-------------------------|----------------------------------------|---------|-------------------|------|--------|-------|

|                         | Progra                                 | m Flash | _                 |      |        |       |

| t <sub>nvmretp10k</sub> | Data retention after up to 10 K cycles | 5       | 50                | —    | years  |       |

| t <sub>nvmretp1k</sub>  | Data retention after up to 1 K cycles  | 20      | 100               | —    | years  |       |

| n <sub>nvmcycp</sub>    | Cycling endurance                      | 10 K    | 50 K              |      | cycles | 2     |

Typical data retention values are based on measured response accelerated at high temperature and derated to a constant 25°C use profile. Engineering Bulletin EB618 does not apply to this technology. Typical endurance defined in Engineering Bulletin EB619.

2. Cycling endurance represents number of program/erase cycles at -40°C  $\leq$  T<sub>i</sub>  $\leq$  125°C.

# 6.5 Security and integrity modules

There are no specifications necessary for the device's security and integrity modules.

# 6.6 Analog

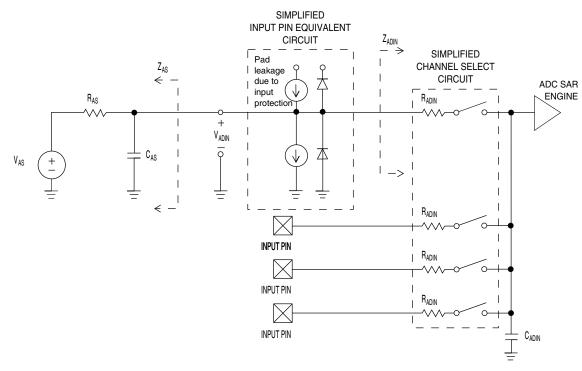

### 6.6.1 ADC electrical specifications

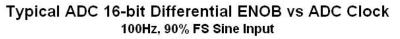

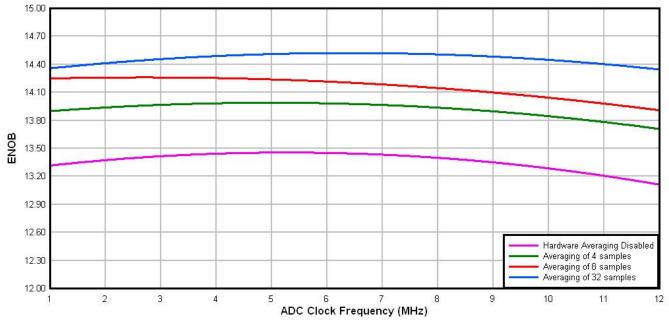

The 16-bit accuracy specifications listed in Table 19 and Table 20 are achievable on the differential pins ADCx\_DP0, ADCx\_DM0.

All other ADC channels meet the 13-bit differential/12-bit single-ended accuracy specifications.

| Symbol                          | Description                                 | Conditions                                                                                                        | Min.              | Typ. <sup>1</sup> | Max.              | Unit | Notes |

|---------------------------------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-------------------|-------------------|-------------------|------|-------|

| V <sub>DDA</sub>                | Supply voltage                              | Absolute                                                                                                          | 1.71              | _                 | 3.6               | V    |       |

| $\Delta V_{DDA}$                | Supply voltage                              | Delta to V <sub>DD</sub> (V <sub>DD</sub> -V <sub>DDA</sub> )                                                     | -100              | 0                 | +100              | mV   | 2     |

| $\Delta V_{SSA}$                | Ground voltage                              | Delta to V <sub>SS</sub> (V <sub>SS</sub> - V <sub>SSA</sub> )                                                    | -100              | 0                 | +100              | mV   | 2     |

| V <sub>REFH</sub>               | ADC reference voltage high                  |                                                                                                                   | 1.13              | V <sub>DDA</sub>  | V <sub>DDA</sub>  | V    | 3     |

| V <sub>REFL</sub>               | V <sub>REFL</sub> ADC reference voltage low |                                                                                                                   | V <sub>SSA</sub>  | V <sub>SSA</sub>  | V <sub>SSA</sub>  | V    | 3     |

| V <sub>ADIN</sub> Input voltage |                                             |                                                                                                                   | V <sub>REFL</sub> | _                 | V <sub>REFH</sub> | V    |       |

| C <sub>ADIN</sub>               | Input capacitance                           | 16-bit mode                                                                                                       | —                 | 8                 | 10                | pF   |       |

|                                 |                                             | • 8-/10-/12-bit modes                                                                                             | —                 | 4                 | 5                 |      |       |

| R <sub>ADIN</sub>               | Input resistance                            |                                                                                                                   | —                 | 2                 | 5                 | kΩ   |       |

| R <sub>AS</sub>                 | Analog source resistance                    | 13-/12-bit modes<br>f <sub>ADCK</sub> < 4 MHz                                                                     | _                 | _                 | 5                 | kΩ   | 4     |

| f <sub>ADCK</sub>               | ADC conversion<br>clock frequency           | ≤ 1312-bit mode                                                                                                   | 1.0               |                   | 18.0              | MHz  | 5     |

| f <sub>ADCK</sub>               | ADC conversion<br>clock frequency           | 16-bit mode                                                                                                       | 2.0               | _                 | 12.0              | MHz  | 5     |

| C <sub>rate</sub>               | ADC conversion<br>rate                      | ≤ 1312 bit modes<br>No ADC hardware averaging<br>Continuous conversions<br>enabled, subsequent<br>conversion time | 20.000            |                   | 818.330           | Ksps | 6     |

#### 6.6.1.1 16-bit ADC operating conditions Table 19. 16-bit ADC operating conditions

Table continues on the next page...

#### Peripheral operating requirements and behaviors

| Symbol            | Description         | Conditions                                                       | Min.   | Typ. <sup>1</sup> | Max.    | Unit | Notes |

|-------------------|---------------------|------------------------------------------------------------------|--------|-------------------|---------|------|-------|

| C <sub>rate</sub> | ADC conversion rate | 16-bit mode<br>No ADC hardware averaging                         | 37.037 | _                 | 461.467 | Ksps | 6     |

|                   |                     | Continuous conversions<br>enabled, subsequent<br>conversion time |        |                   |         |      |       |

Table 19.

16-bit ADC operating conditions (continued)

- 1. Typical values assume V<sub>DDA</sub> = 3.0 V, Temp = 25 °C, f<sub>ADCK</sub> = 1.0 MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

- 2. DC potential difference.

- 3. For packages without dedicated VREFH and VREFL pins,  $V_{REFH}$  is internally tied to  $V_{DDA}$ , and  $V_{REFL}$  is internally tied to  $V_{SSA}$ .

- 4. This resistance is external to MCU. The analog source resistance must be kept as low as possible to achieve the best results. The results in this data sheet were derived from a system which has < 8 Ω analog source resistance. The R<sub>AS</sub>/C<sub>AS</sub> time constant should be kept to < 1ns.</p>

- 5. To use the maximum ADC conversion clock frequency, the ADHSC bit must be set and the ADLPC bit must be clear.

- 6. For guidelines and examples of conversion rate calculation, download the ADC calculator tool

Figure 6. ADC input impedance equivalency diagram

### 6.6.1.2 16-bit ADC electrical characteristics Table 20. 16-bit ADC characteristics (V<sub>REFH</sub> = V<sub>DDA</sub>, V<sub>REFL</sub> = V<sub>SSA</sub>)

| Symbol               | Description    | Conditions <sup>1</sup> | Min.  | Typ. <sup>2</sup> | Max. | Unit | Notes |

|----------------------|----------------|-------------------------|-------|-------------------|------|------|-------|

| I <sub>DDA_ADC</sub> | Supply current |                         | 0.215 | _                 | 1.7  | mA   | 3     |

Table continues on the next page...

| Symbol              | Description            | Conditions <sup>1</sup>                         | Min. | Typ. <sup>2</sup>                 | Max. | Unit  | Notes                                                                                                                |

|---------------------|------------------------|-------------------------------------------------|------|-----------------------------------|------|-------|----------------------------------------------------------------------------------------------------------------------|

| E <sub>IL</sub>     | Input leakage<br>error |                                                 |      | I <sub>In</sub> × R <sub>AS</sub> |      | mV    | I <sub>In</sub> =<br>leakage<br>current<br>(refer to<br>the MCU's<br>voltage<br>and current<br>operating<br>ratings) |

|                     | Temp sensor<br>slope   | Across the full temperature range of the device | _    | 1.715                             | _    | mV/°C |                                                                                                                      |

| V <sub>TEMP25</sub> | Temp sensor<br>voltage | 25 °C                                           | _    | 719                               | —    | mV    |                                                                                                                      |

### Table 20. 16-bit ADC characteristics ( $V_{REFH} = V_{DDA}$ , $V_{REFL} = V_{SSA}$ ) (continued)

- 1. All accuracy numbers assume the ADC is calibrated with  $V_{\mathsf{REFH}}$  =  $V_{\mathsf{DDA}}$

- Typical values assume V<sub>DDA</sub> = 3.0 V, Temp = 25°C, f<sub>ADCK</sub> = 2.0 MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

- The ADC supply current depends on the ADC conversion clock speed, conversion rate and the ADLPC bit (low power). For lowest power operation the ADLPC bit must be set, the HSC bit must be clear with 1 MHz ADC conversion clock speed.

- 4. 1 LSB =  $(V_{REFH} V_{REFL})/2^N$

- 5. ADC conversion clock < 16 MHz, Max hardware averaging (AVGE = %1, AVGS = %11)

- 6. Input data is 100 Hz sine wave. ADC conversion clock < 12 MHz.

- 7. Input data is 1 kHz sine wave. ADC conversion clock < 12 MHz.

Typical ADC 16-bit Single-Ended ENOB vs ADC Clock 100Hz, 90% FS Sine Input

Figure 8. Typical ENOB vs. ADC\_CLK for 16-bit single-ended mode

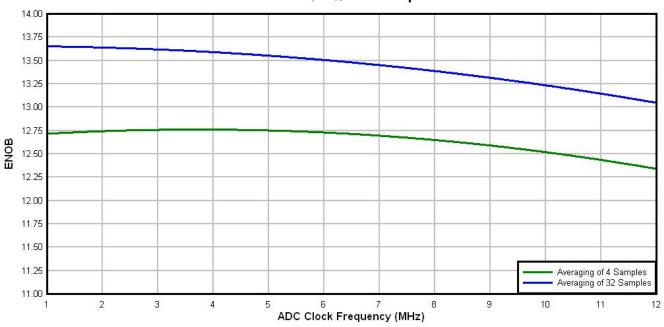

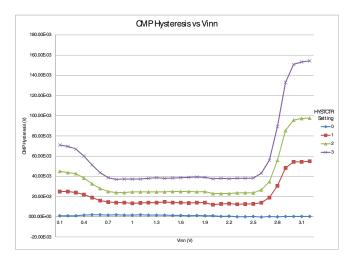

### 6.6.2 CMP and 6-bit DAC electrical specifications Table 21. Comparator and 6-bit DAC electrical specifications

| Symbol             | Description                                            | Min.                  | Тур. | Max.            | Unit |

|--------------------|--------------------------------------------------------|-----------------------|------|-----------------|------|

| V <sub>DD</sub>    | Supply voltage                                         | 1.71                  |      | 3.6             | V    |

| I <sub>DDHS</sub>  | Supply current, high-speed mode (EN = 1, PMODE = 1)    | _                     | _    | 200             | μA   |

| I <sub>DDLS</sub>  | Supply current, low-speed mode (EN = 1, PMODE = 0)     | _                     | _    | 20              | μA   |

| V <sub>AIN</sub>   | Analog input voltage                                   | V <sub>SS</sub>       | _    | V <sub>DD</sub> | V    |

| V <sub>AIO</sub>   | Analog input offset voltage                            | —                     | _    | 20              | mV   |

| V <sub>H</sub>     | Analog comparator hysteresis <sup>1</sup>              |                       |      |                 |      |

|                    | • CR0[HYSTCTR] = 00                                    | _                     | 5    | _               | mV   |

|                    | • CR0[HYSTCTR] = 01                                    | _                     | 10   | _               | mV   |

|                    | • CR0[HYSTCTR] = 10                                    | _                     | 20   | _               | mV   |

|                    | • CR0[HYSTCTR] = 11                                    | —                     | 30   | _               | mV   |

| V <sub>CMPOh</sub> | Output high                                            | V <sub>DD</sub> – 0.5 |      |                 | V    |

| V <sub>CMPOI</sub> | Output low                                             | _                     | _    | 0.5             | V    |

| t <sub>DHS</sub>   | Propagation delay, high-speed mode (EN = 1, PMODE = 1) | 20                    | 50   | 200             | ns   |

| t <sub>DLS</sub>   | Propagation delay, low-speed mode (EN = 1, PMODE = 0)  | 80                    | 250  | 600             | ns   |

Table continues on the next page ...

#### Peripheral operating requirements and behaviors

| Table 21. Comparator and 6-bit DAC electrical specifications (continued | Table 21. | Comparator and | d 6-bit DAC electrical s | specifications | (continued) |

|-------------------------------------------------------------------------|-----------|----------------|--------------------------|----------------|-------------|

|-------------------------------------------------------------------------|-----------|----------------|--------------------------|----------------|-------------|

| Symbol             | Description                                         | Min. | Тур. | Max. | Unit             |

|--------------------|-----------------------------------------------------|------|------|------|------------------|

|                    | Analog comparator initialization delay <sup>2</sup> | —    | —    | 40   | μs               |

| I <sub>DAC6b</sub> | 6-bit DAC current adder (enabled)                   | _    | 7    | —    | μA               |

| INL                | 6-bit DAC integral non-linearity                    | -0.5 | —    | 0.5  | LSB <sup>3</sup> |

| DNL                | 6-bit DAC differential non-linearity                | -0.3 | —    | 0.3  | LSB              |

1. Typical hysteresis is measured with input voltage range limited to 0.7 to  $V_{DD}$  – 0.7 V.

- 2. Comparator initialization delay is defined as the time between software writes to change control inputs (writes to DACEN,

- VRSEL, PSEL, MSEL, VOSEL) and the comparator output settling to a stable level.

- 3. 1 LSB = V<sub>reference</sub>/64

Figure 9. Typical hysteresis vs. Vin level ( $V_{DD}$  = 3.3 V, PMODE = 0)

Figure 10. Typical hysteresis vs. Vin level (V<sub>DD</sub> = 3.3 V, PMODE = 1)

### 6.6.3 12-bit DAC electrical characteristics

### 6.6.3.1 12-bit DAC operating requirements Table 22. 12-bit DAC operating requirements

| Symbol            | Desciption              | Min. | Max.                    | Unit | Notes |

|-------------------|-------------------------|------|-------------------------|------|-------|

| V <sub>DDA</sub>  | Supply voltage          | 1.71 | 3.6                     | V    |       |

| V <sub>DACR</sub> | Reference voltage       | 1.13 | 3.6                     | V    | 1     |

| T <sub>A</sub>    | Temperature             |      | emperature<br>he device | °C   |       |

| CL                | Output load capacitance | _    | 100                     | pF   | 2     |

| ١L                | Output load current     | — 1  |                         | mA   |       |

1. The DAC reference can be selected to be  $V_{DDA}$  or the voltage output of the VREF module (VREF\_OUT)

2. A small load capacitance (47 pF) can improve the bandwidth performance of the DAC

### 6.6.3.2 12-bit DAC operating behaviors Table 23. 12-bit DAC operating behaviors

| Symbol                     | Description                                                                         | Min.                      | Тур.     | Max.              | Unit   | Notes |

|----------------------------|-------------------------------------------------------------------------------------|---------------------------|----------|-------------------|--------|-------|

| I <sub>DDA_DACL</sub>      | Supply current — low-power mode                                                     | —                         | —        | 250               | μΑ     |       |

| I <sub>DDA_DACH</sub><br>P | Supply current — high-speed mode                                                    | _                         | _        | 900               | μΑ     |       |

| t <sub>DACLP</sub>         | Full-scale settling time (0x080 to 0xF7F) —<br>low-power mode                       |                           | 100      | 200               | μs     | 1     |

| t <sub>DACHP</sub>         | Full-scale settling time (0x080 to 0xF7F) — high-power mode                         | _                         | 15       | 30                | μs     | 1     |

| t <sub>CCDACLP</sub>       | Code-to-code settling time (0xBF8 to 0xC08)<br>— low-power mode and high-speed mode | _                         | 0.7      | 1                 | μs     | 1     |

| V <sub>dacoutl</sub>       | DAC output voltage range low — high-speed mode, no load, DAC set to 0x000           | _                         | —        | 100               | mV     |       |

| V <sub>dacouth</sub>       | DAC output voltage range high — high-<br>speed mode, no load, DAC set to 0xFFF      | V <sub>DACR</sub><br>-100 | —        | V <sub>DACR</sub> | mV     |       |

| INL                        | Integral non-linearity error — high speed mode                                      | _                         | —        | ±8                | LSB    | 2     |

| DNL                        | Differential non-linearity error — V <sub>DACR</sub> > 2<br>V                       | —                         | —        | ±1                | LSB    | 3     |

| DNL                        | Differential non-linearity error — V <sub>DACR</sub> = VREF_OUT                     | —                         | —        | ±1                | LSB    | 4     |

| VOFFSET                    | Offset error                                                                        | _                         | ±0.4     | ±0.8              | %FSR   | 5     |

| E <sub>G</sub>             | Gain error                                                                          | —                         | ±0.1     | ±0.6              | %FSR   | 5     |

| PSRR                       | Power supply rejection ratio, $V_{DDA} \ge 2.4 \text{ V}$                           | 60                        | -        | 90                | dB     |       |

| T <sub>CO</sub>            | Temperature coefficient offset voltage                                              | —                         | 3.7      | —                 | μV/C   | 6     |

| T <sub>GE</sub>            | Temperature coefficient gain error                                                  | —                         | 0.000421 | —                 | %FSR/C |       |

| Rop                        | Output resistance load = $3 \text{ k}\Omega$                                        | —                         | —        | 250               | Ω      |       |

Table continues on the next page ...

| 80   | 64   | 48  | 32  | Pin Name          | Default   | ALT0      | ALT1              | ALT2      | ALT3            | ALT4       | ALT5      | ALT6     | ALT7 |

|------|------|-----|-----|-------------------|-----------|-----------|-------------------|-----------|-----------------|------------|-----------|----------|------|

| LQFP | LQFP | QFN | QFN | 1 III Hullio      | Boldan    |           |                   |           |                 |            |           |          |      |

| 62   | 50   | 38  | 26  | PTC5/<br>LLWU_P9  | DISABLED  |           | PTC5/<br>LLWU_P9  | SPI0_SCK  | LPTMR0_<br>ALT2 |            |           | CMP0_OUT |      |

| 63   | 51   | 39  | 27  | PTC6/<br>LLWU_P10 | CMP0_IN0  | CMP0_IN0  | PTC6/<br>LLWU_P10 | SPI0_MOSI | EXTRG_IN        |            | SPI0_MISO |          |      |

| 64   | 52   | 40  | 28  | PTC7              | CMP0_IN1  | CMP0_IN1  | PTC7              | SPI0_MISO |                 |            | SPI0_MOSI |          |      |

| 65   | 53   | -   | _   | PTC8              | CMP0_IN2  | CMP0_IN2  | PTC8              | I2C0_SCL  | TPM0_CH4        |            |           |          |      |

| 66   | 54   | -   | _   | PTC9              | CMP0_IN3  | CMP0_IN3  | PTC9              | I2C0_SDA  | TPM0_CH5        |            |           |          |      |

| 67   | 55   | -   | -   | PTC10             | DISABLED  |           | PTC10             | I2C1_SCL  |                 |            |           |          |      |

| 68   | 56   | _   | _   | PTC11             | DISABLED  |           | PTC11             | I2C1_SDA  |                 |            |           |          |      |

| 69   | _    | _   | _   | PTC12             | DISABLED  |           | PTC12             |           |                 | TPM_CLKIN0 |           |          |      |

| 70   | _    | -   | _   | PTC13             | DISABLED  |           | PTC13             |           |                 | TPM_CLKIN1 |           |          |      |

| 71   | _    | -   | _   | PTC16             | DISABLED  |           | PTC16             |           |                 |            |           |          |      |

| 72   | _    | -   | _   | PTC17             | DISABLED  |           | PTC17             |           |                 |            |           |          |      |

| 73   | 57   | 41  | _   | PTD0              | DISABLED  |           | PTD0              | SPI0_PCS0 |                 | TPM0_CH0   |           |          |      |

| 74   | 58   | 42  | _   | PTD1              | ADC0_SE5b | ADC0_SE5b | PTD1              | SPI0_SCK  |                 | TPM0_CH1   |           |          |      |

| 75   | 59   | 43  | _   | PTD2              | DISABLED  |           | PTD2              | SPI0_MOSI | UART2_RX        | TPM0_CH2   | SPI0_MISO |          |      |

| 76   | 60   | 44  | _   | PTD3              | DISABLED  |           | PTD3              | SPI0_MISO | UART2_TX        | TPM0_CH3   | SPI0_MOSI |          |      |

| 77   | 61   | 45  | 29  | PTD4/<br>LLWU_P14 | DISABLED  |           | PTD4/<br>LLWU_P14 | SPI1_PCS0 | UART2_RX        | TPM0_CH4   |           |          |      |

| 78   | 62   | 46  | 30  | PTD5              | ADC0_SE6b | ADC0_SE6b | PTD5              | SPI1_SCK  | UART2_TX        | TPM0_CH5   |           |          |      |

| 79   | 63   | 47  | 31  | PTD6/<br>LLWU_P15 | ADC0_SE7b | ADC0_SE7b | PTD6/<br>LLWU_P15 | SPI1_MOSI | UART0_RX        |            | SPI1_MISO |          |      |

| 80   | 64   | 48  | 32  | PTD7              | DISABLED  |           | PTD7              | SPI1_MISO | UART0_TX        |            | SPI1_MOSI |          |      |

# 8.2 KL15 Pinouts

The below figures show the pinout diagrams for the devices supported by this document. Many signals may be multiplexed onto a single pin. To determine what signals can be used on which pin, see the previous section.

Pinout

#### How to Reach Us:

Home Page: www.freescale.com

Web Support: http://www.freescale.com/support

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 +1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 10 5879 8000 support.asia@freescale.com Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductors products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claims alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

RoHS-compliant and/or Pb-free versions of Freescale products have the functionality and electrical characteristics as their non-RoHS-complaint and/or non-Pb-free counterparts. For further information, see http://www.freescale.com or contact your Freescale sales representative.

For information on Freescale's Environmental Products program, go to http://www.freescale.com/epp.

$\label{eq:FreescaleTM} Freescale TM and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.$

© 2012 Freescale Semiconductor, Inc.

Document Number: KL15P80M48SF0 Rev. 3, 9/19/2012