# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                      |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 48MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, TSI, UART/USART                        |

| Peripherals                | Brown-out Detect/Reset, DMA, LVD, POR, PWM, WDT                       |

| Number of I/O              | 70                                                                    |

| Program Memory Size        | 128KB (128K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 16K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                          |

| Data Converters            | A/D 16x16b; D/A 1x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 80-LQFP                                                               |

| Supplier Device Package    | 80-FQFP (12x12)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mkl15z128vlk4 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 3.7 Guidelines for ratings and operating requirements

Follow these guidelines for ratings and operating requirements:

- Never exceed any of the chip's ratings.

- During normal operation, don't exceed any of the chip's operating requirements.

- If you must exceed an operating requirement at times other than during normal operation (for example, during power sequencing), limit the duration as much as possible.

### 3.8 Definition: Typical value

A *typical value* is a specified value for a technical characteristic that:

- Lies within the range of values specified by the operating behavior

- Given the typical manufacturing process, is representative of that characteristic during operation when you meet the typical-value conditions or other specified conditions

Typical values are provided as design guidelines and are neither tested nor guaranteed.

### 3.8.1 Example 1

This is an example of an operating behavior that includes a typical value:

| Symbol          | Description                                    | Min. | Тур. | Max. | Unit |

|-----------------|------------------------------------------------|------|------|------|------|

| I <sub>WP</sub> | Digital I/O weak<br>pullup/pulldown<br>current | 10   | 70   | 130  | μΑ   |

### 3.8.2 Example 2

This is an example of a chart that shows typical values for various voltage and temperature conditions:

General

# 5.1 AC electrical characteristics

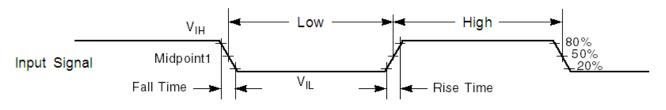

Unless otherwise specified, propagation delays are measured from the 50% to the 50% point, and rise and fall times are measured at the 20% and 80% points, as shown in the following figure.

The midpoint is  $V_{IL}$  +  $(V_{IH} - V_{IL})/2$ .

#### Figure 1. Input signal measurement reference

All digital I/O switching characteristics, unless otherwise specified, assumes:

- 1. output pins

- have  $C_L=30$  pF loads,

- are slew rate disabled, and

- are normal drive strength

# 5.2 Nonswitching electrical specifications

### 5.2.1 Voltage and current operating requirements

Table 1. Voltage and current operating requirements

| Symbol             | Description                                                  | Min.                 | Max.                 | Unit | Notes |

|--------------------|--------------------------------------------------------------|----------------------|----------------------|------|-------|

| V <sub>DD</sub>    | Supply voltage                                               | 1.71                 | 3.6                  | V    |       |

| V <sub>DDA</sub>   | Analog supply voltage                                        | 1.71                 | 3.6                  | V    |       |

| $V_{DD} - V_{DDA}$ | V <sub>DD</sub> -to-V <sub>DDA</sub> differential voltage    | -0.1                 | 0.1                  | V    |       |

| $V_{SS} - V_{SSA}$ | V <sub>SS</sub> -to-V <sub>SSA</sub> differential voltage    | -0.1                 | 0.1                  | V    |       |

| V <sub>IH</sub>    | Input high voltage                                           |                      |                      |      |       |

|                    | • $2.7 \text{ V} \le \text{V}_{\text{DD}} \le 3.6 \text{ V}$ | $0.7 \times V_{DD}$  | —                    | V    |       |

|                    | • $1.7 \text{ V} \le \text{V}_{\text{DD}} \le 2.7 \text{ V}$ | $0.75 \times V_{DD}$ | _                    | V    |       |

| V <sub>IL</sub>    | Input low voltage                                            |                      |                      |      |       |

|                    | • $2.7 \text{ V} \le \text{V}_{\text{DD}} \le 3.6 \text{ V}$ | —                    | $0.35 \times V_{DD}$ | V    |       |

|                    | • $1.7 \text{ V} \le \text{V}_{\text{DD}} \le 2.7 \text{ V}$ | _                    | $0.3 \times V_{DD}$  | V    |       |

| V <sub>HYS</sub>   | Input hysteresis                                             | $0.06 \times V_{DD}$ | —                    | V    |       |

Table continues on the next page...

#### General

| Symbol             | Description                                                 | Min. | Тур. | Max. | Unit | Notes |

|--------------------|-------------------------------------------------------------|------|------|------|------|-------|

|                    | Low-voltage warning thresholds — low range                  |      |      |      |      | 1     |

| V <sub>LVW1L</sub> | Level 1 falling (LVWV=00)                                   | 1.74 | 1.80 | 1.86 | V    |       |

| V <sub>LVW2L</sub> | Level 2 falling (LVWV=01)                                   | 1.84 | 1.90 | 1.96 | V    |       |

| V <sub>LVW3L</sub> | Level 3 falling (LVWV=10)                                   | 1.94 | 2.00 | 2.06 | V    |       |

| $V_{LVW4L}$        | Level 4 falling (LVWV=11)                                   | 2.04 | 2.10 | 2.16 | v    |       |

| V <sub>HYSL</sub>  | Low-voltage inhibit reset/recover hysteresis —<br>low range | _    | ±40  |      | mV   |       |

| V <sub>BG</sub>    | Bandgap voltage reference                                   | 0.97 | 1.00 | 1.03 | V    |       |

| t <sub>LPO</sub>   | Internal low power oscillator period — factory trimmed      | 900  | 1000 | 1100 | μs   |       |

### Table 2. V<sub>DD</sub> supply LVD and POR operating requirements (continued)

1. Rising thresholds are falling threshold + hysteresis voltage

# 5.2.3 Voltage and current operating behaviors

| Symbol           | Description                                                                                            | Min.                  | Max.  | Unit | Notes |

|------------------|--------------------------------------------------------------------------------------------------------|-----------------------|-------|------|-------|

| V <sub>OH</sub>  | Output high voltage — Normal drive pad                                                                 |                       |       |      | 1     |

|                  | • 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V, I <sub>OH</sub> = -5 mA                                   | V <sub>DD</sub> – 0.5 | —     | V    |       |

|                  | • $1.71 \text{ V} \le \text{V}_{\text{DD}} \le 2.7 \text{ V}, \text{ I}_{\text{OH}} = -1.5 \text{ mA}$ | $V_{DD} - 0.5$        | —     | V    |       |

| V <sub>OH</sub>  | Output high voltage — High drive pad                                                                   |                       |       |      | 1     |

|                  | • 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V, I <sub>OH</sub> = -18 mA                                  | $V_{DD} - 0.5$        | _     | V    |       |

|                  | • 1.71 V $\leq$ V <sub>DD</sub> $\leq$ 2.7 V, I <sub>OH</sub> = -6 mA                                  | $V_{DD} - 0.5$        | —     | V    |       |

| I <sub>OHT</sub> | Output high current total for all ports                                                                | _                     | 100   | mA   |       |

| V <sub>OL</sub>  | Output low voltage — Normal drive pad                                                                  |                       |       |      | 1     |

|                  | • 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V, I <sub>OL</sub> = 5 mA                                    | _                     | 0.5   | V    |       |

|                  | • 1.71 V $\leq$ V <sub>DD</sub> $\leq$ 2.7 V, I <sub>OL</sub> = 1.5 mA                                 | —                     | 0.5   | V    |       |

| V <sub>OL</sub>  | Output low voltage — High drive pad                                                                    |                       |       |      | 1     |

|                  | • 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V, I <sub>OL</sub> = 18 mA                                   | _                     | 0.5   | V    |       |

|                  | • 1.71 V $\leq$ V <sub>DD</sub> $\leq$ 2.7 V, I <sub>OL</sub> = 6 mA                                   | _                     | 0.5   | V    |       |

| I <sub>OLT</sub> | Output low current total for all ports                                                                 | _                     | 100   | mA   |       |

| I <sub>IN</sub>  | Input leakage current (per pin) for full temperature range                                             | —                     | 1     | μΑ   | 2     |

| I <sub>IN</sub>  | Input leakage current (per pin) at 25 °C                                                               | _                     | 0.025 | μA   | 2     |

| I <sub>IN</sub>  | Input leakage current (total all pins) for full temperature range                                      | —                     | 65    | μΑ   | 2     |

| I <sub>OZ</sub>  | Hi-Z (off-state) leakage current (per pin)                                                             | _                     | 1     | μA   |       |

Table 3. Voltage and current operating behaviors

Table continues on the next page...

| Table 3. | Voltage and curr | ent operating behavio | rs (continued) |

|----------|------------------|-----------------------|----------------|

|----------|------------------|-----------------------|----------------|

| Symbol          | Description                 | Min. | Max. | Unit | Notes |

|-----------------|-----------------------------|------|------|------|-------|

| R <sub>PU</sub> | Internal pullup resistors   | 20   | 50   | kΩ   | 3     |

| R <sub>PD</sub> | Internal pulldown resistors | 20   | 50   | kΩ   | 4     |

<sup>1.</sup> PTB0, PTB1, PTD6, and PTD7 I/O have both high drive and normal drive capability selected by the associated PTx\_PCRn[DSE] control bit. All other GPIOs are normal drive only.

2. Measured at  $V_{DD} = 3.6 V$

- 3. Measured at  $V_{DD}$  supply voltage =  $V_{DD}$  min and Vinput =  $V_{SS}$

- 4. Measured at  $V_{DD}$  supply voltage =  $V_{DD}$  min and Vinput =  $V_{DD}$

### 5.2.4 Power mode transition operating behaviors

All specifications except  $t_{POR}$  and VLLSx $\rightarrow$ RUN recovery times in the following table assume this clock configuration:

- CPU and system clocks = 48 MHz

- Bus and flash clock = 24 MHz

- FEI clock mode

| Symbol           | Description                                                                                                                                                       | Min. | Тур. | Max. | Unit | Notes |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|-------|

| t <sub>POR</sub> | After a POR event, amount of time from the point $V_{DD}$ reaches 1.8 V to execution of the first instruction across the operating temperature range of the chip. |      | _    | 300  | μs   |       |

|                  | • VLLS0 $\rightarrow$ RUN                                                                                                                                         | _    | 95   | 115  | μs   |       |

|                  | • VLLS1 → RUN                                                                                                                                                     | _    | 93   | 115  | μs   |       |

|                  | VLLS3 → RUN                                                                                                                                                       | _    | 42   | 53   | μs   |       |

|                  | • LLS → RUN                                                                                                                                                       |      | 4    | 4.6  | μs   |       |

|                  | <ul> <li>VLPS → RUN</li> </ul>                                                                                                                                    | _    | 4    | 4.4  | μs   |       |

|                  | • STOP $\rightarrow$ RUN                                                                                                                                          | _    | 4    | 4.4  | μs   |       |

Table 4. Power mode transition operating behaviors

| Symbol                | Description                                                                | Min. | Тур.       | Max.         | Unit | Notes |

|-----------------------|----------------------------------------------------------------------------|------|------------|--------------|------|-------|

| I <sub>DD_VLLS0</sub> | Very low-leakage stop mode 0 current<br>(SMC_STOPCTRL[PORPO] = 0) at 3.0 V |      | 001        | 0.40         | nA   |       |

|                       | at 25 °C                                                                   |      | 381<br>956 | 943<br>11760 |      |       |

|                       | at 50 °C                                                                   | _    | 2370       | 13260        |      |       |

|                       | at 70 °C                                                                   | _    | 4800       | 15700        |      |       |

|                       | at 85 °C                                                                   | _    | 12410      | 23480        |      |       |

|                       | at 105 °C                                                                  |      |            |              |      |       |

| I <sub>DD_VLLS0</sub> | Very low-leakage stop mode 0 current<br>(SMC_STOPCTRL[PORPO] = 1) at 3.0 V | _    | 176        | 860          |      | 6     |

|                       | at 25 °C                                                                   | _    | 760        | 3577         | nA   |       |

|                       | at 50 °C                                                                   | _    | 2120       | 11660        |      |       |

|                       | at 70 °C                                                                   | _    | 4500       | 18450        |      |       |

|                       | at 85 °C                                                                   | _    | 12130      | 22441        |      |       |

|                       | at 105 °C                                                                  |      |            |              |      |       |

#### Table 5. Power consumption operating behaviors (continued)

1. The analog supply current is the sum of the active or disabled current for each of the analog modules on the device. See each module's specification for its supply current.

- 2. MCG configured for PEE mode. CoreMark benchmark compiled using Keil 4.54 with optimization level 3, optimized for time.

- 3. MCG configured for FEI mode.

- 4. Incremental current consumption from peripheral activity is not included.

- 5. MCG configured for BLPI mode.

- 6. No brownout

#### Table 6. Low power mode peripheral adders — typical value

| Symbol        | Description                                                                                                      |     | Temperature (°C) |     |     |     | Unit |    |

|---------------|------------------------------------------------------------------------------------------------------------------|-----|------------------|-----|-----|-----|------|----|

|               |                                                                                                                  | -40 | 25               | 50  | 70  | 85  | 105  |    |

| IIREFSTEN4MHz | 4 MHz internal reference clock (IRC)<br>adder. Measured by entering STOP or<br>VLPS mode with 4 MHz IRC enabled. | 56  | 56               | 56  | 56  | 56  | 56   | μA |

| IREFSTEN32KHz | 32 kHz internal reference clock (IRC)<br>adder. Measured by entering STOP<br>mode with the 32 kHz IRC enabled.   | 52  | 52               | 52  | 52  | 52  | 52   | μA |

| IEREFSTEN4MHz | External 4MHz crystal clock adder.<br>Measured by entering STOP or VLPS<br>mode with the crystal enabled.        | 206 | 228              | 237 | 245 | 251 | 258  | uA |

Table continues on the next page ...

| Symbol | Description                                                                                                                                                                                                             |     | Temperature (°C) |     |     |     | Unit |    |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------|-----|-----|-----|------|----|

|        |                                                                                                                                                                                                                         | -40 | 25               | 50  | 70  | 85  | 105  |    |

|        | ADC peripheral adder combining the<br>measured values at VDD and VDDA by<br>placing the device in STOP or VLPS<br>mode. ADC is configured for low power<br>mode using the internal clock and<br>continuous conversions. | 366 | 366              | 366 | 366 | 366 | 366  | μΑ |

Table 6. Low power mode peripheral adders — typical value (continued)

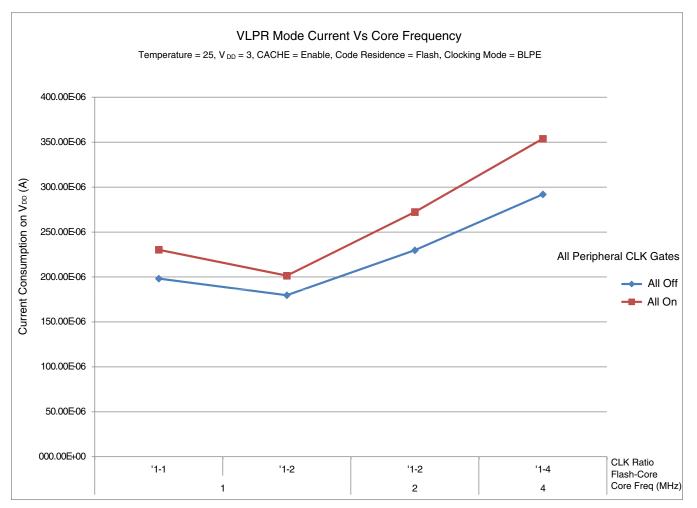

### 5.2.5.1 Diagram: Typical IDD\_RUN operating behavior

The following data was measured under these conditions:

- MCG in FBE for run mode, and BLPE for VLPR mode

- No GPIOs toggled

- Code execution from flash with cache enabled

- For the ALLOFF curve, all peripheral clocks are disabled except FTFA

#### General

Figure 3. VLPR mode current vs. core frequency

### 5.2.6 EMC radiated emissions operating behaviors

# Table 7. EMC radiated emissions operating behaviors for 64-pin LQFP package

| Symbol           | Description                        | Frequency<br>band (MHz) | Тур. | Unit | Notes |

|------------------|------------------------------------|-------------------------|------|------|-------|

| V <sub>RE1</sub> | Radiated emissions voltage, band 1 | 0.15–50                 | 13   | dBµV | 1, 2  |

| V <sub>RE2</sub> | Radiated emissions voltage, band 2 | 50–150                  | 15   | dBµV |       |

| V <sub>RE3</sub> | Radiated emissions voltage, band 3 | 150–500                 | 12   | dBµV |       |

| V <sub>RE4</sub> | Radiated emissions voltage, band 4 | 500–1000                | 7    | dBµV |       |

| $V_{RE\_IEC}$    | IEC level                          | 0.15–1000               | М    | —    | 2, 3  |

Determined according to IEC Standard 61967-1, Integrated Circuits - Measurement of Electromagnetic Emissions, 150 kHz to 1 GHz Part 1: General Conditions and Definitions and IEC Standard 61967-2, Integrated Circuits - Measurement of Electromagnetic Emissions, 150 kHz to 1 GHz Part 2: Measurement of Radiated Emissions – TEM Cell and Wideband TEM Cell Method. Measurements were made while the microcontroller was running basic application code. The reported emission level is the value of the maximum measured emission, rounded up to the next whole number, from among the measured orientations in each frequency range.

- 2.  $V_{DD} = 3.3 \text{ V}, T_A = 25 \text{ °C}, f_{OSC} = 8 \text{ MHz}$  (crystal),  $f_{SYS} = 48 \text{ MHz}, f_{BUS} = 48 \text{ MHz}$

- 3. Specified according to Annex D of IEC Standard 61967-2, Measurement of Radiated Emissions TEM Cell and Wideband TEM Cell Method

### 5.2.7 Designing with radiated emissions in mind

To find application notes that provide guidance on designing your system to minimize interference from radiated emissions:

- 1. Go to www.freescale.com.

- 2. Perform a keyword search for "EMC design."

#### 5.2.8 Capacitance attributes

#### Table 8. Capacitance attributes

| Symbol            | Description                     | Min. | Max. | Unit |

|-------------------|---------------------------------|------|------|------|

| C <sub>IN_A</sub> | Input capacitance: analog pins  | —    | 7    | pF   |

| C <sub>IN_D</sub> | Input capacitance: digital pins |      | 7    | pF   |

### 5.3 Switching specifications

### 5.3.1 Device clock specifications

| Symbol                  | Description                    | Min.            | Max. | Unit | Notes |

|-------------------------|--------------------------------|-----------------|------|------|-------|

|                         | Normal run                     | mode            | 1    |      |       |

| f <sub>SYS</sub>        | System and core clock          | —               | 48   | MHz  |       |

| f <sub>BUS</sub>        | Bus clock                      | —               | 24   | MHz  |       |

| f <sub>FLASH</sub>      | Flash clock                    | —               | 24   | MHz  |       |

| f <sub>LPTMR</sub>      | LPTMR clock                    |                 | 24   | MHz  |       |

|                         | VLPR mo                        | de <sup>1</sup> |      | 1    |       |

| f <sub>SYS</sub>        | System and core clock          | —               | 4    | MHz  |       |

| f <sub>BUS</sub>        | Bus clock                      |                 | 1    | MHz  |       |

| f <sub>FLASH</sub>      | Flash clock                    | —               | 1    | MHz  |       |

| f <sub>LPTMR</sub>      | LPTMR clock                    | —               | 24   | MHz  |       |

| f <sub>ERCLK</sub>      | External reference clock       | —               | 16   | MHz  |       |

| f <sub>LPTMR_pin</sub>  | LPTMR clock                    | —               | 24   | MHz  |       |

| f <sub>lptmr_ercl</sub> | LPTMR external reference clock | —               | 16   | MHz  |       |

Table continues on the next page ...

### 5.4.2 Thermal attributes

| Board type        | Symbol            | Description                                                                                              | 80<br>LQFP | 64<br>LQFP | 48 QFN | 32 QFN | Unit | Notes |

|-------------------|-------------------|----------------------------------------------------------------------------------------------------------|------------|------------|--------|--------|------|-------|

| Single-layer (1S) | R <sub>θJA</sub>  | Thermal resistance, junction<br>to ambient (natural<br>convection)                                       | 70         | 71         | 84     | 92     | °C/W | 1     |

| Four-layer (2s2p) | R <sub>θJA</sub>  | Thermal resistance, junction<br>to ambient (natural<br>convection)                                       | 53         | 52         | 28     | 33     | °C/W |       |

| Single-layer (1S) | R <sub>θJMA</sub> | Thermal resistance, junction<br>to ambient (200 ft./min. air<br>speed)                                   | _          | 59         | 69     | 75     | °C/W |       |

| Four-layer (2s2p) | R <sub>θJMA</sub> | Thermal resistance, junction<br>to ambient (200 ft./min. air<br>speed)                                   | _          | 46         | 22     | 27     | °C/W |       |

| _                 | R <sub>θJB</sub>  | Thermal resistance, junction to board                                                                    | 34         | 34         | 10     | 12     | °C/W | 2     |

| _                 | R <sub>θJC</sub>  | Thermal resistance, junction to case                                                                     | 15         | 20         | 2.0    | 1.8    | °C/W | 3     |

|                   | $\Psi_{JT}$       | Thermal characterization<br>parameter, junction to<br>package top outside center<br>(natural convection) | 0.6        | 5          | 5.0    | 8      | °C/W | 4     |

Table 10. Thermal attributes

- 1. Determined according to JEDEC Standard JESD51-2, Integrated Circuits Thermal Test Method Environmental Conditions —Natural Convection (Still Air), or EIA/JEDEC Standard JESD51-6, Integrated Circuit Thermal Test Method Environmental Conditions—Forced Convection (Moving Air).

- 2. Determined according to JEDEC Standard JESD51-8, Integrated Circuit Thermal Test Method Environmental Conditions —Junction-to-Board.

- 3. Determined according to Method 1012.1 of MIL-STD 883, *Test Method Standard, Microcircuits*, with the cold plate temperature used for the case temperature. The value includes the thermal resistance of the interface material between the top of the package and the cold plate.

- 4. Determined according to JEDEC Standard JESD51-2, Integrated Circuits Thermal Test Method Environmental Conditions —Natural Convection (Still Air).

# 6 Peripheral operating requirements and behaviors

### 6.1 Core modules

### 6.1.1 SWD Electricals

#### Table 11. SWD full voltage range electricals

| Symbol | Description       | Min. | Max. | Unit |

|--------|-------------------|------|------|------|

|        | Operating voltage | 1.71 | 3.6  | V    |

Table continues on the next page...

### 6.2 System modules

There are no specifications necessary for the device's system modules.

# 6.3 Clock modules

# 6.3.1 MCG specifications

| Symbol                  | Description                                                                                                          |                                                                                                                                                      | Min.                            | Тур.      | Max.    | Unit                  | Notes |

|-------------------------|----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-----------|---------|-----------------------|-------|

| f <sub>ints_ft</sub>    |                                                                                                                      | frequency (slow clock) —<br>nominal V <sub>DD</sub> and 25 °C                                                                                        | —                               | 32.768    | —       | kHz                   |       |

| f <sub>ints_t</sub>     | Internal reference<br>trimmed                                                                                        | frequency (slow clock) — user                                                                                                                        | 31.25                           | _         | 39.0625 | kHz                   |       |

| $\Delta_{fdco\_res\_t}$ | Resolution of trimmed average DCO output<br>frequency at fixed voltage and temperature —<br>using SCTRIM and SCFTRIM |                                                                                                                                                      | _                               | ± 0.3     | ± 0.6   | %f <sub>dco</sub>     | 1     |

| $\Delta f_{dco\_t}$     |                                                                                                                      | rimmed average DCO output tage and temperature                                                                                                       |                                 | +0.5/-0.7 | ± 3     | %f <sub>dco</sub>     | 1, 2  |

| $\Delta f_{dco_t}$      |                                                                                                                      | rimmed average DCO output<br>ed voltage and temperature                                                                                              | _                               | ± 0.4     | ± 1.5   | %f <sub>dco</sub>     | 1, 2  |

| f <sub>intf_ft</sub>    |                                                                                                                      | nternal reference frequency (fast clock) —<br>actory trimmed at nominal V <sub>DD</sub> and 25 °C                                                    |                                 | 4         | —       | MHz                   |       |

| $\Delta f_{intf_{ft}}$  | (fast clock) over te                                                                                                 | Frequency deviation of internal reference clock<br>(fast clock) over temperature and voltage<br>factory trimmed at nominal V <sub>DD</sub> and 25 °C |                                 | +1/-2     | ± 3     | %f <sub>intf_ft</sub> | 2     |

| f <sub>intf_t</sub>     | Internal reference<br>trimmed at nomina                                                                              | frequency (fast clock) — user<br>Il V <sub>DD</sub> and 25 °C                                                                                        | 3                               | —         | 5       | MHz                   |       |

| f <sub>loc_low</sub>    | Loss of external cl<br>RANGE = 00                                                                                    | ock minimum frequency —                                                                                                                              | (3/5) x<br>f <sub>ints_t</sub>  | —         | —       | kHz                   |       |

| f <sub>loc_high</sub>   | Loss of external cl<br>RANGE = 01, 10,                                                                               | ock minimum frequency —<br>or 11                                                                                                                     | (16/5) x<br>f <sub>ints_t</sub> | _         | —       | kHz                   |       |

|                         |                                                                                                                      | FI                                                                                                                                                   | L                               |           |         |                       |       |

| f <sub>fll_ref</sub>    | FLL reference freq                                                                                                   | uency range                                                                                                                                          | 31.25                           | —         | 39.0625 | kHz                   |       |

| f <sub>dco</sub>        | DCO output<br>frequency range                                                                                        | Low range (DRS = 00)<br>640 × f <sub>fll_ref</sub>                                                                                                   | 20                              | 20.97     | 25      | MHz                   | 3, 4  |

|                         | Mid range (DRS = 01)<br>$1280 \times f_{fll_ref}$                                                                    |                                                                                                                                                      | 40                              | 41.94     | 48      | MHz                   |       |

#### Table 12. MCG specifications

Table continues on the next page...

KL15 Sub-Family Data Sheet Data Sheet, Rev. 3, 9/19/2012.

### 6.3.2 Oscillator electrical specifications

This section provides the electrical characteristics of the module.

#### 6.3.2.1 Oscillator DC electrical specifications Table 13. Oscillator DC electrical specifications

| Symbol          | Description                                                | Min. | Тур. | Max. | Unit | Notes |

|-----------------|------------------------------------------------------------|------|------|------|------|-------|

| V <sub>DD</sub> | Supply voltage                                             | 1.71 | —    | 3.6  | V    |       |

| IDDOSC          | Supply current — low-power mode (HGO=0)                    |      |      |      |      | 1     |

|                 | • 32 kHz                                                   | _    | 500  | _    | nA   |       |

|                 | • 4 MHz                                                    | _    | 200  | _    | μA   |       |

|                 | • 8 MHz (RANGE=01)                                         | _    | 300  | _    | μA   |       |

|                 | • 16 MHz                                                   | _    | 950  | _    | μA   |       |

|                 | • 24 MHz                                                   | _    | 1.2  | _    | mA   |       |

|                 | • 32 MHz                                                   | _    | 1.5  | _    | mA   |       |

| IDDOSC          | Supply current — high gain mode (HGO=1)                    |      |      |      |      | 1     |

|                 | • 32 kHz                                                   | _    | 25   | _    | μA   |       |

|                 | • 4 MHz                                                    | _    | 400  | _    | μA   |       |

|                 | • 8 MHz (RANGE=01)                                         | _    | 500  | _    | μA   |       |

|                 | • 16 MHz                                                   | _    | 2.5  | _    | mA   |       |

|                 | • 24 MHz                                                   | _    | 3    | _    | mA   |       |

|                 | • 32 MHz                                                   | _    | 4    | _    | mA   |       |

| C <sub>x</sub>  | EXTAL load capacitance                                     |      | _    |      |      | 2, 3  |

| Cy              | XTAL load capacitance                                      | _    | —    | _    |      | 2, 3  |

| R <sub>F</sub>  | Feedback resistor — low-frequency, low-power mode (HGO=0)  | _    | _    | _    | MΩ   | 2, 4  |

|                 | Feedback resistor — low-frequency, high-gain mode (HGO=1)  | _    | 10   |      | MΩ   |       |

|                 | Feedback resistor — high-frequency, low-power mode (HGO=0) |      | _    |      | MΩ   |       |

|                 | Feedback resistor — high-frequency, high-gain mode (HGO=1) |      | 1    |      | MΩ   |       |

Table continues on the next page ...

KL15 Sub-Family Data Sheet Data Sheet, Rev. 3, 9/19/2012.

| Symbol                       | Description                                                                                            | Min. | Тур.            | Max. | Unit | Notes |

|------------------------------|--------------------------------------------------------------------------------------------------------|------|-----------------|------|------|-------|

| R <sub>S</sub>               | Series resistor — low-frequency, low-power mode (HGO=0)                                                | —    | _               | _    | kΩ   |       |

|                              | Series resistor — low-frequency, high-gain mode (HGO=1)                                                | —    | 200             |      | kΩ   |       |

|                              | Series resistor — high-frequency, low-power mode (HGO=0)                                               | —    |                 |      | kΩ   |       |

|                              | Series resistor — high-frequency, high-gain<br>mode (HGO=1)                                            |      |                 |      |      |       |

|                              |                                                                                                        | —    | 0               | _    | kΩ   |       |

| V <sub>pp</sub> <sup>5</sup> | Peak-to-peak amplitude of oscillation (oscillator<br>mode) — low-frequency, low-power mode<br>(HGO=0)  | _    | 0.6             | _    | V    |       |

|                              | Peak-to-peak amplitude of oscillation (oscillator<br>mode) — low-frequency, high-gain mode<br>(HGO=1)  | _    | V <sub>DD</sub> | _    | V    |       |

|                              | Peak-to-peak amplitude of oscillation (oscillator<br>mode) — high-frequency, low-power mode<br>(HGO=0) | _    | 0.6             | _    | V    |       |

|                              | Peak-to-peak amplitude of oscillation (oscillator<br>mode) — high-frequency, high-gain mode<br>(HGO=1) |      | V <sub>DD</sub> | _    | V    |       |

#### Table 13. Oscillator DC electrical specifications (continued)

- 1.  $V_{DD}$ =3.3 V, Temperature =25 °C

- 2. See crystal or resonator manufacturer's recommendation

- 3. C<sub>x</sub>,C<sub>y</sub> can be provided by using the integrated capacitors when the low frequency oscillator (RANGE = 00) is used. For all other cases external capacitors must be used.

- 4. When low power mode is selected,  $R_F$  is integrated and must not be attached externally.

- 5. The EXTAL and XTAL pins should only be connected to required oscillator components and must not be connected to any other devices.

#### 6.3.2.2 Oscillator frequency specifications Table 14. Oscillator frequency specifications

| Symbol                | Description                                                                                           | Min. | Тур. | Max. | Unit | Notes |

|-----------------------|-------------------------------------------------------------------------------------------------------|------|------|------|------|-------|

| f <sub>osc_lo</sub>   | Oscillator crystal or resonator frequency — low frequency mode (MCG_C2[RANGE]=00)                     | 32   | _    | 40   | kHz  |       |

| f <sub>osc_hi_1</sub> | Oscillator crystal or resonator frequency — high<br>frequency mode (low range)<br>(MCG_C2[RANGE]=01)  | 3    | _    | 8    | MHz  |       |

| f <sub>osc_hi_2</sub> | Oscillator crystal or resonator frequency — high<br>frequency mode (high range)<br>(MCG_C2[RANGE]=1x) | 8    | _    | 32   | MHz  |       |

| f <sub>ec_extal</sub> | Input clock frequency (external clock mode)                                                           | —    | _    | 48   | MHz  | 1, 2  |

| t <sub>dc_extal</sub> | Input clock duty cycle (external clock mode)                                                          | 40   | 50   | 60   | %    |       |

Table continues on the next page...

Peripheral operating requirements and behaviors

#### 6.4.1.2 Flash timing specifications — commands Table 16. Flash command timing specifications

| Symbol                | Description                                   | Min. | Тур. | Max. | Unit | Notes |

|-----------------------|-----------------------------------------------|------|------|------|------|-------|

| t <sub>rd1sec1k</sub> | Read 1s Section execution time (flash sector) | _    | —    | 60   | μs   | 1     |

| t <sub>pgmchk</sub>   | Program Check execution time                  | _    | —    | 45   | μs   | 1     |

| t <sub>rdrsrc</sub>   | Read Resource execution time                  | _    | —    | 30   | μs   | 1     |

| t <sub>pgm4</sub>     | Program Longword execution time               | _    | 65   | 145  | μs   |       |

| t <sub>ersscr</sub>   | Erase Flash Sector execution time             | _    | 14   | 114  | ms   | 2     |

| t <sub>rd1all</sub>   | Read 1s All Blocks execution time             | _    | —    | 1.8  | ms   |       |

| t <sub>rdonce</sub>   | Read Once execution time                      | _    | —    | 25   | μs   | 1     |

| t <sub>pgmonce</sub>  | Program Once execution time                   | _    | 65   | _    | μs   |       |

| t <sub>ersall</sub>   | Erase All Blocks execution time               | _    | 62   | 500  | ms   | 2     |

| t <sub>vfykey</sub>   | Verify Backdoor Access Key execution time     | _    | —    | 30   | μs   | 1     |

1. Assumes 25MHz flash clock frequency.

2. Maximum times for erase parameters based on expectations at cycling end-of-life.

#### 6.4.1.3 Flash high voltage current behaviors Table 17. Flash high voltage current behaviors

| Symbol              | Description                                                           | Min. | Тур. | Max. | Unit |

|---------------------|-----------------------------------------------------------------------|------|------|------|------|

| I <sub>DD_PGM</sub> | Average current adder during high voltage flash programming operation | —    | 2.5  | 6.0  | mA   |

| I <sub>DD_ERS</sub> | Average current adder during high voltage flash erase operation       |      | 1.5  | 4.0  | mA   |

### 6.4.1.4 Reliability specifications

#### Table 18. NVM reliability specifications

| Symbol                  | Description                            | Min.    | Typ. <sup>1</sup> | Max. | Unit   | Notes |

|-------------------------|----------------------------------------|---------|-------------------|------|--------|-------|

|                         | Progra                                 | m Flash | _                 |      |        |       |

| t <sub>nvmretp10k</sub> | Data retention after up to 10 K cycles | 5       | 50                | —    | years  |       |

| t <sub>nvmretp1k</sub>  | Data retention after up to 1 K cycles  | 20      | 100               | —    | years  |       |

| n <sub>nvmcycp</sub>    | Cycling endurance                      | 10 K    | 50 K              |      | cycles | 2     |

Typical data retention values are based on measured response accelerated at high temperature and derated to a constant 25°C use profile. Engineering Bulletin EB618 does not apply to this technology. Typical endurance defined in Engineering Bulletin EB619.

2. Cycling endurance represents number of program/erase cycles at -40°C  $\leq$  T<sub>i</sub>  $\leq$  125°C.

# 6.5 Security and integrity modules

There are no specifications necessary for the device's security and integrity modules.

# 6.6 Analog

### 6.6.1 ADC electrical specifications

The 16-bit accuracy specifications listed in Table 19 and Table 20 are achievable on the differential pins ADCx\_DP0, ADCx\_DM0.

All other ADC channels meet the 13-bit differential/12-bit single-ended accuracy specifications.

| Symbol            | Description                       | Conditions                                                                                                        | Min.              | Typ. <sup>1</sup> | Max.              | Unit | Notes |

|-------------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------|-------------------|-------------------|-------------------|------|-------|

| V <sub>DDA</sub>  | Supply voltage                    | Absolute                                                                                                          | 1.71              | _                 | 3.6               | V    |       |

| $\Delta V_{DDA}$  | Supply voltage                    | Delta to V <sub>DD</sub> (V <sub>DD</sub> -V <sub>DDA</sub> )                                                     | -100              | 0                 | +100              | mV   | 2     |

| $\Delta V_{SSA}$  | Ground voltage                    | Delta to V <sub>SS</sub> (V <sub>SS</sub> - V <sub>SSA</sub> )                                                    | -100              | 0                 | +100              | mV   | 2     |

| V <sub>REFH</sub> | ADC reference voltage high        |                                                                                                                   | 1.13              | V <sub>DDA</sub>  | V <sub>DDA</sub>  | V    | 3     |

| V <sub>REFL</sub> | ADC reference voltage low         |                                                                                                                   | V <sub>SSA</sub>  | V <sub>SSA</sub>  | V <sub>SSA</sub>  | V    | 3     |

| V <sub>ADIN</sub> | Input voltage                     |                                                                                                                   | V <sub>REFL</sub> | _                 | V <sub>REFH</sub> | V    |       |

| C <sub>ADIN</sub> | Input capacitance                 | 16-bit mode                                                                                                       | _                 | 8                 | 10                | pF   |       |

|                   |                                   | • 8-/10-/12-bit modes                                                                                             | _                 | 4                 | 5                 |      |       |

| R <sub>ADIN</sub> | Input resistance                  |                                                                                                                   | _                 | 2                 | 5                 | kΩ   |       |

| R <sub>AS</sub>   | Analog source<br>resistance       | 13-/12-bit modes<br>f <sub>ADCK</sub> < 4 MHz                                                                     | _                 | _                 | 5                 | kΩ   | 4     |

| f <sub>ADCK</sub> | ADC conversion<br>clock frequency | ≤ 1312-bit mode                                                                                                   | 1.0               |                   | 18.0              | MHz  | 5     |

| f <sub>ADCK</sub> | ADC conversion<br>clock frequency | 16-bit mode                                                                                                       | 2.0               | _                 | 12.0              | MHz  | 5     |

| C <sub>rate</sub> | ADC conversion rate               | ≤ 1312 bit modes<br>No ADC hardware averaging<br>Continuous conversions<br>enabled, subsequent<br>conversion time | 20.000            |                   | 818.330           | Ksps | 6     |

#### 6.6.1.1 16-bit ADC operating conditions Table 19. 16-bit ADC operating conditions

Table continues on the next page...

#### 6.6.3.1 12-bit DAC operating requirements Table 22. 12-bit DAC operating requirements

| Symbol           | Desciption              | Min. | Max.                    | Unit | Notes |

|------------------|-------------------------|------|-------------------------|------|-------|

| V <sub>DDA</sub> | Supply voltage          | 1.71 | 3.6                     | V    |       |

| VDACR            | Reference voltage       | 1.13 | 3.6                     | V    | 1     |

| T <sub>A</sub>   | Temperature             |      | emperature<br>he device | °C   |       |

| CL               | Output load capacitance | _    | 100                     | pF   | 2     |

| ١L               | Output load current     | —    | 1                       | mA   |       |

1. The DAC reference can be selected to be  $V_{DDA}$  or the voltage output of the VREF module (VREF\_OUT)

2. A small load capacitance (47 pF) can improve the bandwidth performance of the DAC

#### 6.6.3.2 12-bit DAC operating behaviors Table 23. 12-bit DAC operating behaviors

| Symbol                     | Description                                                                         | Min.                      | Тур.     | Max.              | Unit   | Notes |

|----------------------------|-------------------------------------------------------------------------------------|---------------------------|----------|-------------------|--------|-------|

| I <sub>DDA_DACL</sub><br>P | Supply current — low-power mode                                                     | —                         | —        | 250               | μΑ     |       |

| I <sub>DDA_DACH</sub><br>P | Supply current — high-speed mode                                                    | _                         | _        | 900               | μA     |       |

| t <sub>DACLP</sub>         | Full-scale settling time (0x080 to 0xF7F) —<br>low-power mode                       |                           | 100      | 200               | μs     | 1     |

| t <sub>DACHP</sub>         | Full-scale settling time (0x080 to 0xF7F) — high-power mode                         | _                         | 15       | 30                | μs     | 1     |

| t <sub>CCDACLP</sub>       | Code-to-code settling time (0xBF8 to 0xC08)<br>— low-power mode and high-speed mode | _                         | 0.7      | 1                 | μs     | 1     |

| V <sub>dacoutl</sub>       | DAC output voltage range low — high-speed mode, no load, DAC set to 0x000           | _                         | —        | 100               | mV     |       |

| V <sub>dacouth</sub>       | DAC output voltage range high — high-<br>speed mode, no load, DAC set to 0xFFF      | V <sub>DACR</sub><br>-100 | —        | V <sub>DACR</sub> | mV     |       |

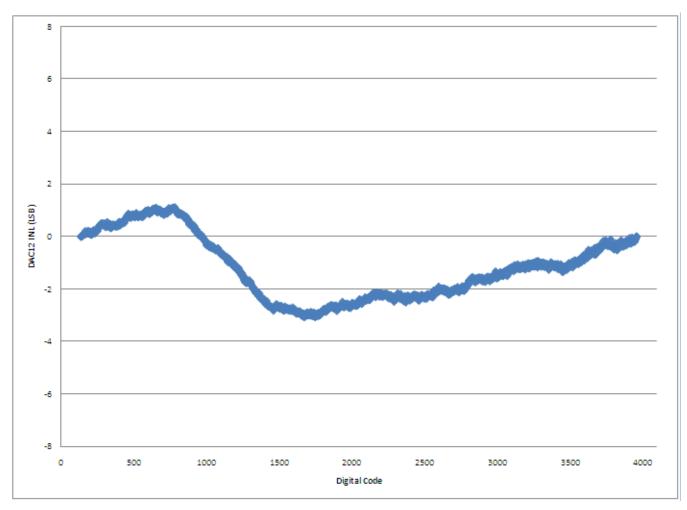

| INL                        | Integral non-linearity error — high speed mode                                      | _                         | —        | ±8                | LSB    | 2     |

| DNL                        | Differential non-linearity error — V <sub>DACR</sub> > 2<br>V                       | _                         | —        | ±1                | LSB    | 3     |

| DNL                        | Differential non-linearity error — V <sub>DACR</sub> = VREF_OUT                     | —                         | —        | ±1                | LSB    | 4     |

| VOFFSET                    | Offset error                                                                        | _                         | ±0.4     | ±0.8              | %FSR   | 5     |

| E <sub>G</sub>             | Gain error                                                                          | —                         | ±0.1     | ±0.6              | %FSR   | 5     |

| PSRR                       | Power supply rejection ratio, $V_{DDA} \ge 2.4 \text{ V}$                           | 60                        | -        | 90                | dB     |       |

| T <sub>CO</sub>            | Temperature coefficient offset voltage                                              | —                         | 3.7      | —                 | μV/C   | 6     |

| T <sub>GE</sub>            | Temperature coefficient gain error                                                  | —                         | 0.000421 | —                 | %FSR/C |       |

| Rop                        | Output resistance load = $3 \text{ k}\Omega$                                        | —                         | —        | 250               | Ω      |       |

Table continues on the next page ...

#### Peripheral operating requirements and behaviors

| Symbol | Description                                      | Min. | Тур. | Max. | Unit | Notes |

|--------|--------------------------------------------------|------|------|------|------|-------|

| SR     | Slew rate -80h→ F7Fh→ 80h                        |      |      |      | V/µs |       |

|        | • High power (SP <sub>HP</sub> )                 |      | 1.7  | —    |      |       |

|        | <ul> <li>Low power (SP<sub>LP</sub>)</li> </ul>  | 0.05 | 0.12 |      |      |       |

| BW     | W 3dB bandwidth                                  |      |      |      | kHz  |       |

|        | <ul> <li>High power (SP<sub>HP</sub>)</li> </ul> | 550  | —    | —    |      |       |

|        | • Low power (SP <sub>LP</sub> )                  |      | _    | _    |      |       |

Table 23. 12-bit DAC operating behaviors (continued)

- 1. Settling within ±1 LSB

- 2. The INL is measured for 0 + 100 mV to  $V_{DACR}$  –100 mV

- 3. The DNL is measured for 0 + 100 mV to  $V_{DACR}$  –100 mV

- 4. The DNL is measured for 0 + 100 mV to  $V_{DACR}$  –100 mV with  $V_{DDA}$  > 2.4 V

- 5. Calculated by a best fit curve from  $V_{SS}$  + 100 mV to  $V_{DACR}$  100 mV 6.  $V_{DDA}$  = 3.0 V, reference select set for  $V_{DDA}$  (DACx\_CO:DACRFS = 1), high power mode (DACx\_CO:LPEN = 0), DAC set to 0x800, temperature range is across the full range of the device

# 6.9 Human-machine interfaces (HMI)

### 6.9.1 TSI electrical specifications

#### Table 28. TSI electrical specifications

| Symbol    | Description                                                                        | Min. | Туре | Max  | Unit |

|-----------|------------------------------------------------------------------------------------|------|------|------|------|

| TSI_RUNF  | Fixed power consumption in run mode                                                | —    | 100  | —    | μA   |

| TSI_RUNV  | Variable power consumption in run mode (depends on oscillator's current selection) | 1.0  | -    | 128  | μA   |

| TSI_EN    | Power consumption in enable mode                                                   | —    | 100  | —    | μA   |

| TSI_DIS   | Power consumption in disable mode                                                  | —    | 1.2  | _    | μA   |

| TSI_TEN   | TSI analog enable time                                                             | —    | 66   | —    | μs   |

| TSI_CREF  | TSI reference capacitor                                                            | —    | 1.0  | —    | pF   |

| TSI_DVOLT | Voltage variation of VP & VM around nominal<br>values                              | 0.19 | -    | 1.03 | V    |

# 7 Dimensions

# 7.1 Obtaining package dimensions

Package dimensions are provided in package drawings.

To find a package drawing, go to www.freescale.com and perform a keyword search for the drawing's document number:

| If you want the drawing for this package | Then use this document number |

|------------------------------------------|-------------------------------|

| 32-pin QFN                               | 98ASA00473D                   |

| 48-pin QFN                               | 98ASA00466D                   |

| 64-pin LQFP                              | 98ASS23234W                   |

| 80-pin LQFP                              | 98ASS23174W                   |

# 8 Pinout

# 8.1 KL15 Signal Multiplexing and Pin Assignments

The following table shows the signals available on each pin and the locations of these pins on the devices supported by this document. The Port Control Module is responsible for selecting which ALT functionality is available on each pin.

| 80<br>LQFP | 64<br>LQFP | 48<br>QFN | 32<br>QFN | Pin Name | Default                             | ALTO                                | ALT1  | ALT2      | ALT3     | ALT4       | ALT5      | ALT6            | ALT7    |

|------------|------------|-----------|-----------|----------|-------------------------------------|-------------------------------------|-------|-----------|----------|------------|-----------|-----------------|---------|

| 1          | 1          | -         | 1         | PTE0     | DISABLED                            |                                     | PTE0  |           | UART1_TX | RTC_CLKOUT | CMP0_OUT  | I2C1_SDA        |         |

| 2          | 2          | -         | 2         | PTE1     | DISABLED                            |                                     | PTE1  | SPI1_MOSI | UART1_RX |            | SPI1_MISO | I2C1_SCL        |         |

| 3          | -          | _         | _         | PTE2     | DISABLED                            |                                     | PTE2  | SPI1_SCK  |          |            |           |                 |         |

| 4          | -          | -         | _         | PTE3     | DISABLED                            |                                     | PTE3  | SPI1_MISO |          |            | SPI1_MOSI |                 |         |

| 5          | -          | -         | _         | PTE4     | DISABLED                            |                                     | PTE4  | SPI1_PCS0 |          |            |           |                 |         |

| 6          | -          | -         | _         | PTE5     | DISABLED                            |                                     | PTE5  |           |          |            |           |                 |         |

| 7          | 3          | 1         | _         | VDD      | VDD                                 | VDD                                 |       |           |          |            |           |                 |         |

| 8          | 4          | 2         | _         | VSS      | VSS                                 | VSS                                 |       |           |          |            |           |                 |         |

| 9          | 5          | 3         | 3         | PTE16    | ADC0_DP1/<br>ADC0_SE1               | ADC0_DP1/<br>ADC0_SE1               | PTE16 | SPI0_PCS0 | UART2_TX | TPM_CLKIN0 |           |                 |         |

| 10         | 6          | 4         | 4         | PTE17    | ADC0_DM1/<br>ADC0_SE5a              | ADC0_DM1/<br>ADC0_SE5a              | PTE17 | SPI0_SCK  | UART2_RX | TPM_CLKIN1 |           | LPTMR0_<br>ALT3 |         |

| 11         | 7          | 5         | 5         | PTE18    | ADC0_DP2/<br>ADC0_SE2               | ADC0_DP2/<br>ADC0_SE2               | PTE18 | SPI0_MOSI |          | I2C0_SDA   | SPI0_MISO |                 |         |

| 12         | 8          | 6         | 6         | PTE19    | ADC0_DM2/<br>ADC0_SE6a              | ADC0_DM2/<br>ADC0_SE6a              | PTE19 | SPI0_MISO |          | I2C0_SCL   | SPI0_MOSI |                 |         |

| 13         | 9          | 7         | _         | PTE20    | ADC0_DP0/<br>ADC0_SE0               | ADC0_DP0/<br>ADC0_SE0               | PTE20 |           | TPM1_CH0 | UART0_TX   |           |                 |         |

| 14         | 10         | 8         | _         | PTE21    | ADC0_DM0/<br>ADC0_SE4a              | ADC0_DM0/<br>ADC0_SE4a              | PTE21 |           | TPM1_CH1 | UART0_RX   |           |                 |         |

| 15         | 11         | _         | _         | PTE22    | ADC0_DP3/<br>ADC0_SE3               | ADC0_DP3/<br>ADC0_SE3               | PTE22 |           | TPM2_CH0 | UART2_TX   |           |                 |         |

| 16         | 12         | -         | _         | PTE23    | ADC0_DM3/<br>ADC0_SE7a              | ADC0_DM3/<br>ADC0_SE7a              | PTE23 |           | TPM2_CH1 | UART2_RX   |           |                 |         |

| 17         | 13         | 9         | 7         | VDDA     | VDDA                                | VDDA                                |       |           |          |            |           |                 |         |

| 18         | 14         | 10        | —         | VREFH    | VREFH                               | VREFH                               |       |           |          |            |           |                 |         |

| 19         | 15         | 11        | _         | VREFL    | VREFL                               | VREFL                               |       |           |          |            |           |                 |         |

| 20         | 16         | 12        | 8         | VSSA     | VSSA                                | VSSA                                |       |           |          |            |           |                 |         |

| 21         | 17         | 13        | _         | PTE29    | CMP0_IN5/<br>ADC0_SE4b              | CMP0_IN5/<br>ADC0_SE4b              | PTE29 |           | TPM0_CH2 | TPM_CLKIN0 |           |                 |         |

| 22         | 18         | 14        | 9         | PTE30    | DAC0_OUT/<br>ADC0_SE23/<br>CMP0_IN4 | DAC0_OUT/<br>ADC0_SE23/<br>CMP0_IN4 | PTE30 |           | TPM0_CH3 | TPM_CLKIN1 |           |                 |         |

| 23         | 19         | -         | _         | PTE31    | DISABLED                            |                                     | PTE31 |           | TPM0_CH4 |            |           |                 |         |

| 24         | 20         | 15        | _         | PTE24    | DISABLED                            |                                     | PTE24 |           | TPM0_CH0 |            | I2C0_SCL  |                 |         |

| 25         | 21         | 16        | _         | PTE25    | DISABLED                            |                                     | PTE25 |           | TPM0_CH1 |            | I2C0_SDA  |                 |         |

| 26         | 22         | 17        | 10        | PTA0     | SWD_CLK                             | TSI0_CH1                            | PTA0  |           | TPM0_CH5 |            |           |                 | SWD_CLK |

| 27         | 23         | 18        | 11        | PTA1     | DISABLED                            | TSI0_CH2                            | PTA1  | UART0_RX  | TPM2_CH0 |            |           |                 |         |

| 28         | 24         | 19        | 12        | PTA2     | DISABLED                            | TSI0_CH3                            | PTA2  | UART0_TX  | TPM2_CH1 |            |           |                 |         |

| 80   | 64   | 48  | 32  | Pin Name          | Default   | ALT0      | ALT1              | ALT2      | ALT3            | ALT4       | ALT5      | ALT6     | ALT7 |

|------|------|-----|-----|-------------------|-----------|-----------|-------------------|-----------|-----------------|------------|-----------|----------|------|

| LQFP | LQFP | QFN | QFN | 1 III Hullio      | Boldan    |           |                   |           |                 |            |           |          |      |

| 62   | 50   | 38  | 26  | PTC5/<br>LLWU_P9  | DISABLED  |           | PTC5/<br>LLWU_P9  | SPI0_SCK  | LPTMR0_<br>ALT2 |            |           | CMP0_OUT |      |

| 63   | 51   | 39  | 27  | PTC6/<br>LLWU_P10 | CMP0_IN0  | CMP0_IN0  | PTC6/<br>LLWU_P10 | SPI0_MOSI | EXTRG_IN        |            | SPI0_MISO |          |      |

| 64   | 52   | 40  | 28  | PTC7              | CMP0_IN1  | CMP0_IN1  | PTC7              | SPI0_MISO |                 |            | SPI0_MOSI |          |      |

| 65   | 53   | -   | _   | PTC8              | CMP0_IN2  | CMP0_IN2  | PTC8              | I2C0_SCL  | TPM0_CH4        |            |           |          |      |

| 66   | 54   | -   | _   | PTC9              | CMP0_IN3  | CMP0_IN3  | PTC9              | I2C0_SDA  | TPM0_CH5        |            |           |          |      |

| 67   | 55   | -   | -   | PTC10             | DISABLED  |           | PTC10             | I2C1_SCL  |                 |            |           |          |      |

| 68   | 56   | -   | _   | PTC11             | DISABLED  |           | PTC11             | I2C1_SDA  |                 |            |           |          |      |

| 69   | _    | _   | _   | PTC12             | DISABLED  |           | PTC12             |           |                 | TPM_CLKIN0 |           |          |      |

| 70   | _    | -   | _   | PTC13             | DISABLED  |           | PTC13             |           |                 | TPM_CLKIN1 |           |          |      |

| 71   | _    | -   | _   | PTC16             | DISABLED  |           | PTC16             |           |                 |            |           |          |      |

| 72   | _    | -   | _   | PTC17             | DISABLED  |           | PTC17             |           |                 |            |           |          |      |

| 73   | 57   | 41  | _   | PTD0              | DISABLED  |           | PTD0              | SPI0_PCS0 |                 | TPM0_CH0   |           |          |      |

| 74   | 58   | 42  | _   | PTD1              | ADC0_SE5b | ADC0_SE5b | PTD1              | SPI0_SCK  |                 | TPM0_CH1   |           |          |      |

| 75   | 59   | 43  | _   | PTD2              | DISABLED  |           | PTD2              | SPI0_MOSI | UART2_RX        | TPM0_CH2   | SPI0_MISO |          |      |

| 76   | 60   | 44  | _   | PTD3              | DISABLED  |           | PTD3              | SPI0_MISO | UART2_TX        | TPM0_CH3   | SPI0_MOSI |          |      |

| 77   | 61   | 45  | 29  | PTD4/<br>LLWU_P14 | DISABLED  |           | PTD4/<br>LLWU_P14 | SPI1_PCS0 | UART2_RX        | TPM0_CH4   |           |          |      |

| 78   | 62   | 46  | 30  | PTD5              | ADC0_SE6b | ADC0_SE6b | PTD5              | SPI1_SCK  | UART2_TX        | TPM0_CH5   |           |          |      |

| 79   | 63   | 47  | 31  | PTD6/<br>LLWU_P15 | ADC0_SE7b | ADC0_SE7b | PTD6/<br>LLWU_P15 | SPI1_MOSI | UART0_RX        |            | SPI1_MISO |          |      |

| 80   | 64   | 48  | 32  | PTD7              | DISABLED  |           | PTD7              | SPI1_MISO | UART0_TX        |            | SPI1_MOSI |          |      |

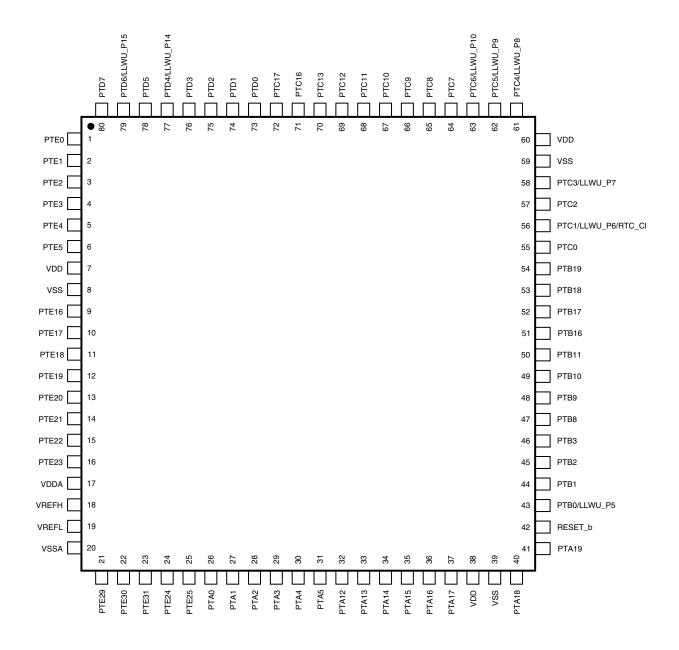

# 8.2 KL15 Pinouts

The below figures show the pinout diagrams for the devices supported by this document. Many signals may be multiplexed onto a single pin. To determine what signals can be used on which pin, see the previous section.

Pinout

Figure 17. KL15 80-pin LQFP pinout diagram