Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                      |

|----------------------------|----------------------------------------------------------------------|

| Product Status             | Obsolete                                                             |

| Core Processor             | ARM® Cortex®-M0+                                                     |

| Core Size                  | 32-Bit                                                               |

| Speed                      | 48MHz                                                                |

| Connectivity               | I <sup>2</sup> C, SPI, TSI, UART/USART                               |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                              |

| Number of I/O              | 70                                                                   |

| Program Memory Size        | 64KB (64K x 8)                                                       |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 8K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                         |

| Data Converters            | A/D 16b SAR; D/A 1x12b                                               |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                   |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 80-LQFP                                                              |

| Supplier Device Package    | 80-LQFP (12x12)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mkl15z64vlk4 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Ordering parts

#### 1.1 Determining valid orderable parts

Valid orderable part numbers are provided on the web. To determine the orderable part numbers for this device, go to www.freescale.com and perform a part number search for the following device numbers: PKL15 and MKL15

#### 2 Part identification

### 2.1 Description

Part numbers for the chip have fields that identify the specific part. You can use the values of these fields to determine the specific part you have received.

#### 2.2 Format

Part numbers for this device have the following format:

Q KL## A FFF R T PP CC N

#### 2.3 Fields

This table lists the possible values for each field in the part number (not all combinations are valid):

| Field | Description               | Values                                                                                         |

|-------|---------------------------|------------------------------------------------------------------------------------------------|

| Q     | Qualification status      | <ul> <li>M = Fully qualified, general market flow</li> <li>P = Prequalification</li> </ul>     |

| KL##  | Kinetis family            | • KL15                                                                                         |

| Α     | Key attribute             | • Z = Cortex-M0+                                                                               |

| FFF   | Program flash memory size | <ul> <li>32 = 32 KB</li> <li>64 = 64 KB</li> <li>128 = 128 KB</li> <li>256 = 256 KB</li> </ul> |

#### Terminology and guidelines

| Field | Description                 | Values                                                                                                                                                       |

|-------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R     | Silicon revision            | (Blank) = Main     A = Revision after main                                                                                                                   |

| Т     | Temperature range (°C)      | • V = -40 to 105                                                                                                                                             |

| PP    | Package identifier          | <ul> <li>FM = 32 QFN (5 mm x 5 mm)</li> <li>FT = 48 QFN (7 mm x 7 mm)</li> <li>LH = 64 LQFP (10 mm x 10 mm)</li> <li>LK = 80 LQFP (12 mm x 12 mm)</li> </ul> |

| CC    | Maximum CPU frequency (MHz) | • 4 = 48 MHz                                                                                                                                                 |

| N     | Packaging type              | R = Tape and reel (Blank) = Trays                                                                                                                            |

## 2.4 Example

This is an example part number:

MKL15Z32VFT4

# 3 Terminology and guidelines

## 3.1 Definition: Operating requirement

An *operating requirement* is a specified value or range of values for a technical characteristic that you must guarantee during operation to avoid incorrect operation and possibly decreasing the useful life of the chip.

## **3.1.1 Example**

This is an example of an operating requirement, which you must meet for the accompanying operating behaviors to be guaranteed:

| Symbol   | Description               | Min. | Max. | Unit |

|----------|---------------------------|------|------|------|

| $V_{DD}$ | 1.0 V core supply voltage | 0.9  | 1.1  | V    |

## 3.2 Definition: Operating behavior

An *operating behavior* is a specified value or range of values for a technical characteristic that are guaranteed during operation if you meet the operating requirements and any other specified conditions.

#### 3.2.1 Example

This is an example of an operating behavior, which is guaranteed if you meet the accompanying operating requirements:

| Symbol          | Description                                  | Min. | Max. | Unit |

|-----------------|----------------------------------------------|------|------|------|

| I <sub>WP</sub> | Digital I/O weak pullup/<br>pulldown current | 10   | 130  | μΑ   |

#### 3.3 Definition: Attribute

An *attribute* is a specified value or range of values for a technical characteristic that are guaranteed, regardless of whether you meet the operating requirements.

#### 3.3.1 Example

This is an example of an attribute:

| Symbol | Description                     | Min. | Max. | Unit |

|--------|---------------------------------|------|------|------|

| CIN_D  | Input capacitance: digital pins | _    | 7    | pF   |

### 3.4 Definition: Rating

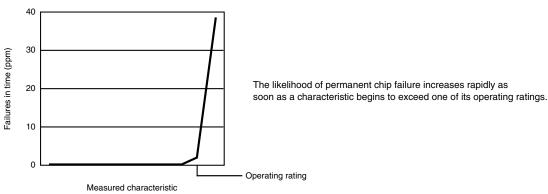

A *rating* is a minimum or maximum value of a technical characteristic that, if exceeded, may cause permanent chip failure:

- Operating ratings apply during operation of the chip.

- Handling ratings apply when the chip is not powered.

#### **3.4.1 Example**

This is an example of an operating rating:

| Symbol   | Description               | Min. | Max. | Unit |

|----------|---------------------------|------|------|------|

| $V_{DD}$ | 1.0 V core supply voltage | -0.3 | 1.2  | V    |

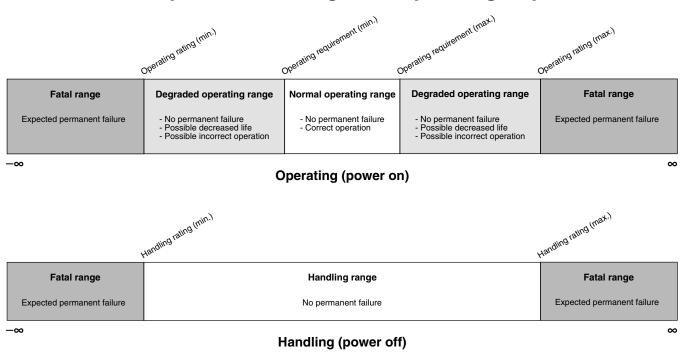

# 3.5 Result of exceeding a rating

# 3.6 Relationship between ratings and operating requirements

# 3.7 Guidelines for ratings and operating requirements

Follow these guidelines for ratings and operating requirements:

- Never exceed any of the chip's ratings.

- During normal operation, don't exceed any of the chip's operating requirements.

- If you must exceed an operating requirement at times other than during normal operation (for example, during power sequencing), limit the duration as much as possible.

### 3.8 Definition: Typical value

A typical value is a specified value for a technical characteristic that:

- Lies within the range of values specified by the operating behavior

- Given the typical manufacturing process, is representative of that characteristic during operation when you meet the typical-value conditions or other specified conditions

Typical values are provided as design guidelines and are neither tested nor guaranteed.

#### 3.8.1 **Example 1**

This is an example of an operating behavior that includes a typical value:

| Symbol          | Description                              | Min. | Тур. | Max. | Unit |

|-----------------|------------------------------------------|------|------|------|------|

| I <sub>WP</sub> | Digital I/O weak pullup/pulldown current | 10   | 70   | 130  | μΑ   |

## 3.8.2 Example 2

This is an example of a chart that shows typical values for various voltage and temperature conditions:

Table 2. V<sub>DD</sub> supply LVD and POR operating requirements (continued)

| Symbol            | Description                                              | Min. | Тур. | Max. | Unit | Notes |

|-------------------|----------------------------------------------------------|------|------|------|------|-------|

|                   | Low-voltage warning thresholds — low range               |      |      |      |      | 1     |

| $V_{LVW1L}$       | Level 1 falling (LVWV=00)                                | 1.74 | 1.80 | 1.86 | V    |       |

| $V_{LVW2L}$       | Level 2 falling (LVWV=01)                                | 1.84 | 1.90 | 1.96 | V    |       |

| $V_{LVW3L}$       | Level 3 falling (LVWV=10)                                | 1.94 | 2.00 | 2.06 | V    |       |

| $V_{LVW4L}$       | Level 4 falling (LVWV=11)                                | 2.04 | 2.10 | 2.16 | V    |       |

| V <sub>HYSL</sub> | Low-voltage inhibit reset/recover hysteresis — low range | _    | ±40  | _    | mV   |       |

| $V_{BG}$          | Bandgap voltage reference                                | 0.97 | 1.00 | 1.03 | V    |       |

| t <sub>LPO</sub>  | Internal low power oscillator period — factory trimmed   | 900  | 1000 | 1100 | μs   |       |

<sup>1.</sup> Rising thresholds are falling threshold + hysteresis voltage

# 5.2.3 Voltage and current operating behaviors

Table 3. Voltage and current operating behaviors

| Symbol           | Description                                                                           | Min.                  | Max.  | Unit | Notes |

|------------------|---------------------------------------------------------------------------------------|-----------------------|-------|------|-------|

| V <sub>OH</sub>  | Output high voltage — Normal drive pad                                                |                       |       |      | 1     |

|                  | • $2.7 \text{ V} \le \text{V}_{DD} \le 3.6 \text{ V}, \text{I}_{OH} = -5 \text{ mA}$  | V <sub>DD</sub> – 0.5 | _     | V    |       |

|                  | • 1.71 V ≤ V <sub>DD</sub> ≤ 2.7 V, I <sub>OH</sub> = -1.5 mA                         | V <sub>DD</sub> – 0.5 | _     | V    |       |

| V <sub>OH</sub>  | Output high voltage — High drive pad                                                  |                       |       |      | 1     |

|                  | • $2.7 \text{ V} \le \text{V}_{DD} \le 3.6 \text{ V}, \text{I}_{OH} = -18 \text{ mA}$ | V <sub>DD</sub> – 0.5 | _     | V    |       |

|                  | • 1.71 V ≤ V <sub>DD</sub> ≤ 2.7 V, I <sub>OH</sub> = -6 mA                           | V <sub>DD</sub> – 0.5 | _     | V    |       |

| I <sub>OHT</sub> | Output high current total for all ports                                               | _                     | 100   | mA   |       |

| V <sub>OL</sub>  | Output low voltage — Normal drive pad                                                 |                       |       |      | 1     |

|                  | • $2.7 \text{ V} \le \text{V}_{DD} \le 3.6 \text{ V}, \text{I}_{OL} = 5 \text{ mA}$   | _                     | 0.5   | V    |       |

|                  | • 1.71 V $\leq$ V <sub>DD</sub> $\leq$ 2.7 V, I <sub>OL</sub> = 1.5 mA                | _                     | 0.5   | V    |       |

| V <sub>OL</sub>  | Output low voltage — High drive pad                                                   |                       |       |      | 1     |

|                  | • $2.7 \text{ V} \le \text{V}_{DD} \le 3.6 \text{ V}, \text{I}_{OL} = 18 \text{ mA}$  | _                     | 0.5   | V    |       |

|                  | • 1.71 V ≤ V <sub>DD</sub> ≤ 2.7 V, I <sub>OL</sub> = 6 mA                            | _                     | 0.5   | V    |       |

| I <sub>OLT</sub> | Output low current total for all ports                                                | _                     | 100   | mA   |       |

| I <sub>IN</sub>  | Input leakage current (per pin) for full temperature range                            | _                     | 1     | μA   | 2     |

| I <sub>IN</sub>  | Input leakage current (per pin) at 25 °C                                              | _                     | 0.025 | μA   | 2     |

| I <sub>IN</sub>  | Input leakage current (total all pins) for full temperature range                     | _                     | 65    | μA   | 2     |

| l <sub>OZ</sub>  | Hi-Z (off-state) leakage current (per pin)                                            | _                     | 1     | μΑ   |       |

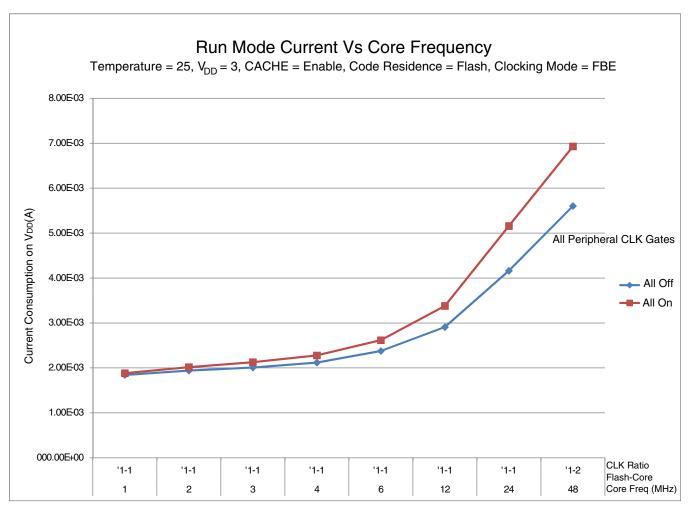

# 5.2.5 Power consumption operating behaviors

#### Table 5. Power consumption operating behaviors

| Symbol                       | Description                                                                                                                                                                        | Min. | Тур. | Max.     | Unit | Notes |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|----------|------|-------|

| I <sub>DDA</sub>             | Analog supply current                                                                                                                                                              | _    | _    | See note | mA   | 1     |

| I <sub>DD_RUNCO_</sub><br>CM | Run mode current in compute operation - 48 MHz core / 24 MHz flash/ bus disabled, LPTMR running using 4MHz internal reference clock, CoreMark® benchmark code executing from flash | _    | 6.4  | _        | mA   | 2     |

|                              | • at 3.0 V                                                                                                                                                                         |      |      |          |      |       |

| I <sub>DD_RUNCO</sub>        | Run mode current in compute operation - 48 MHz core / 24 MHz flash / bus clock disabled, code of while(1) loop executing from flash • at 3.0 V                                     | _    | 4.1  | 5.2      | mA   | 3     |

|                              |                                                                                                                                                                                    |      |      |          |      |       |

| I <sub>DD_RUN</sub>          | Run mode current - 48 MHz core / 24 MHz bus and flash, all peripheral clocks disabled, code of while(1) loop executing from flash                                                  |      | F 1  | 6.0      | A    | 3     |

|                              | • at 3.0 V                                                                                                                                                                         | _    | 5.1  | 6.3      | mA   |       |

| I <sub>DD_RUN</sub>          | Run mode current - 48 MHz core / 24 MHz bus<br>and flash, all peripheral clocks enabled, code of<br>while(1) loop executing from flash                                             |      |      |          |      | 3, 4, |

|                              | • at 3.0 V                                                                                                                                                                         |      |      |          |      |       |

|                              | • at 25 °C                                                                                                                                                                         | _    | 6.4  | 7.8      | mA   |       |

|                              | • at 125 °C                                                                                                                                                                        | _    | 6.8  | 8.3      | mA   |       |

| I <sub>DD_WAIT</sub>         | Wait mode current - core disabled / 48 MHz<br>system / 24 MHz bus / flash disabled (flash doze<br>enabled), all peripheral clocks disabled<br>• at 3.0 V                           | _    | 3.7  | 5.0      | mA   | 3     |

| I <sub>DD_WAIT</sub>         | Wait mode current - core disabled / 24 MHz<br>system / 24 MHz bus / flash disabled (flash doze<br>enabled), all peripheral clocks disabled<br>• at 3.0 V                           | _    | 2.9  | 4.2      | mA   | 3     |

| I <sub>DD_PSTOP2</sub>       | Stop mode current with partial stop 2 clocking option - core and system disabled / 10.5 MHz bus  • at 3.0 V                                                                        | _    | 2.5  | 3.7      | mA   | 3     |

| I <sub>DD_VLPRCO</sub>       | Very low power run mode current in compute operation - 4 MHz core / 0.8 MHz flash / bus clock disabled, code of while(1) loop executing from flash  • at 3.0 V                     | _    | 188  | 570      | μΑ   | 5     |

| I <sub>DD_VLPR</sub>         | Very low power run mode current - 4 MHz core / 0.8 MHz bus and flash, all peripheral clocks disabled, code of while(1) loop executing from flash • at 3.0 V                        | _    | 224  | 613      | μА   | 5     |

|                              | 1                                                                                                                                                                                  | I    | I    | 1        |      | I     |

Table 6. Low power mode peripheral adders — typical value (continued)

| Symbol           | Description                                                                                                                                                                                                                                                                           |     | •   | Tempera | ature (°C | ;)  |     | Ur |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|---------|-----------|-----|-----|----|

|                  |                                                                                                                                                                                                                                                                                       | -40 | 25  | 50      | 70        | 85  | 105 | 1  |

| lerefsten32kHz   | External 32 kHz crystal clock adder by means of the OSC0_CR[EREFSTEN and EREFSTEN] bits. Measured by                                                                                                                                                                                  |     |     |         |           |     |     |    |

|                  | entering all modes with the crystal                                                                                                                                                                                                                                                   | 440 | 490 | 540     | 560       | 570 | 580 |    |

|                  | enabled.                                                                                                                                                                                                                                                                              | 440 | 490 | 540     | 560       | 570 | 580 |    |

|                  | VLLS1                                                                                                                                                                                                                                                                                 | 490 | 490 | 540     | 560       | 570 | 680 | n  |

|                  | VLLS3                                                                                                                                                                                                                                                                                 | 510 | 560 | 560     | 560       | 610 | 680 |    |

|                  | LLS                                                                                                                                                                                                                                                                                   | 510 | 560 | 560     | 560       | 610 | 680 |    |

|                  | VLPS                                                                                                                                                                                                                                                                                  |     |     |         |           |     |     |    |

|                  | STOP                                                                                                                                                                                                                                                                                  |     |     |         |           |     |     |    |

| I <sub>CMP</sub> | CMP peripheral adder measured by placing the device in VLLS1 mode with CMP enabled using the 6-bit DAC and a single external input for compare. Includes 6-bit DAC power consumption.                                                                                                 | 22  | 22  | 22      | 22        | 22  | 22  | ٢  |

| I <sub>RTC</sub> | RTC peripheral adder measured by placing the device in VLLS1 mode with external 32 kHz crystal enabled by means of the RTC_CR[OSCE] bit and the RTC ALARM set for 1 minute. Includes ERCLK32K (32 kHz external crystal) power consumption.                                            | 432 | 357 | 388     | 475       | 532 | 810 | n  |

| luart            | UART peripheral adder measured by placing the device in STOP or VLPS mode with selected clock source waiting for RX data at 115200 baud rate. Includes selected clock source power consumption.                                                                                       |     |     |         |           |     |     |    |

|                  | MCGIRCLK (4MHz internal reference clock)                                                                                                                                                                                                                                              | 66  | 66  | 66      | 66        | 66  | 66  | μ  |

|                  | OSCERCLK (4MHz external crystal)                                                                                                                                                                                                                                                      | 214 | 237 | 246     | 254       | 260 | 268 |    |

| I <sub>TPM</sub> | TPM peripheral adder measured by placing the device in STOP or VLPS mode with selected clock source configured for output compare generating 100Hz clock signal. No load is placed on the I/O generating the clock signal. Includes selected clock source and I/O switching currents. |     |     |         |           |     |     | μ  |

|                  | MCGIRCLK (4MHz internal reference clock)                                                                                                                                                                                                                                              | 86  | 86  | 86      | 86        | 86  | 86  |    |

|                  | OSCERCLK (4MHz external crystal)                                                                                                                                                                                                                                                      | 235 | 256 | 265     | 274       | 280 | 287 |    |

| I <sub>BG</sub>  | Bandgap adder when BGEN bit is set and device is placed in VLPx, LLS, or VLLSx mode.                                                                                                                                                                                                  | 45  | 45  | 45      | 45        | 45  | 45  | μ  |

Figure 2. Run mode supply current vs. core frequency

#### General

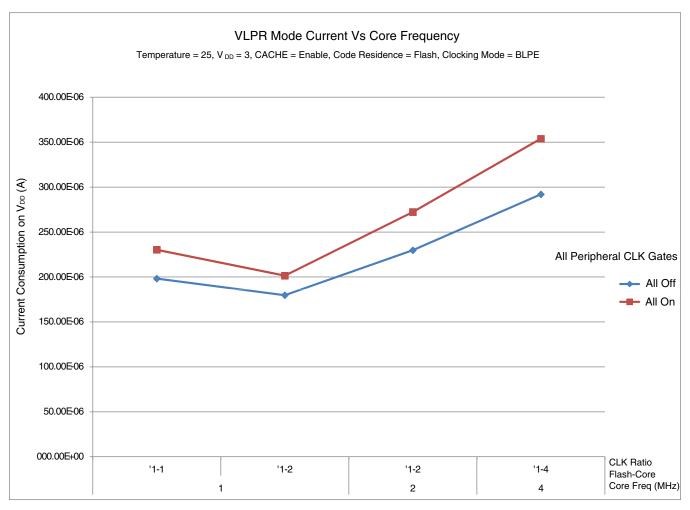

Figure 3. VLPR mode current vs. core frequency

#### 5.2.6 EMC radiated emissions operating behaviors

Table 7. EMC radiated emissions operating behaviors for 64-pin LQFP package

| Symbol              | Description                        | Frequency band (MHz) | Тур. | Unit | Notes |

|---------------------|------------------------------------|----------------------|------|------|-------|

| V <sub>RE1</sub>    | Radiated emissions voltage, band 1 | 0.15–50              | 13   | dΒμV | 1, 2  |

| V <sub>RE2</sub>    | Radiated emissions voltage, band 2 | 50–150               | 15   | dΒμV |       |

| V <sub>RE3</sub>    | Radiated emissions voltage, band 3 | 150–500              | 12   | dΒμV |       |

| V <sub>RE4</sub>    | Radiated emissions voltage, band 4 | 500-1000             | 7    | dΒμV |       |

| V <sub>RE_IEC</sub> | IEC level                          | 0.15-1000            | М    | _    | 2, 3  |

Determined according to IEC Standard 61967-1, Integrated Circuits - Measurement of Electromagnetic Emissions, 150

kHz to 1 GHz Part 1: General Conditions and Definitions and IEC Standard 61967-2, Integrated Circuits - Measurement of

Electromagnetic Emissions, 150 kHz to 1 GHz Part 2: Measurement of Radiated Emissions—TEM Cell and Wideband

TEM Cell Method. Measurements were made while the microcontroller was running basic application code. The reported

emission level is the value of the maximum measured emission, rounded up to the next whole number, from among the

measured orientations in each frequency range.

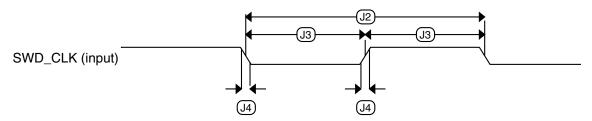

Table 11. SWD full voltage range electricals (continued)

| Symbol | Description                                     | Min. | Max. | Unit |

|--------|-------------------------------------------------|------|------|------|

| J1     | SWD_CLK frequency of operation                  |      |      |      |

|        | Serial wire debug                               | 0    | 25   | MHz  |

| J2     | SWD_CLK cycle period                            | 1/J1 | _    | ns   |

| J3     | SWD_CLK clock pulse width                       |      |      |      |

|        | Serial wire debug                               | 20   | _    | ns   |

| J4     | SWD_CLK rise and fall times                     | _    | 3    | ns   |

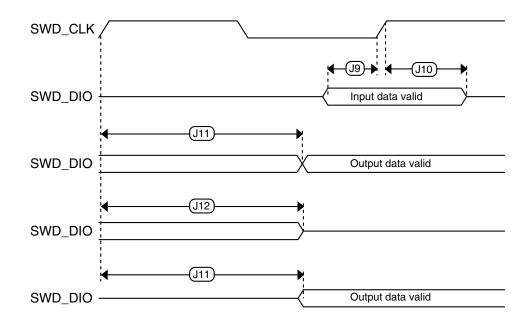

| J9     | SWD_DIO input data setup time to SWD_CLK rise   | 10   | _    | ns   |

| J10    | SWD_DIO input data hold time after SWD_CLK rise | 0    | _    | ns   |

| J11    | SWD_CLK high to SWD_DIO data valid              | _    | 32   | ns   |

| J12    | SWD_CLK high to SWD_DIO high-Z                  | 5    | _    | ns   |

Figure 4. Serial wire clock input timing

Figure 5. Serial wire data timing

Table 19. 16-bit ADC operating conditions (continued)

| Symbol | Description    | Conditions                                                 | Min.   | Typ. <sup>1</sup> | Max.    | Unit | Notes |

|--------|----------------|------------------------------------------------------------|--------|-------------------|---------|------|-------|

| - Tale | ADC conversion | 16-bit mode                                                |        |                   |         |      | 6     |

|        | rate           | No ADC hardware averaging                                  | 37.037 | _                 | 461.467 | Ksps |       |

|        |                | Continuous conversions enabled, subsequent conversion time |        |                   |         |      |       |

- Typical values assume V<sub>DDA</sub> = 3.0 V, Temp = 25 °C, f<sub>ADCK</sub> = 1.0 MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

- 2. DC potential difference.

- For packages without dedicated VREFH and VREFL pins, V<sub>REFH</sub> is internally tied to V<sub>DDA</sub>, and V<sub>REFL</sub> is internally tied to V<sub>SSA</sub>.

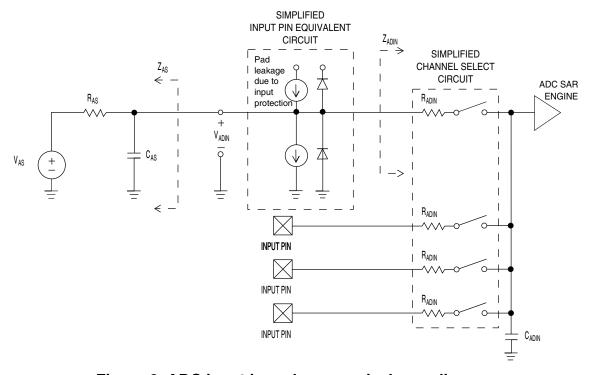

- 4. This resistance is external to MCU. The analog source resistance must be kept as low as possible to achieve the best results. The results in this data sheet were derived from a system which has < 8  $\Omega$  analog source resistance. The R<sub>AS</sub>/C<sub>AS</sub> time constant should be kept to < 1ns.

- 5. To use the maximum ADC conversion clock frequency, the ADHSC bit must be set and the ADLPC bit must be clear.

- 6. For guidelines and examples of conversion rate calculation, download the ADC calculator tool

Figure 6. ADC input impedance equivalency diagram

#### 6.6.1.2 16-bit ADC electrical characteristics Table 20. 16-bit ADC characteristics ( $V_{REFH} = V_{DDA}$ , $V_{REFL} = V_{SSA}$ )

| Symbol               | Description    | Conditions <sup>1</sup> | Min.  | Typ. <sup>2</sup> | Max. | Unit | Notes |  |

|----------------------|----------------|-------------------------|-------|-------------------|------|------|-------|--|

| I <sub>DDA_ADC</sub> | Supply current |                         | 0.215 |                   | 1.7  | mA   | 3     |  |

Table 20. 16-bit ADC characteristics ( $V_{REFH} = V_{DDA}$ ,  $V_{REFL} = V_{SSA}$ ) (continued)

| Symbol             | Description                     | Conditions <sup>1</sup>      | Min.         | Typ. <sup>2</sup> | Max.         | Unit             | Notes                   |

|--------------------|---------------------------------|------------------------------|--------------|-------------------|--------------|------------------|-------------------------|

|                    | ADC .                           | • ADLPC = 1, ADHSC = 0       | 1.2          | 2.4               | 3.9          | MHz              | t <sub>ADACK</sub> = 1/ |

| _                  | asynchronous clock source       | • ADLPC = 1, ADHSC = 1       | 2.4          | 4.0               | 6.1          | MHz              | f <sub>ADACK</sub>      |

| f <sub>ADACK</sub> | order domination                | • ADLPC = 0, ADHSC = 0       | 3.0          | 5.2               | 7.3          | MHz              |                         |

|                    |                                 | • ADLPC = 0, ADHSC = 1       | 4.4          | 6.2               | 9.5          | MHz              |                         |

|                    | Sample Time                     | See Reference Manual chapter | for sample t | imes              |              |                  |                         |

| TUE                | Total unadjusted                | 12-bit modes                 | _            | ±4                | ±6.8         | LSB <sup>4</sup> | 5                       |

|                    | error                           | <12-bit modes                | _            | ±1.4              | ±2.1         |                  |                         |

| DNL                | Differential non-               | 12-bit modes                 | _            | ±0.7              | -1.1 to +1.9 | LSB <sup>4</sup> | 5                       |

|                    | linearity                       |                              |              |                   | -0.3 to 0.5  |                  |                         |

|                    |                                 | • <12-bit modes              | _            | ±0.2              |              |                  |                         |

| INL                | Integral non-                   | 12-bit modes                 | _            | ±1.0              | -2.7 to +1.9 | LSB <sup>4</sup> | 5                       |

|                    | linearity                       |                              |              |                   | -0.7 to +0.5 |                  |                         |

|                    |                                 | <12-bit modes                | _            | ±0.5              |              |                  |                         |

| $E_FS$             | Full-scale error • 12-bit modes |                              | _            | -4                | -5.4         | LSB <sup>4</sup> | V <sub>ADIN</sub> =     |

|                    |                                 | • <12-bit modes              | _            | -1.4              | -1.8         |                  | V <sub>DDA</sub>        |

| E <sub>Q</sub>     | Quantization                    | 16-bit modes                 | _            | -1 to 0           | _            | LSB <sup>4</sup> |                         |

|                    | error                           | • ≤1312-bit modes            | _            | _                 | ±0.5         |                  |                         |

| ENOB               | Effective number                | 16-bit differential mode     |              |                   |              |                  | 6                       |

|                    | of bits                         | • Avg = 32                   | 12.8         | 14.5              | _            | bits             |                         |

|                    |                                 | • Avg = 4                    | 11.9         | 13.8              | _            | bits             |                         |

|                    |                                 | 16-bit single-ended mode     |              |                   |              |                  |                         |

|                    |                                 | • Avg = 32                   | 10.0         | 40.0              |              | la ta a          |                         |

|                    |                                 | • Avg = 4                    | 12.2         | 13.9              | _            | bits             |                         |

|                    | Signal-to-noise                 | See ENOB                     | 11.4         | 13.1              | _            | bits             |                         |

| SINAD              | plus distortion                 | See ENOD                     | 6.02         | 2 × ENOB +        | 1.76         | dB               |                         |

| THD                | Total harmonic                  | 16-bit differential mode     |              |                   |              |                  | 7                       |

|                    | distortion                      | • Avg = 32                   | _            | -94               | _            | dB               |                         |

|                    |                                 | 16-bit single-ended mode     |              |                   |              |                  |                         |

|                    |                                 | • Avg = 32                   | _            | -85               | _            | dB               |                         |

| SFDR               | Spurious free                   | 16-bit differential mode     |              |                   |              |                  | 7                       |

|                    | dynamic range                   | • Avg = 32                   | 82           | 95                |              | dB               |                         |

|                    |                                 | 16-bit single-ended mode     |              |                   |              |                  |                         |

|                    |                                 | • Avg = 32                   | 78           | 90                | _            | dB               |                         |

# 6.6.3.1 12-bit DAC operating requirements Table 22. 12-bit DAC operating requirements

| Symbol            | Desciption                    | Min.                   | Max.                    | Unit | Notes |

|-------------------|-------------------------------|------------------------|-------------------------|------|-------|

| $V_{DDA}$         | Supply voltage                | 1.71                   | 3.6                     | V    |       |

| V <sub>DACR</sub> | Reference voltage             | 1.13                   | 3.6                     | V    | 1     |

| T <sub>A</sub>    | Temperature                   | Operating t range of t | emperature<br>he device | °C   |       |

| C <sub>L</sub>    | Output load capacitance — 100 |                        | 100                     | pF   | 2     |

| ΙL                | Output load current           | _                      | 1                       | mA   |       |

- 1. The DAC reference can be selected to be  $V_{\text{DDA}}$  or the voltage output of the VREF module (VREF\_OUT)

- 2. A small load capacitance (47 pF) can improve the bandwidth performance of the DAC

# 6.6.3.2 12-bit DAC operating behaviors Table 23. 12-bit DAC operating behaviors

| Symbol                     | Description                                                                       | Min.                      | Тур.     | Max.              | Unit   | Notes |

|----------------------------|-----------------------------------------------------------------------------------|---------------------------|----------|-------------------|--------|-------|

| I <sub>DDA_DACL</sub><br>P | Supply current — low-power mode                                                   | _                         | _        | 250               | μΑ     |       |

| I <sub>DDA_DACH</sub>      | Supply current — high-speed mode                                                  | _                         | _        | 900               | μА     |       |

| t <sub>DACLP</sub>         | Full-scale settling time (0x080 to 0xF7F) — low-power mode                        | _                         | 100      | 200               | μs     | 1     |

| t <sub>DACHP</sub>         | Full-scale settling time (0x080 to 0xF7F) — high-power mode                       | _                         | 15       | 30                | μs     | 1     |

| t <sub>CCDACLP</sub>       | Code-to-code settling time (0xBF8 to 0xC08)  — low-power mode and high-speed mode | _                         | 0.7      | 1                 | μs     | 1     |

| V <sub>dacoutl</sub>       | DAC output voltage range low — high-speed mode, no load, DAC set to 0x000         | _                         | _        | 100               | mV     |       |

| V <sub>dacouth</sub>       | DAC output voltage range high — high-<br>speed mode, no load, DAC set to 0xFFF    | V <sub>DACR</sub><br>-100 | _        | V <sub>DACR</sub> | mV     |       |

| INL                        | Integral non-linearity error — high speed mode                                    | _                         | _        | ±8                | LSB    | 2     |

| DNL                        | Differential non-linearity error — V <sub>DACR</sub> > 2<br>V                     | _                         | _        | ±1                | LSB    | 3     |

| DNL                        | Differential non-linearity error — V <sub>DACR</sub> = VREF_OUT                   | _                         | _        | ±1                | LSB    | 4     |

| V <sub>OFFSET</sub>        | Offset error                                                                      | _                         | ±0.4     | ±0.8              | %FSR   | 5     |

| E <sub>G</sub>             | Gain error                                                                        | _                         | ±0.1     | ±0.6              | %FSR   | 5     |

| PSRR                       | Power supply rejection ratio, V <sub>DDA</sub> ≥ 2.4 V                            | 60                        | _        | 90                | dB     |       |

| T <sub>CO</sub>            | Temperature coefficient offset voltage                                            | _                         | 3.7      | _                 | μV/C   | 6     |

| T <sub>GE</sub>            | Temperature coefficient gain error                                                | _                         | 0.000421 | _                 | %FSR/C |       |

| Rop                        | Output resistance load = $3 \text{ k}\Omega$                                      |                           | _        | 250               | Ω      |       |

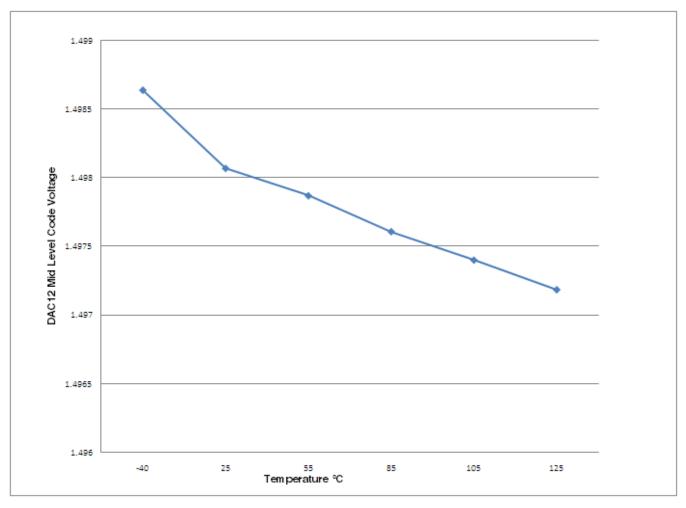

Figure 12. Offset at half scale vs. temperature

#### 6.7 Timers

See General switching specifications.

#### 6.8 Communication interfaces

# 6.8.1 SPI switching specifications

The Serial Peripheral Interface (SPI) provides a synchronous serial bus with master and slave operations. Many of the transfer attributes are programmable. The following tables provide timing characteristics for classic SPI timing modes. See the SPI chapter of the chip's Reference Manual for information about the modified transfer formats used for communicating with slower peripheral devices.

KL15 Sub-Family Data Sheet Data Sheet, Rev. 3, 9/19/2012.

#### Peripheral operating requirements and behaviors

All timing is shown with respect to  $20\%~V_{DD}$  and  $80\%~V_{DD}$  thresholds, unless noted, as well as input signal transitions of 3 ns and a 30 pF maximum load on all SPI pins.

Table 24. SPI master mode timing on slew rate disabled pads

| Num. | Symbol              | Description                    | Min.                      | Max.                     | Unit               | Note |

|------|---------------------|--------------------------------|---------------------------|--------------------------|--------------------|------|

| 1    | f <sub>op</sub>     | Frequency of operation         | f <sub>periph</sub> /2048 | f <sub>periph</sub> /2   | Hz                 | 1    |

| 2    | t <sub>SPSCK</sub>  | SPSCK period                   | 2 x t <sub>periph</sub>   | 2048 x                   | ns                 | 2    |

|      |                     |                                |                           | t <sub>periph</sub>      |                    |      |

| 3    | t <sub>Lead</sub>   | Enable lead time               | 1/2                       | _                        | t <sub>SPSCK</sub> | _    |

| 4    | t <sub>Lag</sub>    | Enable lag time                | 1/2                       | _                        | t <sub>SPSCK</sub> | _    |

| 5    | t <sub>WSPSCK</sub> | Clock (SPSCK) high or low time | t <sub>periph</sub> - 30  | 1024 x                   | ns                 | _    |

|      |                     |                                |                           | t <sub>periph</sub>      |                    |      |

| 6    | t <sub>SU</sub>     | Data setup time (inputs)       | 16                        | _                        | ns                 | _    |

| 7    | t <sub>HI</sub>     | Data hold time (inputs)        | 0                         | _                        | ns                 | _    |

| 8    | t <sub>v</sub>      | Data valid (after SPSCK edge)  | _                         | 10                       | ns                 | _    |

| 9    | t <sub>HO</sub>     | Data hold time (outputs)       | 0                         | _                        | ns                 | _    |

| 10   | t <sub>RI</sub>     | Rise time input                | _                         | t <sub>periph</sub> - 25 | ns                 | _    |

|      | t <sub>FI</sub>     | Fall time input                |                           |                          |                    |      |

| 11   | t <sub>RO</sub>     | Rise time output               | _                         | 25                       | ns                 | _    |

|      | t <sub>FO</sub>     | Fall time output               |                           |                          |                    |      |

<sup>1.</sup> For SPI0  $f_{periph}$  is the bus clock ( $f_{BUS}$ ). For SPI1  $f_{periph}$  is the system clock ( $f_{SYS}$ ).

Table 25. SPI master mode timing on slew rate enabled pads

| Num. | Symbol              | Description                    | Min.                      | Max.                     | Unit               | Note |

|------|---------------------|--------------------------------|---------------------------|--------------------------|--------------------|------|

| 1    | f <sub>op</sub>     | Frequency of operation         | f <sub>periph</sub> /2048 | f <sub>periph</sub> /2   | Hz                 | 1    |

| 2    | t <sub>SPSCK</sub>  | SPSCK period                   | 2 x t <sub>periph</sub>   | 2048 x                   | ns                 | 2    |

|      |                     |                                |                           | t <sub>periph</sub>      |                    |      |

| 3    | t <sub>Lead</sub>   | Enable lead time               | 1/2                       | _                        | t <sub>SPSCK</sub> | _    |

| 4    | t <sub>Lag</sub>    | Enable lag time                | 1/2                       | _                        | t <sub>SPSCK</sub> | _    |

| 5    | t <sub>WSPSCK</sub> | Clock (SPSCK) high or low time | t <sub>periph</sub> - 30  | 1024 x                   | ns                 | _    |

|      |                     |                                |                           | t <sub>periph</sub>      |                    |      |

| 6    | t <sub>SU</sub>     | Data setup time (inputs)       | 96                        | _                        | ns                 | _    |

| 7    | t <sub>HI</sub>     | Data hold time (inputs)        | 0                         | _                        | ns                 | _    |

| 8    | t <sub>v</sub>      | Data valid (after SPSCK edge)  | _                         | 52                       | ns                 | _    |

| 9    | t <sub>HO</sub>     | Data hold time (outputs)       | 0                         | _                        | ns                 | _    |

| 10   | t <sub>RI</sub>     | Rise time input                | _                         | t <sub>periph</sub> - 25 | ns                 | _    |

|      | t <sub>Fl</sub>     | Fall time input                |                           |                          |                    |      |

| 11   | t <sub>RO</sub>     | Rise time output               | _                         | 36                       | ns                 | _    |

|      | t <sub>FO</sub>     | Fall time output               |                           |                          |                    |      |

<sup>1.</sup> For SPI0  $f_{periph}$  is the bus clock ( $f_{BUS}$ ). For SPI1  $f_{periph}$  is the system clock ( $f_{SYS}$ ).

<sup>2.</sup>  $t_{periph} = 1/f_{periph}$

<sup>2.</sup>  $t_{periph} = 1/f_{periph}$

#### **Pinout**

| 80<br>LQFP | 64<br>LQFP | 48<br>QFN | 32<br>QFN | Pin Name                       | Default                 | ALT0                    | ALT1                           | ALT2      | ALT3     | ALT4       | ALT5      | ALT6            | ALT7    |

|------------|------------|-----------|-----------|--------------------------------|-------------------------|-------------------------|--------------------------------|-----------|----------|------------|-----------|-----------------|---------|

| 29         | 25         | 20        | 13        | PTA3                           | SWD_DIO                 | TSI0_CH4                | PTA3                           | I2C1_SCL  | TPM0_CH0 |            |           |                 | SWD_DIO |

| 30         | 26         | 21        | 14        | PTA4                           | NMI_b                   | TSI0_CH5                | PTA4                           | I2C1_SDA  | TPM0_CH1 |            |           |                 | NMI_b   |

| 31         | 27         | ı         | _         | PTA5                           | DISABLED                |                         | PTA5                           |           | TPM0_CH2 |            |           |                 |         |

| 32         | 28         | -         | _         | PTA12                          | DISABLED                |                         | PTA12                          |           | TPM1_CH0 |            |           |                 |         |

| 33         | 29         | -         | _         | PTA13                          | DISABLED                |                         | PTA13                          |           | TPM1_CH1 |            |           |                 |         |

| 34         | _          | _         | _         | PTA14                          | DISABLED                |                         | PTA14                          | SPI0_PCS0 | UARTO_TX |            |           |                 |         |

| 35         | 1          | -         | _         | PTA15                          | DISABLED                |                         | PTA15                          | SPI0_SCK  | UARTO_RX |            |           |                 |         |

| 36         | _          | _         | _         | PTA16                          | DISABLED                |                         | PTA16                          | SPI0_MOSI |          |            | SPI0_MISO |                 |         |

| 37         | 1          | -         | _         | PTA17                          | DISABLED                |                         | PTA17                          | SPI0_MISO |          |            | SPI0_MOSI |                 |         |

| 38         | 30         | 22        | 15        | VDD                            | VDD                     | VDD                     |                                |           |          |            |           |                 |         |

| 39         | 31         | 23        | 16        | VSS                            | VSS                     | VSS                     |                                |           |          |            |           |                 |         |

| 40         | 32         | 24        | 17        | PTA18                          | EXTAL0                  | EXTAL0                  | PTA18                          |           | UART1_RX | TPM_CLKIN0 |           |                 |         |

| 41         | 33         | 25        | 18        | PTA19                          | XTAL0                   | XTAL0                   | PTA19                          |           | UART1_TX | TPM_CLKIN1 |           | LPTMR0_<br>ALT1 |         |

| 42         | 34         | 26        | 19        | RESET_b                        | RESET_b                 |                         | PTA20                          |           |          |            |           |                 |         |

| 43         | 35         | 27        | 20        | PTB0/<br>LLWU_P5               | ADC0_SE8/<br>TSI0_CH0   | ADC0_SE8/<br>TSI0_CH0   | PTB0/<br>LLWU_P5               | I2C0_SCL  | TPM1_CH0 |            |           |                 |         |

| 44         | 36         | 28        | 21        | PTB1                           | ADC0_SE9/<br>TSI0_CH6   | ADC0_SE9/<br>TSI0_CH6   | PTB1                           | I2C0_SDA  | TPM1_CH1 |            |           |                 |         |

| 45         | 37         | 29        | -         | PTB2                           | ADC0_SE12/<br>TSI0_CH7  | ADC0_SE12/<br>TSI0_CH7  | PTB2                           | I2C0_SCL  | TPM2_CH0 |            |           |                 |         |

| 46         | 38         | 30        | -         | PTB3                           | ADC0_SE13/<br>TSI0_CH8  | ADC0_SE13/<br>TSI0_CH8  | PTB3                           | I2CO_SDA  | TPM2_CH1 |            |           |                 |         |

| 47         | 1          | -         | _         | PTB8                           | DISABLED                |                         | PTB8                           |           | EXTRG_IN |            |           |                 |         |

| 48         | 1          | -         | _         | PTB9                           | DISABLED                |                         | PTB9                           |           |          |            |           |                 |         |

| 49         | ı          | -         | _         | PTB10                          | DISABLED                |                         | PTB10                          | SPI1_PCS0 |          |            |           |                 |         |

| 50         | 1          | -         | _         | PTB11                          | DISABLED                |                         | PTB11                          | SPI1_SCK  |          |            |           |                 |         |

| 51         | 39         | 31        | _         | PTB16                          | TSI0_CH9                | TSI0_CH9                | PTB16                          | SPI1_MOSI | UARTO_RX | TPM_CLKIN0 | SPI1_MISO |                 |         |

| 52         | 40         | 32        | _         | PTB17                          | TSI0_CH10               | TSI0_CH10               | PTB17                          | SPI1_MISO | UARTO_TX | TPM_CLKIN1 | SPI1_MOSI |                 |         |

| 53         | 41         | _         | _         | PTB18                          | TSI0_CH11               | TSI0_CH11               | PTB18                          |           | TPM2_CH0 |            |           |                 |         |

| 54         | 42         | _         | _         | PTB19                          | TSI0_CH12               | TSI0_CH12               | PTB19                          |           | TPM2_CH1 |            |           |                 |         |

| 55         | 43         | 33        | _         | PTC0                           | ADC0_SE14/<br>TSI0_CH13 | ADC0_SE14/<br>TSI0_CH13 | PTC0                           |           | EXTRG_IN |            | CMP0_OUT  |                 |         |

| 56         | 44         | 34        | 22        | PTC1/<br>LLWU_P6/<br>RTC_CLKIN | ADC0_SE15/<br>TSI0_CH14 | ADC0_SE15/<br>TSI0_CH14 | PTC1/<br>LLWU_P6/<br>RTC_CLKIN | I2C1_SCL  |          | TPM0_CH0   |           |                 |         |

| 57         | 45         | 35        | 23        | PTC2                           | ADC0_SE11/<br>TSI0_CH15 | ADC0_SE11/<br>TSI0_CH15 | PTC2                           | I2C1_SDA  |          | TPM0_CH1   |           |                 |         |

| 58         | 46         | 36        | 24        | PTC3/<br>LLWU_P7               | DISABLED                |                         | PTC3/<br>LLWU_P7               |           | UART1_RX | TPM0_CH2   | CLKOUT    |                 |         |

| 59         | 47         | -         | -         | VSS                            | VSS                     | VSS                     |                                |           |          |            |           |                 |         |

| 60         | 48         | -         | _         | VDD                            | VDD                     | VDD                     |                                |           |          |            |           |                 |         |

| 61         | 49         | 37        | 25        | PTC4/<br>LLWU_P8               | DISABLED                |                         | PTC4/<br>LLWU_P8               | SPI0_PCS0 | UART1_TX | TPM0_CH3   |           |                 |         |

| 80<br>LQFP | 64<br>LQFP | 48<br>QFN | 32<br>QFN | Pin Name          | Default   | ALT0      | ALT1              | ALT2      | ALT3            | ALT4       | ALT5      | ALT6     | ALT7 |

|------------|------------|-----------|-----------|-------------------|-----------|-----------|-------------------|-----------|-----------------|------------|-----------|----------|------|

| 62         | 50         | 38        | 26        | PTC5/<br>LLWU_P9  | DISABLED  |           | PTC5/<br>LLWU_P9  | SPI0_SCK  | LPTMR0_<br>ALT2 |            |           | CMP0_OUT |      |

| 63         | 51         | 39        | 27        | PTC6/<br>LLWU_P10 | CMP0_IN0  | CMP0_IN0  | PTC6/<br>LLWU_P10 | SPI0_MOSI | EXTRG_IN        |            | SPI0_MISO |          |      |

| 64         | 52         | 40        | 28        | PTC7              | CMP0_IN1  | CMP0_IN1  | PTC7              | SPI0_MISO |                 |            | SPI0_MOSI |          |      |

| 65         | 53         | -         | -         | PTC8              | CMP0_IN2  | CMP0_IN2  | PTC8              | I2C0_SCL  | TPM0_CH4        |            |           |          |      |

| 66         | 54         | -         | -         | PTC9              | CMP0_IN3  | CMP0_IN3  | PTC9              | I2CO_SDA  | TPM0_CH5        |            |           |          |      |

| 67         | 55         | -         | _         | PTC10             | DISABLED  |           | PTC10             | I2C1_SCL  |                 |            |           |          |      |

| 68         | 56         | -         | _         | PTC11             | DISABLED  |           | PTC11             | I2C1_SDA  |                 |            |           |          |      |

| 69         | _          | -         | -         | PTC12             | DISABLED  |           | PTC12             |           |                 | TPM_CLKIN0 |           |          |      |

| 70         | _          | -         | _         | PTC13             | DISABLED  |           | PTC13             |           |                 | TPM_CLKIN1 |           |          |      |

| 71         | _          | _         | _         | PTC16             | DISABLED  |           | PTC16             |           |                 |            |           |          |      |

| 72         | _          | -         | _         | PTC17             | DISABLED  |           | PTC17             |           |                 |            |           |          |      |

| 73         | 57         | 41        | _         | PTD0              | DISABLED  |           | PTD0              | SPI0_PCS0 |                 | TPM0_CH0   |           |          |      |

| 74         | 58         | 42        | _         | PTD1              | ADC0_SE5b | ADC0_SE5b | PTD1              | SPI0_SCK  |                 | TPM0_CH1   |           |          |      |

| 75         | 59         | 43        | -         | PTD2              | DISABLED  |           | PTD2              | SPI0_MOSI | UART2_RX        | TPM0_CH2   | SPI0_MISO |          |      |

| 76         | 60         | 44        | -         | PTD3              | DISABLED  |           | PTD3              | SPI0_MISO | UART2_TX        | TPM0_CH3   | SPI0_MOSI |          |      |

| 77         | 61         | 45        | 29        | PTD4/<br>LLWU_P14 | DISABLED  |           | PTD4/<br>LLWU_P14 | SPI1_PCS0 | UART2_RX        | TPM0_CH4   |           |          |      |

| 78         | 62         | 46        | 30        | PTD5              | ADC0_SE6b | ADC0_SE6b | PTD5              | SPI1_SCK  | UART2_TX        | TPM0_CH5   |           |          |      |

| 79         | 63         | 47        | 31        | PTD6/<br>LLWU_P15 | ADC0_SE7b | ADC0_SE7b | PTD6/<br>LLWU_P15 | SPI1_MOSI | UARTO_RX        |            | SPI1_MISO |          |      |

| 80         | 64         | 48        | 32        | PTD7              | DISABLED  |           | PTD7              | SPI1_MISO | UARTO_TX        |            | SPI1_MOSI |          |      |

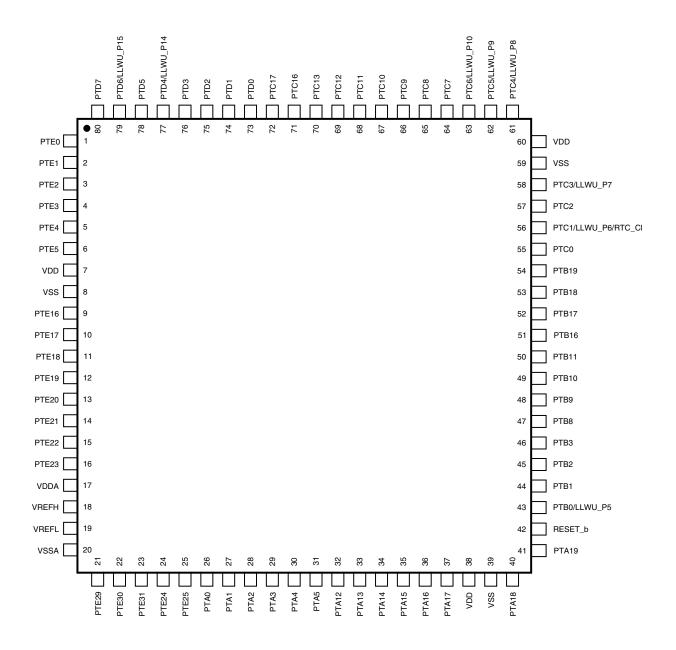

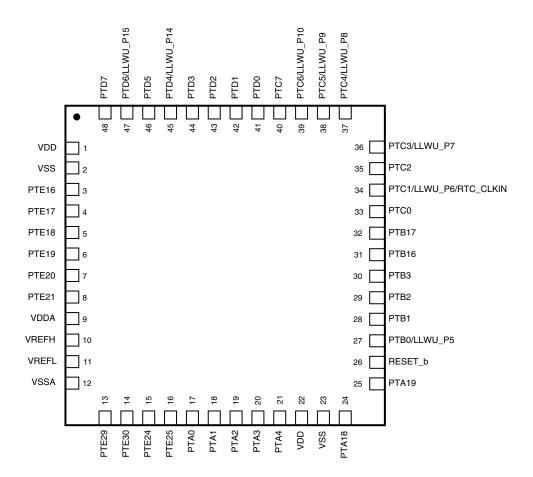

#### 8.2 KL15 Pinouts

The below figures show the pinout diagrams for the devices supported by this document. Many signals may be multiplexed onto a single pin. To determine what signals can be used on which pin, see the previous section.

Figure 17. KL15 80-pin LQFP pinout diagram

Figure 19. KL15 48-pin QFN pinout diagram