#### Zilog - EZ80F92AZ020EC Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ80                                                      |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                          |

| Number of I/O              | 24                                                        |

| Program Memory Size        | 128KB (128K x 8)                                          |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 8K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                 |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 100-LQFP                                                  |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/ez80f92az020ec |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Watchdog Timer Operation                                                                                                                                                                                                                                      |                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| Programmable Reload Timers<br>Programmable Reload Timers Overview<br>Programmable Reload Timer Operation<br>Programmable Reload Timer Registers                                                                                                               | . 76<br>. 77                                  |

| Real-Time Clock         Real-Time Clock Overview         Real-Time Clock Alarm         Real-Time Clock Oscillator and Source Selection         Real-Time Clock Battery Backup         Real-Time Clock Recommended Operation         Real-Time Clock Registers | . 88<br>. 89<br>. 89<br>. 89<br>. 89<br>. 89  |

| Universal Asynchronous Receiver/Transmitter<br>UART Functional Description<br>UART Functions<br>UART Interrupts<br>UART Recommended Usage<br>Baud Rate Generator<br>BRG Control Registers<br>UART Registers                                                   | 105<br>105<br>106<br>108<br>109<br>110        |

| Infrared Encoder/Decoder                                                                                                                                                                                                                                      | 124                                           |

| Functional Description         Transmit         Receive         Receiver Frequency Divider         Jitter         Infrared Encoder/Decoder Signal Pins         Loopback Testing                                                                               | 125<br>125<br>127<br>128<br>128               |

| Serial Peripheral Interface                                                                                                                                                                                                                                   | 131<br>133<br>134<br>134<br>135<br>135        |

| I <sup>2</sup> C Serial I/O Interface                                                                                                                                                                                                                         | <b>141</b><br>143<br>143<br>144<br>146<br>153 |

| Zilog Debug Interface                                                                                                                                                                                                                                         | 162                                           |

# Zilog<sup>®</sup> 13

| Pin No | Symbol          | Function              | Signal Direction   | Description                                                                                                                                                                                                                                                                                                                  |

|--------|-----------------|-----------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 67     | V <sub>DD</sub> | Power Supply          |                    | Power Supply.                                                                                                                                                                                                                                                                                                                |

| 68     | PD0             | GPIO Port D           | Bidirectional      | This pin can be used for general-purpose<br>I/O. It can be individually programmed as<br>input or output and can also be used<br>individually as an interrupt input. Each<br>Port D pin, when programmed as output,<br>can be selected to be an open-drain or<br>open-source output. Port D is multiplexed<br>with one UART. |

|        | TxD0            | UART<br>Transmit Data | Output             | This pin is used by the UART to transmit asynchronous serial data. This signal is multiplexed with PD0.                                                                                                                                                                                                                      |

|        | IR_TxD          | IrDA Transmit<br>Data | Output             | This pin is used by the IrDA encoder/<br>decoder to transmit serial data. This signal<br>is multiplexed with PD0.                                                                                                                                                                                                            |

| 69     | PD1             | GPIO Port D           | Bidirectional      | This pin can be used for general-purpose<br>I/O. It can be individually programmed as<br>input or output and can also be used<br>individually as an interrupt input. Each<br>Port D pin, when programmed as output,<br>can be selected to be an open-drain or<br>open-source output. Port D is multiplexed<br>with one UART. |

|        | RxD0            | Receive Data          | Input              | This pin is used by the UART to receive asynchronous serial data. This signal is multiplexed with PD1.                                                                                                                                                                                                                       |

|        | IR_RxD          | IrDA Receive<br>Data  | Input              | This pin is used by the IrDA encoder/<br>decoder to receive serial data. This signal is<br>multiplexed with PD1.                                                                                                                                                                                                             |

| 70     | PD2             | GPIO Port D           | Bidirectional      | This pin can be used for general-purpose<br>I/O. It can be individually programmed as<br>input or output and can also be used<br>individually as an interrupt input. Each<br>Port D pin, when programmed as output,<br>can be selected to be an open-drain or<br>open-source output. Port D is multiplexed<br>with one UART. |

|        | RTS0            | Request To<br>Send    | Output, Active Low | Modem control signal from UART.<br>This signal is multiplexed with PD2.                                                                                                                                                                                                                                                      |

## Table 1. 100-Pin LQFP Pin Identification of the eZ80F92 Device (Continued)

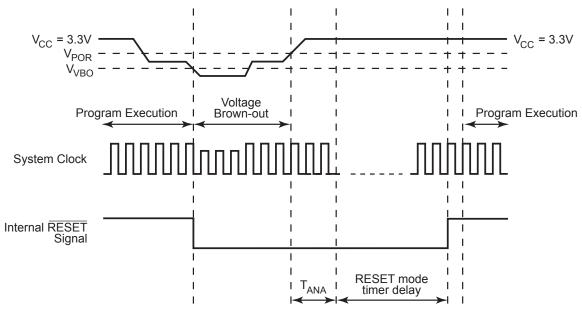

Figure 4. Voltage Brownout Reset Operation

## Zilog<sup>®</sup> 67

## **Chip Select Registers**

#### Chip Select x Lower Bound Register

For Memory Chip Selects, the Chip Select *x* Lower Bound register, listed in Table 22, defines the lower bound of the address range for which the corresponding Memory Chip Select (if enabled) can be active. For I/O Chip Selects, this register defines the address to which ADDR[15:8] is compared to generate an I/O Chip Select. All Chip Select lower bound registers reset to 00h.

#### Table 22. Chip Select x Lower Bound Register(CS0\_LBR = 00A8h, CS1\_LBR = 00ABh, CS2\_LBR = $00AEh, CS3_LBR = 00B1h)$

| Bit                     | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| CS0_LBR Reset           | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| CS1_LBR Reset           | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| CS2_LBR Reset           | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| CS3_LBR Reset           | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| CPU Access              | R/W |

| Note: R/W = Read/Write. |     |     |     |     |     |     |     |     |

Bit

| Position         | Value       | Description                                                                                                                                                                                                                                                                                                      |

|------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0]<br>CSx_LBR | 00h–<br>FFh | <b>For Memory Chip Selects (CSX_IO = 0)</b><br>This byte specifies the lower bound of the Chip Select address<br>range. The upper byte of the address bus, ADDR[23:16], is<br>compared to the values contained in these registers for<br>determining whether a Memory Chip Select signal should be<br>generated. |

|                  |             | For I/O Chip Selects (CSX_IO = 1)<br>This byte specifies the Chip Select address value. ADDR[15:8] is<br>compared to the values contained in these registers for<br>determining whether an I/O Chip Select signal should be<br>generated.                                                                        |

Zilog 70

**Chip Select x Bus Mode Control Register+**The Chip Select Bus Mode register, listed in Table 25, configures the Chip Select for eZ80<sup>®</sup>, Z80<sup>®</sup>, Intel<sup>TM</sup>, or Motorola bus modes. Changing the bus mode allows the eZ80F92 device to interface to peripherals based on the Z80-, Intel-, or Motorola-style asynchronous bus interfaces. When a bus mode other than CPU is programmed for a particular Chip Select, the CSx\_WAIT setting in that Chip Select Control Register is ignored.

Table 25. Chip Select x Bus Mode Control Register(CS0\_BMC = 00F0h, CS1\_BMC = 00F1h, CS2\_BMC = 00F2h, CS3\_BMC = 00F3h)

| Bit                                    | 7   | 6   | 5   | 4 | 3   | 2   | 1   | 0   |

|----------------------------------------|-----|-----|-----|---|-----|-----|-----|-----|

| CS0_BMC Reset                          | 0   | 0   | 0   | 0 | 0   | 0   | 1   | 0   |

| CS1_BMC Reset                          | 0   | 0   | 0   | 0 | 0   | 0   | 1   | 0   |

| CS2_BMC Reset                          | 0   | 0   | 0   | 0 | 0   | 0   | 1   | 0   |

| CS3_BMC Reset                          | 0   | 0   | 0   | 0 | 0   | 0   | 1   | 0   |

| CPU Access                             | R/W | R/W | R/W | R | R/W | R/W | R/W | R/W |

| Note: R/W = Read/Write; R = Read Only. |     |     |     |   |     |     |     |     |

| Bit<br>Position | Value | Description                                                 |

|-----------------|-------|-------------------------------------------------------------|

| Position        | Value | Description                                                 |

| [7:6]           | 00    | $eZ80^{$ ® bus mode.                                        |

| BUS_MODE        | 01    | Z80 bus mode.                                               |

|                 | 10    | Intel <sup>TM</sup> bus mode.                               |

|                 | 11    | Motorola bus mode.                                          |

| 5               | 0     | Separate address and data.                                  |

| AD_MUX          | 1     | Multiplexed address and data—appears on data bus DATA[7:0]. |

| 4               | 0     | Reserved.                                                   |

# Zilog 87

| [1:0]   | 00 | Timer counts at system clock divided by clock divider.                                                             |

|---------|----|--------------------------------------------------------------------------------------------------------------------|

| TMR0_IN | 01 | Timer event input is Real-Time Clock source<br>(32 kHz or 50/60 Hz—see Real-Time Clock on page 88 for<br>details). |

|         | 10 | The timer event input is the GPIO Port B pin 0.                                                                    |

|         | 11 | The timer event input is the GPIO Port B pin 0.                                                                    |

## **Real-Time Clock Minutes Register**

This register contains the current minutes count. See Table 39.

#### Table 39. Real-Time Clock Minutes Register; (RTC\_MIN = 00E1h)

| Bit                                                                                       | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|-------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|------|

| Reset                                                                                     | Х    | Х    | Х    | Х    | Х    | Х    | Х    | Х    |

| CPU Access                                                                                | R/W* |

| Note: X = Unchanged by RESET; R/W* = Read Only if RTC locked, Read/Write if RTC unlocked. |      |      |      |      |      |      |      |      |

#### Binary-Coded-Decimal Operation (BCD\_EN = 1)

| Bit<br>Position               | Value | Description                                  |  |  |  |

|-------------------------------|-------|----------------------------------------------|--|--|--|

| [7:4]<br>TEN_MIN              | 0–5   | The tens digit of the current minutes count. |  |  |  |

| [3:0]<br>MIN                  | 0–9   | The ones digit of the current minutes count. |  |  |  |

| Binary Operation (BCD_EN = 0) |       |                                              |  |  |  |

| Bit<br>Position | Value       | Description                |

|-----------------|-------------|----------------------------|

| [7:0]<br>MIN    | 00h–<br>3Bh | The current minutes count. |

## **Real-Time Clock Alarm Minutes Register**

This register contains the alarm minutes value. See Table 47.

#### Table 47. Real-Time Clock Alarm Minutes Register; (RTC\_AMIN = 00E9h)

| Bit                                             | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |

|-------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|--|

| Reset                                           | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   |  |

| CPU Access                                      | R/W |  |

| Note: X = Unchanged by RESET; R/W = Read/Write. |     |     |     |     |     |     |     |     |  |

#### Binary-Coded-Decimal Operation (BCD\_EN = 1)

3Bh

| •                 |           |                                            |

|-------------------|-----------|--------------------------------------------|

| Bit<br>Position   | Value     | Description                                |

| [7:4]<br>ATEN_MIN | 0–5       | The tens digit of the alarm minutes value. |

| [3:0]<br>AMIN     | 0–9       | The ones digit of the alarm minutes value. |

| Binary Operat     | tion (BCD | _EN = 0)                                   |

| Bit               | Value     | Description                                |

| Position          | Value     | Description                                |

| [7:0]             | 00h-      | The alarm minutes value.                   |

AMIN

zilog 101

#### Real-Time Clock Alarm Day-of-the-Week Register

This register contains the alarm day-of-the-week value. See Table 49.

#### Table 49. Real-Time Clock Alarm Day-of-the-Week Register; (RTC\_ADOW = 00EBh)

| Bit        | 7 | 6 | 5 | 4 | 3    | 2    | 1    | 0    |

|------------|---|---|---|---|------|------|------|------|

| Reset      | 0 | 0 | 0 | 0 | Х    | Х    | Х    | Х    |

| CPU Access | R | R | R | R | R/W* | R/W* | R/W* | R/W* |

Note: X = Unchanged by RESET; R = Read Only; R/W\* = Read Only if RTC locked, Read/Write if RTC unlocked.

#### Binary-Coded-Decimal Operation (BCD\_EN = 1)

| Bit<br>Position | Value | Description                      |

|-----------------|-------|----------------------------------|

| [7:4]           | 0000  | Reserved.                        |

| [3:0]<br>ADOW   | 1-7   | The alarm day-of-the-week.value. |

Binary Operation (BCD\_EN = 0)

| Bit<br>Position | Value       | Description                      |

|-----------------|-------------|----------------------------------|

| [7:4]           | 0000        | Reserved.                        |

| [3:0]<br>ADOW   | 01h–<br>07h | The alarm day-of-the-week value. |

# Zilog 119

#### **UART Modem Control Register**

This register is used to control and check the modem status, as listed in Table 63.

## Table 63. UART Modem Control Registers(UART0\_MCTL = 00C4h, UART1\_MCTL = 00D4h)

| Bit        | 7 | 6 | 5   | 4   | 3   | 2   | 1   | 0   |

|------------|---|---|-----|-----|-----|-----|-----|-----|

| Reset      | 0 | 0 | 0   | 0   | 0   | 0   | 0   | 0   |

| CPU Access | R | R | R/W | R/W | R/W | R/W | R/W | R/W |

Note: R = Read Only; R/W = Read/Write.

| Bit<br>Position | Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:6]           | 00b   | Reserved—must be 00b.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5               | 0     | MULTIDROP mode disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| MDM             | 1     | MULTIDROP mode enabled. See Table 62 on page 118 for parity select definitions.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4               | 0     | LOOP BACK mode is not enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| LOOP            | 1     | LOOP BACK mode is enabled.<br>The UART operates in internal LOOP BACK mode. The<br>transmit data output port is disconnected from the internal<br>transmit data output and set to 1. The receive data input port is<br>disconnected and internal receive data is connected to internal<br>transmit data. The modem status input ports are disconnected<br>and the four bits of the modem control register are connected<br>as modem status inputs. The two modem control output ports<br>(OUT1&2) are set to their inactive state. |

| 3<br>OUT2       | 0–1   | No function in normal operation.<br>In LOOP BACK mode, this bit is connected to the DCD bit in<br>the UART Status Register.                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2<br>OUT1       | 0–1   | No function in normal operation.<br>In LOOP BACK mode, this bit is connected to the RI bit in the<br>UART Status Register.                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1<br>RTS        | 0–1   | <b>Request To Send</b><br>In normal operation, the RTS output port is the inverse of this<br>bit. In LOOP BACK mode, this bit is connected to the CTS bit in<br>the UART Status Register.                                                                                                                                                                                                                                                                                                                                          |

| 0<br>DTR        | 0–1   | <b>Data Terminal Ready</b><br>In normal operation, the DTR output port is the inverse of this<br>bit. In LOOP BACK mode, this bit is connected to the DSR bit<br>in the UART Status Register.                                                                                                                                                                                                                                                                                                                                      |

Zilog 128

Setting the upper 4 bits of IR\_CTL to 00h disables the frequency divider but not the IrDA receiver. In this mode, the IrDA receiver uses edge detection on the IR RxD bit stream.

#### Jitter

Due to the inherent sampling of the received IR\_RxD signal by the BIt Rate Clock, some jitter can be expected on the first bit in any sequence of data. However, all subsequent bits in the received data stream are a fixed 16 clock periods wide.

## Infrared Encoder/Decoder Signal Pins

The IrDA endec signal pins (IR\_TxD and IR\_RxD) are multiplexed with General-Purpose I/O (GPIO) pins. These GPIO pins must be configured for alternate function operation for the endec to operate.

The remaining six UART0 pins (CTS0, DCD0, DSR0, DTR0, RTS and RI0) are not required for use with the endec. The UART0 modem status interrupt should be disabled to prevent unwanted interrupts from these pins. The GPIO pins corresponding to these six unused UART0 pins can be used for inputs, outputs, or interrupt sources. Recommended GPIO Port D control register settings are provided in Table 69. See General-Purpose Input/Output on page 39 for additional information about setting the GPIO Port modes.

| GPIO Port D Bits | Allowable GPIO<br>Port Mode                               | Allowable Port Mode Functions                                                                                      |

|------------------|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| PD0              | 7                                                         | Alternate function.                                                                                                |

| PD1              | 7                                                         | Alternate function.                                                                                                |

| PD2-PD7          | Any other than GPIO Mode 7<br>(1, 2, 3, 4, 5, 6, 8, or 9) | Output, input, open-drain, open-source, level-<br>sensitive interrupt input, or edge-triggered<br>interrupt input. |

#### Table 69. GPIO Mode Selection when using the IrDA Encoder/Decoder

## **Loopback Testing**

Both internal and external loopback testing can be accomplished with the IrDA endec on the eZ80F92 device. Setting the LOOP\_BACK bit to 1 enables internal loopback testing. During internal loopback, the IR\_TxD output signal is inverted and connected on-chip to the IR\_RxD input. External loopback testing of the off-chip IrDA transceiver can be accomplished by transmitting data from the UART while the receiver is enabled (IR\_RxEN set to 1).

Zilog 152

is transmitted, the IFLG is set and the I2C\_SR register contains C8h and the  $I^2C$  returns to the idle state. The AAK bit must be set to 1 before reentering SLAVE mode.

If no acknowledge is received after transmitting a byte, the IFLG is set and the I2C\_SR register contains C0h. The  $I^2C$  then returns to the idle state.

If a STOP condition is detected after an acknowledge bit, the I<sup>2</sup>C returns to the idle state.

#### **Slave Receive**

In SLAVE RECEIVE mode, a number of data bytes are received from a master transmitter.

The I<sup>2</sup>C enters SLAVE RECEIVE mode when it receives its own slave address and a Write bit (lsb = 0) after a START condition. The I<sup>2</sup>C transmits an acknowledge bit and sets the IFLG bit in the I2C\_CTL register and the I2C\_SR register contains the status code 60h. The I<sup>2</sup>C also enters SLAVE RECEIVE mode when it receives the general call address 00h (if the GCE bit in the I2C\_SAR register is set). The status code is then 70h.

Note:

When the  $l^2C$  contains a 10-bit slave address (signified by FOh-F7h in the  $l2C\_SAR$  register), it transmits an acknowledge after the first address byte is received but no interrupt is generated. IFLG is not set and the status does not change. The  $l^2C$  generates an interrupt only after the second address byte is received. The  $l^2C$  sets the IFLG bit and loads the status code as described above.

I<sup>2</sup>C goes from MASTER mode to SLAVE RECEIVE mode when arbitration is lost during the transmission of an address, and the slave address and Write bit (or the general call address if the CGE bit in the I2C\_SAR register is set to 1) are received. The status code in the I2C\_SR register is 68h if the slave address is received or 78h if the general call address is received. The IFLG bit must be cleared to 0 to allow data transfer to continue.

If the AAK bit in the I2C\_CTL register is set to 1 then an acknowledge bit (Low level on SDA) is transmitted and the IFLG bit is set after each byte is received. The I2C\_SR register contains the status code 80h or 90h if SLAVE RECEIVE mode is entered with the general call address. The received data byte can be read from the I2C\_DR register and the IFLG bit must be cleared to allow the transfer to continue. If a STOP condition or a repeated START condition is detected after the acknowledge bit, the IFLG bit is set and the I2C\_SR register contains status code A0h.

If the AAK bit is cleared to 0 during a transfer, the  $I^2C$  transmits a not-acknowledge bit (High level on SDA) after the next byte is received, and set the IFLG bit. The I2C\_SR register contains the status code 88h or 98h if SLAVE RECEIVE mode is entered with the general call address. The  $I^2C$  returns to the idle state when the IFLG bit is cleared to 0.

## I<sup>2</sup>C Registers

#### Addressing

The processor interface provides access to six 8-bit registers: four Read/Write registers, one Read Only register and two Write Only registers, as listed in Table 83.

| Register | Description                          |

|----------|--------------------------------------|

| I2C_SAR  | Slave address register               |

| I2C_XSAR | Extended slave address register      |

| I2C_DR   | Data byte register                   |

| I2C_CTL  | Control register                     |

| I2C_SR   | Status register (Read Only)          |

| I2C_CCR  | Clock Control register (Write Only)  |

| I2C_SRR  | Software reset register (Write Only) |

|          |                                      |

#### Table 83. I<sup>2</sup>C Register Descriptions

## **Resetting the I<sup>2</sup>C Registers**

**Hardware Reset**— When the I<sup>2</sup>C is reset by a hardware reset of the eZ80F92 device, the I2C\_SAR, I2C\_XSAR, I2C\_DR and I2C\_CTL registers are cleared to 00h; while the I2C\_SR register is set to F8h.

**Software Reset**— Perform a software reset by writing any value to the I<sup>2</sup>C Software Reset Register (I2C\_SRR). A software reset sets the I<sup>2</sup>C back to idle and the STP, STA, and IFLG bits of the I2C\_CTL register to 0.

## I<sup>2</sup>C Slave Address Register

The I2C\_SAR register provides the 7-bit address of the I<sup>2</sup>C when in SLAVE mode and allows 10-bit addressing in conjunction with the I2C\_XSAR register. I2C\_SAR[7:1] = sla[6:0] is the 7-bit address of the I<sup>2</sup>C when in 7-bit SLAVE mode. When the I<sup>2</sup>C receives this address after a START condition, it enters SLAVE mode. I2C\_SAR[7] corresponds to the first bit received from the I<sup>2</sup>C bus.

When the register receives an address starting with F7h to F0h (I2C\_SAR[7:3] = 11110b), the I<sup>2</sup>C recognizes that a 10-bit slave addressing mode is selected. The I<sup>2</sup>C sends an ACK after receiving the I2C\_SAR byte (the device does not generate an interrupt at this point). After the next byte of the address (I2C\_XSAR) is received, the I<sup>2</sup>C generates an interrupt and goes into SLAVE mode. Then I2C\_SAR[2:1] are used as the upper 2 bits for the 10-bit extended address. The full 10-bit address is supplied by {I2C\_SAR[2:1], I2C\_XSAR[7:0]}. See Table 84 on page 154.

zilog 159

## Table 89. I<sup>2</sup>C Status Codes (Continued)

| Code | Status                                                                                       |

|------|----------------------------------------------------------------------------------------------|

| 40h  | Address and Read bit transmitted, ACK received                                               |

| 48h  | Address and Read bit transmitted, ACK not received                                           |

| 50h  | Data byte received in MASTER mode, ACK transmitted                                           |

| 58h  | Data byte received in MASTER mode, NACK transmitted                                          |

| 60h  | Slave address and Write bit received, ACK transmitted                                        |

| 68h  | Arbitration lost in address as master, slave address and Write bit received, ACK transmitted |

| 70h  | General Call address received, ACK transmitted                                               |

| 78h  | Arbitration lost in address as master, General Call address received, ACK transmitted        |

| 80h  | Data byte received after slave address received, ACK transmitted                             |

| 88h  | Data byte received after slave address received, NACK transmitted                            |

| 90h  | Data byte received after General Call received, ACK transmitted                              |

| 98h  | Data byte received after General Call received, NACK transmitted                             |

| A0h  | STOP or repeated START condition received in SLAVE mode                                      |

| A8h  | Slave address and Read bit received, ACK transmitted                                         |

| B0h  | Arbitration lost in address as master, slave address and Read bit received, ACK transmitted  |

| B8h  | Data byte transmitted in SLAVE mode, ACK received                                            |

| C0h  | Data byte transmitted in SLAVE mode, ACK not received                                        |

| C8h  | Last byte transmitted in SLAVE mode, ACK received                                            |

| D0h  | Second Address byte and Write bit transmitted, ACK received                                  |

| D8h  | Second Address byte and Write bit transmitted, ACK not received                              |

| F8h  | No relevant status information, IFLG = 0                                                     |

If an illegal condition occurs on the  $I^2C$  bus, the bus error state is entered (status code 00h). To recover from this state, the STP bit in the I2C\_CTL register must be set and the IFLG bit cleared. The  $I^2C$  then returns to the idle state. No STOP condition is transmitted on the  $I^2C$  bus.

Note:

The STP and STA bits may be set to 1 at the same time to recover from the bus error. The  $I^2C$  then sends a START condition.

zilog 161

### **Bus Clock Speed**

The I<sup>2</sup>C bus is defined for bus clock speeds up to 100 kbps (400 kbps in FAST mode).

To ensure correct detection of START and STOP conditions on the bus, the  $I^2C$  must sample the  $I^2C$  bus at least ten times faster than the bus clock speed of the fastest master on the bus. The sampling frequency should therefore be at least 1 MHz (4 MHz in FAST mode) to guarantee correct operation with other bus masters.

The I<sup>2</sup>C sampling frequency is determined by the frequency of the CPU system clock and the value in the I2C\_CCR bits 2 to 0. The bus clock speed generated by the I<sup>2</sup>C in MAS-TER mode is determined by the frequency of the input clock and the values in I2C\_CCR[2:0] and I2C\_CCR[6:3].

#### I<sup>2</sup>C Software Reset Register

The I2C\_SRR register is a Write Only register. Writing any value to this register performs a software reset of the  $I^2C$  module. See Table 91.

| Bit                   | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----------------------|---|---|---|---|---|---|---|---|

| Reset                 | Х | Х | Х | Х | Х | Х | Х | Х |

| CPU Access            | W | W | W | W | W | W | W | W |

| Note: W = Write Only. |   |   |   |   |   |   |   |   |

| Bit<br>Position | Value   | Description                                                                        |

|-----------------|---------|------------------------------------------------------------------------------------|

| [7:0]<br>SRR    | 00h–FFh | Writing any value to this register performs a software reset of the $l^2C$ module. |

zilog 172

Table 95. ZDI Address Match Registers(ZDI\_ADDR0\_L = 00h, ZDI\_ADDR0\_H = 01h, ZDI\_ADDR0\_U = 02h, ZDI\_ADDR1\_L = 04h, ZDI\_ADDR1\_H = 05h, ZDI\_ADDR1\_U = 06h, ZDI\_ADDR2\_L = 08h, ZDI\_ADDR2\_H = 09h, ZDI\_ADDR2\_U = 0Ah, ZDI\_ADDR3\_L = 0Ch, ZDI\_ADDR3\_H = 0Dh, and ZDI\_ADDR3\_U = 0Eh in the ZDI Register Write Only Address Space)

| Bit                   | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----------------------|---|---|---|---|---|---|---|---|

| Reset                 | Х | Х | Х | Х | Х | Х | Х | Х |

| CPU Access            | W | W | W | W | W | W | W | W |

| Note: W = Write Only. |   |   |   |   |   |   |   |   |

| Bit<br>Position                                            | Value       | Description                                                                                                                                                                                                                   |

|------------------------------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0]<br>ZDI_ADDRx_L,<br>ZDI_ADDRx_H,<br>or<br>ZDI_ADDRx_U | 00h–<br>FFh | The four sets of ZDI address match registers are used for setting the addresses for generating BREAK points.<br>The 24-bit addresses are supplied by {ZDI_ADDRx_U, ZDI_ADDRx_H, ZDI_ADDRx_L, where <i>x</i> is 0, 1, 2, or 3. |

#### **ZDI BREAK Control Register**

The ZDI BREAK Control register is used to enable BREAK points. ZDI asserts a BREAK when the CPU instruction address, ADDR[23:0], matches the value in the ZDI Address Match 3 registers, {ZDI\_ADDR3\_U, ZDI\_ADDR3\_H, ZDI\_ADDR3\_L}. BREAKs can only occur on an instruction boundary. If the instruction address is not the beginning of an instruction (that is, for multibyte instructions), then the BREAK occurs at the end of the current instruction. The BRK\_NEXT bit is set to 1. The BRK\_NEXT bit must be reset to 0 to release the BREAK. See Table 96 on page 173.

Zilog 190

## **Random Access Memory**

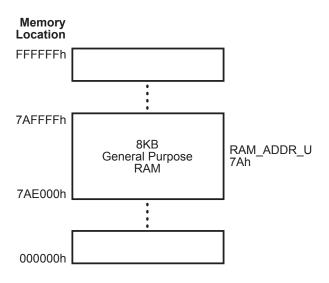

The eZ80F92 features 8KB (8192 bytes) single-port data Random Access Memory (RAM) for general-purpose use. The eZ80F93 features 4 KB (4096 bytes) general-purpose RAM. RAM can be enabled or disabled, and it can be relocated to the top of any 64 KB page in memory. Data is passed to and from RAM via the 8-bit data bus. On-chip RAM operates with zero WAIT states.

For the eZ80F92, RAM occupies memory addresses in the range {RAM\_ADDR\_U[7:0], E000h} to {RAM\_ADDR\_U[7:0], FFFFh}. Following a RESET, RAM is enabled with RAM\_ADDR\_U set to FFh. Figure 46 displays a memory map of on-chip RAM. In this example, the RAM Address Upper Byte register, RAM\_ADDR\_U, is set to 7Ah. Figure 46 is not drawn to scale, as RAM occupies only a very small fraction of the available 16 MB address space.

For the eZ80F93 device, RAM occupies memory addresses in the range {RAM\_ADDR\_U[7:0], F000h} to {RAM\_ADDR\_U[7:0], F000h}. Following a RESET, RAM is enabled with RAM\_ADDR\_U set to FFh. Figure 47 on page 191 displays a memory map of on-chip RAM. In this example, the RAM Address Upper Byte register, RAM\_ADDR\_U, is set to 7Ah. Figure 46 is not drawn to scale, as RAM occupies only a very small fraction of the available 16 MB address space.

## **RAM Control Registers**

## **RAM Control Register**

The internal data RAM can be disabled by clearing the RAM\_EN bit. The default, upon RESET, is for RAM to be enabled.

#### Table 111. RAM Control Register; (RAM\_CTL=00B4h)

| Bit                                    | 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----------------------------------------|-----|---|---|---|---|---|---|---|

| Reset                                  | 1   | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| CPU Access                             | R/W | R | R | R | R | R | R | R |

| Note: R/W = Read/Write; R = Read Only. |     |   |   |   |   |   |   |   |

| Bit<br>Position | Value   | Description                             |

|-----------------|---------|-----------------------------------------|

| -               |         | •                                       |

| 7<br>RAM_EN     | 0       | On-chip general-purpose RAM is disabled |

|                 | 1       | On-chip general-purpose RAM is enabled  |

| [6:0]           | 0000000 | Reserved                                |

## **RAM Address Upper Byte Register**

The RAM\_ADDR\_U register defines the upper byte of the address for the on-chip RAM. If enabled, RAM addresses assume priority over all Chip Selects. The external Chip Select signals are not asserted if the corresponding RAM address is enabled.

Table 112. RAM Address Upper Byte Register; (RAM\_ADDR\_U=00B5h)

|                                      |             |                                                                                                                                                                                                                        | , | J | · · – | -   |     | , |   |  |

|--------------------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|-------|-----|-----|---|---|--|

| Bit                                  |             | 7                                                                                                                                                                                                                      | 6 | 5 | 4     | 3   | 2   | 1 | 0 |  |

| Reset                                |             | 1                                                                                                                                                                                                                      | 1 | 1 | 1     | 1   | 1   | 1 | 1 |  |

| CPU Access R/W R/W R/W R/W R/W R/W R |             |                                                                                                                                                                                                                        |   |   |       | R/W | R/W |   |   |  |

| Note: R/W = Read/Write.              |             |                                                                                                                                                                                                                        |   |   |       |     |     |   |   |  |

| Bit                                  |             |                                                                                                                                                                                                                        |   |   |       |     |     |   |   |  |

| Position                             | Value       | Description                                                                                                                                                                                                            |   |   |       |     |     |   |   |  |

| [7:0]<br>RAM_ADDR_U                  | 00h–<br>FFh | This byte defines the upper byte of the RAM address. On-chip<br>RAM is prioritized over all Memory Chip Selects. If the enabled<br>RAM and Chip Select addresses overlap, the external Chip<br>Select is not asserted. |   |   |       |     |     |   |   |  |

#### 243

## Index

## **Numerics**

100-pin LQFP package 4, 20

16-bit clock divisor value 110, 135

16-bit divisor count 110, 135

20 MHz Primary Crystal Oscillator Operation 219

32 KHz Real-Time Clock Crystal Oscillator Operation 220

## Α

AAK 143, 147, 148, 149, 151, 156 AAK bit 151, 152 Absolute Maximum Ratings 222 Absolute maximum ratings 222 AC Characteristics 229 ACK 143, 147, 148, 149, 150, 151, 153, 158, 159 Acknowledge 143 Address Bus 5, 6, 7, 8, 9 address bus 46, 50, 52, 53, 54, 55, 56, 57, 60, 63, 64, 67, 68, 90, 169, 179, 185 address bus, 24-bit 25 Addressing 153 ADL Memory mode 181, 185 ALARM 89, 103 alarm condition 89, 90, 102, 103 ALARM flag 102 Arbitration 145 Architectural Overview 1 asynchronous serial data 13, 15

## В

Baud Rate Generator 109 Baud Rate Generator Functional Description 134 BCD—see binary-coded-decimal operation 88, 102, 103 Binary Operation 90, 91, 92, 93, 94, 95, 96, 97 binary operation 88 Binary-Coded-Decimal Operation 90, 91, 92, 93, 94, 95, 96, 97, 98, 99, 100, 101 binary-coded-decimal operation 88 bit generation 104 Block Diagram 2 Boundary-Scan Architecture 187 break detection 104, 113 break point trigger functions 187 **BRG** Control Registers 110 Bus Acknowledge 12 bus acknowledge pin 52, 179 Bus Arbitration Overview 141 Bus Enable bit 155 Bus Mode Controller 53 bus mode state 53, 54, 57, 61, 65, 71 Bus Modes 66 Bus modes 53 bus modes 70 Bus Request 11 Bus Requests During ZDI Debug Mode 169 BUSACK 12, 22, 52, 169, 179, 185, 238 BUSREQ 11, 22, 52, 169, 179, 185 Byte Format 143

## С

Characteristics, electrical Absolute maximum ratings 222 Chip Select 09 Chip Select 19 Chip Select 29 Chip Select 3 9 Chip Select Registers 67 Chip Select x Bus Mode Control Register 70 Chip Select x Control Register 69 Chip Select x Lower Bound Register 67 Chip Select x Upper Bound Register 68 Chip Select/Wait State Generator block 5, 6, 7, 8, 9 Chip Selects and Wait States 48 Chip Selects During Bus Request/Bus Acknowledge Cycles 52 Clear to Send 14, 16, 122 clock divisor value, 16-bit 110, 135 clock initialization circuitry 187 **Clock Peripheral Power-Down Registers 36** Clock Synchronization 144

zilog

246

Interrupt Enable Flag 184 Interrupt Enable flags 47 interrupt input 13, 14, 15, 16, 18, 19 interrupt request 41, 42, 43, 45, 46, 47, 82, 203 interrupt service routine 45, 47 interrupt service routine, SPI 45 interrupt vector 45, 46 interrupt vector address 46, 47 interrupt, highest-priority 45, 46 interrupts, edge-selectable 43 Introduction to On-Chip Instrumentation 187 Introduction, Zilog Debug Interface 162 IORQ 11, 12, 22, 51, 53, 54, 56, 57, 60 IORQ Assertion Delay 233, 234 IORQ Deassertion Delay 233, 234 **IORO Hold Time 235** IR RxD 13, 126, 127, 128 IR RxD modulation signal 13, 125, 128, 129 IR TxD 13 IR TxD modulation signal 13, 125, 128, 129 IrDA Encoder/Decoder 128 IrDA encoder/decoder 13 IrDA endec 37 IrDA specifications 124 IrDA standard 124 IrDA standard baud rates 124 IrDA transceiver 128 IrDA Transmit Data 13 IrDA—see Infrared Data Association 124 IRO 46 irq en 82, 134, 137 irg en bit 79 IVECT 45, 46, 47

## J

Jitter, Infrared Encoder/Decoder 128 JTAG interface 187 JTAG mode selection 188 JTAG Test Clock 12 JTAG Test Data In 12 JTAG Test Data Out 12 JTAG Test Mode 12 JTAG Test Trigger Output 12

## L

least-significant bit 105, 164 least-significant byte 46, 84 level-sensitive interrupt input 128 level-sensitive interrupt modes 41 level-sensitive interrupts 43 Level-Triggered Interrupts 42 Line break detection 104 Loopback Testing, Infrared Encoder/Decoder 128 low-byte vector 45 Low-Power Modes 35 LSB 160 lsb 84 lsb—see least-significant bit 83, 84, 146, 147, 149, 152 LSB—see least-significant byte 46, 47, 84

## Μ

maskable interrupt 36 maskable interrupt sources 45 maskable interrupt vectors 46 Maskable Interrupts 45 Mass Erase 197 Mass Erase operation 202, 203, 205, 206, 207 Mass Erase Violation 203 Master In, Slave Out 19, 131 MASTER mode 132, 141, 156, 158, 159, 160, 161 Master mode 152, 157 master mode 151 Master Mode Start bit 156 Master Mode Stop bit 156 MASTER mode, SPI 133 Master Out, Slave In 19, 131 Master Receive 141, 149 Master Transmit 146 MASTER TRANSMIT mode 141 master en bit 134 Memory and I/O Chip Selects 48 Memory Chip Select Example 49 Memory Chip Select Operation 48 Memory Chip Select Priority 49 Memory Request 11 memory space 48, 50