# E·XFL

### Zilog - EZ80F92AZ020SC00TR Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                      |

|----------------------------|---------------------------------------------------------------|

| Core Processor             | eZ80                                                          |

| Core Size                  | 8-Bit                                                         |

| Speed                      | 20MHz                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                       |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                              |

| Number of I/O              | 24                                                            |

| Program Memory Size        | 128KB (128K x 8)                                              |

| Program Memory Type        | FLASH                                                         |

| EEPROM Size                | -                                                             |

| RAM Size                   | 8K x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                     |

| Data Converters            | -                                                             |

| Oscillator Type            | Internal                                                      |

| Operating Temperature      | 0°C ~ 70°C (TA)                                               |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 100-LQFP                                                      |

| Supplier Device Package    | -                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/ez80f92az020sc00tr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# <mark>z</mark>ilog<sup>°</sup>

# Warning: DO NOT USE IN LIFE SUPPORT

# LIFE SUPPORT POLICY

ZILOG'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF ZILOG CORPORATION.

## As used herein

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

### **Document Disclaimer**

©2008 by Zilog, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZILOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. The information contained within this document has been verified according to the general principles of electrical and mechanical engineering.

Zilog is a registered trademark of Zilog, Inc. in the United States and in other countries. eZ80Acclaim!, eZ80, and Z80 are trademarks or registered trademarks of Zilog Inc. All other product or service names are the property of their respective owners.

ISO 9001:2000 FS 507510 Zilog products are designed and manufactured under an ISO registered 9001:2000 Quality Management System. For more details, please visit www.zilog.com/quality.

# Zilogi

# **Table of Contents**

| Architectural Overview         Features         Block Diagram         Pin Description         Pin Characteristics                                                                                                                                                                                                                                                       | . 1<br>. 2<br>. 4<br>20                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| Register Map                                                                                                                                                                                                                                                                                                                                                            |                                                                |

| eZ80 <sup>®</sup> CPU Core                                                                                                                                                                                                                                                                                                                                              |                                                                |

| Reset                                                                                                                                                                                                                                                                                                                                                                   | 32<br>32                                                       |

| Low-Power Modes<br>Overview<br>SLEEP Mode<br>HALT Mode<br>Clock Peripheral Power-Down Registers                                                                                                                                                                                                                                                                         | 35<br>35<br>36<br>36                                           |

| General-Purpose Input/Output GPIO Overview GPIO Operation GPIO Interrupts GPIO Control Registers                                                                                                                                                                                                                                                                        | 39<br>39<br>42                                                 |

| Interrupt Controller                                                                                                                                                                                                                                                                                                                                                    | 45                                                             |

| Chip Selects and Wait States<br>Memory and I/O Chip Selects<br>Memory Chip Select Operation<br>I/O Chip Select Operation<br>Wait States<br>WAIT Input Signal<br>Chip Selects During Bus Request/Bus Acknowledge Cycles<br>Bus Mode Controller<br>eZ80 Bus Mode<br>Z80 Bus Mode<br>Intel <sup>TM</sup> Bus Mode<br>Intel <sup>TM</sup> Bus Mode<br>Chip Select Registers | 48<br>48<br>50<br>51<br>52<br>53<br>53<br>53<br>53<br>63<br>67 |

| Watchdog Timer         Watchdog Timer Overview                                                                                                                                                                                                                                                                                                                          |                                                                |

# Zilog 17

| Pin No | Symbol           | Function                             | Signal Direction  | Description                                                                                                                                                                                                                                                                                                                  |

|--------|------------------|--------------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 82     | PC6              | GPIO Port C                          | Bidirectional     | This pin can be used for general-purpose<br>I/O. It can be individually programmed as<br>input or output and can also be used<br>individually as an interrupt input. Each<br>Port C pin, when programmed as output,<br>can be selected to be an open-drain or<br>open-source output. Port C is multiplexed<br>with one UART. |

|        | DCD1             | Data Carrier<br>Detect               | Input, Active Low | Modem status signal to the UART. This signal is multiplexed with PC6.                                                                                                                                                                                                                                                        |

| 83     | PC7              | GPIO Port C                          | Bidirectional     | This pin can be used for general-purpose<br>I/O. It can be individually programmed as<br>input or output and can also be used<br>individually as an interrupt input. Each<br>Port C pin, when programmed as output,<br>can be selected to be an open-drain or<br>open-source output. Port C is multiplexed<br>with one UART. |

|        | RI1              | Ring Indicator                       | Input, Active Low | Modem status signal to the UART.<br>This signal is multiplexed with PC7.                                                                                                                                                                                                                                                     |

| 84     | V <sub>SS</sub>  | Ground                               |                   | Ground.                                                                                                                                                                                                                                                                                                                      |

| 85     | X <sub>IN</sub>  | System Clock<br>Oscillator Input     | Input             | This pin is the input to the onboard crystal oscillator for the primary system clock. If an external oscillator is used, its clock output should be connected to this pin. When a crystal is used, it should be connected between $X_{IN}$ and $X_{OUT}$ .                                                                   |

| 86     | X <sub>OUT</sub> | System Clock<br>Oscillator<br>Output | Output            | This pin is the output of the onboard crystal oscillator. When used, a crystal should be connected between $X_{IN}$ and $X_{OUT}.$                                                                                                                                                                                           |

| 87     | V <sub>DD</sub>  | Power Supply                         |                   | Power Supply.                                                                                                                                                                                                                                                                                                                |

# Table 1. 100-Pin LQFP Pin Identification of the eZ80F92 Device (Continued)

| Pin No | o Symbol        | Function                         | Signal Direction | Description                                                |

|--------|-----------------|----------------------------------|------------------|------------------------------------------------------------|

| 96     | V <sub>DD</sub> | Power Supply                     |                  | Power Supply.                                              |

| 97     | V <sub>SS</sub> | Ground                           |                  | Ground.                                                    |

| 98     | SDA             | I <sup>2</sup> C Serial Data     | Bidirectional    | This pin carries the I <sup>2</sup> C data signal.         |

| 99     | SCL             | I <sup>2</sup> C Serial<br>Clock | Bidirectional    | This pin is used to receive and transmit the $I^2C$ clock. |

| 100    | PHI             | System Clock                     | Output           | This pin is an output driven by the internal system clock. |

Table 1. 100-Pin LQFP Pin Identification of the eZ80F92 Device (Continued)

# **Pin Characteristics**

Table 2 lists the characteristics of each pin in the eZ80F92 device's 100-pin LQFP package.

| Table 2. Pin Characteristics of the eZ | 280F92 Device |

|----------------------------------------|---------------|

|----------------------------------------|---------------|

| Pin<br>No | Symbol          | Direction | Reset<br>Direction | Active<br>Low/High | Tristate<br>Output | Pull<br>Up/Down | Schmitt<br>Trigger<br>Input | Open Drain/<br>Source |

|-----------|-----------------|-----------|--------------------|--------------------|--------------------|-----------------|-----------------------------|-----------------------|

| 1         | ADDR0           | I/O       | 0                  | N/A                | Yes                | No              | No                          | No                    |

| 2         | ADDR1           | I/O       | 0                  | N/A                | Yes                | No              | No                          | No                    |

| 3         | ADDR2           | I/O       | 0                  | N/A                | Yes                | No              | No                          | No                    |

| 4         | ADDR3           | I/O       | 0                  | N/A                | Yes                | No              | No                          | No                    |

| 5         | ADDR4           | I/O       | 0                  | N/A                | Yes                | No              | No                          | No                    |

| 6         | ADDR5           | I/O       | 0                  | N/A                | Yes                | No              | No                          | No                    |

| 7         | V <sub>DD</sub> |           |                    |                    |                    |                 |                             |                       |

| 8         | V <sub>SS</sub> |           |                    |                    |                    |                 |                             |                       |

| 9         | ADDR6           | I/O       | 0                  | N/A                | Yes                | No              | No                          | No                    |

| 10        | ADDR7           | I/O       | 0                  | N/A                | Yes                | No              | No                          | No                    |

| 11        | ADDR8           | I/O       | 0                  | N/A                | Yes                | No              | No                          | No                    |

| 12        | ADDR9           | I/O       | 0                  | N/A                | Yes                | No              | No                          | No                    |

| 13        | ADDR10          | I/O       | 0                  | N/A                | Yes                | No              | No                          | No                    |

| 14        | ADDR11          | I/O       | 0                  | N/A                | Yes                | No              | No                          | No                    |

| 15        | ADDR12          | I/O       | 0                  | N/A                | Yes                | No              | No                          | No                    |

# Zilog<sup>1</sup> 24

| Pin<br>No                                                           | Symbol | Direction | Reset<br>Direction | Active<br>Low/High | Tristate<br>Output | Pull<br>Up/Down | Schmitt<br>Trigger<br>Input | Open Drain/<br>Source |  |

|---------------------------------------------------------------------|--------|-----------|--------------------|--------------------|--------------------|-----------------|-----------------------------|-----------------------|--|

| 99                                                                  | SCL    | I/O       | I                  | N/A                | Yes                | Up              | No                          | OD                    |  |

| 100                                                                 | PHI    | 0         | 0                  | N/A                | Yes                | No              | No                          | No                    |  |

| Note: I = Input, O = Output, I/O = Input and Output, U = Undefined. |        |           |                    |                    |                    |                 |                             |                       |  |

# Table 2. Pin Characteristics of the eZ80F92 Device (Continued)

Zilog<sup>°</sup> 27

| Table 3. | Register | Мар | (Continued) |

|----------|----------|-----|-------------|

|----------|----------|-----|-------------|

| Address<br>(hex) | Mnemonic             | Name                                           | Reset<br>(hex) | CPU<br>Access | Page<br>No |

|------------------|----------------------|------------------------------------------------|----------------|---------------|------------|

| 00A4             | PD_ALT1              | Port D Alternate Register 1                    | 00             | R/W           | 44         |

| 00A5             | PD_ALT2              | Port D Alternate Register 2                    | 00             | R/W           | 44         |

| Chip Sele        | ct/Wait State Gene   | rator                                          |                |               |            |

| 00A8             | CS0_LBR              | Chip Select 0 Lower Bound Register             | 00             | R/W           | 67         |

| 00A9             | CS0_UBR              | Chip Select 0 Upper Bound Register             | FF             | R/W           | 68         |

| 00AA             | CS0_CTL              | Chip Select 0 Control Register                 | E8             | R/W           | 69         |

| 00AB             | CS1_LBR              | Chip Select 1 Lower Bound Register             | 00             | R/W           | 67         |

| 00AC             | CS1_UBR              | Chip Select 1 Upper Bound Register             | 00             | R/W           | 68         |

| 00AD             | CS1_CTL              | Chip Select 1 Control Register                 | 00             | R/W           | 69         |

| 00AE             | CS2_LBR              | Chip Select 2 Lower Bound Register             | 00             | R/W           | 67         |

| 00AF             | CS2_UBR              | Chip Select 2 Upper Bound Register             | 00             | R/W           | 68         |

| 00B0             | CS2_CTL              | Chip Select 2 Control Register                 | 00             | R/W           | 69         |

| 00B1             | CS3_LBR              | Chip Select 3 Lower Bound Register             | 00             | R/W           | 67         |

| 00B2             | CS3_UBR              | Chip Select 3 Upper Bound Register             | 00             | R/W           | 68         |

| 00B3             | CS3_CTL              | Chip Select 3 Control Register                 | 00             | R/W           | 69         |

| On-Chip F        | RAM Control          |                                                |                |               |            |

| 00B4             | RAM_CTL              | RAM Control Register                           | 80             | R/W           | 192        |

| 00B5             | RAM_ADDR_U           | RAM Address Upper Byte Register                | FF             | R/W           | 192        |

| Serial Per       | ipheral Interface (S | SPI) Block                                     |                |               |            |

| 00B8             | SPI_BRG_L            | SPI Baud Rate Generator Register—Low<br>Byte   | 02             | R/W           | 136        |

| 00B9             | SPI_BRG_H            | SPI Baud Rate Generator Register—<br>High Byte | 00             | R/W           | 136        |

| 00BA             | SPI_CTL              | SPI Control Register                           | 04             | R/W           | 137        |

| 00BB             | SPI_SR               | SPI Status Register                            | 00             | R             | 137        |

| 00BC             | SPI_TSR              | SPI Transmit Shift Register                    | XX             | W             | 139        |

|                  | SPI_RBR              | SPI Receive Buffer Register                    | XX             | R             | 139        |

| Infrared E       | ncoder/Decoder B     | lock                                           |                |               |            |

| 00BF             | IR_CTL               | Infrared Encoder/Decoder Control               | 00             | R/W           | 129        |

# Zilog<sup>®</sup> 62

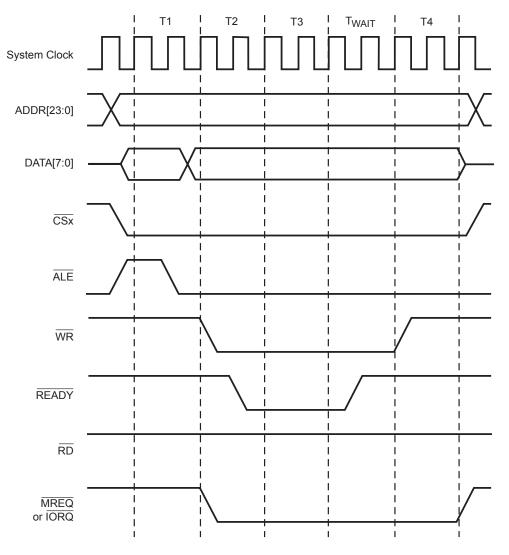

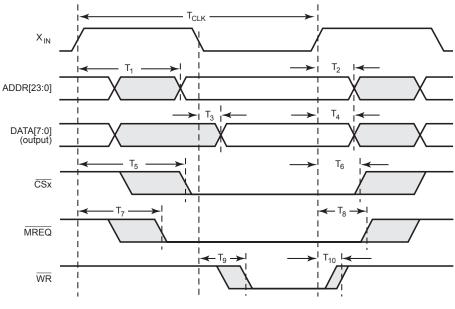

Figure 15. Example: Intel  $^{\rm TM}$  Bus Mode Write Timing—Multiplexed Address and Data Bus

Zilog<sup>®</sup> 84

Table 34. Timer Data Register—High Byte(TMR0\_DR\_H = 0082h, TMR1\_DR\_H = 0085h, TMR2\_DR\_H = 0088h, TMR3\_DR\_H = 008Bh, TMR4\_DR\_H = 008Eh, or TMR5\_DR\_H = 0091h)

| Bit                  | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----------------------|---|---|---|---|---|---|---|---|

| Reset                | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| CPU Access           | R | R | R | R | R | R | R | R |

| Note: R = Read only. |   | • | • | • |   |   | • |   |

| Bit<br>Position    | Value | Description                                                                                                                                                                                               |

|--------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0]<br>TMRx_DR_H |       | These bits represent the High byte of the 2-byte timer data value, {TMRx_DR_H[7:0], TMRx_DR_L[7:0]}. Bit 7 is bit 15 (msb) of the 16-bit timer data value. Bit 0 is bit 8 of the 16-bit timer data value. |

#### Timer Reload Register—Low Byte

The Timer Reload Register—Low Byte, listed in Table 35, stores the least-significant byte (LSB) of the 2-byte timer reload value. In CONTINUOUS mode, the timer reload value is reloaded into the timer upon end-of-count. When RST\_EN (TMRx\_CTL[1]) is set to 1 to enable the automatic reload and restart function, the timer reload value is written to the timer on the next rising edge of the clock.

Note:

The Timer Data registers and Timer Reload registers share the same address space.

Table 35. Timer Reload Register—Low Byte(TMR0\_RR\_L = 0081h, TMR1\_RR\_L = 0084h, TMR2\_RR\_L = 0087h, TMR3\_RR\_L = 008Ah, TMR4\_RR\_L = 008Dh, or TMR5\_RR\_L = 0090h)

| Bit                   | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----------------------|---|---|---|---|---|---|---|---|

| Reset                 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| CPU Access            | W | W | W | W | W | W | W | W |

| Note: W = Write only. |   |   |   |   |   |   |   |   |

| Bit<br>Desition       |   |   |   |   |   |   |   |   |

| Position           | Value   | Description                                                                                                                                                                                                   |

|--------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0]<br>TMRx_RR_L | 00h–FFh | These bits represent the Low byte of the 2-byte timer reload value, {TMRx_RR_H[7:0], TMRx_RR_L[7:0]}. Bit 7 is bit 7 of the 16-bit timer reload value. Bit 0 is bit 0 (lsb) of the 16-bit timer reload value. |

# **Real-Time Clock Hours Register**

This register contains the current hours count. See Table 40.

#### Table 40. Real-Time Clock Hours Register; (RTC\_HRS = 00E2h)

| Bit                                                                                       | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|-------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|------|

| Reset                                                                                     | Х    | Х    | Х    | Х    | Х    | Х    | Х    | Х    |

| CPU Access                                                                                | R/W* |

| Note: X = Unchanged by RESET; R/W* = Read Only if RTC locked, Read/Write if RTC unlocked. |      |      |      |      |      |      |      |      |

#### Binary-Coded-Decimal Operation (BCD\_EN = 1)

| Bit<br>Position               | Value | Description                                |  |  |

|-------------------------------|-------|--------------------------------------------|--|--|

| [7:4]<br>TEN_HRS              | 0–2   | The tens digit of the current hours count. |  |  |

| [3:0]<br>HRS                  | 0–9   | The ones digit of the current hours count. |  |  |

| Binary Operation (BCD_EN = 0) |       |                                            |  |  |

| Bit<br>Position | Value       | Description              |

|-----------------|-------------|--------------------------|

| [7:0]<br>HRS    | 00h–<br>17h | The current hours count. |

then can discard the byte or take other appropriate action. If the interrupt is caused by a receive-data-ready condition, the application alternately reads the UARTx\_LSR and UARTx\_RBR registers and removes all of the received data bytes. It reads the UARTx\_LSR register before reading the UARTx\_RBR register to determine that there is no error in the received data.

To control and check modem status, the application sets up the modem by writing to the UARTx\_MCTL register and reading the UARTx\_MSR register before starting the process mentioned above.

**Poll Mode Transfers.** When interrupts are disabled, all data transfers are referred to as poll mode transfers. In poll mode transfers, the application must continually poll the UARTx\_LSR register to transmit or receive data without enabling the interrupts. The same is true for the UARTx\_MSR register. If the interrupts are not enabled, the data in the UARTx\_IIR register cannot be used to determine the cause of an interrupt.

## **Baud Rate Generator**

The Baud Rate Generator consists of a 16-bit downcounter, two registers, and associated decoding logic. The initial value of the Baud Rate Generator is defined by the two BRG Divisor Latch registers, {UARTx\_BRG\_H, UARTx\_BRG\_L}. At the rising edge of each system clock, the BRG decrements until it reaches the value 0001h. On the next system clock rising edge, the BRG reloads the initial value from {UARTx\_BRG\_H, UARTx\_BRG\_H, UARTx\_BRG\_L} and outputs a pulse to indicate the end-of-count. Calculate the UART data rate with the following equation:

|                      |   | System Clock Frequency                     |

|----------------------|---|--------------------------------------------|

| UART Data Rate (bps) | = | 16 X (UART Baud Rate Generator<br>Divisor) |

Upon RESET, the 16-bit BRG divisor value resets to 0002h. A minimum BRG divisor value of 0001h is also valid, and effectively bypasses the BRG. A software Write to either the Low- or High-byte registers for the BRG Divisor Latch causes both the Low and High bytes to load into the BRG counter, and causes the count to restart.

The divisor registers can only be accessed if bit 7 of the UART Line Control register (UARTx\_LCTL) is set to 1. After reset, this bit is reset to 0.

**Z**ilog | 114

#### **UART Interrupt Identification Register**

The Read Only UARTx\_IIR register allows the user to check whether the FIFO is enabled and the status of interrupts. These registers share the same I/O addresses as the UARTx\_FCTL registers. See Table 57 and Table 58.

# Table 57. UART Interrupt Identification Registers(UART0\_IIR = 00C2h, UART1\_IIR = 00D2h)

| Bit                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7                 | 6                                                    | 5                                                        | 4 | 3 | 2        | 1 | 0 |  |  |  |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------------------------------------------|----------------------------------------------------------|---|---|----------|---|---|--|--|--|

| Reset                 | Reset                                                                                                                                                                                                                                                                                                                                                                                                                                            |                   | 0                                                    | 0                                                        | 0 | 0 | 0        | 0 | 1 |  |  |  |

| CPU Access            |                                                                                                                                                                                                                                                                                                                                                                                                                                                  | R                 | R                                                    | R                                                        | R | R | R        | R | R |  |  |  |

| Note: R = Read        | only.                                                                                                                                                                                                                                                                                                                                                                                                                                            |                   |                                                      |                                                          |   |   |          |   |   |  |  |  |

| Bit<br>Position Value |                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Descr             | iption                                               |                                                          |   |   |          |   |   |  |  |  |

| [7:6]                 | 00                                                                                                                                                                                                                                                                                                                                                                                                                                               | FIFO is disabled. |                                                      |                                                          |   |   |          |   |   |  |  |  |

| FSTS                  | 10                                                                                                                                                                                                                                                                                                                                                                                                                                               | Receiv            | Receive FIFO is disabled (MULTIDROP mode).           |                                                          |   |   |          |   |   |  |  |  |

|                       | 11                                                                                                                                                                                                                                                                                                                                                                                                                                               | FIFO i            | FIFO is enabled.                                     |                                                          |   |   |          |   |   |  |  |  |

| [5:4]                 | 00                                                                                                                                                                                                                                                                                                                                                                                                                                               | Reser             | ved.                                                 |                                                          |   |   |          |   |   |  |  |  |

| [3:1]<br>INSTS        | <ul> <li>000– Interrupt Status Code</li> <li>110 The code indicated in these three bits is valid only if INTBIT is</li> <li>1. If two internal interrupt sources are active and their respective enable bits are High, only the higher priority interrupt is seen by the application. The lower-priority interrupt code is indicated only after the higher-priority interrupt is serviced. Table 58 lists the interrupt status codes.</li> </ul> |                   |                                                      |                                                          |   |   | iterrupt |   |   |  |  |  |

| 0                     | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                | There             | There is an active interrupt source within the UART. |                                                          |   |   |          |   |   |  |  |  |

| INTBIT                | NTBIT 1                                                                                                                                                                                                                                                                                                                                                                                                                                          |                   |                                                      | There is not an active interrupt source within the UART. |   |   |          |   |   |  |  |  |

#### Table 58. UART Interrupt Status Codes

| INSTS<br>Value | Priority | Interrupt Type                       |

|----------------|----------|--------------------------------------|

| 011            | Highest  | Receiver Line Status                 |

| 010            | Second   | Receiver Data Ready or Trigger Level |

| 110            | Third    | Character Time-out                   |

| 101            | Fourth   | Transmission Complete                |

# zilog 121

| Bit<br>Position | Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3<br>FE         | 0     | No framing error detected for character at the top of the FIFO.<br>This bit is reset to 0 when the UARTx_LSR register is read.                                                                                                                                                                                                                                                                                                          |

|                 | 1     | Framing error detected for the character at the top of the FIFO.<br>This bit is set to 1 when the stop bit following the data/parity bit<br>is logic 0.                                                                                                                                                                                                                                                                                 |

| 2<br>PE         | 0     | The received character at the top of the FIFO does not contain<br>a parity error. In multidrop mode, this indicates that the<br>received character is a data byte. This bit is reset to 0 when the<br>UARTx_LSR register is read.                                                                                                                                                                                                       |

|                 | 1     | The received character at the top of the FIFO contains a parity<br>error. In multidrop mode, this indicates that the received<br>character is an address byte.                                                                                                                                                                                                                                                                          |

| 1<br>OE         | 0     | The received character at the top of the FIFO does not contain<br>an overrun error. This bit is reset to 0 when the UARTx_LSR<br>register is read.                                                                                                                                                                                                                                                                                      |

|                 | 1     | Overrun error is detected. If the FIFO is not enabled, this indicates that the data in the receive buffer register was not read before the next character was transferred into the receiver buffer register. If the FIFO is enabled, this indicates the FIFO was already full when an additional character was received by the receiver shift register. The character in the receiver shift register is not put into the receiver FIFO. |

| 0<br>DR         | 0     | This bit is reset to 0 when the UARTx_RBR register is read or all bytes are read from the receiver FIFO.                                                                                                                                                                                                                                                                                                                                |

|                 | 1     | <b>Data Ready</b><br>If the FIFO is not enabled, this bit is set to 1 when a complete<br>incoming character is transferred into the receiver buffer<br>register from the receiver shift register. If the FIFO is enabled,<br>this bit is set to 1 when a character is received and transferred<br>to the receiver FIFO.                                                                                                                 |

# **UART Modem Status Register**

This register is used to show the status of the UART signals. See Table 65 on page 122.

# **UART Scratch Pad Register**

The UARTx\_SPR register can be used by the system as a general-purpose Read/Write register. See Table 66.

# Table 66. UART Scratch Pad Registers(UART0\_SPR = 00C7h, UART1\_SPR = 00D7h)

| Bit                     | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Reset                   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| CPU Access              | R/W |

| Note: R/W = Read/Write. |     | •   |     | •   | •   | •   |     |     |

| Bit<br>Position | Value       | Description                                                                                  |

|-----------------|-------------|----------------------------------------------------------------------------------------------|

| [7:0]<br>SPR    | 00h–<br>FFh | The UART scratch pad register is available for use as a general-purpose Read/Write register. |

| Baud Rate | Minimum Pulse<br>Width | Maximum Pulse<br>Width |

|-----------|------------------------|------------------------|

| 57600     | 1.41 s                 | 4.34 s                 |

| 115200    | 1.41 s                 | 2.23 s                 |

#### Table 67. IrDA Physical Layer 1.4 Pulse Durations Specifications (Continued)

## **Receiver Frequency Divider**

The IrDA receiver uses a 6-bit frequency divider. The value is derived from the system clock to measure IR\_RxD pulses. The IrDA endec detects pulses that are within the IrDA Physical Layer specified minimum and maximum ranges, with system clock frequencies from 5 MHz up to 50 MHz.

The upper four bits of the frequency divider factor are set via the FREQ\_DIV bit in the IR\_CTL register, based on the following equation:

Frequency Divider Factor = System Clock Frequency (MHz) Target Frequency of 3.33 MHz

The remaining lower two bits of the divider are set to 03h. The target frequency corresponds to a period of 1.2 seconds. The FREQ\_DIV value must be rounded to the nearest integer and the resulting period of the 6-bit frequency divider must not be larger than 1.4 seconds, which is the IrDA defined minimum pulse width. If the period is greater than 1.4 seconds, FREQ\_DIV should be rounded to the next lower integer. The receiver frequency divider value versus the system clock frequency is shown in table, below.

Table 68. Frequency Divider Values

| System Clock                                              | FREQ_DIV                              |  |  |  |

|-----------------------------------------------------------|---------------------------------------|--|--|--|

| < 5.0 MHz                                                 | 00h*                                  |  |  |  |

| 5.0–7.8 MHz                                               | 01h                                   |  |  |  |

| 7.8–10.8 MHz                                              | 02h                                   |  |  |  |

| 10.8–13.6 MHz                                             | 03h                                   |  |  |  |

| 13.6–25 MHz                                               | FLOOR[4-bit Frequency Divider Factor] |  |  |  |

| 25–50 MHz                                                 | ROUND[4-bit Frequency Divider Factor] |  |  |  |

| Note: *The frequency divider is disabled when set to 00h. |                                       |  |  |  |

zilog 166

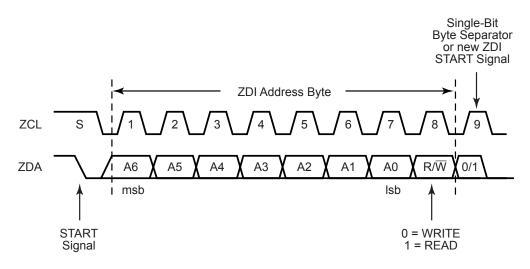

can be repeated. Repeated Read or Write operations can occur without requiring a resend of the ZDI command. To initiate a new ZDI command, a START signal must follow. Figure 41 displays the timing for address Writes to ZDI registers.

# **ZDI Write Operations**

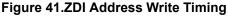

#### **ZDI Single-Byte Write**

For single-byte Write operations, the address and Write control bit are first written to the ZDI block. Following the single-bit byte separator, the data is shifted into the ZDI block on the next eight rising edges of ZCL. The master terminates activity after 8 clock cycles. Figure 42 displays the timing for ZDI single-byte Write operations.

#### Figure 42.ZDI Single-Byte Data Write Timing

**Z**ilog <sub>188</sub>

be accessed via the clock (TCK) and data (TDI) pins. See the Zilog Debug Interface section on page 162 for more information about ZDI.

# **OCI Interface**

There are five dedicated pins on the eZ80F92 device for the OCI interface. Four pins—TCK, TMS, TDI, and TDO—are required for IEEE Standard 1149.1-compliant JTAG ports. The TRIGOUT pin provides additional testability features. These five OCI pins are listed in Table 110.

| Symbol  | Name             | Туре                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------|------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ТСК     | Clock            | Input                  | Asynchronous to the primary CPU system clock. The<br>TCK period must be at least twice the system clock<br>period. During RESET, this pin is sampled to select<br>either OCI or ZDI DEBUG modes. If Low during<br>RESET, the OCI is enabled. If High during RESET,<br>the OCI is powered down and ZDI DEBUG mode is<br>enabled. When ZDI DEBUG mode is active, this pin is<br>the ZDI clock. On-chip pull-up ensures a default value<br>of 1 (High). |

| TMS     | Test Mode Select | Input                  | This serial test mode input controls JTAG mode<br>selection. On-chip pull-up ensures a default value of<br>1 (High). The TMS signal is sampled on the rising<br>edge of the TCK signal.                                                                                                                                                                                                                                                              |

| TDI     | Data In          | Input<br>(OCI enabled) | Serial test data input. On-chip pull-up ensures a default value of 1 (High). This pin is input-only when the OCI is enabled. The input data is sampled on the rising edge of the TCK signal.                                                                                                                                                                                                                                                         |

|         |                  | I/O<br>(OCI disabled)  | When the OCI is disabled, this pin functions as the ZDA (ZDI Data) I/O pin.                                                                                                                                                                                                                                                                                                                                                                          |

| TDO     | Data Out         | Output                 | The output data changes on the falling edge of the TCK signal.                                                                                                                                                                                                                                                                                                                                                                                       |

| TRIGOUT | Trigger Output   | Output                 | Generates an active High trigger pulse when valid<br>OCI trigger events occur. Output is tristate when no<br>data is driven out.                                                                                                                                                                                                                                                                                                                     |

### Table 110. OCI Pins

### Table 120. Flash Interrupt Control Register; (FLASH\_IRQ=00FBh)

| Bit                                                                    | 7   | 6   | 5 | 4 | 3 | 2 | 1 | 0 |

|------------------------------------------------------------------------|-----|-----|---|---|---|---|---|---|

| Reset                                                                  | 0   | 0   | 0 | 0 | 0 | 0 | 0 | 0 |

| CPU Access                                                             | R/W | R/W | R | R | R | R | R | R |

| Note: R/W = Read/Write, R = Read Only. Read resets bits [5] and [3:0]. |     |     |   |   |   |   |   |   |

| Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | Flash Erase/Row Program Done Interrupt is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1     | Flash Erase/Row Program Done Interrupt is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 0     | Error Condition Interrupt is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1     | Error Condition Interrupt is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 0     | Erase/Row Program Done Flag is not set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1     | Erase/Row Program Done Flag is set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0     | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 0     | The Write Violation Error Flag is not set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1     | The Write Violation Error Flag is set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 0     | The Row Program Time-out Error Flag is not set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1     | The Row Program Time-out Error Flag is set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0     | The Page Erase Violation Error Flag is not set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1     | The Page Erase Violation Error Flag is set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0     | The Mass Erase Violation Error Flag is not set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1     | The Mass Erase Violation Error Flag is set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|       | 0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>1<br>0<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 |

# Flash Page Select Register

The msb of this register is used to select whether all Flash access and Page Erases are directed to the 256-byte Information Page or to the main Flash memory array. When the main array is selected, the lower 7-bits (6 bits in the eZ80F93 device) are used to select one of the 128 pages for Page Erase or I/O Write operations.

To perform a Page Erase, the software must set the proper page value prior to setting the Page Erase bit in the Flash control register.

Zilog 213

# **Op-Code Map**

Table 135 through Table 141 on page 219 list the hex values for each of the eZ80 $^{\mbox{\ensuremath{\mathbb{R}}}}$  CPU instructions.

## Table 135. Op Code Map—First Op Code

| Lege                          |                           | Lowe             | r Op Co            | ode Nit       | oble               |             |               |                |              |                |                    |                |                    |              |               |            |

|-------------------------------|---------------------------|------------------|--------------------|---------------|--------------------|-------------|---------------|----------------|--------------|----------------|--------------------|----------------|--------------------|--------------|---------------|------------|

| Op                            | Upper<br>Code<br>Nibble ~ | 🔺 🗚              | 4<br>ND <b>⊲</b>   | Mnem          | onic               |             |               |                |              |                |                    |                |                    |              |               |            |

| Firs                          | t Opera                   |                  |                    | econd (       | Operan             | d           |               |                |              |                |                    |                |                    |              |               |            |