Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/ez80f93az020sc00tr |  |

|----------------------------|---------------------------------------------------------------|--|

| Supplier Device Package    | -                                                             |  |

| Package / Case             | 100-LQFP                                                      |  |

| Mounting Type              | Surface Mount                                                 |  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                               |  |

| Oscillator Type            | Internal                                                      |  |

| Data Converters            | -                                                             |  |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                     |  |

| RAM Size                   | 4K x 8                                                        |  |

| EEPROM Size                | -                                                             |  |

| Program Memory Type        | FLASH                                                         |  |

| Program Memory Size        | 64KB (64K x 8)                                                |  |

| Number of I/O              | 24                                                            |  |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                              |  |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                       |  |

| Speed                      | 20MHz                                                         |  |

| Core Size                  | 8-Bit                                                         |  |

| Core Processor             | eZ80                                                          |  |

| Product Status             | Obsolete                                                      |  |

| Details                    |                                                               |  |

# **Table of Contents**

| Architectural Overview                                 |          |

|--------------------------------------------------------|----------|

| Features                                               |          |

| Block DiagramPin Description                           |          |

| Pin Characteristics                                    |          |

|                                                        |          |

| Register Map                                           |          |

| eZ80 <sup>®</sup> CPU Core                             | . 31     |

| Features                                               | . 31     |

| Reset                                                  | 32       |

| Reset Operation                                        | . 32     |

| Power-On Reset                                         |          |

| Voltage Brownout Reset                                 | . 33     |

| Low-Power Modes                                        | . 35     |

| Overview                                               |          |

| SLEEP Mode                                             |          |

| HALT Mode                                              |          |

| Clock Peripheral Power-Down Registers                  |          |

| General-Purpose Input/Output                           | . 39     |

| GPIO Overview                                          |          |

| GPIO Operation                                         |          |

| GPIO Interrupts                                        |          |

| GPIO Control Registers                                 |          |

| Interrupt Controller                                   |          |

| Maskable Interrupts                                    |          |

| Nonmaskable Interrupts                                 | 47       |

| Chip Selects and Wait States                           |          |

| Memory and I/O Chip Selects                            |          |

| Memory Chip Select Operation                           |          |

| I/O Chip Select Operation                              |          |

| Wait States                                            |          |

| Chip Selects During Bus Request/Bus Acknowledge Cycles | 51<br>52 |

| Bus Mode Controller                                    |          |

| eZ80 Bus Mode                                          |          |

| Z80 Bus Mode                                           | . 53     |

| Intel <sup>TM</sup> Bus Mode                           | . 55     |

| Motorola Bus Mode                                      |          |

| Chip Select Registers                                  | 67       |

| Watchdog Timer                                         | . 72     |

| Watchdog Timer Overview                                |          |

PS015313-0508

## eZ80F92/eZ80F93 Product Specification

| Introduction                                                   |       |

|----------------------------------------------------------------|-------|

| ZDI Clock and Data Conventions                                 |       |

| ZDI Start Condition                                            |       |

| ZDI Register Addressing                                        |       |

| ZDI Write Operations                                           | . 166 |

| ZDI Read Operations                                            |       |

| Operation of the eZ80F92 Device During ZDI Breakpoints         |       |

| Bus Requests During ZDI DEBUG Mode                             |       |

| ZDI Write Only Registers                                       |       |

| ZDI Register Definitions                                       |       |

| On-Chip Instrumentation                                        |       |

| Introduction to On-Chip Instrumentation                        |       |

| OCI Activation                                                 |       |

| OCI Interface                                                  |       |

| OCI Information Requests                                       | . 189 |

| Random Access Memory                                           | . 190 |

| RAM Control Registers                                          | . 192 |

| Flash Memory                                                   | . 193 |

| Flash Memory Arrangement in eZ80F92                            | . 193 |

| Flash Memory Arrangement in the eZ80F93                        |       |

| Flash Memory Overview                                          |       |

| Programming Flash Memory                                       |       |

| Erasing Flash Memory                                           |       |

|                                                                |       |

| eZ80 <sup>®</sup> CPU Instruction Set                          |       |

| Op-Code Map                                                    | . 213 |

| On-Chip Oscillators                                            |       |

| 20 MHz Primary Crystal Oscillator Operation                    |       |

| 32 kHz Real-Time Clock Crystal Oscillator Operation            |       |

| Electrical Characteristics                                     |       |

| Absolute Maximum Ratings                                       |       |

| DC Characteristics                                             |       |

| POR and VBO Electrical Characteristics                         |       |

| Typical Current Consumption Under Various Operating Conditions |       |

| AC Characteristics                                             |       |

| External Memory Write Timing                                   |       |

| External Memory Write Timing                                   |       |

| External I/O Write Timing                                      |       |

| Wait State Timing for Read Operations                          |       |

| Wait State Timing for Write Operations                         |       |

| General Purpose I/O Port Input Sample Timing                   | . 237 |

PS015313-0508 Table of Contents

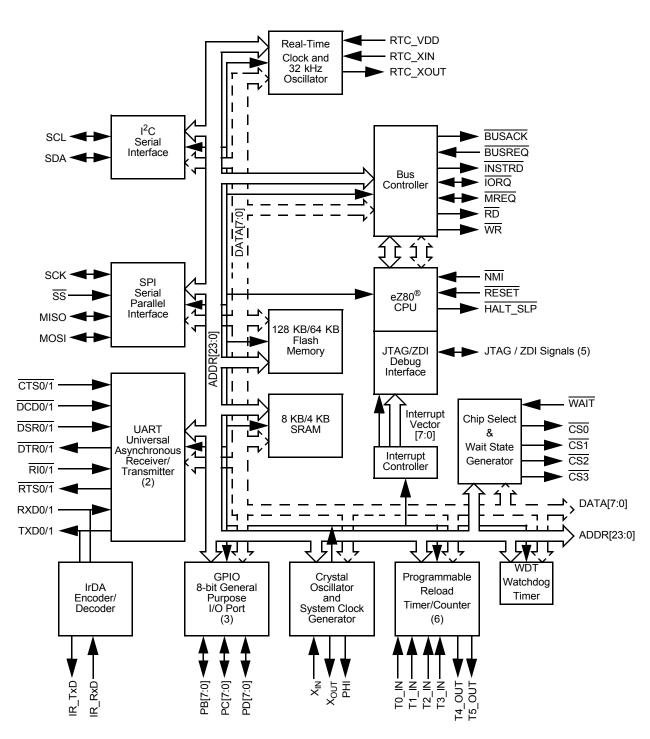

Figure 1.eZ80F92 Block Diagram

PS015313-0508 Architectural Overview

Table 5. Clock Peripheral Power-Down Register 2; (CLK\_PPD2 = 00DCh)

| Bit                                    | 7   | 6 | 5   | 4   | 3   | 2   | 1   | 0   |

|----------------------------------------|-----|---|-----|-----|-----|-----|-----|-----|

| Reset                                  | 0   | 0 | 0   | 0   | 0   | 0   | 0   | 0   |

| CPU Access                             | R/W | R | R/W | R/W | R/W | R/W | R/W | R/W |

| Note: R/W = Read/Write; R = Read Only. |     |   |     |     |     |     |     |     |

| Bit<br>Position | Value | Description                                              |

|-----------------|-------|----------------------------------------------------------|

| 7               | 1     | PHI Clock output is disabled (output is high-impedance). |

| PHI_OFF         | 0     | PHI Clock output is enabled.                             |

| 6               | 0     | Reserved.                                                |

| 5               | 1     | System clock to PRT5 is powered down.                    |

| PRT5_OFF        | 0     | System clock to PRT5 is powered up.                      |

| 4               | 1     | System clock to PRT4 is powered down.                    |

| PRT4_OFF        | 0     | System clock to PRT4 is powered up.                      |

| 3               | 1     | System clock to PRT3 is powered down.                    |

| PRT3_OFF        | 0     | System clock to PRT3 is powered up.                      |

| 2               | 1     | System clock to PRT2 is powered down.                    |

| PRT2_OFF        | 0     | System clock to PRT2 is powered up.                      |

| 1               | 1     | System clock to PRT1 is powered down.                    |

| PRT1_OFF        | 0     | System clock to PRT1 is powered up.                      |

| 0               | 1     | System clock to PRT0 is powered down.                    |

| PRT0_OFF        | 0     | System clock to PRT0 is powered up.                      |

PS015313-0508 Low-Power Modes

# **Chip Selects and Wait States**

The eZ80F92 device generates four Chip Selects for external devices. Each Chip Select may be programmed to access either memory space or I/O space. The Memory Chip Selects can be individually programmed on a 64 KB boundary. The I/O Chip Selects can each choose a 256-byte section of I/O space. In addition, each Chip Select may be programmed for up to 7 wait states.

## Memory and I/O Chip Selects

Each of the Chip Selects can be enabled for either the memory address space or the I/O address space, but not both. To select the memory address space for a particular Chip Select, CSX\_IO (CSx\_CTL[4]) must be reset to 0. To select the I/O address space for a particular Chip Select, CSX\_IO must be set to 1. After RESET, the default is for all Chip Selects to be configured for the memory address space. For either the memory address space or the I/O address space, the individual Chip Selects must be enabled by setting CSx\_EN (CSx\_CTL[3]) to 1.

# **Memory Chip Select Operation**

Operation of each of the Memory Chip Selects is controlled by three control registers. To enable a particular Memory Chip Select, the following conditions must be met:

- The Chip Select is enabled by setting CSx EN to 1

- The Chip Select is configured for Memory by clearing CSX IO to 0

- The address is in the associated Chip Select range:

CSx LBR[7:0] ≤ ADDR[23:16] ≤ CSx UBR[7:0]

- No higher priority (lower number) Chip Select meets the above conditions

- A memory access instruction must be executing

If all of the foregoing conditions are met to generate a Memory Chip Select, then the following actions occur:

- The appropriate Chip Select— $\overline{CS0}$ ,  $\overline{CS1}$ ,  $\overline{CS2}$ , or  $\overline{CS3}$ —is asserted (driven Low)

- MREQ is asserted (driven Low)

- Depending upon the instruction, either  $\overline{RD}$  or  $\overline{WR}$  is asserted (driven Low)

If the upper and lower bounds are set to the same value ( $CSx\_UBR = CSx\_LBR$ ), then a particular Chip Select is valid for a single 64 KB page.

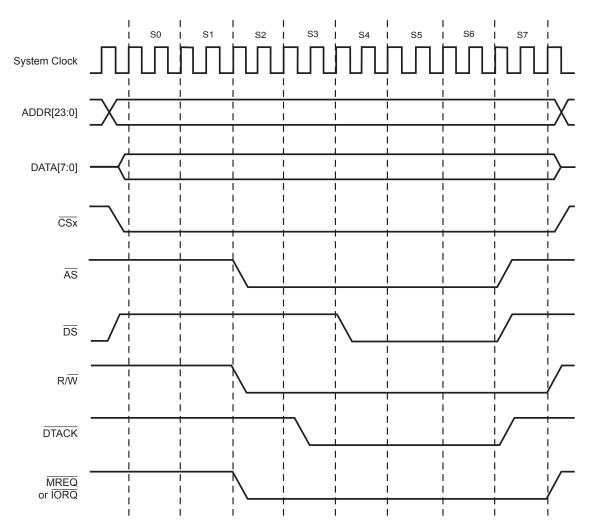

Figure 18. Example: Motorola Bus Mode Write Timing

#### **Switching Between Bus Modes**

Each time the bus mode controller must switch from one bus mode to another, there is a one-cycle CPU system clock delay. An extra clock cycle is not required for repeated access in any of the bus modes; nor is it required when the eZ80F92 device switches to eZ80® bus mode. The extra clock cycles are not shown in the timing examples. Due to the asynchronous nature of these bus protocols, the extra delay does not impact peripheral communication.

## Chip Select x Upper Bound Register

For Memory Chip Selects, the Chip Select *x* Upper Bound registers, listed in Table 23, defines the upper bound of the address range for which the corresponding Chip Select (if enabled) can be active. For I/O Chip Selects, this register produces no effect. The reset state for the Chip Select 0 Upper Bound register is FFh, while the reset state for the other Chip Select upper bound registers is 00h.

Table 23. Chip Select x Upper Bound Register(CS0\_UBR = 00A9h, CS1\_UBR = 00ACh, CS2\_UBR = 00AFh, CS3\_UBR = 00B2h)

| Bit                     | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| CS0_UBR Reset           | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

| CS1_UBR Reset           | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| CS2_UBR Reset           | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| CS3_UBR Reset           | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| CPU Access              | R/W |

| Note: R/W = Read/Write. |     |     |     |     |     |     |     |     |

| Bit<br>Position  | Value       | Description                                                                                                                                                                                                                                                                         |

|------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0]<br>CSx_UBR | 00h–<br>FFh | For Memory Chip Selects (CSx_IO = 0) This byte specifies the upper bound of the Chip Select address range. The upper byte of the address bus, ADDR[23:16], is compared to the values contained in these registers for determining whether a Chip Select signal should be generated. |

|                  |             | For I/O Chip Selects (CSx_IO = 1) No effect.                                                                                                                                                                                                                                        |

If the NMI\_OUT bit in the WDT\_CTL register is set to 1, then upon time-out, the WDT asserts an NMI for CPU processing. The NMI\_FLAG bit can be polled by the CPU to determine the source of the NMI event.

## **Watchdog Timer Registers**

### **Watchdog Timer Control Register**

The Watchdog Timer Control register, listed in Table 27, is an 8-bit Read/Write register used to enable the Watchdog Timer, set the time-out period, indicate the source of the most recent RESET, and select the required operation upon WDT time-out.

Table 27. Watchdog Timer Control Register; (WDT\_CTL = 0093h)

| Bit                                    | 7   | 6   | 5   | 4   | 3   | 2 | 1   | 0   |

|----------------------------------------|-----|-----|-----|-----|-----|---|-----|-----|

| Reset                                  | 0   | 0   | 0/1 | 0   | 0   | 0 | 0   | 0   |

| CPU Access                             | R/W | R/W | R   | R/W | R/W | R | R/W | R/W |

| Note: R = Read only; R/W = Read/Write. |     |     |     |     |     |   |     |     |

| Bit<br>Position | Value | Description                                                                                                                                                                      |  |  |  |  |  |  |

|-----------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 7 0             |       | WDT is disabled.                                                                                                                                                                 |  |  |  |  |  |  |

| WDT_EN          | 1     | WDT is enabled. When enabled, the WDT cannot be disabled without a RESET.                                                                                                        |  |  |  |  |  |  |

| 6               | 0     | WDT time-out resets the CPU.                                                                                                                                                     |  |  |  |  |  |  |

| NMI_OUT         | 1     | WDT time-out generates a nonmaskable interrupt (NMI) to the CPU.                                                                                                                 |  |  |  |  |  |  |

| 5               | 0     | RESET caused by external full-chip reset or ZDI reset.                                                                                                                           |  |  |  |  |  |  |

| RST_FLAG* 1     |       | RESET caused by WDT time-out. This flag is set by the WDT time-out, even if the NMI_OUT flag is set to 1. The CPU can poll this bit to determine the source of the RESET or NMI. |  |  |  |  |  |  |

| [4:3]           | 00    | WDT clock source is system clock.                                                                                                                                                |  |  |  |  |  |  |

| WDT_CLK         | 01    | WDT clock source is Real-Time Clock source (32 kHz on-chip oscillator or 50/60 Hz input as set by RTC_CTRL[4]).                                                                  |  |  |  |  |  |  |

|                 | 10    | Reserved.                                                                                                                                                                        |  |  |  |  |  |  |

|                 | 11    | Reserved.                                                                                                                                                                        |  |  |  |  |  |  |

| 2               | 0     | Reserved.                                                                                                                                                                        |  |  |  |  |  |  |

Note: \*RST\_FLAG is only cleared by a non-WDT RESET.

PS015313-0508 Watchdog Timer

### Timer Data Register—Low Byte

This Read Only register returns the Low byte of the current count value of the selected timer. The Timer Data Register—Low Byte, listed in Table 33, can be read while the timer is in operation. Reading the current count value does not affect timer operation. To read the 16-bit data of the current count value, {TMRx\_DR\_H[7:0], TMRx\_DR\_L[7:0]}, first read the Timer Data Register—Low Byte and then read the Timer Data Register—High Byte. The Timer Data Register—High Byte value is latched when a Read of the Timer Data Register—Low Byte occurs.

#### Note:

The Timer Data registers and Timer Reload registers share the same address space.

Table 33. Timer Data Register—Low Byte(TMR0\_DR\_L = 0081h, TMR1\_DR\_L = 0084h, TMR2\_DR\_L = 0087h, TMR3\_DR\_L = 008Ah, TMR4\_DR\_L = 008Dh, or TMR5\_DR\_L = 0090h)

| Bit                  | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----------------------|---|---|---|---|---|---|---|---|

| Reset                | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| CPU Access           | R | R | R | R | R | R | R | R |

| Note: R = Read only. |   |   |   |   |   |   |   |   |

| Bit<br>Position    | Value   | Description                                                                                                                                                                                             |

|--------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0]<br>TMRx_DR_L | 00h–FFh | These bits represent the Low byte of the 2-byte timer data value, {TMRx_DR_H[7:0], TMRx_DR_L[7:0]}. Bit 7 is bit 7 of the 16-bit timer data value. Bit 0 is bit 0 (lsb) of the 16-bit timer data value. |

#### Timer Data Register—High Byte

This Read Only register returns the High byte of the current count value of the selected timer. The Timer Data Register—High Byte, listed in Table 34 on page 84, can be read while the timer is in operation. Reading the current count value does not affect timer operation.

To read the 16-bit data of the current count value, {TMRx\_DR\_H[7:0], TMRx\_DR\_L[7:0]}, first read the Timer Data Register—Low Byte and then read the Timer Data Register—High Byte. The Timer Data Register—High Byte value is latched when a Read of the Timer Data Register—Low Byte occurs.

Note:

The timer data registers and timer reload registers share the same address space.

Table 67. IrDA Physical Layer 1.4 Pulse Durations Specifications (Continued)

| Baud Rate | Minimum Pulse<br>Width | Maximum Pulse<br>Width |

|-----------|------------------------|------------------------|

| 57600     | 1.41 s                 | 4.34 s                 |

| 115200    | 1.41 s                 | 2.23 s                 |

## **Receiver Frequency Divider**

The IrDA receiver uses a 6-bit frequency divider. The value is derived from the system clock to measure IR\_RxD pulses. The IrDA endec detects pulses that are within the IrDA Physical Layer specified minimum and maximum ranges, with system clock frequencies from 5 MHz up to 50 MHz.

The upper four bits of the frequency divider factor are set via the FREQ\_DIV bit in the IR CTL register, based on the following equation:

The remaining lower two bits of the divider are set to 03h. The target frequency corresponds to a period of 1.2 seconds. The FREQ\_DIV value must be rounded to the nearest integer and the resulting period of the 6-bit frequency divider must not be larger than 1.4 seconds, which is the IrDA defined minimum pulse width. If the period is greater than 1.4 seconds, FREQ\_DIV should be rounded to the next lower integer. The receiver frequency divider value versus the system clock frequency is shown in table, below.

**Table 68. Frequency Divider Values**

| System Clock       | FREQ_DIV                                 |

|--------------------|------------------------------------------|

| < 5.0 MHz          | 00h*                                     |

| 5.0–7.8 MHz        | 01h                                      |

| 7.8–10.8 MHz       | 02h                                      |

| 10.8–13.6 MHz      | 03h                                      |

| 13.6–25 MHz        | FLOOR[4-bit Frequency Divider Factor]    |

| 25–50 MHz          | ROUND[4-bit Frequency Divider Factor]    |

| Note: *The frequen | ncy divider is disabled when set to 00h. |

PS015313-0508 Infrared Encoder/Decoder

|      |      | COK                     | COK                    | COV                  | SS High             |

|------|------|-------------------------|------------------------|----------------------|---------------------|

| СРНА | CPOL | SCK<br>Transmit<br>Edge | SCK<br>Receive<br>Edge | SCK<br>Idle<br>State | Between Characters? |

| 0    | 0    | Falling                 | Rising                 | Low                  | Yes                 |

| 0    | 1    | Rising                  | Falling                | High                 | Yes                 |

| 1    | 0    | Rising                  | Falling                | Low                  | No                  |

| 1    | 1    | Falling                 | Rising                 | High                 | No                  |

## **SPI Functional Description**

When a master transmits to a slave device via the MOSI signal, the slave device responds by sending data to the master via the master's MISO signal. The resulting implication is a full-duplex transmission, with both data out and data in synchronized with the same clock signal. Thus the byte transmitted is replaced by the byte received and eliminates the requirement for separate transmit-empty and receive-full status bits. A single status bit, SPIF, is used to signify that the I/O operation is completed, see the SPI Status Register (SPI SR) on page 137.

The SPI is double-buffered on Read, but not on Write. If a Write is performed during data transfer, the transfer occurs uninterrupted, and the Write is unsuccessful. This condition causes the WRITE COLLISION (WCOL) status bit in the SPI\_SR register to be set. After a data byte is shifted, the SPIF flag of the SPI\_SR register is set.

In SPI MASTER mode, the SCK pin functions as an output. It idles High or Low, depending on the CPOL bit in the SPI\_CTL register, until data is written to the shift register. Data transfer is initiated by writing to the transmit shift register, SPI\_TSR. Eight clocks are then generated to shift the 8 bits of transmit data out the MOSI pin while shifting in 8 bits of data on the MISO pin. After transfer, the SCK signal idles.

In SPI SLAVE mode, the start logic receives a logic Low from the  $\overline{SS}$  pin and a clock input at the SCK pin, and the slave is synchronized to the master. Data from the master is received serially from the slave MOSI signal and loads the 8-bit shift register. After the 8-bit shift register is loaded, its data is parallel transferred to the Read buffer. During a Write cycle data is written into the shift register, then the slave waits for the SPI master to initiate a data transfer, supply a clock signal, and shift the data out on the slave's MISO signal.

If the CPHA bit in the SPI\_CTL register is 0, a transfer begins when  $\overline{SS}$  pin signal goes Low and the transfer ends when  $\overline{SS}$  goes High after eight clock cycles on SCK. When the CPHA bit is set to 1, a transfer begins the first time SCK becomes active while  $\overline{SS}$  is Low and the transfer ends when the SPIF flag gets set.

Table 79. 1<sup>2</sup>C 10-Bit Master Transmit Status Codes

| Code            | I <sup>2</sup> C State                                      | Microcontroller Response                      | Next I <sup>2</sup> C Action        |

|-----------------|-------------------------------------------------------------|-----------------------------------------------|-------------------------------------|

| 38h             | Arbitration lost                                            | Clear IFLG                                    | Return to idle                      |

|                 |                                                             | Or set STA, clear IFLG                        | Transmit START when bus free        |

| 68h             | Arbitration lost,<br>SLA+W received,                        | Clear IFLG, clear AAK = 0                     | Receive data byte,<br>transmit NACK |

| ACK transmitted | Or clear IFLG, set AAK = 1                                  | Receive data byte,<br>transmit ACK            |                                     |

| B0h             | Arbitration lost,<br>SLA+R received,                        | Write byte to DATA, clear IFLG, clear AAK = 0 | Transmit last byte, receive ACK     |

| ACK transmitted | Or write byte to DATA, clear IFLG, set AAK = 1              | Transmit data byte, receive ACK               |                                     |

| D0h             | Second Address byte + W transmitted,                        | Write byte to DATA, clear IFLG                | Transmit data byte, receive ACK     |

|                 | ACK received                                                | Or set STA, clear IFLG                        | Transmit repeated START             |

|                 |                                                             | Or set STP, clear IFLG                        | Transmit STOP                       |

|                 |                                                             | Or set STA & STP, clear IFLG                  | Transmit STOP then START            |

| D8h             | Second Address byte<br>+ W transmitted,<br>ACK not received | Same as code D0h                              | Same as code D0h                    |

If a repeated START condition is transmitted, the status code is 10h instead of 08h.

After each data byte is transmitted, the IFLG is 1 and one of the status codes listed in Table 80 is in the I2C\_SR register.

Table 80. 1<sup>2</sup>C Master Transmit Status Codes For Data Bytes

| Code | I <sup>2</sup> C State              | Microcontroller Response       | Next I <sup>2</sup> C Action    |

|------|-------------------------------------|--------------------------------|---------------------------------|

| 28h  | Data byte transmitted, ACK received | Write byte to DATA, clear IFLG | Transmit data byte, receive ACK |

|      |                                     | Or set STA, clear IFLG         | Transmit repeated START         |

|      |                                     | Or set STP, clear IFLG         | Transmit STOP                   |

|      |                                     | Or set STA & STP, clear IFLG   | Transmit START then STOP        |

PS015313-0508 I2C Serial I/O Interface

## I<sup>2</sup>C Clock Control Register

The I2C\_CCR register is a Write Only register. The seven LSBs control the frequency at which the I<sup>2</sup>C bus is sampled and the frequency of the I<sup>2</sup>C clock line (SCL) when the I<sup>2</sup>C is in MASTER mode. The Write Only I2C\_CCR registers share the same I/O addresses as the Read Only I2C\_SR registers. See Table 90.

Table 90. I<sup>2</sup>C Clock Control Registers(I2C\_CCR = 00CCh)

| Bit                  | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----------------------|---|---|---|---|---|---|---|---|

| Reset                | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| CPU Access           | W | W | W | W | W | W | W | W |

| Note: W = Read only. |   |   |   |   |   |   |   |   |

| Bit<br>Position | Value         | Description                                  |

|-----------------|---------------|----------------------------------------------|

| 7               | 0             | Reserved.                                    |

| [6:3]<br>M      | 0000–<br>1111 | I <sup>2</sup> C clock divider scalar value. |

| [2:0]<br>N      | 000–<br>111   | I <sup>2</sup> C clock divider exponent.     |

The I<sup>2</sup>C clocks are derived from the CPU system clock. The frequency of the CPU system clock is  $f_{SCK}$ . The I<sup>2</sup>C bus is sampled by the I<sup>2</sup>C block at the frequency  $f_{SAMP}$  supplied by:

$$f_{\text{SAMP}} = \frac{f_{\text{SCLK}}}{2^{N}}$$

In MASTER mode, the  $I^2C$  clock output frequency on SCL ( $f_{SCL}$ ) is supplied by:

$$f_{SCL} = \frac{f_{SCLK}}{10 \cdot (M+1)(2)^N}$$

The use of two separately-programmable dividers allows the MASTER mode output frequency to be set independently of the frequency at which the I<sup>2</sup>C bus is sampled. This feature is particularly useful in multimaster systems because the frequency at which the I<sup>2</sup>C bus is sampled must be at least 10 times the frequency of the fastest master on the bus to ensure that START and STOP conditions are always detected. By using two programmable clock divider stages, a high sampling frequency can be ensured while allowing the MASTER mode output to be set to a lower frequency.

PS015313-0508 I2C Serial I/O Interface

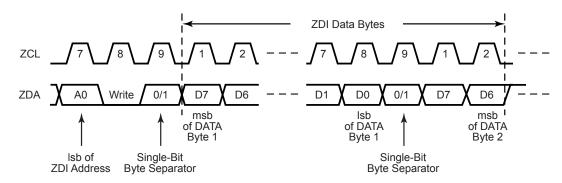

#### **ZDI Block Write**

The Block Write operation is initiated in the same manner as the single-byte Write operation, but instead of terminating the Write operation after the first data byte is transferred, the ZDI master can continue to transmit additional bytes of data to the ZDI slave on the eZ80F92 device. After the receipt of each byte of data the ZDI register address increments by 1. If the ZDI register address reaches the end of the Write Only ZDI register address space (30h), the address stops incrementing. Figure 43 displays the timing for ZDI Block Write operations.

Figure 43.ZDI Block Data Write Timing

## **ZDI Read Operations**

#### **ZDI Single-Byte Read**

Single-byte Read operations are initiated in the same manner as single-byte Write operations, with the exception that the  $R/\overline{W}$  bit of the ZDI register address is set to 1. Upon receipt of a slave address with the  $R/\overline{W}$  bit set to 1, the eZ80F92 device's ZDI block loads the selected data into the shifter at the beginning of the first cycle following the single-bit data separator. The msb is shifted out first. Figure 44 displays the timing for ZDI single-byte Read operations.

PS015313-0508 Zilog Debug Interface

Table 99. ZDI Read/Write Control Register Functions(ZDI\_RW\_CTL = 16h in the ZDI Register Write Only Address Space (Continued))

| Hex<br>Value | Command                                                            | Hex<br>Value | Command                                          |

|--------------|--------------------------------------------------------------------|--------------|--------------------------------------------------|

| 0A           | Exchange CPU register sets  AF ← AF'  BC ← BC'  DE ← DE'  HL ← HL' | 8A           | Reserved                                         |

| 0B           | Read memory from current PC value, increment PC                    | 8B           | Write memory from current PC value, increment PC |

The eZ80<sup>®</sup> CPU's alternate register set (A', F', B', C', D', E', HL') cannot be read directly. The ZDI programmer must execute the exchange instruction (EXX) to gain access to the alternate eZ80 CPU register set.

PS015313-0508 Zilog Debug Interface

Table 109. ZDI Read Memory Register(ZDI\_RD\_MEM = 20h in the ZDI Register Read Only Address Space)

| Bit                  | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----------------------|---|---|---|---|---|---|---|---|

| Reset                | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| CPU Access           | R | R | R | R | R | R | R | R |

| Note: R = Read Only. |   |   |   |   |   |   |   |   |

| Bit<br>Position     | Value       | Description                                                                                                                                                                                                                                             |

|---------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0]<br>ZDI_RD_MEM | 00h–<br>FFh | 8-bit data read from the memory address indicated by the CPU's program counter. In Z80 <sup>®</sup> MEMORY mode, 8-bit data is transferred out from address {MBASE, PC[15:0]}. In ADL Memory mode, 8-bit data is transferred out from address PC[23:0]. |

PS015313-0508 Zilog Debug Interface

**Table 145. DC Characteristics (Continued)**

|                  |                       | T <sub>A</sub> = 0 °C | to 70 °C      | T <sub>A</sub> = 0 °C | to 105 °C     |       |                                                                     |

|------------------|-----------------------|-----------------------|---------------|-----------------------|---------------|-------|---------------------------------------------------------------------|

| Symbol           | Parameter             | Min                   | Max           | Min                   | Max           | Units | Conditions                                                          |

| I <sub>RTC</sub> | RTC Supply<br>Current | 2.5                   | 10<br>Typical | 2.5                   | 10<br>Typical | μΑ    | Supply current into RTC_V <sub>DD</sub> ; SLEEP mode <sup>2</sup> . |

#### **Notes**

- 1. This condition excludes all pins with on-chip pull-ups when driven Low.

- 2. RTC current increases when the eZ80F92 device is not in SLEEP mode as the RTC\_VDD pin supplies power to system clock buffers within the Real-Time Clock circuit.

#### POR and VBO Electrical Characteristics

Table 146 lists the Power-On Reset and Voltage Brownout characteristics of the eZ80F92 device.

Table 146. POR and VBO Electrical Characteristics

|                      |                                                                         | $T_A = 0$ | ) °C to +′ |      |      |                                    |

|----------------------|-------------------------------------------------------------------------|-----------|------------|------|------|------------------------------------|

| Symbol               | Parameter                                                               | Min       | Тур        | Max  | Unit | Conditions                         |

| V <sub>VBO</sub>     | VBO Voltage Threshold                                                   | 2.40      | 2.55       | 2.85 | V    | V <sub>CC</sub> = V <sub>VBO</sub> |

| V <sub>POR</sub>     | POR Voltage Threshold                                                   | 2.45      | 2.65       | 2.90 | V    | V <sub>CC</sub> = V <sub>POR</sub> |

| V <sub>HYST</sub>    | POR/VBO Hysteresis                                                      | 50        | 100        | 150  | mV   |                                    |

| T <sub>ANA</sub>     | POR/VBO analog RESET duration                                           | 40        |            | 100  | μs   |                                    |

| T <sub>VBO_MIN</sub> | VBO pulse reject period                                                 |           | 10         |      | μs   |                                    |

| V <sub>CCRAMP</sub>  | V <sub>CC</sub> ramp rate requirements to guarantee proper RESET occurs | 0.1       |            | 100  | V/ms |                                    |

# **Typical Current Consumption Under Various Operating Conditions**

In the following pages, Figure 53 on page 225 displays the typical current consumption of the eZ80F92 device versus the number of WAIT states while operating 25 °C, 3.3 V, and with either a 5 MHz, 10 MHz, 15 MHz, or 20 MHz system clock. Figure 54 on page 226 displays the typical current consumption of the eZ80F92 device versus the system clock frequency while operating 25 °C, 3.3 V, and using 0, 2, or 7 WAIT states. Figure 55 on page 227 displays the typical current consumption of the eZ80F92 device versus temperature while operating at 3.3 V, 7 WAIT states, and with either a 5 MHz, 10 MHz, 15 MHz or 20 MHz system clock. Figure 56 on page 228 displays the typical current consumption

PS015313-0508 Electrical Characteristics

**Table 149. External Write Timing**

|                 | Abbreviation                          | Delay (ns) |      |

|-----------------|---------------------------------------|------------|------|

| Parameter       |                                       | Min        | Max  |

| T <sub>1</sub>  | Clock Rise to ADDR Valid Delay        | _          | 13   |

| T <sub>2</sub>  | Clock Rise to ADDR Hold Time          | 2.0        | _    |

| T <sub>3</sub>  | Clock Fall to Output DATA Valid Delay | _          | 11   |

| T <sub>4</sub>  | Clock Rise to DATA Hold Time          | 2.0        | _    |

| T <sub>5</sub>  | Clock Rise to CSx Assertion Delay     | 2.0        | 19.0 |

| T <sub>6</sub>  | Clock Rise to CSx Deassertion Delay   | 2.0        | 18.0 |

| T <sub>7</sub>  | Clock Rise to MREQ Assertion Delay    | 2.0        | 16.0 |

| T <sub>8</sub>  | Clock Rise to MREQ Deassertion Delay  | 2.0        | 16.0 |

| T <sub>9</sub>  | Clock Fall to WR Assertion Delay      | 1.8        | 6.5  |

| T <sub>10</sub> | Clock Rise to WR Deassertion Delay*   | 1.6        | 6.5  |

|                 | WR Deassertion to ADDR Hold Time      | 0.25       | _    |

|                 | WR Deassertion to DATA Hold Time      | 0.25       | _    |

|                 | WR Deassertion to CSx Hold Time       | 0.25       | _    |

|                 | WR Deassertion to MREQ Hold Time      | 0.25       | _    |

**Note:** \*At the conclusion of a <u>Write cycle</u>, deassertion of <u>WR</u> always occurs before any change to ADDR, DATA, <u>CSx</u>, or <u>MREQ</u>.

PS015313-0508 Electrical Characteristics

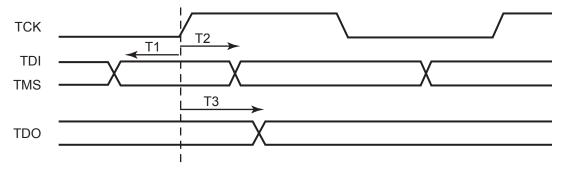

# **Zilog Debug Interface Timing**

Figure 65 and Table 155 display timing information for TCK, TDI, TDO, TMS pins.

Figure 65.ZDI Timing

**Table 155. ZDI Timing Specifications**

| Parameter        | Abbreviation                     | Delay (ns)           |     |

|------------------|----------------------------------|----------------------|-----|

|                  |                                  | Min                  | Max |

| T <sub>TCK</sub> | TCK Period                       | 2 x T <sub>XIN</sub> |     |

| T <sub>1</sub>   | TDI/TMS setup to TCK Rise        | 4                    |     |

| T <sub>2</sub>   | TDI/TMS hold after TCK Rise Fall | 4                    |     |

| T <sub>3</sub>   | TCK Rise to TDO change           |                      | 10  |

PS015313-0508 Electrical Characteristics

Clocking Overview 141 DTR0 14, 128 Complex triggers 187 DTR1 16 CONTINUOUS mode 76, 78, 79, 80, 81, 82, 84, 85 **CPHA 132** E CPHA bit 133 CPOL 132 edge-selectable interrupts 43 CPOL bit 133 edge-triggered interrupt input 128 CPU system clock cycle 54 edge-triggered interrupt mode 41, 43 CS0 9, 21, 48, 49, 50, 51 Edge-Triggered Interrupts 42 CS1 9, 21, 48, 49, 50, 51 EI, Op Code Map 213 CS2 9, 21, 48, 50, 51 **Electrical Characteristics 222** CS3 9, 21, 48, 50, 51 **ENAB 157** CTS 119, 122 Enabling and Disabling the WDT 73 CTS0 14, 128 ENAB—see Bus Enable bit 155 CTS1 16 Endec 129 **Customer Information 253** endec 125, 128 endec—see Infrared Encoder/Decoder 37, 124, 128 Erase operations 193, 194 D **Event Counter 80** DATA bus 60 External Bus Acknowledge Timing 238 Data Bus 10 external bus request 52, 165, 169 data bus 52, 53, 55, 56, 57, 64, 70, 90, 169, 179, 185 External I/O Chip Selects 25 Data Carrier Detect 14, 17, 122 External I/O Read Timing 233 Data Set Ready 14, 16, 122 External I/O Write Timing 234 Data Terminal Ready 14, 16, 119 External Memory Read Timing 230 Data Transfer Procedure with SPI configured as a External Memory Write Timing 231 Slave 135 external pull-down resistor 40 External System Clock Driver (PHI) Timing 238 Data Transfer Procedure with SPI Configured as the Master 135 eZ80 bus mode 66, 70 data transfer, SPI 138 eZ80 CPU 11, 35, 52, 56, 57, 64, 171, 187 Data Validity 142 eZ80 CPU Core 31 DC Characteristics 223 eZ80 CPU Instruction Set 208 DCD 119, 122 eZ80 Product ID Low and High Byte Registers 182 DCD0 14, 128 eZ80 Product ID Revision Register 183 DCD1 17 eZ80 system clock cycle 53, 54, 57, 60 eZ80 Webserver-i 208 **DCTS 122** eZ80F92 3, 72, 171, 183 **DDCD 122** eZ80F92 device 1, 4, 5, 10, 25, 35, 39, 45, 46, 48, **DDSR 122** 50, 66, 76, 80, 108, 110, 153, 163, 164, 165, 167, divisor count 110, 135 175, 176, 180, 181, 185, 219, 223, 224, 229, 238 DSR 119, 122 DSR0 14, 128 eZ80F92 processor 2 DSR1 16

DTACK 64 DTR 119, 122