#### Zilog - EZ80F93AZ020SG Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| D | e | t | a | i | l | S |

|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ80                                                      |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                          |

| Number of I/O              | 24                                                        |

| Program Memory Size        | 64KB (64K x 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 4K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                 |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 100-LQFP                                                  |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/ez80f93az020sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Zilog<sup>®</sup> 13

| Pin No | Symbol          | Function              | Signal Direction   | Description                                                                                                                                                                                                                                                                                                                  |

|--------|-----------------|-----------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 67     | V <sub>DD</sub> | Power Supply          |                    | Power Supply.                                                                                                                                                                                                                                                                                                                |

| 68     | PD0             | GPIO Port D           | Bidirectional      | This pin can be used for general-purpose<br>I/O. It can be individually programmed as<br>input or output and can also be used<br>individually as an interrupt input. Each<br>Port D pin, when programmed as output,<br>can be selected to be an open-drain or<br>open-source output. Port D is multiplexed<br>with one UART. |

|        | TxD0            | UART<br>Transmit Data | Output             | This pin is used by the UART to transmit asynchronous serial data. This signal is multiplexed with PD0.                                                                                                                                                                                                                      |

|        | IR_TxD          | IrDA Transmit<br>Data | Output             | This pin is used by the IrDA encoder/<br>decoder to transmit serial data. This signal<br>is multiplexed with PD0.                                                                                                                                                                                                            |

| 69     | PD1             | GPIO Port D           | Bidirectional      | This pin can be used for general-purpose<br>I/O. It can be individually programmed as<br>input or output and can also be used<br>individually as an interrupt input. Each<br>Port D pin, when programmed as output,<br>can be selected to be an open-drain or<br>open-source output. Port D is multiplexed<br>with one UART. |

|        | RxD0            | Receive Data          | Input              | This pin is used by the UART to receive asynchronous serial data. This signal is multiplexed with PD1.                                                                                                                                                                                                                       |

|        | IR_RxD          | IrDA Receive<br>Data  | Input              | This pin is used by the IrDA encoder/<br>decoder to receive serial data. This signal is<br>multiplexed with PD1.                                                                                                                                                                                                             |

| 70     | PD2             | GPIO Port D           | Bidirectional      | This pin can be used for general-purpose<br>I/O. It can be individually programmed as<br>input or output and can also be used<br>individually as an interrupt input. Each<br>Port D pin, when programmed as output,<br>can be selected to be an open-drain or<br>open-source output. Port D is multiplexed<br>with one UART. |

|        | RTS0            | Request To<br>Send    | Output, Active Low | Modem control signal from UART.<br>This signal is multiplexed with PD2.                                                                                                                                                                                                                                                      |

#### Table 1. 100-Pin LQFP Pin Identification of the eZ80F92 Device (Continued)

# Zilog 18

| Pin No | Symbol | Function            | Signal Direction  | Description                                                                                                                                                                                                                                                                          |

|--------|--------|---------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 88     | PB0    | GPIO Port B         | Bidirectional     | This pin can be used for general-purpose<br>I/O. It can be individually programmed as<br>input or output and can also be used<br>individually as an interrupt input. Each<br>Port B pin, when programmed as output,<br>can be selected to be an open-drain or<br>open-source output. |

|        | T0_IN  | Timer 0 In          | Input             | Alternate clock source for Programmable<br>Reload Timers 0 and 2. This signal is<br>multiplexed with PB0.                                                                                                                                                                            |

| 89     | PB1    | GPIO Port B         | Bidirectional     | This pin can be used for general-purpose<br>I/O. It can be individually programmed as<br>input or output and can also be used<br>individually as an interrupt input. Each<br>Port B pin, when programmed as output,<br>can be selected to be an open-drain or<br>open-source output. |

|        | T1_IN  | Timer 1 In          | Input             | Alternate clock source for Programmable<br>Reload Timers 1 and 3. This signal is<br>multiplexed with PB1.                                                                                                                                                                            |

| 90     | PB2    | GPIO Port B         | Bidirectional     | This pin can be used for general-purpose<br>I/O. It can be individually programmed as<br>input or output and can also be used<br>individually as an interrupt input. Each<br>Port B pin, when programmed as output,<br>can be selected to be an open-drain or<br>open-source output. |

|        | SS     | Slave Select        | Input, Active Low | The slave select input line is used to select<br>a slave device in SPI mode. This signal is<br>multiplexed with PB2.                                                                                                                                                                 |

| 91     | PB3    | GPIO Port B         | Bidirectional     | This pin can be used for general-purpose<br>I/O. It can be individually programmed as<br>input or output and can also be used<br>individually as an interrupt input. Each<br>Port B pin, when programmed as output,<br>can be selected to be an open-drain or<br>open-source output. |

|        | SCK    | SPI Serial<br>Clock | Bidirectional     | SPI serial clock. This signal is multiplexed with PB3.                                                                                                                                                                                                                               |

#### Table 1. 100-Pin LQFP Pin Identification of the eZ80F92 Device (Continued)

# Zilog<sup>1</sup>23

| Pin<br>No | Symbol           | Direction | Reset<br>Direction | Active<br>Low/High | Tristate<br>Output | Pull<br>Up/Down | Schmitt<br>Trigger<br>Input | Open Drain/<br>Source |

|-----------|------------------|-----------|--------------------|--------------------|--------------------|-----------------|-----------------------------|-----------------------|

| 71        | PD3              | I/O       | I                  | N/A                | Yes                | No              | No                          | OD & OS               |

| 72        | PD4              | I/O       | I                  | N/A                | Yes                | No              | No                          | OD & OS               |

| 73        | PD5              | I/O       | I                  | N/A                | Yes                | No              | No                          | OD & OS               |

| 74        | PD6              | I/O       | I                  | N/A                | Yes                | No              | No                          | OD & OS               |

| 75        | PD7              | I/O       | I                  | N/A                | Yes                | No              | No                          | OD & OS               |

| 76        | PC0              | I/O       | I                  | N/A                | Yes                | No              | No                          | OD & OS               |

| 77        | PC1              | I/O       | I                  | N/A                | Yes                | No              | No                          | OD & OS               |

| 78        | PC2              | I/O       | I                  | N/A                | Yes                | No              | No                          | OD & OS               |

| 79        | PC3              | I/O       | I                  | N/A                | Yes                | No              | No                          | OD & OS               |

| 80        | PC4              | I/O       | I                  | N/A                | Yes                | No              | No                          | OD & OS               |

| 81        | PC5              | I/O       | I                  | N/A                | Yes                | No              | No                          | OD & OS               |

| 82        | PC6              | I/O       | I                  | N/A                | Yes                | No              | No                          | OD & OS               |

| 83        | PC7              | I/O       | I                  | N/A                | Yes                | No              | No                          | OD & OS               |

| 84        | V <sub>SS</sub>  |           |                    |                    |                    |                 |                             |                       |

| 85        | X <sub>IN</sub>  | I         | I                  | N/A                | N/A                | No              | No                          | N/A                   |

| 86        | Х <sub>ОUT</sub> | 0         | 0                  | N/A                | No                 | No              | No                          | No                    |

| 87        | V <sub>DD</sub>  |           |                    |                    |                    |                 |                             |                       |

| 88        | PB0              | I/O       | I                  | N/A                | Yes                | No              | No                          | OD & OS               |

| 89        | PB1              | I/O       | I                  | N/A                | Yes                | No              | No                          | OD & OS               |

| 90        | PB2              | I/O       | I                  | N/A                | Yes                | No              | No                          | OD & OS               |

| 91        | PB3              | I/O       | I                  | N/A                | Yes                | No              | No                          | OD & OS               |

| 92        | PB4              | I/O       | I                  | N/A                | Yes                | No              | No                          | OD & OS               |

| 93        | PB5              | I/O       | I                  | N/A                | Yes                | No              | No                          | OD & OS               |

| 94        | PB6              | I/O       | I                  | N/A                | Yes                | No              | No                          | OD & OS               |

| 95        | PB7              | I/O       | I                  | N/A                | Yes                | No              | No                          | OD & OS               |

| 96        | V <sub>DD</sub>  |           |                    |                    |                    |                 |                             |                       |

| 97        | V <sub>SS</sub>  |           |                    |                    |                    |                 |                             |                       |

| 98        | SDA              | I/O       | I                  | N/A                | Yes                | Up              | No                          | OD                    |

#### Table 2. Pin Characteristics of the eZ80F92 Device (Continued)

Zilog 43

an interrupt request signal to the CPU. Any time a port pin is configured for edge-triggered interrupt, writing a 1 to that pin's Port *x* Data register causes a reset of the edgedetected interrupt. The programmer must set the bit in the Port *x* Data register to 1 before entering either single or dual edge-triggered interrupt mode for that port pin.

When configured for dual edge-triggered interrupt mode (GPIO Mode 6), both a rising and a falling edge on the pin cause an interrupt request to be sent to the CPU.

When configured for single edge-triggered interrupt mode (GPIO Mode 9), the value in the Port x Data register determines if a positive or negative edge causes an interrupt request. A 0 in the Port x Data register bit sets the selected pin to generate an interrupt request for falling edges. A 1 in the Port x Data register bit sets the selected pin to generate an interrupt an interrupt request for rising edges.

#### **GPIO Control Registers**

The 12 GPIO Control Registers operate in groups of four with a set for each Port (B, C, and D). Each GPIO port features a Port Data register, Port Data Direction register, Port Alternate register 1, and Port Alternate register 2.

#### Port x Data Registers

When the port pins are configured for one of the output modes, the data written to the Port x Data registers, listed in Table 7, are driven on the corresponding pins. In all modes, reading from the Port x Data registers always returns the current sampled value of the corresponding pins.

When the port pins are configured as edge-triggered interrupt sources, writing a 1 to the corresponding bit in the Port x Data register clears the interrupt signal that is sent to the CPU. When the port pins are configured for edge-selectable interrupts or level-sensitive interrupts, the value written to the Port x Data register bit selects the interrupt edge or interrupt level. See Table 6 on page 39 for more information.

| Bit                      | 7       | 6      | 5   | 4   | 3   | 2   | 1   | 0   |

|--------------------------|---------|--------|-----|-----|-----|-----|-----|-----|

| Reset                    | Х       | Х      | Х   | Х   | Х   | Х   | Х   | Х   |

| CPU Access               | R/W     | R/W    | R/W | R/W | R/W | R/W | R/W | R/W |

| Note: X = Undefined; R/W | = Read/ | Write. |     |     |     |     |     |     |

#### Table 7. Port x Data Registers; (PB\_DR = 009Ah, PC\_DR = 009Eh, PD\_DR = 00A2h)

Zilog 61

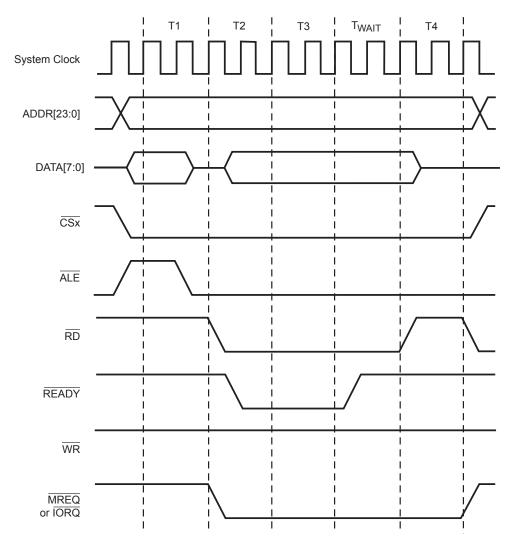

Signal timing for Intel<sup>TM</sup> bus mode with multiplexed address and data is displayed for a Read operation in Figure 14 and for a Write operation in Figure 15 on page 62. In the figures, each Intel bus mode state is 2 CPU system clock cycles in duration. Figure 14 and Figure 15 on page 62 also display the assertion of one wait state ( $T_{WAIT}$ ) by the selected peripheral.

Figure 14. Example: Intel<sup>TM</sup> Bus Mode Read Timing—Multiplexed Address and Data Bus

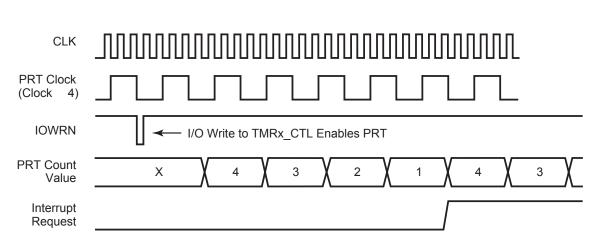

#### Table 30. PRT CONTINUOUS Mode Operation Example

| Parameter                  | Control Register(s)    | Value |

|----------------------------|------------------------|-------|

| PRT Enabled                | TMRx_CTL[0]            | 1     |

| Reload and Restart Enabled | TMRx_CTL[1]            | 1     |

| PRT Clock Divider = 4      | TMRx_CTL[3:2]          | 00b   |

| CONTINUOUS Mode            | TMRx_CTL[4]            | 1     |

| PRT Interrupt Enabled      | TMRx_CTL[6]            | 1     |

| PRT Reload Value           | {TMRx_RR_H, TMRx_RR_L} | 0004h |

|                            |                        |       |

#### **Reading the Current Count Value**

The CPU is capable of reading the current count value while the timer is running. This Read event does not affect timer operation. The High byte of the current count value is latched during a Read of the Low byte.

#### **Timer Interrupts**

The timer interrupt flag, PRT\_IRQ, is set to 1 whenever the timer reaches its end-of-count value, 0000h, in SINGLE PASS mode, or when the timer reloads the start value in CONTINUOUS mode. The interrupt flag is only set when the timer reaches 0000h (or reloads) from 0001h. The timer interrupt flag is not set to 1 when the timer is loaded with the value 0000h, which selects the maximum time-out period.

The CPU can be programmed to poll the PRT\_IRQ bit for the time-out event. Alternatively, an interrupt service request signal can be sent to the CPU by setting IRQ\_EN to 1.

Zilog 79

eZ80F92/eZ80F93 Product Specification

## zilog 104

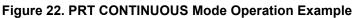

### Universal Asynchronous Receiver/Transmitter

The UART module implements all of the logic required to support several asynchronous communications protocols. The module also implements two separate 16-byte-deep FIFOs for both transmission and reception. A block diagram of the UART is displayed in Figure 25.

Figure 25.UART Block Diagram

The UART module provides the following asynchronous communication protocol-related features and functions:

- 5-, 6-, 7-, 8- or 9-bit data transmission

- Even/odd, space/mark, or no parity bit generation and detection

- Start and stop bit generation and detection

- Supports up to two stop bits

- Line break detection and generation

- Receiver overrun and framing errors detection

- Logic and associated I/O to provide modem handshake capability

**Z**ilog | 114

#### **UART Interrupt Identification Register**

The Read Only UARTx\_IIR register allows the user to check whether the FIFO is enabled and the status of interrupts. These registers share the same I/O addresses as the UARTx\_FCTL registers. See Table 57 and Table 58.

### Table 57. UART Interrupt Identification Registers(UART0\_IIR = 00C2h, UART1\_IIR = 00D2h)

| Bit                                                     |             | 7                                                  | 6                                                                                                                                                                                                                                                                                                                                                                                                                   | 5          | 4        | 3      | 2         | 1      | 0 |

|---------------------------------------------------------|-------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------|--------|-----------|--------|---|

| Reset                                                   | 0           | 0                                                  | 0                                                                                                                                                                                                                                                                                                                                                                                                                   | 0          | 0        | 0      | 0         | 1      |   |

| CPU Access                                              |             | R                                                  | R                                                                                                                                                                                                                                                                                                                                                                                                                   | R          | R        | R      | R         | R      | R |

| Note: R = Read                                          | only.       |                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                     |            |          |        |           |        |   |

| Bit<br>Position                                         | Descr       | iption                                             |                                                                                                                                                                                                                                                                                                                                                                                                                     |            |          |        |           |        |   |

| [7:6]                                                   | 00          | FIFO i                                             | FIFO is disabled.                                                                                                                                                                                                                                                                                                                                                                                                   |            |          |        |           |        |   |

| FSTS                                                    | 10          | Receive FIFO is disabled (MULTIDROP mode).         |                                                                                                                                                                                                                                                                                                                                                                                                                     |            |          |        |           |        |   |

|                                                         | 11          | FIFO i                                             | s enable                                                                                                                                                                                                                                                                                                                                                                                                            | ed.        |          |        |           |        |   |

| [5:4]                                                   | 00          | Reser                                              | ved.                                                                                                                                                                                                                                                                                                                                                                                                                |            |          |        |           |        |   |

| [3:1]<br>INSTS                                          | 000–<br>110 | The co<br>1. If tw<br>respec<br>interru<br>code is | Interrupt Status Code<br>The code indicated in these three bits is valid only if INTBIT is<br>1. If two internal interrupt sources are active and their<br>respective enable bits are High, only the higher priority<br>interrupt is seen by the application. The lower-priority interrupt<br>code is indicated only after the higher-priority interrupt is<br>serviced. Table 58 lists the interrupt status codes. |            |          |        |           |        |   |

| 0 0 There is an active interrupt source within the UART |             |                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                     | ART.       |          |        |           |        |   |

| INTBIT                                                  | 1           | There                                              | is not ar                                                                                                                                                                                                                                                                                                                                                                                                           | n active i | nterrupt | source | within th | e UART |   |

#### Table 58. UART Interrupt Status Codes

| INSTS<br>Value | Priority | Interrupt Type                       |

|----------------|----------|--------------------------------------|

| 011            | Highest  | Receiver Line Status                 |

| 010            | Second   | Receiver Data Ready or Trigger Level |

| 110            | Third    | Character Time-out                   |

| 101            | Fourth   | Transmission Complete                |

## zilog 122

### Table 65. UART Modem Status Registers(UART0\_MSR = 00C6h, UART1\_MSR = 00D6h)

| Bit                  | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----------------------|---|---|---|---|---|---|---|---|

| Reset                | Х | Х | Х | Х | Х | Х | Х | Х |

| CPU Access           | R | R | R | R | R | R | R | R |

| Note: R = Read only. |   | • |   | • | • | • | • |   |

| Bit       |       |                                                                                                                                                                                              |

|-----------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Position  | Value | Description                                                                                                                                                                                  |

| 7<br>DCD  | 0–1   | <b>Data Carrier Detect</b><br>In NORMAL mode, this bit reflects the inverted state of the<br>DCDx input pin. In LOOP BACK mode, this bit reflects the<br>value of the UARTx_MCTL[3] = out2.  |

| 6<br>RI   | 0–1   | <b>Ring Indicator</b><br>In NORMAL mode, this bit reflects the inverted state of the $\overline{RIx}$ input pin. In LOOP BACK mode, this bit reflects the value of the UARTx_MCTL[2] = out1. |

| 5<br>DSR  | 0–1   | <b>Data Set Ready</b><br>In NORMAL mode, this bit reflects the inverted state of the<br>DSRx input pin. In LOOP BACK mode, this bit reflects the<br>value of the UARTx_MCTL[0] = DTR.        |

| 4<br>CTS  | 0–1   | <b>Clear To Send</b><br>In NORMAL mode, this bit reflects the inverted state of the<br>CTSx input pin. In LOOP BACK mode, this bit reflects the value<br>of the UARTx_MCTL[1] = RTS.         |

| 3<br>DDCD | 0–1   | Delta Status Change of DCD<br>This bit is set to 1 whenever the DCDx pin changes state. This<br>bit is reset to 0 when the UARTx_MSR register is read.                                       |

| 2<br>TERI | 0–1   | <b>Trailing Edge Change on RI</b><br>This bit is set to 1 whenever a falling edge is detected on the<br>RIx pin. This bit is reset to 0 when the UARTx_MSR register is<br>read.              |

| 1<br>DDSR | 0–1   | Delta Status Change of DSR<br>This bit is set to 1 whenever the DSRx pin changes state. This<br>bit is reset to 0 when the UARTx_MSR register is read.                                       |

| 0<br>DCTS | 0–1   | Delta Status Change of CTS<br>This bit is set to 1 whenever the CTSx pin changes state.<br>This bit is reset to 0 when the UARTx_MSR register is read.                                       |

zilog 124

### **Infrared Encoder/Decoder**

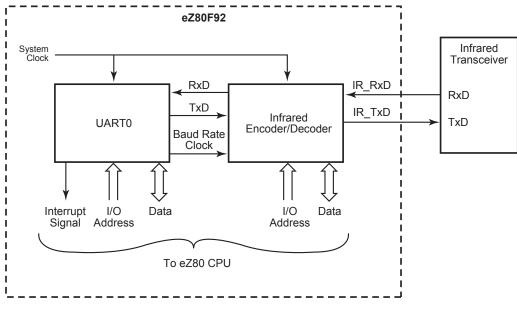

The eZ80F92 device contains a UART to infrared encoder/decoder (endec). The IrDA endec is integrated with the on-chip UART0 to allow easy communication between the CPU and IrDA Physical Layer Specification Version 1.4-compatible infrared transceivers, as displayed in Figure 26. Infrared communication provides secure, reliable, high-speed, low-cost, point-to-point communication between PCs, PDAs, mobile telephones, printers, and other infrared-enabled devices.

Figure 26. Infrared System Block Diagram

#### **Functional Description**

When the IrDA endec is enabled, the transmit data from the on-chip UART is encoded as digital signals in accordance with the IrDA standard and output to the infrared transceiver. Likewise, data received from the infrared transceiver is decoded by the endec and passed to the UART. Communication is half-duplex, meaning that simultaneous data transmission and reception is not allowed.

The baud rate is set by the UART Baud Rate Generator, and supports IrDA standard baud rates from 9600 bps to 115.2 kbps. Higher baud rates than 115.2 kbps are possible, but do not meet IrDA specifications for these data rates. The UART must be enabled to use the

Zilog 127

| Baud Rate | Minimum Pulse<br>Width | Maximum Pulse<br>Width |

|-----------|------------------------|------------------------|

| 57600     | 1.41 s                 | 4.34 s                 |

| 115200    | 1.41 s                 | 2.23 s                 |

#### Table 67. IrDA Physical Layer 1.4 Pulse Durations Specifications (Continued)

#### **Receiver Frequency Divider**

The IrDA receiver uses a 6-bit frequency divider. The value is derived from the system clock to measure IR\_RxD pulses. The IrDA endec detects pulses that are within the IrDA Physical Layer specified minimum and maximum ranges, with system clock frequencies from 5 MHz up to 50 MHz.

The upper four bits of the frequency divider factor are set via the FREQ\_DIV bit in the IR\_CTL register, based on the following equation:

Frequency Divider Factor = System Clock Frequency (MHz) Target Frequency of 3.33 MHz

The remaining lower two bits of the divider are set to 03h. The target frequency corresponds to a period of 1.2 seconds. The FREQ\_DIV value must be rounded to the nearest integer and the resulting period of the 6-bit frequency divider must not be larger than 1.4 seconds, which is the IrDA defined minimum pulse width. If the period is greater than 1.4 seconds, FREQ\_DIV should be rounded to the next lower integer. The receiver frequency divider value versus the system clock frequency is shown in table, below.

Table 68. Frequency Divider Values

| System Clock                                              | FREQ_DIV                              |  |  |  |  |  |

|-----------------------------------------------------------|---------------------------------------|--|--|--|--|--|

| < 5.0 MHz                                                 | 00h*                                  |  |  |  |  |  |

| 5.0–7.8 MHz                                               | 01h                                   |  |  |  |  |  |

| 7.8–10.8 MHz                                              | 02h                                   |  |  |  |  |  |

| 10.8–13.6 MHz                                             | 03h                                   |  |  |  |  |  |

| 13.6–25 MHz                                               | FLOOR[4-bit Frequency Divider Factor] |  |  |  |  |  |

| 25–50 MHz ROUND[4-bit Frequency Divider Factor]           |                                       |  |  |  |  |  |

| Note: *The frequency divider is disabled when set to 00h. |                                       |  |  |  |  |  |

# zilog 157

#### Table 87. I<sup>2</sup>C Control Registers(I2C\_CTL = 00CBh)

| Bit                       | 7                                      | 6   | 5   | 4   | 3   | 2   | 1 | 0 |

|---------------------------|----------------------------------------|-----|-----|-----|-----|-----|---|---|

| Reset                     | 0                                      | 0   | 0   | 0   | 0   | 0   | 0 | 0 |

| CPU Access                | R/W                                    | R/W | R/W | R/W | R/W | R/W | R | R |

| Note: R/W = Read/Write; I | Note: R/W = Read/Write; R = Read Only. |     |     |     |     |     |   |   |

| Bit<br>Position | Value | Description                                                      |

|-----------------|-------|------------------------------------------------------------------|

| 7               | 0     | I <sup>2</sup> C interrupt is disabled.                          |

| IEN             | 1     | I <sup>2</sup> C interrupt is enabled.                           |

| 6               | 0     | The $I^2C$ bus (SCL/SDA) is disabled and all inputs are ignored. |

| ENAB            | 1     | The I <sup>2</sup> C bus (SCL/SDA) is enabled.                   |

| 5               | 0     | Master mode START condition is sent.                             |

| STA             | 1     | Master mode start-transmit START condition on the bus.           |

| 4               | 0     | Master mode STOP condition is sent.                              |

| STP             | 1     | Master mode stop-transmit STOP condition on the bus.             |

| 3               | 0     | I <sup>2</sup> C interrupt flag is not set.                      |

| IFLG            | 1     | I <sup>2</sup> C interrupt flag is set.                          |

| 2               | 0     | Not Acknowledge.                                                 |

| AAK             | 1     | Acknowledge.                                                     |

| [1:0]           | 00    | Reserved.                                                        |

Zilog 169

Because many register Read/Write operations exhibit secondary effects, such as clearing flags or causing operations to commence, the effects of the Read/Write operations during a ZDI BREAK must be taken into consideration.

#### **Bus Requests During ZDI DEBUG Mode**

The ZDI block on the eZ80F92 device allows an external device to take control of the address and data bus while the eZ80F92 device is in DEBUG mode. ZDI\_BUSACK\_EN causes ZDI to allow or prevent acknowledgement of bus requests by external peripherals. The bus acknowledge only occurs at the end of the current ZDI operation (indicated by a High during the single-bit byte separator). The default reset condition is for bus acknowledgement to be disabled. To allow bus acknowledgement, the ZDI\_BUSACK\_EN must be written.

When an external bus request (BUSREQ pin asserted) is detected, ZDI waits until completion of the current operation before responding. ZDI acknowledges the bus request by asserting the bus acknowledge (BUSACK) signal. If the ZDI block is not currently shifting data, it acknowledges the bus request immediately. ZDI uses the single-bit byte separator of each data word to determine if it is at the end of a ZDI operation. If the bit is a logical 0, ZDI does not assert BUSACK to allow additional data Read or Write operations. If the bit is a logical 1, indicating completion of the ZDI commands, BUSACK is asserted.

#### Potential Hazards of Enabling Bus Requests During DEBUG Mode

There are some potential hazards that the user must be aware of when enabling external bus requests during ZDI DEBUG mode. First, when the address and data bus are used by an external source, ZDI must only access ZDI registers and internal CPU registers to prevent possible Bus contention. The bus acknowledge status is reported in the ZDI\_BUS\_STAT register. The BUSACK output pin also indicates the bus acknowledge state.

A second hazard is that when a bus acknowledge is granted, the ZDI is subject to any WAIT states that are assigned to the device currently accessed by the external peripheral. To prevent data errors, ZDI should avoid data transmission while another device is controlling the bus.

Finally, exiting ZDI DEBUG mode while an external peripheral controls the address and data buses, as indicated by BUSACK assertion, may produce unpredictable results.

Zilog 181

#### **ZDI Write Memory Register**

A Write to the ZDI Write Memory register causes the eZ80F92 device to write the 8-bit data to the memory location specified by the current address in the program counter. In  $Z80^{\ensuremath{\mathbb{R}}}$  MEMORY mode, this address is {MBASE, PC[15:0]}. In ADL MEMORY mode, this address is PC[23:0]. The program counter, PC, increments after each data Write. However, the ZDI register address does not increment automatically when this register is accessed. As a result, the ZDI master is allowed to write any number of data bytes by writing to this address one time followed by any number of data bytes. See Table 102.

Table 102. ZDI Write Memory Register(ZDI\_WR\_MEM = 30h in the ZDI Register Write Only Address Space)

| Bit                      | 7      | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|--------------------------|--------|---|---|---|---|---|---|---|

| Reset                    | Х      | Х | Х | Х | Х | Х | Х | Х |

| CPU Access               | W      | W | W | W | W | W | W | W |

| Note: X = Undefined; W = | Write. |   |   |   |   |   |   |   |

| Bit<br>Position     | Value       | Description                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0]<br>ZDI_WR_MEM | 00h–<br>FFh | The 8-bit data that is transferred to the ZDI slave following<br>a Write to this address is written to the address indicated<br>by the current program counter. The program counter is<br>incremented following each 8 bits of data. In Z80<br>MEMORY mode, ({MBASE, PC[15:0]}) $\leftarrow$ 8 bits of<br>transferred data. In ADL MEMORY mode,<br>(PC[23:0]) $\leftarrow$ 8 bits of transferred data. |

## zilog 184

| Bit<br>Position | Value | Description                                                                                  |

|-----------------|-------|----------------------------------------------------------------------------------------------|

| 4<br>ADL        | 0     | The CPU is operating in $Z80^{\mbox{\ensuremath{\mathbb{R}}}}$ MEMORY mode.<br>(ADL bit = 0) |

|                 | 1     | The CPU is operating in ADL MEMORY mode.<br>(ADL bit = 1)                                    |

| 3               | 0     | The CPU's Mixed-Memory mode (MADL) bit is reset to 0.                                        |

| MADL            | 1     | The CPU's Mixed-Memory mode (MADL) bit is set to 1.                                          |

| 2<br>IEF1       | 0     | The CPU's Interrupt Enable Flag 1 is reset to 0. Maskable interrupts are disabled.           |

|                 | 1     | The CPU's Interrupt Enable Flag 1 is set to 1. Maskable interrupts are enabled.              |

| [1:0]           | 00    | Reserved.                                                                                    |

#### ZDI Read Register Low, High, and Upper

The ZDI register Read Only address space offers Low, High, and Upper functions, which contain the value read by a Read operation from the ZDI Read/Write Control register (ZDI\_RW\_CTL). This data is valid only while in ZDI BREAK mode and only if the instruction is read by a request from the ZDI Read/Write Control register. See Table 107.

Table 107. ZDI Read Register Low, High and Upper(ZDI\_RD\_L = 10h, ZDI\_RD\_H = 11h, and ZDI\_RD\_U = 12h in the ZDI Register Read Only Address Space)

| Bit                  | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----------------------|---|---|---|---|---|---|---|---|

| Reset                | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| CPU Access           | R | R | R | R | R | R | R | R |

| Note: R = Read Only. |   |   |   |   |   |   |   |   |

| Bit<br>Position                                | Value       | Description                                                                                                                                                                        |

|------------------------------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0]<br>ZDI_RD_L,<br>ZDI_RD_H, or<br>ZDI_RD_U | 00h–<br>FFh | Values read from the memory location as requested by the ZDI Read Control register during a ZDI Read operation.<br>The 24-bit value is supplied by {ZDI_RD_U, ZDI_RD_H, ZDI_RD_L}. |

## Zilog 187

## **On-Chip Instrumentation**

#### Introduction to On-Chip Instrumentation

On-Chip Instrumentation<sup>1</sup> (OCI<sup>TM</sup>) for the eZ80<sup>®</sup> CPU core enables powerful debugging features. The OCI provides run control, memory and register visibility, complex breakpoints, and trace history features.

The OCI employs all of the functions of the ZDI as described in the Zilog Debug Interface section that starts on page 162. It also adds the following debug features:

- Control via a 4-pin Joint Test Action Group (JTAG)-standard port that conforms to the IEEE Standard 1149.1 (Test Access Port and Boundary Scan Architecture)<sup>2</sup>

- Complex break point trigger functions

- Break point enhancements, such as the ability to:

- Define two break point addresses that form a range

- Break on masked data values

- Start or stop trace

- Assert a trigger output signal

- Trace history buffer

- Software break point instruction

There are four sections to the OCI:

- 1. JTAG interface

- 2. ZDI debug control

- 3. Trace buffer memory

- 4. Complex triggers

#### **OCI** Activation

OCI features clock initialization circuitry so that external debug hardware can be detected during power-up. The external debugger must drive the OCI clock pin (TCK) Low at least two system clock cycles prior to the end of the RESET to activate the OCI block. If TCK is High at the end of the RESET, the OCI block shuts down so that it does not draw power in normal product operation. When the OCI is shut down, ZDI is enabled directly and can

<sup>1.</sup> On-Chip Instrumentation and OCI are trademarks of First Silicon Solutions, Inc.

<sup>2.</sup> The eZ80F92 does not contain the boundary scan register required for 1149.1 compliance.

Zilog 219

#### Table 141. Op Code Map—Fourth Byte After 0FDh, 0CBh, and dd\*

| Legend                               |            | r Nibbl               | le of 4tl   | h Byte |    |                  |         |          |    |   |   |   |   |                  |   |

|--------------------------------------|------------|-----------------------|-------------|--------|----|------------------|---------|----------|----|---|---|---|---|------------------|---|

| Upper<br>Nibble<br>of Fourth<br>Byte | <u>→</u> 4 | 6<br>BIT <del>∢</del> | – Mner      | monic  |    |                  |         |          |    |   |   |   |   |                  |   |

| First Opera                          | υ,         |                       | l<br>Second |        | nd |                  |         |          |    |   |   |   |   |                  |   |

|                                      |            |                       |             |        |    | Lo               | wer Nil | bble (He | x) |   |   |   |   |                  |   |

| 0                                    | 1          | 2                     | 3           | 4      | 5  | 6                | 7       | 8        | 9  | А | В | С | D | E                | F |

| 0                                    |            |                       |             |        |    | RLC<br>(IY+d)    |         |          |    |   |   |   |   | RRC<br>(IY+d)    |   |

| 1                                    |            |                       |             |        |    | RL<br>(IY+d)     |         |          |    |   |   |   |   | RR<br>(IY+d)     |   |

| 2                                    |            |                       |             |        |    | SLA<br>(IY+d)    |         |          |    |   |   |   |   | SRA<br>(IY+d)    |   |

| 3                                    |            |                       |             |        |    |                  |         |          |    |   |   |   |   | SRL<br>(IY+d)    |   |

| 4                                    |            |                       |             |        |    | BIT 0,<br>(IY+d) |         |          |    |   |   |   |   | BIT 1,<br>(IY+d) |   |

| 5                                    |            |                       |             |        |    | BIT 2,<br>(IY+d) |         |          |    |   |   |   |   | BIT 3,<br>(IY+d) |   |

| $\widehat{\mathbf{x}}^{6}$           |            |                       |             |        |    | BIT 4,<br>(IY+d) |         |          |    |   |   |   |   | BIT 5,<br>(IY+d) |   |

| Upper Nibble (Hex)                   |            |                       |             |        |    | BIT 6,<br>(IY+d) |         |          |    |   |   |   |   | BIT 7,<br>(IY+d) |   |

| Nibbl                                |            |                       |             |        |    | RES 0,           |         |          |    |   |   |   |   | RES 1,           |   |

| Chper                                |            |                       |             |        |    | (IY+d)<br>RES 2, |         |          |    |   |   |   |   | (IY+d)<br>RES 3, |   |

| A                                    |            |                       |             |        |    | (IY+d)<br>RES 4, |         |          |    |   |   |   |   | (IY+d)<br>RES 5, |   |

| A                                    |            |                       |             |        |    | (IY+d)           |         |          |    |   |   |   |   | (IY+d)           |   |

| В                                    |            |                       |             |        |    | RES 6,<br>(IY+d) |         |          |    |   |   |   |   | RES 7,<br>(IY+d) |   |

| С                                    |            |                       |             |        |    | SET 0,<br>(IY+d) |         |          |    |   |   |   |   | SET 1,<br>(IY+d) |   |

| D                                    |            |                       | 1           |        |    | SET 2,<br>(IY+d) |         |          |    |   |   |   |   | SET 3,<br>(IY+d) |   |

| E                                    |            |                       |             |        |    | SET 4,<br>(IY+d) |         |          |    |   |   |   |   | SET 5,<br>(IY+d) |   |

| F                                    |            |                       |             |        |    | SET 6,<br>(IY+d) |         |          |    |   |   |   |   | SET 7,<br>(IY+d) |   |

Notes: d = 8-bit two's-complement displacement.

zilog 224

#### Table 145. DC Characteristics (Continued)

|                  |                       | T <sub>A</sub> = 0 °C | to 70 °C      | T <sub>A</sub> = 0 °C | to 105 °C     |       |                                                                     |

|------------------|-----------------------|-----------------------|---------------|-----------------------|---------------|-------|---------------------------------------------------------------------|

| Symbol           | Parameter             | Min                   | Мах           | Min                   | Max           | Units | Conditions                                                          |

| I <sub>RTC</sub> | RTC Supply<br>Current | 2.5                   | 10<br>Typical | 2.5                   | 10<br>Typical | μA    | Supply current into RTC_V <sub>DD</sub> ; SLEEP mode <sup>2</sup> . |

#### Notes

1. This condition excludes all pins with on-chip pull-ups when driven Low.

2. RTC current increases when the eZ80F92 device is not in SLEEP mode as the RTC\_VDD pin supplies power to system clock buffers within the Real-Time Clock circuit.

#### **POR and VBO Electrical Characteristics**

Table 146 lists the Power-On Reset and Voltage Brownout characteristics of the eZ80F92 device.

#### Table 146. POR and VBO Electrical Characteristics

|                      |                                                                         | T <sub>A</sub> = 0 | ) °C to +1 |      |      |                    |

|----------------------|-------------------------------------------------------------------------|--------------------|------------|------|------|--------------------|

| Symbol               | Parameter                                                               | Min                | Тур        | Max  | Unit | Conditions         |

| V <sub>VBO</sub>     | VBO Voltage Threshold                                                   | 2.40               | 2.55       | 2.85 | V    | $V_{CC} = V_{VBO}$ |

| V <sub>POR</sub>     | POR Voltage Threshold                                                   | 2.45               | 2.65       | 2.90 | V    | $V_{CC} = V_{POR}$ |

| V <sub>HYST</sub>    | POR/VBO Hysteresis                                                      | 50                 | 100        | 150  | mV   |                    |

| T <sub>ANA</sub>     | POR/VBO analog RESET duration                                           | 40                 |            | 100  | μs   |                    |

| T <sub>VBO_MIN</sub> | VBO pulse reject period                                                 |                    | 10         |      | μs   |                    |

| V <sub>CCRAMP</sub>  | V <sub>CC</sub> ramp rate requirements to guarantee proper RESET occurs | 0.1                |            | 100  | V/ms |                    |

#### **Typical Current Consumption Under Various Operating Conditions**

In the following pages, Figure 53 on page 225 displays the typical current consumption of the eZ80F92 device versus the number of WAIT states while operating 25 °C, 3.3 V, and with either a 5 MHz, 10 MHz, 15 MHz, or 20 MHz system clock. Figure 54 on page 226 displays the typical current consumption of the eZ80F92 device versus the system clock frequency while operating 25 °C, 3.3 V, and using 0, 2, or 7 WAIT states. Figure 55 on page 227 displays the typical current consumption of the eZ80F92 device versus temperature while operating at 3.3 V, 7 WAIT states, and with either a 5 MHz, 10 MHz, 15 MHz or 20 MHz system clock. Figure 56 on page 228 displays the typical current consumption

## Zilog 241

## **Ordering Information**

Table 156 lists a part name, a product specification index code, and a brief description of each part.

#### Table 156. Ordering Information;

| Part Name | PSI                               | Description                                                                 |

|-----------|-----------------------------------|-----------------------------------------------------------------------------|

| eZ80F92   | eZ80F92AZ020SC,<br>eZ80F92AZ020SG | 100-pin LQFP, 128 KB Flash memory, 8 KB SRAM, 20 MHz, Standard Temperature. |

|           | eZ80F92AZ020EC,<br>eZ80F92AZ020EG | 100-pin LQFP, 128 KB Flash memory, 8 KB SRAM, 20 MHz, Extended Temperature. |

| eZ80F93   | eZ80F93AZ020SC,<br>eZ80F93AZ020SG | 100-pin LQFP, 64 KB Flash memory, 4 KB SRAM, 20 MHz, Standard Temperature.  |

|           | eZ80F93AZ020EC,<br>eZ80F93AZ020EG | 100-pin LQFP, 64 KB Flash memory, 4 KB SRAM, 20 MHz, Extended Temperature.  |

Navigate your browser to Zilog's website to order the <u>eZ80F92</u> or the <u>eZ80F93</u>. Or, contact your local <u>Zilog Sales Office</u> to order these devices. Zilog provides additional assistance on its <u>Customer Service</u> page, and is also here to help with technical support issues.

For Zilog's valuable <u>software development tools</u> and <u>downloadable software</u>, visit <u>www.zilog.com</u>.

#### **Part Number Description**

Zilog part numbers consist of a number of components, as listed in the following examples:

| Zilog Base Products |                    |

|---------------------|--------------------|

| eZ80 <sup>®</sup>   | Zilog eZ80 CPU     |

| F92                 | Product Number     |

| AZ                  | Package            |

| 020                 | Speed              |

| S or E              | Temperature        |

| C or G              | Environmental Flow |

zilog |<sub>2</sub>

251

voltage brown-out threshold 32 voltage, supply 2, 32, 33, 40, 141, 222, 223 VVBO—see Voltage Brown-Out threshold 33, 224

#### W

WAIT 1, 11, 22, 57, 60, 64 WAIT condition 206 WAIT Input Signal 51 WAIT pin, external 53, 54 WAIT Request 11 WAIT state 61, 235, 236 wait state 54 Wait State Timing for Read Operations 235 Wait State Timing for Write Operations 236 WAIT States 225, 226 WAIT states 46, 51, 52, 53, 54, 60, 69, 169, 190, 200, 224 Wait States 51, 223 Wait states 200 wait states 48 Watch-Dog Timer 32, 35, 72, 168 Watch-Dog Timer Control Register 74 Watch-Dog Timer Control register 30 Watch-Dog Timer Operation 73 Watch-Dog Timer Overview 72 Watch-Dog Timer Registers 74 Watch-Dog Timer reset 30 Watch-Dog Timer Reset Register 75 Watch-Dog Timer time-out 36 Watch-Dog Timer time-out reset 30 WCOL 133, 134 wcOl 138 WDT 32, 35, 72, 73, 74 WDT clock source 72, 74 WDT clock sources 73 WDT RESET 74 WDT time-out 72, 73, 74, 75 WDT time-out period 73, 75 WDT time-out values 73 WR 11, 22, 48, 51, 54, 57, 60, 232, 234 Write Collision 134 write collision 133 write collision, SPI 138

Write Violation 203

#### Χ

XIN 17, 23 XOUT 17, 23

#### Ζ

Z80-53 Z80 Bus Mode 53 Z80 Memory mode 181, 185 ZCL 164, 166, 173 ZCL pin 164 ZDA 164, 173, 188 ZDA pin 164 ZDI 187 ZDI Address Match Registers 171 ZDI Block Read 168 **ZDI BLOCK WRITE 167** ZDI Break 174 **ZDI BREAK Control Register 172** ZDI BREAK mode 184 ZDI Bus Control Register 179 ZDI Bus Status Register 185 ZDI Clock and Data Conventions 164 ZDI Clock Frequency 163 ZDI data transfer 165 ZDI debug control 187 ZDI Debug mode 165, 179, 185 ZDI master 165, 167, 168, 180, 181, 185 ZDI Master Control Register 175 **ZDI Read Memory Register 185 ZDI Read Operations 167** ZDI Read Register Low, High, and Upper 184 ZDI Read/Write Control Register 176 ZDI Read-Only Registers 171 ZDI Register Addressing 165 **ZDI Register Definitions 171** ZDI Single-Bit Byte Separator 165 ZDI Single-Byte Read 167 **ZDI SINGLE-BYTE WRITE 166** ZDI slave 164, 167, 168 ZDI START command 165