#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E-XF

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | 8051                                                                       |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 50MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART                         |

| Peripherals                | CapSense, DMA, LCD, POR, PWM, WDT                                          |

| Number of I/O              | 38                                                                         |

| Program Memory Size        | 16KB (16K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 512 x 8                                                                    |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                               |

| Data Converters            | A/D 16x12b; D/A 2x8b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 68-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 68-QFN (8x8)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c3444lti-110 |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **More Information**

Cypress provides a wealth of data at www.cypress.com to help you to select the right PSoC device for your design, and to help you to quickly and effectively integrate the device into your design. For a comprehensive list of resources, see the knowledge base article KBA86521, How to Design with PSoC 3, PSoC 4, and PSoC 5LP. Following is an abbreviated list for PSoC 3:

- Overview: PSoC Portfolio, PSoC Roadmap

- Product Selectors: PSoC 1, PSoC 3, PSoC 4, PSoC 5LP In addition, PSoC Creator includes a device selection tool.

- Application notes: Cypress offers a large number of PSoC application notes and code examples covering a broad range of topics, from basic to advanced level. Recommended application notes for getting started with PSoC 3 are:

- AN54181: Getting Started With PSoC 3

- AN61290: Hardware Design Considerations

- AN57821: Mixed Signal Circuit Board Layout

- AN58304: Pin Selection for Analog Designs

- AN81623: Digital Design Best Practices

- AN73854: Introduction To Bootloaders

using the PSoC Creator IDE C compiler

- Development Kits:

- CY8CKIT-030 is designed for analog performance, for developing high-precision analog, low-power, and low-voltage applications.

- CY8CKIT-001 provides a common development platform for any one of the PSoC 1, PSoC 3, PSoC 4, or PSoC 5LP families of devices.

- The MiniProg3 device provides an interface for flash programming and debug.

- Technical Reference Manuals (TRM)

- Architecture TRM

- Registers TRM

- Programming Specification

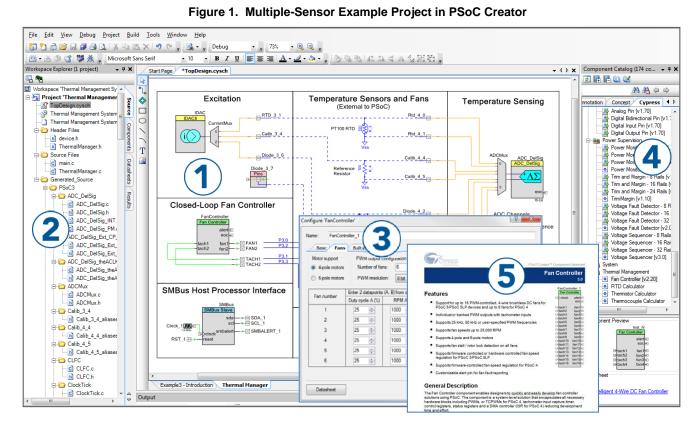

# PSoC Creator

PSoC Creator is a free Windows-based Integrated Design Environment (IDE). It enables concurrent hardware and firmware design of PSoC 3, PSoC 4, and PSoC 5LP based systems. Create designs using classic, familiar schematic capture supported by over 100 pre-verified, production-ready PSoC Components; see the list of component datasheets. With PSoC Creator, you can:

1. Drag and drop component icons to build your hardware system design in the main design workspace

2. Codesign your application firmware with the PSoC hardware,

- 3. Configure components using the configuration tools

- 4. Explore the library of 100+ components

- 5. Review component datasheets

The device provides a PLL to generate clock frequencies up to 50 MHz from the IMO, external crystal, or external reference clock. It also contains a separate, very low-power Internal low-speed oscillator (ILO) for the sleep and watchdog timers. A 32.768-kHz external watch crystal is also supported for use in RTC applications. The clocks, together with programmable clock dividers, provide the flexibility to integrate most timing requirements.

The CY8C34 family supports a wide supply operating range from 1.71 V to 5.5 V. This allows operation from regulated supplies such as 1.8 V ± 5 percent, 2.5 V ±10 percent, 3.3 V ± 10 percent, or 5.0 V ± 10 percent, or directly from a wide range of battery types. In addition, it provides an integrated high efficiency synchronous boost converter that can power the device from supply voltages as low as 0.5 V. This enables the device to be powered directly from a single battery or solar cell. In addition, you can use the boost converter to generate other voltages required by the device, such as a 3.3-V supply for LCD glass drive. The boost's output is available on the V<sub>BOOST</sub> pin, allowing other devices in the application to be powered from the PSoC.

PSoC supports a wide range of low-power modes. These include a 200-nA hibernate mode with RAM retention and a 1- $\mu$ A sleep mode with RTC. In the second mode the optional 32.768-kHz watch crystal runs continuously and maintains an accurate RTC.

Power to all major functional blocks, including the programmable digital and analog peripherals, can be controlled independently by firmware. This allows low-power background processing when some peripherals are not in use. This, in turn, provides a total device current of only 1.2 mA when the CPU is running at 6 MHz, or 0.8 mA running at 3 MHz.

The details of the PSoC power modes are covered in the "Power System" section on page 30 of this data sheet.

PSoC uses JTAG (4-wire) or SWD (2-wire) interfaces for programming, debug, and test. The 1-wire SWV may also be used for 'printf' style debugging. By combining SWD and SWV, you can implement a full debugging interface with just three pins. Using these standard interfaces enables you to debug or program the PSoC with a variety of hardware solutions from Cypress or third party vendors. PSoC supports on-chip break points and 4 KB instruction and data race memory for debug. Details of the programming, test, and debugging interfaces are discussed in the "Programming, Debug Interfaces, Resources" section on page 65 of this data sheet.

# 2. Pinouts

Each VDDIO pin powers a specific set of I/O pins. (The USBIOs are powered from VDDD.) Using the VDDIO pins, a single PSoC can support multiple voltage levels, reducing the need for off-chip level shifters. The black lines drawn on the pinout diagrams in Figure 2-3 through Figure 2-6, as well as Table 2-1, show the pins that are powered by each VDDIO.

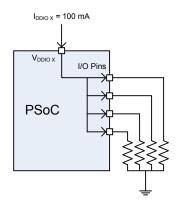

Each VDDIO may source up to 100 mA total to its associated I/O pins, as shown in Figure 2-1.

### Figure 2-1. VDDIO Current Limit

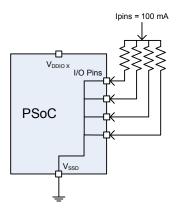

Conversely, for the 100-pin and 68-pin devices, the set of I/O pins associated with any VDDIO may sink up to 100 mA total, as shown in Figure 2-2.

#### Figure 2-2. I/O Pins Current Limit

For the 48-pin devices, the set of I/O pins associated with VDDIO0 plus VDDIO2 may sink up to 100 mA total. The set of I/O pins associated with VDDIO1 plus VDDIO3 may sink up to a total of 100 mA.

#### 4.3.1.2 Logical Instructions

The logical instructions perform Boolean operations such as AND, OR, XOR on bytes, rotate of accumulator contents, and swap of nibbles in an accumulator. The Boolean operations on the bytes are performed on the bit-by-bit basis. Table 4-2 shows the list of logical instructions and their description.

#### Table 4-2. Logical Instructions

|     | Mnemonic      | Description                           | Bytes | Cycles |

|-----|---------------|---------------------------------------|-------|--------|

| ANL | A,Rn          | AND register to accumulator           | 1     | 1      |

| ANL | A,Direct      | AND direct byte to accumulator        | 2     | 2      |

| ANL | A,@Ri         | AND indirect RAM to accumulator       | 1     | 2      |

| ANL | A,#data       | AND immediate data to accumulator     | 2     | 2      |

| ANL | Direct, A     | AND accumulator to direct byte        | 2     | 3      |

| ANL | Direct, #data | AND immediate data to direct byte     | 3     | 3      |

| ORL | A,Rn          | OR register to accumulator            | 1     | 1      |

| ORL | A,Direct      | OR direct byte to accumulator         | 2     | 2      |

| ORL | A,@Ri         | OR indirect RAM to accumulator        | 1     | 2      |

| ORL | A,#data       | OR immediate data to accumulator      | 2     | 2      |

| ORL | Direct, A     | OR accumulator to direct byte         | 2     | 3      |

| ORL | Direct, #data | OR immediate data to direct byte      | 3     | 3      |

| XRL | A,Rn          | XOR register to accumulator           | 1     | 1      |

| XRL | A,Direct      | XOR direct byte to accumulator        | 2     | 2      |

| XRL | A,@Ri         | XOR indirect RAM to accumulator       | 1     | 2      |

| XRL | A,#data       | XOR immediate data to accumulator     | 2     | 2      |

| XRL | Direct, A     | XOR accumulator to direct byte        | 2     | 3      |

| XRL | Direct, #data | XOR immediate data to direct byte     | 3     | 3      |

| CLR | Α             | Clear accumulator                     | 1     | 1      |

| CPL | A             | Complement accumulator                | 1     | 1      |

| RL  | А             | Rotate accumulator left               | 1     | 1      |

| RLC | A             | Rotate accumulator left through carry | 1     | 1      |

| RR  | A             | Rotate accumulator right              | 1     | 1      |

| RRC | А             | Rotate accumulator right though carry | 1     | 1      |

| SWA | PA            | Swap nibbles within accumulator       | 1     | 1      |

## 4.4 DMA and PHUB

The PHUB and the DMA controller are responsible for data transfer between the CPU and peripherals, and also data transfers between peripherals. The PHUB and DMA also control device configuration during boot. The PHUB consists of:

- A central hub that includes the DMA controller, arbiter, and router

- Multiple spokes that radiate outward from the hub to most peripherals

There are two PHUB masters: the CPU and the DMA controller. Both masters may initiate transactions on the bus. The DMA channels can handle peripheral communication without CPU intervention. The arbiter in the central hub determines which DMA channel is the highest priority if there are multiple requests.

#### 4.4.1 PHUB Features

- CPU and DMA controller are both bus masters to the PHUB

- Eight Multi-layer AHB Bus parallel access paths (spokes) for peripheral access

- Simultaneous CPU and DMA access to peripherals located on different spokes

- Simultaneous DMA source and destination burst transactions on different spokes

- Supports 8, 16, 24, and 32-bit addressing and data

#### Table 4-6. PHUB Spokes and Peripherals

| PHUB Spokes | Peripherals                                                                                         |

|-------------|-----------------------------------------------------------------------------------------------------|

| 0           | SRAM                                                                                                |

| 1           | IOs, PICU, EMIF                                                                                     |

| 2           | PHUB local configuration, Power manager,<br>Clocks, IC, SWV, EEPROM, Flash<br>programming interface |

| 3           | Analog interface and trim, Decimator                                                                |

| 4           | USB, CAN, I <sup>2</sup> C, Timers, Counters, and PWMs                                              |

| 5           | Reserved                                                                                            |

| 6           | UDBs group 1                                                                                        |

| 7           | UDBs group 2                                                                                        |

#### 4.4.2 DMA Features

- Twenty-four DMA channels

- Each channel has one or more Transaction Descriptors (TDs) to configure channel behavior. Up to 128 total TDs can be defined

- TDs can be dynamically updated

- Eight levels of priority per channel

- Any digitally routable signal, the CPU, or another DMA channel, can trigger a transaction

- Each channel can generate up to two interrupts per transfer

- Transactions can be stalled or canceled

- Supports transaction size of infinite or 1 to 64 KB

- TDs may be nested and/or chained for complex transactions

#### 4.4.3 Priority Levels

The CPU always has higher priority than the DMA controller when their accesses require the same bus resources. Due to the system architecture, the CPU can never starve the DMA. DMA channels of higher priority (lower priority number) may interrupt current DMA transfers. In the case of an interrupt, the current transfer is allowed to complete its current transaction. To ensure latency limits when multiple DMA accesses are requested simultaneously, a fairness algorithm guarantees an interleaved minimum percentage of bus bandwidth for priority levels 2 through 7. Priority levels 0 and 1 do not take part in the fairness algorithm and may use 100 percent of the bus bandwidth. If a tie occurs on two DMA requests of the same priority level, a simple round robin method is used to evenly share the allocated bandwidth. The round robin allocation can be disabled for each DMA channel, allowing it to always be at the head of the line. Priority levels 2 to 7 are guaranteed the minimum bus bandwidth shown in Table 4-7 after the CPU and DMA priority levels 0 and 1 have satisfied their requirements.

#### Table 4-7. Priority Levels

| Priority Level | % Bus Bandwidth |

|----------------|-----------------|

| 0              | 100.0           |

| 1              | 100.0           |

| 2              | 50.0            |

| 3              | 25.0            |

| 4              | 12.5            |

| 5              | 6.2             |

| 6              | 3.1             |

| 7              | 1.5             |

When the fairness algorithm is disabled, DMA access is granted based solely on the priority level; no bus bandwidth guarantees are made.

#### 4.4.4 Transaction Modes Supported

The flexible configuration of each DMA channel and the ability to chain multiple channels allow the creation of both simple and complex use cases. General use cases include, but are not limited to:

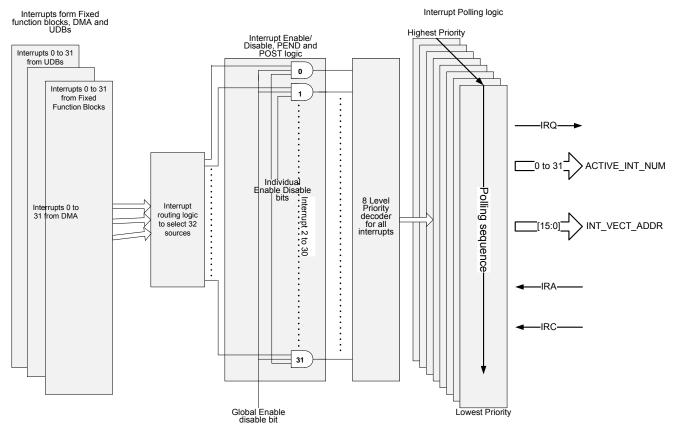

- 6: CPU acknowledges the interrupt request

- 7: ISR address is read by CPU for branching

- 8, 9: PEND and POST bits are cleared respectively after receiving the IRA from core

- 10: IRA bit is cleared after completing the current instruction and starting the instruction execution from ISR location (takes 7 cycles)

- 11: IRC is set to indicate the completion of ISR, Active int. status is restored with previous status

The total interrupt latency (ISR execution)

- = POST + PEND + IRQ + IRA + Completing current instruction and branching

- = 1+1+1+2+7 cycles

- = 12 cycles

Figure 4-3. Interrupt Structure

## 6.4 I/O System and Routing

PSoC I/Os are extremely flexible. Every GPIO has analog and digital I/O capability. All I/Os have a large number of drive modes, which are set at POR. PSoC also provides up to four individual I/O voltage domains through the VDDIO pins.

There are two types of I/O pins on every device; those with USB provide a third type. Both General Purpose I/O (GPIO) and Special I/O (SIO) provide similar digital functionality. The primary differences are their analog capability and drive strength. Devices that include USB also provide two USBIO pins that support specific USB functionality as well as limited GPIO capability.

All I/O pins are available for use as digital inputs and outputs for both the CPU and digital peripherals. In addition, all I/O pins can generate an interrupt. The flexible and advanced capabilities of the PSoC I/O, combined with any signal to any pin routability, greatly simplify circuit design and board layout. All GPIO pins can be used for analog input, CapSense<sup>[13]</sup>, and LCD segment drive, while SIO pins are used for voltages in excess of VDDA and for programmable output voltages.

- Features supported by both GPIO and SIO:

- User programmable port reset state

- □ Separate I/O supplies and voltages for up to four groups of I/O

- Digital peripherals use DSI to connect the pins

- Input or output or both for CPU and DMA

- Eight drive modes

- Every pin can be an interrupt source configured as rising edge, falling edge or both edges. If required, level sensitive interrupts are supported through the DSI

- Dedicated port interrupt vector for each port

- Slew rate controlled digital output drive mode

- Access port control and configuration registers on either port basis or pin basis

- Separate port read (PS) and write (DR) data registers to avoid read modify write errors

- Special functionality on a pin by pin basis

- Additional features only provided on the GPIO pins:

- LCD segment drive on LCD equipped devices

- □ CapSense<sup>[13]</sup>

- Analog input and output capability

- Continuous 100 µA clamp current capability

- Standard drive strength down to 1.7 V

- Additional features only provided on SIO pins:

- B Higher drive strength than GPIO

- $\blacksquare$  Hot swap capability (5 V tolerance at any operating V\_{DD})

- Programmable and regulated high input and output drive levels down to 1.2 V

- D No analog input, CapSense, or LCD capability

- Dver voltage tolerance up to 5.5 V

- □ SIO can act as a general purpose analog comparator

- USBIO features:

- □ Full speed USB 2.0 compliant I/O

- Highest drive strength for general purpose use

- □ Input, output, or both for CPU and DMA

- □ Input, output, or both for digital peripherals

- Digital output (CMOS) drive mode

- Each pin can be an interrupt source configured as rising edge, falling edge, or both edges

<sup>13.</sup> GPIOs with opamp outputs are not recommended for use with CapSense

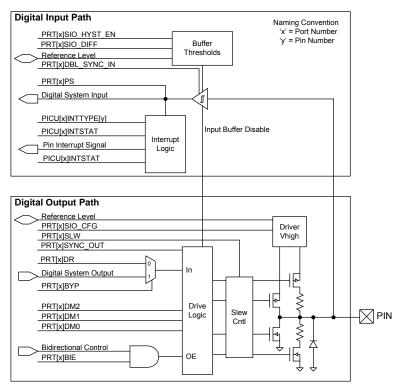

## Figure 6-10. SIO Input/Output Block Diagram

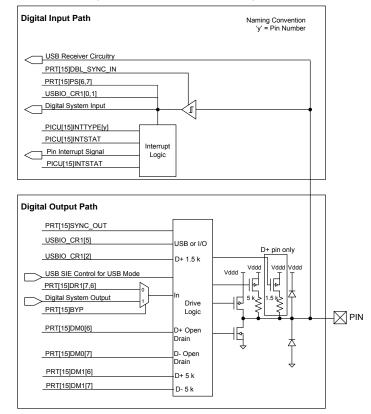

Figure 6-11. USBIO Block Diagram

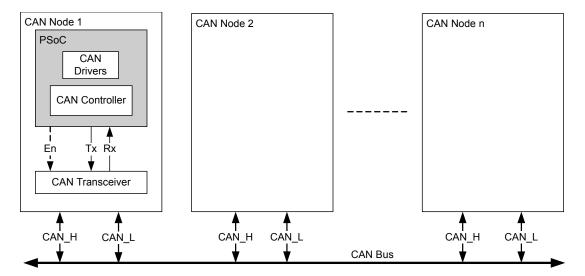

Figure 7-14. CAN Bus System Implementation

#### 7.5.1 CAN Features

- CAN2.0A/B protocol implementation ISO 11898 compliant

Standard and extended frames with up to 8 bytes of data per frame

- Message filter capabilities

- Remote Transmission Request (RTR) support

- Programmable bit rate up to 1 Mbps

- Listen Only mode

- SW readable error counter and indicator

- Sleep mode: Wake the device from sleep with activity on the Rx pin

- Supports two or three wire interface to external transceiver (Tx, Rx, and Enable). The three-wire interface is compatible with the Philips PHY; the PHY is not included on-chip. The three wires can be routed to any I/O

- Enhanced interrupt controller

- CAN receive and transmit buffers status

- CAN controller error status including BusOff

- Receive path

- **□** 16 receive buffers each with its own message filter

- Enhanced hardware message filter implementation that covers the ID, IDE and RTR

- DeviceNet addressing support

- Multiple receive buffers linkable to build a larger receive message array

- a Automatic transmission request (RTR) response handler

- Lost received message notification

- Transmit path

- Eight transmit buffers

- Programmable transmit priority

- Round robin

- · Fixed priority

- Message transmissions abort capability

7.5.2 Software Tools Support

CAN Controller configuration integrated into PSoC Creator:

- CAN Configuration walkthrough with bit timing analyzer

- Receive filter setup

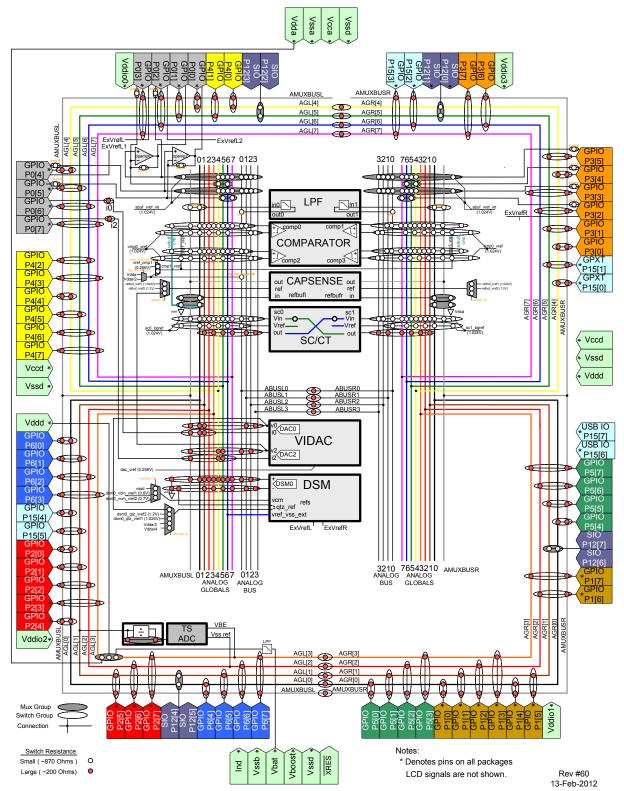

Figure 8-2. CY8C34 Analog Interconnect

To preserve detail of this figure, this figure is best viewed with a PDF display program or printed on a 11" × 17" paper.

#### Figure 8-12. Mixer Configuration

## 8.11 Sample and Hold

The main application for a sample and hold, is to hold a value stable while an ADC is performing a conversion. Some applications require multiple signals to be sampled simultaneously, such as for power calculations (V and I).

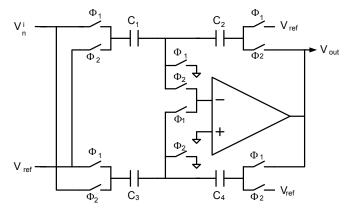

# Figure 8-13. Sample and Hold Topology $(\Phi 1 \text{ and } \Phi 2 \text{ are opposite phases of a clock})$

## 8.11.1 Down Mixer

The SC/CT block can be used as a mixer to down convert an input signal. This circuit is a high bandwidth passive sample network that can sample input signals up to 14 MHz. This sampled value is then held using the opamp with a maximum clock rate of 4 MHz. The output frequency is at the difference between the input frequency and the highest integer multiple of the Local Oscillator that is less than the input.

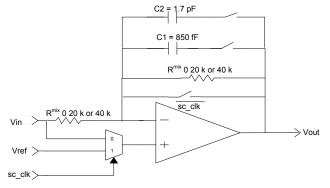

#### 8.11.2 First Order Modulator - SC Mode

A first order modulator is constructed by placing the SC/CT block in an integrator mode and using a comparator to provide a 1-bit feedback to the input. Depending on this bit, a reference voltage is either subtracted or added to the input signal. The block output is the output of the comparator and not the integrator in the modulator case. The signal is downshifted and buffered and then processed by a decimator to make a delta-sigma converter or a counter to make an incremental converter. The accuracy of the sampled data from the first-order modulator is determined from several factors.

The main application for this modulator is for a low-frequency ADC with high accuracy. Applications include strain gauges, thermocouples, precision voltage, and current measurement.

# 9. Programming, Debug Interfaces, Resources

PSoC devices include extensive support for programming, testing, debugging, and tracing both hardware and firmware. Three interfaces are available: JTAG, SWD, and SWV. JTAG and SWD support all programming and debug features of the device. JTAG also supports standard JTAG scan chains for board level test and chaining multiple JTAG devices to a single JTAG connection.

# For more information on PSoC 3 Programming, refer to the $PSoC^{\textcircled{R}}$ 3 Device Programming Specifications.

Complete Debug on Chip (DoC) functionality enables full device debugging in the final system using the standard production device. It does not require special interfaces, debugging pods, simulators, or emulators. Only the standard programming connections are required to fully support debug.

The PSoC Creator IDE software provides fully integrated programming and debug support for PSoC devices. The low cost MiniProg3 programmer and debugger is designed to provide full programming and debug support of PSoC devices in conjunction with the PSoC Creator IDE. PSoC JTAG, SWD, and SWV interfaces are fully compatible with industry standard third party tools.

All DOC circuits are disabled by default and can only be enabled in firmware. If not enabled, the only way to reenable them is to erase the entire device, clear flash protection, and reprogram the device with new firmware that enables DOC. Disabling DOC features, robust flash protection, and hiding custom analog and digital functionality inside the PSoC device provide a level of security not possible with multichip application solutions. Additionally, all device interfaces can be permanently disabled (Device Security) for applications concerned about phishing attacks due to a maliciously reprogrammed device. Permanently disabling interfaces is not recommended in most applications because you cannot access the device later. Because all programming, debug, and test interfaces are disabled when Device Security is enabled, PSoCs with Device Security enabled may not be returned for failure analysis.

#### Table 9-1. Debug Configurations

| Debug and Trace Configuration | GPIO Pins Used |

|-------------------------------|----------------|

| All debug and trace disabled  | 0              |

| JTAG                          | 4 or 5         |

| SWD                           | 2              |

| SWV                           | 1              |

| SWD + SWV                     | 3              |

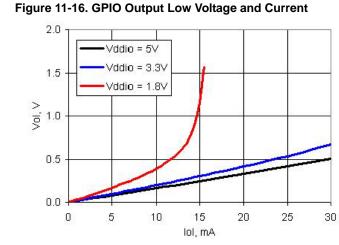

5 4 Voh, V 3 2 Vddio = 5V Vddio = 3.3V 1 Vddio = 1.8V 0 10 0 5 15 20 25 30 loh, mA

## Figure 11-15. GPIO Output High Voltage and Current

## Table 11-10. GPIO AC Specifications

| Parameter | Description                                                                             | Conditions                            | Min | Тур | Max | Units |

|-----------|-----------------------------------------------------------------------------------------|---------------------------------------|-----|-----|-----|-------|

| TriseF    | Rise time in Fast Strong Mode <sup>[41]</sup>                                           | 3.3 V V <sub>DDIO</sub> Cload = 25 pF | -   | -   | 6   | ns    |

| TfallF    | Fall time in Fast Strong Mode <sup>[41]</sup>                                           | 3.3 V V <sub>DDIO</sub> Cload = 25 pF | -   | -   | 6   | ns    |

| TriseS    | Rise time in Slow Strong Mode <sup>[41]</sup>                                           | 3.3 V V <sub>DDIO</sub> Cload = 25 pF | -   | -   | 60  | ns    |

| TfallS    | Fall time in Slow Strong Mode <sup>[41]</sup>                                           | 3.3 V V <sub>DDIO</sub> Cload = 25 pF | -   | -   | 60  | ns    |

|           | GPIO output operating frequency                                                         |                                       |     |     |     |       |

|           | $2.7 \text{ V} \leq \text{V}_{\text{DDIO}} \leq 5.5 \text{ V}$ , fast strong drive mode | 90/10% V <sub>DDIO</sub> into 25 pF   | -   | -   | 33  | MHz   |

| Fgpioout  | $1.71 \text{ V} \leq \text{V}_{\text{DDIO}} < 2.7 \text{ V}$ , fast strong drive mode   | 90/10% V <sub>DDIO</sub> into 25 pF   | -   | -   | 20  | MHz   |

|           | $3.3 \text{ V} \leq \text{V}_{\text{DDIO}} \leq 5.5 \text{ V}$ , slow strong drive mode | 90/10% V <sub>DDIO</sub> into 25 pF   | -   | -   | 7   | MHz   |

|           | 1.71 V $\leq$ V <sub>DDIO</sub> < 3.3 V, slow strong drive mode                         | 90/10% V <sub>DDIO</sub> into 25 pF   | -   | -   | 3.5 | MHz   |

| Fgpioin   | GPIO input operating frequency                                                          |                                       | 1   |     |     |       |

| gpioin    | 1.71 V ≤ V <sub>DDIO</sub> ≤ 5.5 V                                                      | 90/10% V <sub>DDIO</sub>              | -   | -   | 33  | MHz   |

<sup>41.</sup> Based on device characterization (Not production tested).

## 11.4.2 SIO

## Table 11-11. SIO DC Specifications

| Parameter       | Description                                            | Conditions                                                        | Min                     | Тур | Max                     | Units |  |  |

|-----------------|--------------------------------------------------------|-------------------------------------------------------------------|-------------------------|-----|-------------------------|-------|--|--|

| Vinmax          | Maximum input voltage                                  | All allowed values of $V_{DDIO}$ and $V_{DDD}$ , see Section 11.1 | -                       | _   | 5.5                     | V     |  |  |

| Vinref          | Input voltage reference (Differential input mode)      |                                                                   | 0.5                     | -   | $0.52 \times V_{DDIO}$  | V     |  |  |

|                 | Output voltage reference (Regulate                     | d output mode)                                                    |                         |     |                         |       |  |  |

| /outref         |                                                        | V <sub>DDIO</sub> > 3.7                                           | 1                       | _   | V <sub>DDIO</sub> – 1   | V     |  |  |

|                 |                                                        | V <sub>DDIO</sub> < 3.7                                           | 1                       | _   | V <sub>DDIO</sub> – 0.5 | V     |  |  |

|                 | Input voltage high threshold                           |                                                                   |                         |     |                         |       |  |  |

| V <sub>IH</sub> | GPIO mode                                              | CMOS input                                                        | $0.7 \times V_{DDIO}$   | _   | _                       | V     |  |  |

|                 | Differential input mode <sup>[42]</sup>                | Hysteresis disabled                                               | SIO_ref + 0.2           | _   | -                       | V     |  |  |

|                 | Input voltage low threshold                            |                                                                   |                         |     |                         |       |  |  |

| V <sub>IL</sub> | GPIO mode                                              | CMOS input                                                        | -                       | _   | $0.3 \times V_{DDIO}$   | V     |  |  |

|                 | Differential input mode <sup>[42]</sup>                | Hysteresis disabled                                               | -                       | -   | SIO_ref-0.2             | V     |  |  |

|                 | Output voltage high                                    |                                                                   |                         |     |                         |       |  |  |

| V               | Unregulated mode                                       | I <sub>OH</sub> = 4 mA, V <sub>DDIO</sub> = 3.3 V                 | V <sub>DDIO</sub> – 0.4 | -   | -                       | V     |  |  |

| V <sub>OH</sub> | Regulated mode <sup>[42]</sup>                         | I <sub>OH</sub> = 1 mA                                            | SIO_ref - 0.65          | _   | SIO_ref + 0.2           | V     |  |  |

|                 | Regulated mode <sup>[42]</sup>                         | I <sub>OH</sub> = 0.1 mA                                          | SIO_ref – 0.3           | -   | SIO_ref + 0.2           | V     |  |  |

|                 | Output voltage low                                     | V <sub>DDIO</sub> = 3.30 V, I <sub>OL</sub> = 25 mA               | -                       | _   | 0.8                     | V     |  |  |

| V <sub>OL</sub> |                                                        | V <sub>DDIO</sub> = 3.30 V, I <sub>OL</sub> = 20 mA               | -                       | _   | 0.4                     | V     |  |  |

|                 |                                                        | V <sub>DDIO</sub> = 1.80 V, I <sub>OL</sub> = 4 mA                | -                       | _   | 0.4                     | V     |  |  |

| Rpullup         | Pull-up resistor                                       |                                                                   | 3.5                     | 5.6 | 8.5                     | kΩ    |  |  |

| Rpulldown       | Pull-down resistor                                     |                                                                   | 3.5                     | 5.6 | 8.5                     | kΩ    |  |  |

| IIL             | Input leakage current (absolute value) <sup>[43]</sup> |                                                                   |                         |     |                         |       |  |  |

|                 | V <sub>IH</sub> <u>≤</u> Vddsio                        | 25 °C, Vddsio = 3.0 V, V <sub>IH</sub> = 3.0 V                    | _                       | -   | 14                      | nA    |  |  |

|                 | V <sub>IH</sub> > Vddsio                               | 25 °C, Vddsio = 0 V, V <sub>IH</sub> = 3.0 V                      | _                       | -   | 10                      | μA    |  |  |

| C <sub>IN</sub> | Input capacitance <sup>[43]</sup>                      |                                                                   | _                       | _   | 7                       | pF    |  |  |

|                 | Input voltage hysteresis                               | Single ended mode (GPIO mode)                                     | _                       | 40  | _                       | mV    |  |  |

| V <sub>H</sub>  | (Schmitt-Trigger) <sup>[43]</sup>                      | Differential mode                                                 | -                       | 35  | -                       | mV    |  |  |

| Idiode          | Current through protection diode to $V_{SSIO}$         |                                                                   | _                       | -   | 100                     | μA    |  |  |

Notes 42. See Figure 6-10 on page 38 and Figure 6-13 on page 42 for more information on SIO reference. 43. Based on device characterization (Not production tested).

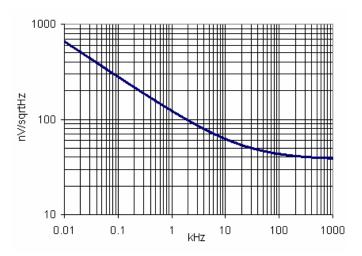

Figure 11-30. Opamp Noise vs Frequency, Power Mode = High,  $V_{DDA}$  = 5V

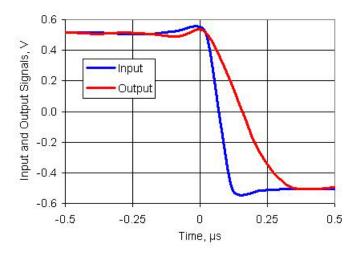

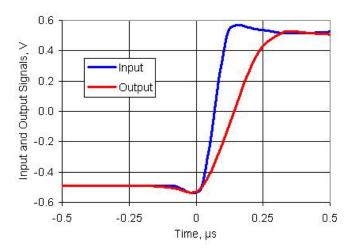

Figure 11-32. Opamp Step Response, Falling

Figure 11-31. Opamp Step Response, Rising

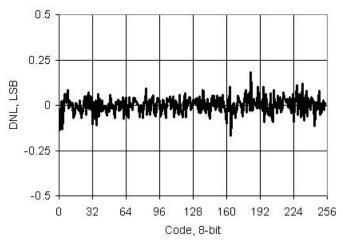

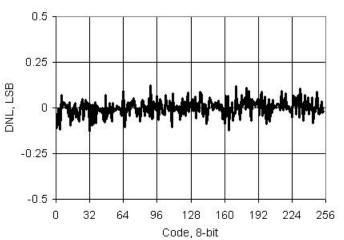

Figure 11-36. IDAC DNL vs Input Code, Range = 255  $\mu$ A, Source Mode

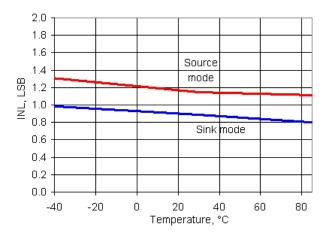

Figure 11-38. IDAC INL vs Temperature, Range = 255  $\mu A$ , High speed mode

Figure 11-37. IDAC DNL vs Input Code, Range = 255  $\mu\text{A},$  Sink Mode

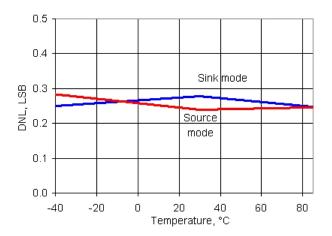

Figure 11-39. IDAC DNL vs Temperature, Range = 255  $\mu\text{A},$  High speed mode

## 11.6.6 USB

## Table 11-51. USB DC Specifications

| Parameter            | Description                                | Conditions                                                                                          | Min  | Тур | Max  | Units |

|----------------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------|------|-----|------|-------|

| V <sub>USB_5</sub>   | operation                                  | USB configured, USB regulator<br>enabled                                                            | 4.35 | -   | 5.25 | V     |

| V <sub>USB_3.3</sub> |                                            | USB configured, USB regulator bypassed                                                              | 3.15 | -   | 3.6  | V     |

| V <sub>USB_3</sub>   |                                            | USB configured, USB regulator bypassed <sup>[58]</sup>                                              | 2.85 | -   | 3.6  | V     |

| IUSB_Configured      | Device supply current in device active     | V <sub>DDD</sub> = 5 V, F <sub>CPU</sub> = 1.5 MHz                                                  | -    | 10  | -    | mA    |

|                      | mode, bus clock and IMO = 24 MHz           | V <sub>DDD</sub> = 3.3 V, F <sub>CPU</sub> = 1.5 MHz                                                | -    | 8   | -    | mA    |

| IUSB_Suspended       | Device supply current in device sleep mode | V <sub>DDD</sub> = 5 V, connected to USB<br>host, PICU configured to wake on<br>USB resume signal   | _    | 0.5 | -    | mA    |

|                      |                                            | V <sub>DDD</sub> = 5 V, disconnected from<br>USB host                                               | -    | 0.3 | -    | mA    |

|                      |                                            | V <sub>DDD</sub> = 3.3 V, connected to USB<br>host, PICU configured to wake on<br>USB resume signal | _    | 0.5 | -    | mA    |

|                      |                                            | V <sub>DDD</sub> = 3.3 V, disconnected from<br>USB host                                             | -    | 0.3 | _    | mA    |

## 11.6.7 Universal Digital Blocks (UDBs)

PSoC Creator provides a library of pre-built and tested standard digital peripherals (UART, SPI, LIN, PRS, CRC, timer, counter, PWM, AND, OR, and so on) that are mapped to the UDB array. See the component data sheets in PSoC Creator for full AC/DC specifications, APIs, and example code.

## Table 11-52. UDB AC Specifications

| Parameter              | Description                                                   | Conditions                                          | Min | Тур | Max   | Units |  |  |  |

|------------------------|---------------------------------------------------------------|-----------------------------------------------------|-----|-----|-------|-------|--|--|--|

| Datapath Per           | Datapath Performance                                          |                                                     |     |     |       |       |  |  |  |

| F <sub>MAX_TIMER</sub> | Maximum frequency of 16-bit timer in a UDB pair               |                                                     | -   | -   | 50.01 | MHz   |  |  |  |

| F <sub>MAX_ADDER</sub> | Maximum frequency of 16-bit adder in a UDB pair               |                                                     | _   | -   | 50.01 | MHz   |  |  |  |

| F <sub>MAX_CRC</sub>   | Maximum frequency of 16-bit<br>CRC/PRS in a UDB pair          |                                                     | -   | -   | 50.01 | MHz   |  |  |  |

| PLD Performa           | ance                                                          |                                                     |     |     |       |       |  |  |  |

| F <sub>MAX_PLD</sub>   | Maximum frequency of a two-pass PLD function in a UDB pair    |                                                     | -   | -   | 50.01 | MHz   |  |  |  |

| Clock to Outp          | out Performance                                               | · · · · · · · · · · · · · · · · · · ·               |     |     |       |       |  |  |  |

| t <sub>CLK_OUT</sub>   | Propagation delay for clock in to data out, see Figure 11-63. | 25 °C, $V_{DDD} \ge 2.7 V$                          | _   | 20  | 25    | ns    |  |  |  |

| t <sub>CLK_OUT</sub>   | Propagation delay for clock in to data out, see Figure 11-63. | Worst-case placement, routing, and<br>pin selection | _   | -   | 55    | ns    |  |  |  |

Note 58. Rise/fall time matching (TR) not guaranteed, see USB Driver AC Specifications on page 86.

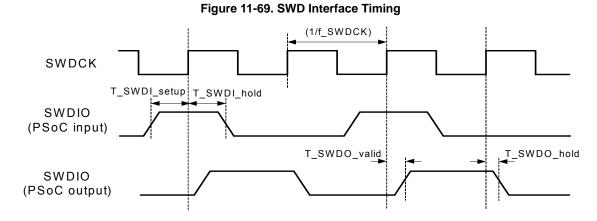

#### 11.8.5 SWD Interface

## Table 11-71. SWD Interface AC Specifications<sup>[71]</sup>

| Parameter    | Description                         | Conditions                                                  | Min | Тур | Max                 | Units |

|--------------|-------------------------------------|-------------------------------------------------------------|-----|-----|---------------------|-------|

| f_SWDCK      | SWDCLK frequency                    | $3.3~V \le V_{DDD} \le 5~V$                                 | -   | _   | 14 <sup>[72]</sup>  | MHz   |

|              |                                     | $1.71 \text{ V} \le \text{V}_{\text{DDD}} < 3.3 \text{ V}$  | _   | -   | 7 <sup>[72]</sup>   | MHz   |

|              |                                     | 1.71 V $\leq$ V <sub>DDD</sub> < 3.3 V, SWD over USBIO pins | _   | -   | 5.5 <sup>[72]</sup> | MHz   |

| T_SWDI_setup | SWDIO input setup before SWDCK high | T = 1/f_SWDCK max                                           | T/4 | _   | -                   | -     |

| T_SWDI_hold  | SWDIO input hold after SWDCK high   | T = 1/f_SWDCK max                                           | T/4 | _   | -                   | -     |

| T_SWDO_valid | SWDCK high to SWDIO output          | T = 1/f_SWDCK max                                           | 1   | I   | 2T/5                | _     |

## 11.8.6 SWV Interface

## Table 11-72. SWV Interface AC Specifications<sup>[71]</sup>

| Parameter | Description           | Conditions | Min | Тур | Max | Units |

|-----------|-----------------------|------------|-----|-----|-----|-------|

|           | SWV mode SWV bit rate |            | _   | _   | 33  | Mbit  |

71. Based on device characterization (Not production tested).

72. ff\_SWDCK must also be no more than 1/3 CPU clock frequency.

# **12. Ordering Information**

In addition to the features listed in Table 12-1, every CY8C34 device includes: a precision on-chip voltage reference, precision oscillators, flash, ECC, DMA, a fixed function I<sup>2</sup>C, 4 KB trace RAM, JTAG/SWD programming and debug, external memory interface, and more. In addition to these features, the flexible UDBs and analog subsection support a wide range of peripherals. To assist you in selecting the ideal part, PSoC Creator makes a part recommendation after you choose the components required by your application. All CY8C34 derivatives incorporate device and flash security in user-selectable security levels; see the TRM for details.

| Table 12-1. | CY8C34 | Family with | Single C | vcle 8051 |

|-------------|--------|-------------|----------|-----------|

|             | 010004 | i anny with |          |           |

|                 | MCU Core        |            |           |             | Analog            |                |     |            |                                        |        |     | Digital  |                      |                  |        | <b>I/O</b> <sup>[81]</sup> |           |      |     |       |              |                         |

|-----------------|-----------------|------------|-----------|-------------|-------------------|----------------|-----|------------|----------------------------------------|--------|-----|----------|----------------------|------------------|--------|----------------------------|-----------|------|-----|-------|--------------|-------------------------|

| Part Number     | CPU Speed (MHz) | Flash (KB) | SRAM (KB) | EEPROM (KB) | LCD Segment Drive | ADC            | DAC | Comparator | SC/CT<br>Analog Blocks <sup>[79]</sup> | Opamps | DFB | CapSense | UDBs <sup>[80]</sup> | 16-bit Timer/PWM | FS USB | CAN 2.0b                   | Total I/O | GPIO | SIO | USBIO | Package      | JTAG ID <sup>[82]</sup> |

| 16 KB Flash     |                 |            |           |             |                   |                |     |            |                                        |        |     |          |                      |                  |        |                            |           |      |     |       |              |                         |

| CY8C3444LTI-110 | 50              | 16         | 2         | 0.5         | ~                 | 12-bit Del-Sig | 2   | 4          | 2                                      | 2      | -   | ~        | 16                   | 4                | -      | -                          | 46        | 38   | 8   | 0     | 68-pin QFN   | 0×1E06E069              |

| CY8C3444LTI-119 | 50              | 16         | 2         | 0.5         | ~                 | 12-bit Del-Sig | 2   | 4          | 2                                      | 2      | -   | ~        | 16                   | 4                | -      | -                          | 29        | 25   | 4   | 0     | 48-pin QFN   | 0×1E077069              |

| CY8C3444PVI-100 | 50              | 16         | 2         | 0.5         | 2                 | 12-bit Del-Sig | 2   | 4          | 2                                      | 2      | -   | ~        | 16                   | 4                | -      | -                          | 29        | 25   | 4   | 0     | 48-pin SSOP  | 0×1E064069              |

| 32 KB Flash     |                 |            |           |             |                   |                |     |            |                                        |        |     |          |                      |                  |        |                            |           |      |     |       |              |                         |

| CY8C3445AXI-104 | 50              | 32         | 4         | 1           | ~                 | 12-bit Del-Sig | 2   | 4          | 2                                      | 2      | -   | ~        | 20                   | 4                | -      | -                          | 70        | 62   | 8   | 0     | 100-pin TQFP | 0×1E068069              |

| CY8C3445LTI-079 | 50              | 32         | 4         | 1           | ~                 | 12-bit Del-Sig | 2   | 4          | 2                                      | 2      | -   | ~        | 20                   | 4                | -      | -                          | 46        | 38   | 8   | 0     | 68-pin QFN   | 0×1E04F069              |

| CY8C3445LTI-078 | 50              | 32         | 4         | 1           | ~                 | 12-bit Del-Sig | 2   | 4          | 2                                      | 2      | -   | ~        | 20                   | 4                | -      | -                          | 29        | 25   | 4   | 0     | 48-pin QFN   | 0×1E04E069              |

| CY8C3445PVI-094 | 50              | 32         | 4         | 1           | 2                 | 12-bit Del-Sig | 2   | 4          | 2                                      | 2      | -   | >        | 20                   | 4                | -      | -                          | 29        | 25   | 4   | 0     | 48-pin SSOP  | 0×1E05E069              |

| CY8C3445AXI-108 | 50              | 32         | 4         | 1           | >                 | 12-bit Del-Sig | 2   | 4          | 2                                      | 2      | -   | >        | 20                   | 4                | ~      | -                          | 72        | 62   | 8   | 2     | 100-pin TQFP | 0×1E06C069              |

| CY8C3445LTI-081 | 50              | 32         | 4         | 1           | >                 | 12-bit Del-Sig | 2   | 4          | 2                                      | 2      | -   | >        | 20                   | 4                | ~      | -                          | 48        | 38   | 8   | 2     | 68-pin QFN   | 0×1E051069              |

| CY8C3445PVI-090 | 50              | 32         | 4         | 1           | >                 | 12-bit Del-Sig | 2   | 4          | 2                                      | 2      | -   | >        | 20                   | 4                | ~      | -                          | 31        | 25   | 4   | 2     | 48-pin SSOP  | 0×1E05A069              |

| 64 KB Flash     |                 |            |           |             |                   |                |     |            |                                        |        |     |          |                      |                  |        |                            |           |      |     |       |              |                         |

| CY8C3446LTI-073 | 50              | 64         | 8         | 2           | >                 | 12-bit Del-Sig | 2   | 4          | 2                                      | 2      | -   | >        | 24                   | 4                | ~      | -                          | 31        | 25   | 4   | 2     | 48-pin QFN   | 0×1E049069              |

| CY8C3446LTI-074 | 50              | 64         | 8         | 2           | 2                 | 12-bit Del-Sig | 2   | 4          | 2                                      | 2      | -   | >        | 24                   | 4                | -      | -                          | 46        | 38   | 8   | 0     | 68-pin QFN   | 0×1E04A069              |

| CY8C3446LTI-083 | 50              | 64         | 8         | 2           | >                 | 12-bit Del-Sig | 2   | 4          | 2                                      | 2      | -   | 5        | 24                   | 4                | -      | 1                          | 29        | 25   | 4   | 0     | 48-pin QFN   | 0x1E053069              |

| CY8C3446AXI-099 | 50              | 64         | 8         | 2           | >                 | 12-bit Del-Sig | 2   | 4          | 2                                      | 2      | -   | 5        | 24                   | 4                | ~      | -                          | 72        | 62   | 8   | 2     | 100-pin TQFP | 0×1E063069              |

| CY8C3446AXI-105 | 50              | 64         | 8         | 2           | >                 | 12-bit Del-Sig | 2   | 4          | 2                                      | 2      | -   | 5        | 24                   | 4                | -      | -                          | 70        | 62   | 8   | 0     | 100-pin TQFP | 0x1E069069              |

| CY8C3446LTI-085 | 50              | 64         | 8         | 2           | ~                 | 12-bit Del-Sig | 2   | 4          | 2                                      | 2      | -   | ~        | 24                   | 4                | ~      | -                          | 48        | 38   | 8   | 2     | 68-pin QFN   | 0×1E055069              |

| CY8C3446PVI-076 | 50              | 64         | 8         | 2           | ~                 | 12-bit Del-Sig | 2   | 4          | 2                                      | 2      | -   | ~        | 24                   | 4                | ~      | -                          | 31        | 25   | 4   | 2     | 48-pin SSOP  | 0×1E04C069              |

| CY8C3446PVI-102 | 50              | 64         | 8         | 2           | ~                 | 12-bit Del-Sig | 2   | 4          | 2                                      | 2      | -   | ~        | 24                   | 4                | -      | ~                          | 29        | 25   | 4   | 0     | 48-pin SSOP  | 0x1E066069              |

Notes

79. Analog blocks support a wide variety of functionality including TIA, PGA, and mixers. See the Example Peripherals on page 43 for more information on how analog blocks can be used.

80. UDBs support a wide variety of functionality including SPI, LIN, UART, timer, counter, PWM, PRS, and others. Individual functions may use a fraction of a UDB or multiple UDBs. Multiple functions can share a single UDB. See the Example Peripherals on page 43 for more information on how UDBs can be used.

81. The I/O Count includes all types of digital I/O: GPIO, SIO, and the two USB I/O. See the I/O System and Routing on page 36 for details on the functionality of each of these types of I/O.

82. The JTAG ID has three major fields. The most significant nibble (left digit) is the version, followed by a 2 byte part number and a 3 nibble manufacturer ID.

## Table 14-1. Acronyms Used in this Document (continued)

| Acronym           | Description                                                  |  |  |  |  |  |  |  |

|-------------------|--------------------------------------------------------------|--|--|--|--|--|--|--|

| PHUB              | peripheral hub                                               |  |  |  |  |  |  |  |

| PHY               | physical layer                                               |  |  |  |  |  |  |  |

| PICU              | port interrupt control unit                                  |  |  |  |  |  |  |  |

| PLA               | programmable logic array                                     |  |  |  |  |  |  |  |

| PLD               | programmable logic device, see also PAL                      |  |  |  |  |  |  |  |

| PLL               | phase-locked loop                                            |  |  |  |  |  |  |  |

| PMDD              | package material declaration data sheet                      |  |  |  |  |  |  |  |

| POR               | power-on reset                                               |  |  |  |  |  |  |  |

| PRES              | precise low-voltage reset                                    |  |  |  |  |  |  |  |

| PRS               | pseudo random sequence                                       |  |  |  |  |  |  |  |

| PS                | port read data register                                      |  |  |  |  |  |  |  |

| PSoC <sup>®</sup> | Programmable System-on-Chip™                                 |  |  |  |  |  |  |  |

| PSRR              | power supply rejection ratio                                 |  |  |  |  |  |  |  |

| PWM               | pulse-width modulator                                        |  |  |  |  |  |  |  |

| RAM               | random-access memory                                         |  |  |  |  |  |  |  |

| RISC              | reduced-instruction-set computing                            |  |  |  |  |  |  |  |

| RMS               | root-mean-square                                             |  |  |  |  |  |  |  |

| RTC               | real-time clock                                              |  |  |  |  |  |  |  |

| RTL               | register transfer language                                   |  |  |  |  |  |  |  |

| RTR               | remote transmission request                                  |  |  |  |  |  |  |  |

| RX                | receive                                                      |  |  |  |  |  |  |  |

| SAR               | successive approximation register                            |  |  |  |  |  |  |  |

| SC/CT             | switched capacitor/continuous time                           |  |  |  |  |  |  |  |

| SCL               | I <sup>2</sup> C serial clock                                |  |  |  |  |  |  |  |

| SDA               | I <sup>2</sup> C serial data                                 |  |  |  |  |  |  |  |

| S/H               | sample and hold                                              |  |  |  |  |  |  |  |

| SINAD             | signal to noise and distortion ratio                         |  |  |  |  |  |  |  |

| SIO               | special input/output, GPIO with advanced features. See GPIO. |  |  |  |  |  |  |  |

| SOC               | start of conversion                                          |  |  |  |  |  |  |  |

## Table 14-1. Acronyms Used in this Document (continued)

| Acronym | Description                                                               |  |  |  |  |  |  |  |

|---------|---------------------------------------------------------------------------|--|--|--|--|--|--|--|

| SOF     | start of frame                                                            |  |  |  |  |  |  |  |

| SPI     | Serial Peripheral Interface, a communications protocol                    |  |  |  |  |  |  |  |

| SR      | slew rate                                                                 |  |  |  |  |  |  |  |

| SRAM    | static random access memory                                               |  |  |  |  |  |  |  |

| SRES    | software reset                                                            |  |  |  |  |  |  |  |

| SWD     | serial wire debug, a test protocol                                        |  |  |  |  |  |  |  |

| SWV     | single-wire viewer                                                        |  |  |  |  |  |  |  |

| TD      | transaction descriptor, see also DMA                                      |  |  |  |  |  |  |  |

| THD     | total harmonic distortion                                                 |  |  |  |  |  |  |  |

| TIA     | transimpedance amplifier                                                  |  |  |  |  |  |  |  |

| TRM     | technical reference manual                                                |  |  |  |  |  |  |  |

| TTL     | transistor-transistor logic                                               |  |  |  |  |  |  |  |

| TX      | transmit                                                                  |  |  |  |  |  |  |  |

| UART    | Universal Asynchronous Transmitter Receiver, a<br>communications protocol |  |  |  |  |  |  |  |

| UDB     | universal digital block                                                   |  |  |  |  |  |  |  |

| USB     | Universal Serial Bus                                                      |  |  |  |  |  |  |  |

| USBIO   | USB input/output, PSoC pins used to connect to a USB port                 |  |  |  |  |  |  |  |

| VDAC    | voltage DAC, see also DAC, IDAC                                           |  |  |  |  |  |  |  |

| WDT     | watchdog timer                                                            |  |  |  |  |  |  |  |

| WOL     | write once latch, see also NVL                                            |  |  |  |  |  |  |  |

| WRES    | watchdog timer reset                                                      |  |  |  |  |  |  |  |

| XRES    | external reset I/O pin                                                    |  |  |  |  |  |  |  |

| XTAL    | crystal                                                                   |  |  |  |  |  |  |  |

# **15. Reference Documents**

PSoC® 3, PSoC® 5 Architecture TRM PSoC® 3 Registers TRM

| Description Title: PSoC <sup>®</sup> 3: CY8C34 Family Datasheet Programmable System-on-Chip (PSoC <sup>®</sup> ) (continued) Document Number: 001-53304 |         |                    |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Revision                                                                                                                                                | ECN     | Submission<br>Date | Orig. of<br>Change | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| *J                                                                                                                                                      | 3179219 | 02/22/2011         | MKEA               | Updated conditions for flash data retention time.<br>Updated 100-pin TQFP package spec.<br>Updated EEPROM AC specifications.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| *К                                                                                                                                                      | 3200146 | 03/28/2011         | MKEA               | Removed Preliminary status from the data sheet.<br>Updated JTAG ID<br>Deleted Cin_G1, ADC input capacitance from Delta-Sigma ADC DC spec table<br>Updated JTAG Interface AC Specifications and SWD Interface Specifications<br>tables<br>Updated USBIO DC specs<br>Added 0.01 to max speed<br>Updated Features on page 1<br>Added Section 5.5, Nonvolatile Latches<br>Updated Flash AC specs<br>Added CAN DC specs<br>Updated delta-sigma graphs, noise histogram figures and RMS Noise spec tables<br>Add reference to application note AN58304 in section 8.1<br>Updated 100-pin TQFP package spec<br>Added oscillator, I/O, VDAC, regulator graphs<br>Updated GPIO and SIO AC specs<br>Updated PIOR with Brown Out AC spec table<br>Updated IDAC graphs<br>Added DMA timing diagram, interrupt timing and interrupt vector, I2C timing<br>diagrams<br>Updated opamp graphs and PGA graphs<br>Added full chip performance graphs<br>Changed MHzECO range.<br>Added "Solder Reflow Peak Temperature" table. |  |  |  |  |

| *L                                                                                                                                                      | 3259185 | 05/17/2011         | MKEA               | Added JTAG and SWD interface connection diagrams<br>Updated $T_{JA}$ and $T_{JC}$ values in Table 13-1<br>Changed typ and max values for the TCVos parameter in Opamp DC<br>specifications table.<br>Updated Clocking subsystem diagram.<br>Changed VSSD to VSSB in the PSoC Power System diagram<br>Updated Ordering information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| Description Document | Description Title: PSoC <sup>®</sup> 3: CY8C34 Family Datasheet Programmable System-on-Chip (PSoC <sup>®</sup> ) (continued) Document Number: 001-53304 |                    |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Revision             | ECN                                                                                                                                                     | Submission<br>Date | Orig. of<br>Change | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| *V                   | 4708125                                                                                                                                                 | 03/31/2015         | MKEA               | Added INL4 and DNL4 specs in VDAC DC Specifications.<br>Updated Figure 6-11.<br>Added second note after Figure 6-4.<br>Added a reference to Fig 6-1 in Section 6.1.1 and Section 6.1.2.<br>Updated Section 6.2.2.<br>Added Section 7.8.1.<br>Updated Boost specifications.                                                                                                                                                                                                    |  |  |  |  |  |  |

| *W                   | 4807497                                                                                                                                                 | 06/23/2015         | MKEA               | Added reference to code examples in More Information.<br>Updated typ value of TWRITE from 2 to 10 in EEPROM AC specs table.<br>Changed "Device supply for USB operation" to "Device supply (VDDD) for USB<br>operation" in USB DC Specifications.<br>Clarified power supply sequencing and margin for VDDA and VDDD.<br>Updated Serial Wire Debug Interface with limitations of debugging on Port 15.<br>Updated Section 11.7.5.<br>Updated Delta-sigma ADC DC Specifications |  |  |  |  |  |  |

| *X                   | 4932879                                                                                                                                                 | 09/24/2015         | MKEA               | Changed the Regulator Output Capacitor min and max from "-" to 0.9 and 1.1,<br>respectively.<br>Added reference to AN54439 in Section 11.9.3.<br>Added MHz ECO DC specs table.<br>Removed references to IPOR rearm issues in Section 6.3.1.1.<br>Table 6-1: Changed DSI Fmax to 33 MHz.<br>Figure 6-1: Changed External I/O or DSI to 0-33 MHz.<br>Table 11-10: Changed Fgpioin Max to 33 MHz.<br>Table 11-12: Changed Fsioin Max to 33 MHz.                                  |  |  |  |  |  |  |

| *Y                   | 5322536                                                                                                                                                 | 06/27/2016         | MKEA               | Updated More Information.<br>Corrected typos in External Electrical Connections.<br>Added links to CAD Libraries in Section 2.                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |