#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | 8051                                                                       |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 50MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART                         |

| Peripherals                | CapSense, DMA, LCD, POR, PWM, WDT                                          |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 16KB (16K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 512 x 8                                                                    |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                               |

| Data Converters            | A/D 16x12b; D/A 2x8b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 48-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 48-QFN (7x7)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c3444lti-119 |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

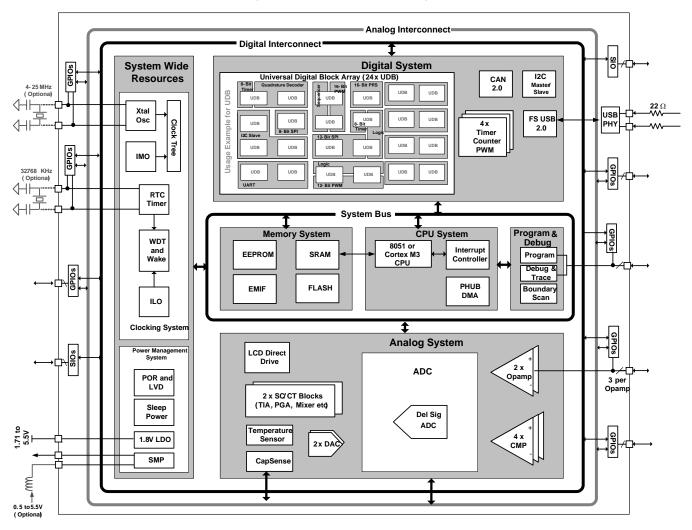

# 1. Architectural Overview

Introducing the CY8C34 family of ultra low-power, flash Programmable System-on-Chip (PSoC<sup>®</sup>) devices, part of a scalable 8-bit PSoC 3 and 32-bit PSoC 5 platform. The CY8C34 family provides configurable blocks of analog, digital, and interconnect circuitry around a CPU subsystem. The combination of a CPU with a flexible analog subsystem, digital subsystem, routing, and I/O enables a high level of integration in a wide variety of consumer, industrial, and medical applications.

Figure 1-1. Simplified Block Diagram

Figure 1-1 illustrates the major components of the CY8C34 family. They are:

- 8051 CPU subsystem

- Nonvolatile subsystem

- Programming, debug, and test subsystem

- Inputs and outputs

- Clocking

- Power

- Digital subsystem

#### Analog subsystem

PSoC's digital subsystem provides half of its unique configurability. It connects a digital signal from any peripheral to any pin through the digital system interconnect (DSI). It also provides functional flexibility through an array of small, fast, lowpower UDBs. PSoC Creator provides a library of prebuilt and tested standard digital peripherals (UART, SPI, LIN, PRS, CRC, timer, counter, PWM, AND, OR, and so on) that are mapped to the UDB array. You can also easily create a digital circuit using boolean primitives by means of graphical design entry. Each UDB contains programmable array logic (PAL)/PLD functionality, together with a small state machine engine to support a wide variety of peripherals.

In addition to the flexibility of the UDB array, PSoC also provides configurable digital blocks targeted at specific functions. For the CY8C34 family these blocks can include four 16-bit timer, counter, and PWM blocks; I<sup>2</sup>C slave, master, and multi-master; Full-Speed USB; and Full CAN 2.0b.

For more details on the peripherals see the "Example Peripherals" section on page 43 of this data sheet. For information on UDBs, DSI, and other digital blocks, see the "Digital Subsystem" section on page 43 of this data sheet.

PSoC's analog subsystem is the second half of its unique configurability. All analog performance is based on a highly accurate absolute voltage reference with less than 1-percent error over temperature and voltage. The configurable analog subsystem includes:

- Analog muxes

- Comparators

- Voltage references

- Analog-to-digital converter (ADC)

- Digital-to-analog converters (DACs)

All GPIO pins can route analog signals into and out of the device using the internal analog bus. This allows the device to interface up to 62 discrete analog signals. The heart of the analog subsystem is a fast, accurate, configurable delta-sigma ADC with these features:

- Less than 100 µV offset

- A gain error of 0.2 percent

- INL less than ±1 LSB

- DNL less than ±1 LSB

- SINAD better than 66 dB

This converter addresses a wide variety of precision analog applications, including some of the most demanding sensors.

Two high-speed voltage or current DACs support 8-bit output signals at update rate of 8 Msps in current DAC (IDAC) and 1 Msps in voltage DAC (VDAC). They can be routed out of any GPIO pin. You can create higher resolution voltage PWM DAC outputs using the UDB array. This can be used to create a pulse width modulated (PWM) DAC of up to 10 bits, at up to 48 kHz. The digital DACs in each UDB support PWM, PRS, or delta-sigma algorithms with programmable widths.

In addition to the ADC and DACs, the analog subsystem provides multiple:

- Uncommitted opamps

- Configurable switched capacitor/continuous time (SC/CT) blocks. These support:

- Transimpedance amplifiers

- Programmable gain amplifiers

- Mixers

#### Other similar analog components

See the "Analog Subsystem" section on page 56 of this data sheet for more details.

PSoC's 8051 CPU subsystem is built around a single cycle pipelined 8051 8-bit processor running at up to 50 MHz. The CPU subsystem includes a programmable nested vector interrupt controller, DMA controller, and RAM. PSoC's nested vector interrupt controller provides low latency by allowing the CPU to vector directly to the first address of the interrupt service routine, bypassing the jump instruction required by other architectures. The DMA controller enables peripherals to exchange data without CPU involvement. This allows the CPU to run slower (saving power) or use those CPU cycles to improve the performance of firmware algorithms. The single cycle 8051 CPU runs ten times faster than a standard 8051 processor. The processor speed itself is configurable, allowing you to tune active power consumption for specific applications.

PSoC's nonvolatile subsystem consists of flash, byte-writeable EEPROM, and nonvolatile configuration options. It provides up to 64 KB of on-chip flash. The CPU can reprogram individual blocks of flash, enabling bootloaders. You can enable an error correcting code (ECC) for high reliability applications. A powerful and flexible protection model secures the user's sensitive information, allowing selective memory block locking for read and write protection. Up to 2 KB of byte-writeable EEPROM is available on-chip to store application data. Additionally, selected configuration options such as boot speed and pin drive mode are stored in nonvolatile memory. This allows settings to activate immediately after power-on reset (POR).

The three types of PSoC I/O are extremely flexible. All I/Os have many drive modes that are set at POR. PSoC also provides up to four I/O voltage domains through the VDDIO pins. Every GPIO has analog I/O, LCD drive<sup>[3]</sup>, CapSense<sup>[4]</sup>, flexible interrupt generation, slew rate control, and digital I/O capability. The SIOs on PSoC allow VOH to be set independently of VDDIO when used as outputs. When SIOs are in input mode they are high impedance. This is true even when the device is not powered or when the pin voltage goes above the supply voltage. This makes the SIO ideally suited for use on an I<sup>2</sup>C bus where the PSoC may not be powered when other devices on the bus are. The SIO pins also have high current sink capability for applications such as LED drives. The programmable input threshold feature of the SIO can be used to make the SIO function as a general purpose analog comparator. For devices with Full-Speed USB the USB physical interface is also provided (USBIO). When not using USB these pins may also be used for limited digital functionality and device programming. All of the features of the PSoC I/Os are covered in detail in the "I/O System and Routing" section on page 36 of this data sheet.

The PSoC device incorporates flexible internal clock generators, designed for high stability and factory trimmed for high accuracy. The Internal Main Oscillator (IMO) is the clock base for the system, and has 2-percent accuracy at 3 MHz. The IMO can be configured to run from 3 MHz up to 24 MHz. Multiple clock derivatives can be generated from the main clock frequency to meet application needs.

#### Notes

<sup>3.</sup> This feature on select devices only. See Ordering Information on page 121 for details.

<sup>4.</sup> GPIOs with opamp outputs are not recommended for use with CapSense.

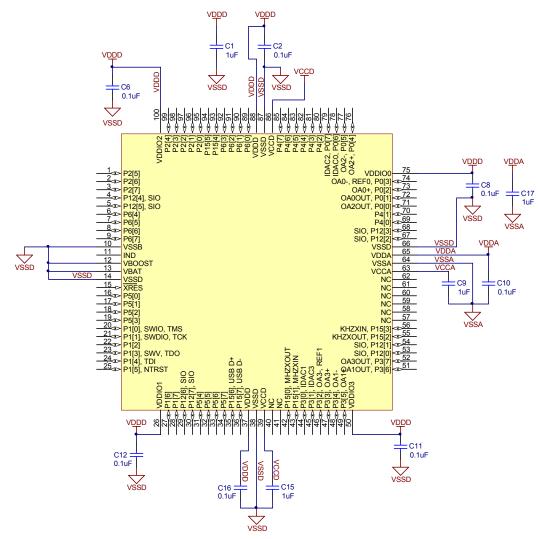

#### Figure 2-3. 48-pin SSOP Part Pinout

#### Notes

- 5. Pins are Do Not Use (DNU) on devices without USB. The pin must be left floating.

- 6. Pins are Do Not Use (DNU) on devices without USB. The pin must be left floating.

- The center pad on the QFN package should be connected to digital ground (VSSD) for best mechanical, thermal, and electrical performance. If not connected to ground, it should be electrically floated and not connected to any other signal. For more information, see AN72845, Design Guidelines for QFN Devices.

Figure 2-7 and Figure 2-8 on page 11 show an example schematic and an example PCB layout, for the 100-pin TQFP part, for optimal analog performance on a two-layer board.

- The two pins labeled VDDD must be connected together.

- The two pins labeled VCCD must be connected together, with capacitance added, as shown in Figure 2-7 and Power System on page 30. The trace between the two VCCD pins should be as short as possible.

- The two pins labeled VSSD must be connected together.

For information on circuit board layout issues for mixed signals, refer to the application note AN57821 - Mixed Signal Circuit Board Layout Considerations for PSoC® 3 and PSoC 5.

#### Figure 2-7. Example Schematic for 100-pin TQFP Part With Power Connections

**Note** The two VCCD pins must be connected together with as short a trace as possible. A trace under the device is recommended, as shown in Figure 2-8 on page 11.

For more information on pad layout, refer to http://www.cypress.com/cad-resources/psoc-3-cad-libraries.

## Table 4-8. Interrupt Vector Table

| #  | Fixed Function            | DMA               | UDB          |

|----|---------------------------|-------------------|--------------|

| 0  | LVD                       | phub_termout0[0]  | udb_intr[0]  |

| 1  | Cache/ECC                 | phub_termout0[1]  | udb_intr[1]  |

| 2  | Reserved                  | phub_termout0[2]  | udb_intr[2]  |

| 3  | Sleep (Pwr Mgr)           | phub_termout0[3]  | udb_intr[3]  |

| 4  | PICU[0]                   | phub_termout0[4]  | udb_intr[4]  |

| 5  | PICU[1]                   | phub_termout0[5]  | udb_intr[5]  |

| 6  | PICU[2]                   | phub_termout0[6]  | udb_intr[6]  |

| 7  | PICU[3]                   | phub_termout0[7]  | udb_intr[7]  |

| 8  | PICU[4]                   | phub_termout0[8]  | udb_intr[8]  |

| 9  | PICU[5]                   | phub_termout0[9]  | udb_intr[9]  |

| 10 | PICU[6]                   | phub_termout0[10] | udb_intr[10] |

| 11 | PICU[12]                  | phub_termout0[11] | udb_intr[11] |

| 12 | PICU[15]                  | phub_termout0[12] | udb_intr[12] |

| 13 | Comparators<br>Combined   | phub_termout0[13] | udb_intr[13] |

| 14 | Switched Caps<br>Combined | phub_termout0[14] | udb_intr[14] |

| 15 | l <sup>2</sup> C          | phub_termout0[15] | udb_intr[15] |

| 16 | CAN                       | phub_termout1[0]  | udb_intr[16] |

| 17 | Timer/Counter0            | phub_termout1[1]  | udb_intr[17] |

| 18 | Timer/Counter1            | phub_termout1[2]  | udb_intr[18] |

| 19 | Timer/Counter2            | phub_termout1[3]  | udb_intr[19] |

| 20 | Timer/Counter3            | phub_termout1[4]  | udb_intr[20] |

| 21 | USB SOF Int               | phub_termout1[5]  | udb_intr[21] |

| 22 | USB Arb Int               | phub_termout1[6]  | udb_intr[22] |

| 23 | USB Bus Int               | phub_termout1[7]  | udb_intr[23] |

| 24 | USB Endpoint[0]           | phub_termout1[8]  | udb_intr[24] |

| 25 | USB Endpoint Data         | phub_termout1[9]  | udb_intr[25] |

| 26 | Reserved                  | phub_termout1[10] | udb_intr[26] |

| 27 | LCD                       | phub_termout1[11] | udb_intr[27] |

| 28 | Reserved                  | phub_termout1[12] | udb_intr[28] |

| 29 | Decimator Int             | phub_termout1[13] | udb_intr[29] |

| 30 | PHUB Error Int            | phub_termout1[14] | udb_intr[30] |

| 31 | EEPROM Fault Int          | phub_termout1[15] | udb_intr[31] |

## 5.5 Nonvolatile Latches (NVLs)

PSoC has a 4-byte array of nonvolatile latches (NVLs) that are used to configure the device at reset. The NVL register map is shown in Table 5-2.

Table 5-2.

Device Configuration NVL Register Map

| Register Address | 7             | 6         | 5            | 4       | 3            | 2     | 1         | 0        |

|------------------|---------------|-----------|--------------|---------|--------------|-------|-----------|----------|

| 0x00             | PRT3RE        | DM[1:0]   | PRT2RDM[1:0] |         | PRT1RDM[1:0] |       | PRT0      | RDM[1:0] |

| 0x01             | PRT12RDM[1:0] |           | PRT6R        | DM[1:0] | PRT5RDM[1:0] |       | PRT4      | RDM[1:0] |

| 0x02             | XRESMEN       | DBGEN     |              |         |              | PRT18 | 5RDM[1:0] |          |

| 0x03             |               | DIG_PHS_I | DLY[3:0]     |         | ECCEN        | DPS   | [1:0]     |          |

The details for individual fields and their factory default settings are shown in Table 5-3:.

#### Table 5-3. Fields and Factory Default Settings

| Field            | Description                                                                                                                                  | Settings                                                                                                                      |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| PRTxRDM[1:0]     | Controls reset drive mode of the corresponding IO port. See "Reset Configuration" on page 42. All pins of the port are set to the same mode. | 00b (default) - high impedance analog<br>01b - high impedance digital<br>10b - resistive pull up<br>11b - resistive pull down |

| XRESMEN          | Controls whether pin P1[2] is used as a GPIO or as<br>an external reset. See "Pin Descriptions" on page 11,<br>XRES description.             | 0 (default for 68-pin 72-pin, and 100-pin parts) - GPIO<br>1 (default for 48-pin parts) - external reset                      |

| DBGEN            | Debug Enable allows access to the debug system, for third-party programmers.                                                                 | 0 - access disabled<br>1 (default) - access enabled                                                                           |

| DPS[1:0]         | Controls the usage of various P1 pins as a debug port.<br>See "Programming, Debug Interfaces, Resources" on<br>page 65.                      |                                                                                                                               |

| ECCEN            | Controls whether ECC flash is used for ECC or for general configuration and data storage. See "Flash Program Memory" on page 22.             | 0 - ECC disabled<br>1 (default) - ECC enabled                                                                                 |

| DIG_PHS_DLY[3:0] | Selects the digital clock phase delay.                                                                                                       | See the TRM for details.                                                                                                      |

Although PSoC Creator provides support for modifying the device configuration NVLs, the number of NVL erase / write cycles is limited – see "Nonvolatile Latches (NVL))" on page 109.

boost typically draws 250  $\mu$ A in active mode and 25  $\mu$ A in standby mode. The boost operating modes must be used in conjunction with chip power modes to minimize total power consumption. Table 6-4 lists the boost power modes available in different chip power modes.

Table 6-4. Chip and Boost Power Modes Compatibility

| Chip Power Modes                     | Boost Power Modes                                                                                                                                                                        |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chip-active or alternate active mode | Boost must be operated in its active mode.                                                                                                                                               |

| Chip-sleep mode                      | Boost can be operated in either active<br>or standby mode. In boost standby<br>mode, the chip must wake up periodi-<br>cally for boost active-mode refresh.                              |

| Chip-hibernate mode                  | Boost can be operated in its active<br>mode. However, it is recommended not<br>to use the boost in chip hibernate mode<br>due to the higher current consumption<br>in boost active mode. |

#### 6.2.2.1 Boost Firmware Requirements

To ensure boost inrush current is within specification at startup, the **Enable Fast IMO During Startup** value must be unchecked in the PSoC Creator IDE. The **Enable Fast IMO During Startup** option is found in PSoC Creator in the design wide resources (cydwr) file **System** tab. Un-checking this option configures the device to run at 12 MHz vs 48 MHz during startup while configuring the device. The slower clock speed results in reduced current draw through the boost circuit.

#### 6.2.2.2 Boost Design Process

Correct operation of the boost converter requires specific component values determined for each designs unique operating conditions. The  $C_{BAT}$  capacitor, Inductor, Schottky diode, and  $C_{BOOST}$  capacitor components are required with the values specified in the electrical specifications, Table 11-7 on page 77. The only variable component value is the inductor  $L_{BOOST}$  which is primarily sized for correct operation of the boost across operating conditions and secondarily for efficiency. Additional operating region constraints exist for  $V_{OUT}$ ,  $V_{BAT}$ ,  $I_{OUT}$ , and  $T_A$ .

The following steps must be followed to determine boost converter operating parameters and  $L_{BOOST}$  value.

- 1. Choose desired  $V_{BAT}\!,\,V_{OUT}\!,\,T_A\!,$  and  $I_{OUT}$  operating condition ranges for the application.

- Determine if V<sub>BAT</sub> and V<sub>OUT</sub> ranges fit the boost operating range based on the T<sub>A</sub> range over V<sub>BAT</sub> and V<sub>OUT</sub> chart, Figure 11-8 on page 77. If the operating ranges are not met,

modify the operating conditions or use an external boost regulator.

- 3. Determine if the desired ambient temperature  $(T_A)$  range fits the ambient temperature operating range based on the  $T_A$ **range over V<sub>BAT</sub> and V<sub>OUT</sub>** chart, Figure 11-8 on page 77. If the temperature range is not met, modify the operating conditions and return to step 2, or use an external boost regulator.

- 4. Determine if the desired output current ( $I_{OUT}$ ) range fits the output current operating range based on the  $I_{OUT}$  range over  $V_{BAT}$  and  $V_{OUT}$  chart, Figure 11-9 on page 77. If the output current range is not met, modify the operating conditions and return to step 2, or use an external boost regulator.

- Find the allowed inductor values based on the L<sub>BOOST</sub> values over V<sub>BAT</sub> and V<sub>OUT</sub> chart, Figure 11-10 on page 77.

- 6. Based on the allowed inductor values, inductor dimensions, inductor cost, boost efficiency, and  $V_{RIPPLE}$  choose the optimum inductor value for the system. Boost efficiency and  $V_{RIPPLE}$  typical values are provided in the **Efficiency vs V<sub>BAT</sub>** and **V<sub>RIPPLE</sub> vs V<sub>BAT</sub>** charts, Figure 11-11 on page 78 through Figure 11-14 on page 78. In general, if high efficiency and low  $V_{RIPPLE}$  are most important, then the highest allowed inductor value should be used. If low inductor cost or small inductor size are most important, then one of the smaller allowed inductor (s) efficiency,  $V_{RIPPLE}$ , cost or dimensions are not acceptable for the application than an external boost regulator should be used.

## 6.3 Reset

CY8C34 has multiple internal and external reset sources available. The reset sources are:

- Power source monitoring The analog and digital power voltages, VDDA, VDDD, VCCA, and VCCD are monitored in several different modes during power up, active mode, and sleep mode (buzzing). If any of the voltages goes outside predetermined ranges then a reset is generated. The monitors are programmable to generate an interrupt to the processor under certain conditions before reaching the reset thresholds.

- External The device can be reset from an external source by pulling the reset pin (XRES) low. The XRES pin includes an internal pull-up to VDDIO1. VDDD, VDDA, and VDDIO1 must all have voltage applied before the part comes out of reset.

- Watchdog timer A watchdog timer monitors the execution of instructions by the processor. If the watchdog timer is not reset by firmware within a certain period of time, the watchdog timer generates a reset.

- Software The device can be reset under program control.

The USBIO pins (P15[7] and P15[6]), when enabled for I/O mode, have limited drive mode control. The drive mode is set using the PRT15.DM0[7, 6] register. A resistive pull option is also available at the USBIO pins, which can be enabled using the PRT15.DM1[7, 6] register. When enabled for USB mode, the drive mode control has no impact on the configuration of the USB pins. Unlike the GPIO and SIO configurations, the port wide configuration registers do not configure the USB drive mode bits. Table 6-7 shows the drive mode configuration for the USBIO pins.

| PRT15.DM1[7,6]<br>Pull up enable | PRT15.DM0[7,6]<br>Drive Mode enable | PRT15.DR[7,6] = 1 | PRT15.DR[7,6] = 0 | Description                   |

|----------------------------------|-------------------------------------|-------------------|-------------------|-------------------------------|

| 0                                | 0                                   | High Z            | Strong Low        | Open Drain, Strong Low        |

| 0                                | 1                                   | Strong High       | Strong Low        | Strong Outputs                |

| 1                                | 0                                   | Res High (5k)     | Strong Low        | Resistive Pull Up, Strong Low |

| 1                                | 1                                   | Strong High       | Strong Low        | Strong Outputs                |

## Table 6-7. USBIO Drive Modes (P15[7] and P15[6])

#### High impedance analog

The default reset state with both the output driver and digital input buffer turned off. This prevents any current from flowing in the I/O's digital input buffer due to a floating voltage. This state is recommended for pins that are floating or that support an analog voltage. High impedance analog pins do not provide digital input functionality.

To achieve the lowest chip current in sleep modes, all I/Os must either be configured to the high impedance analog mode, or have their pins driven to a power supply rail by the PSoC device or by external circuitry.

High impedance digital

The input buffer is enabled for digital signal input. This is the standard high impedance (High Z) state recommended for digital inputs.

Resistive pull-up or resistive pull-down

Resistive pull-up or pull-down, respectively, provides a series resistance in one of the data states and strong drive in the other. Pins can be used for digital input and output in these modes. Interfacing to mechanical switches is a common application for these modes. Resistive pull-up and pull-down are not available with SIO in regulated output mode.

Open drain, drives high and open drain, drives low

Open drain modes provide high impedance in one of the data states and strong drive in the other. Pins can be used for digital input and output in these modes. A common application for these modes is driving the  $I^2C$  bus signal lines.

Strong drive

Provides a strong CMOS output drive in either high or low state. This is the standard output mode for pins. Strong Drive mode pins must not be used as inputs under normal circumstances. This mode is often used to drive digital output signals or external FETs.

Resistive pull-up and pull-down

Similar to the resistive pull-up and resistive pull-down modes except the pin is always in series with a resistor. The high data state is pull-up while the low data state is pull-down. This mode is most often used when other signals that may cause shorts can drive the bus. Resistive pull-up and pull-down are not available with SIO in regulated output mode.

#### 6.4.2 Pin Registers

Registers to configure and interact with pins come in two forms that may be used interchangeably.

All I/O registers are available in the standard port form, where each bit of the register corresponds to one of the port pins. This register form is efficient for quickly reconfiguring multiple port pins at the same time.

I/O registers are also available in pin form, which combines the eight most commonly used port register bits into a single register for each pin. This enables very fast configuration changes to individual pins with a single register write.

#### 6.4.3 Bidirectional Mode

High-speed bidirectional capability allows pins to provide both the high impedance digital drive mode for input signals and a second user selected drive mode such as strong drive (set using PRT×DM[2:0] registers) for output signals on the same pin, based on the state of an auxiliary control bus signal. The bidirectional capability is useful for processor busses and communications interfaces such as the SPI Slave MISO pin that requires dynamic hardware control of the output buffer.

The auxiliary control bus routes up to 16 UDB or digital peripheral generated output enable signals to one or more pins.

#### 6.4.4 Slew Rate Limited Mode

GPIO and SIO pins have fast and slow output slew rate options for strong and open drain drive modes, not resistive drive modes. Because it results in reduced EMI, the slow edge rate option is recommended for signals that are not speed critical, generally less than 1 MHz. The fast slew rate is for signals between 1 MHz and 33 MHz. The slew rate is individually configurable for each pin, and is set by the PRTxSLW registers.

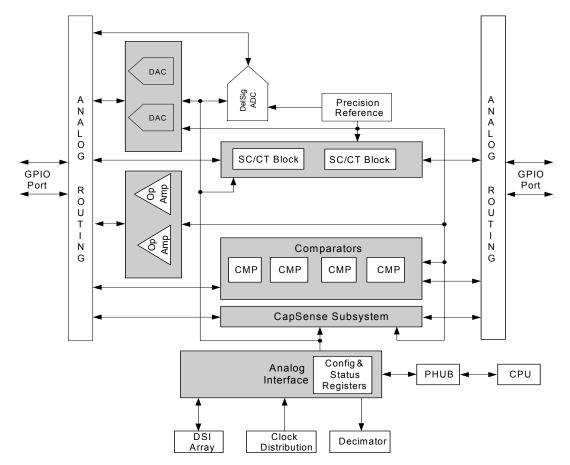

# 8. Analog Subsystem

The analog programmable system creates application specific combinations of both standard and advanced analog signal processing blocks. These blocks are then interconnected to each other and also to any pin on the device, providing a high level of design flexibility and IP security. The features of the analog subsystem are outlined here to provide an overview of capabilities and architecture.

- Flexible, configurable analog routing architecture provided by analog globals, analog mux bus, and analog local buses.

- High resolution Delta-Sigma ADC.

- Two 8-bit DACs that provide either voltage or current output.

- Four comparators with optional connection to configurable LUT outputs.

- Two configurable switched capacitor/continuous time (SC/CT) blocks for functions that include opamp, unity gain buffer, programmable gain amplifier, transimpedance amplifier, and mixer.

- Two opamps for internal use and connection to GPIO that can be used as high current output buffers.

- CapSense subsystem to enable capacitive touch sensing.

- Precision reference for generating an accurate analog voltage for internal analog blocks.

#### Figure 8-1. Analog Subsystem Block Diagram

## 8.7 CapSense

The CapSense system provides a versatile and efficient means for measuring capacitance in applications such as touch sense buttons, sliders, proximity detection, etc. The CapSense system uses a configuration of system resources, including a few hardware functions primarily targeted for CapSense. Specific resource usage is detailed in the CapSense component in PSoC Creator.

A capacitive sensing method using a delta-sigma modulator (CSD) is used. It provides capacitance sensing using a switched capacitor technique with a delta-sigma modulator to convert the sensing current to a digital code.

#### 8.8 Temp Sensor

Die temperature is used to establish programming parameters for writing flash. Die temperature is measured using a dedicated sensor based on a forward biased transistor. The temperature sensor has its own auxiliary ADC.

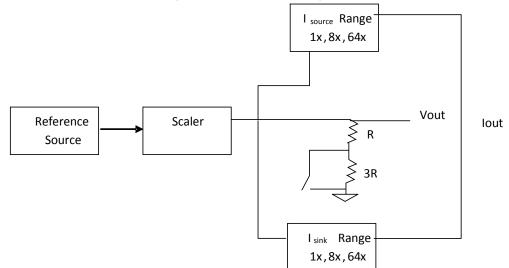

#### 8.9 DAC

The CY8C34 parts contain two Digital to Analog Convertors (DACs). Each DAC is 8-bit and can be configured for either voltage or current output. The DACs support CapSense, power supply regulation, and waveform generation. Each DAC has the following features:

- Adjustable voltage or current output in 255 steps

- Programmable step size (range selection)

- Eight bits of calibration to correct ± 25 percent of gain error

- Source and sink option for current output

- High and low speed / power modes

- 8 Msps conversion rate for current output

- 1 Msps conversion rate for voltage output

- Monotonic in nature

- Data and strobe inputs can be provided by the CPU or DMA, or routed directly from the DSI

- Dedicated low-resistance output pin for high-current mode

#### Figure 8-11. DAC Block Diagram

#### 8.9.1 Current DAC

The current DAC (IDAC) can be configured for the ranges 0 to 31.875  $\mu$ A, 0 to 255  $\mu$ A, and 0 to 2.04 mA. The IDAC can be configured to source or sink current.

#### 8.9.2 Voltage DAC

For the voltage DAC (VDAC), the current DAC output is routed through resistors. The two ranges available for the VDAC are 0 to 1.02 V and 0 to 4.08 V. In voltage mode any load connected to the output of a DAC should be purely capacitive (the output of the VDAC is not buffered).

## 8.10 Up/Down Mixer

In continuous time mode, the SC/CT block components are used to build an up or down mixer. Any mixing application contains an input signal frequency and a local oscillator frequency. The polarity of the clock, Fclk, switches the amplifier between inverting or noninverting gain. The output is the product of the input and the switching function from the local oscillator, with frequency components at the local oscillator plus and minus the signal frequency (Fclk + Fin and Fclk – Fin) and reduced-level frequency components at odd integer multiples of the local oscillator frequency. The local oscillator frequency is provided by the selected clock source for the mixer.

Continuous time up and down mixing works for applications with input signals and local oscillator frequencies up to 1 MHz.

## 11.4.4 XRES

## Table 11-17. XRES DC Specifications

| Parameter       | Description                                                   | Conditions | Min                   | Тур | Max                   | Units |

|-----------------|---------------------------------------------------------------|------------|-----------------------|-----|-----------------------|-------|

| V <sub>IH</sub> | Input voltage high threshold                                  |            | $0.7 \times V_{DDIO}$ | _   | -                     | V     |

| V <sub>IL</sub> | Input voltage low threshold                                   |            | -                     | -   | $0.3 \times V_{DDIO}$ | V     |

| Rpullup         | Pull-up resistor                                              |            | 3.5                   | 5.6 | 8.5                   | kΩ    |

| C <sub>IN</sub> | Input capacitance <sup>[46]</sup>                             |            | -                     | 3   | -                     | pF    |

| V <sub>H</sub>  | Input voltage hysteresis<br>(Schmitt-Trigger) <sup>[46]</sup> |            | -                     | 100 | _                     | mV    |

| Idiode          | Current through protection diode to $V_{DDIO}$ and $V_{SSIO}$ |            | _                     | _   | 100                   | μA    |

## Table 11-18. XRES AC Specifications

| Parameter          | Description       | Conditions | Min | Тур | Max | Units |

|--------------------|-------------------|------------|-----|-----|-----|-------|

| T <sub>RESET</sub> | Reset pulse width |            | 1   | -   | -   | μs    |

<sup>46.</sup> Based on device characterization (Not production tested).

## Table 11-22. Delta-sigma ADC AC Specifications

| Parameter    | Description                                                       | Conditions                                   | Min | Тур | Max    | Units   |

|--------------|-------------------------------------------------------------------|----------------------------------------------|-----|-----|--------|---------|

|              | Startup time                                                      |                                              | -   | -   | 4      | Samples |

| THD          | Total harmonic distortion <sup>[51]</sup>                         | Buffer gain = 1, 12-bit,<br>Range = ±1.024 V | _   | _   | 0.0032 | %       |

| 12-Bit Resol | ution Mode                                                        | •                                            |     |     |        | •       |

| SR12         | Sample rate, continuous, high power <sup>[51]</sup>               | Range = ±1.024 V, unbuffered                 | 4   | -   | 192    | ksps    |

| BW12         | Input bandwidth at max sample rate <sup>[51]</sup>                | Range = ±1.024 V, unbuffered                 | -   | 44  | _      | kHz     |

| SINAD12int   | Signal to noise ratio, 12-bit, internal reference <sup>[51]</sup> | Range = ±1.024 V, unbuffered                 | 66  | -   | -      | dB      |

| 8-Bit Resolu | tion Mode                                                         | •                                            |     |     |        | •       |

| SR8          | Sample rate, continuous, high power <sup>[51]</sup>               | Range = ±1.024 V, unbuffered                 | 8   | -   | 384    | ksps    |

| BW8          | Input bandwidth at max sample rate <sup>[51]</sup>                | Range = ±1.024 V, unbuffered                 | -   | 88  | _      | kHz     |

| SINAD8int    | Signal to noise ratio, 8-bit, internal reference <sup>[51]</sup>  | Range = ±1.024 V, unbuffered                 | 43  | -   | -      | dB      |

#### Table 11-23. Delta-sigma ADC Sample Rates, Range = ±1.024 V

| Resolution, | Conti | nuous  | Multi-Sample |       |  |

|-------------|-------|--------|--------------|-------|--|

| Bits        | Min   | Max    | Min          | Max   |  |

| 8           | 8000  | 384000 | 1911         | 91701 |  |

| 9           | 6400  | 307200 | 1543         | 74024 |  |

| 10          | 5566  | 267130 | 1348         | 64673 |  |

| 11          | 4741  | 227555 | 1154         | 55351 |  |

| 12          | 4000  | 192000 | 978          | 46900 |  |

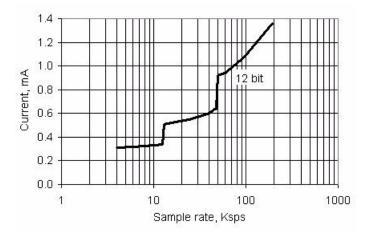

# Figure 11-33. Delta-sigma ADC IDD vs sps, Range = $\pm 1.024$ V, Continuous Sample Mode, Input Buffer Bypassed

#### 11.5.3 Voltage Reference

#### Table 11-24. Voltage Reference Specifications

See also ADC external reference specifications in Section 11.5.2.

| Parameter        | Description                 | Conditions              | Min   | Тур   | Max   | Units |

|------------------|-----------------------------|-------------------------|-------|-------|-------|-------|

| V <sub>REF</sub> | Precision reference voltage | Initial trimming, 25 °C | 1.014 | 1.024 | 1.034 | V     |

|                  |                             |                         | (–1%) |       | (+1%) |       |

#### 11.5.4 Analog Globals

#### Table 11-25. Analog Globals Specifications

| Parameter | Description                                                                        | Conditions             | Min | Тур  | Max  | Units |

|-----------|------------------------------------------------------------------------------------|------------------------|-----|------|------|-------|

| Rppag     | Resistance pin-to-pin through P2[4],<br>AGL0, DSM INP, AGL1, P2[5] <sup>[52]</sup> | V <sub>DDA</sub> = 3 V | _   | 1472 | 2200 | Ω     |

| Rppmuxbus | Resistance pin-to-pin through P2[3], amuxbusL, P2[4] <sup>[52]</sup>               | V <sub>DDA</sub> = 3 V | _   | 706  | 1100 | Ω     |

#### 11.5.5 Comparator

#### Table 11-26. Comparator DC Specifications

| Parameter         | Description                                       | Conditions                                          | Min              | Тур | Max                        | Units |

|-------------------|---------------------------------------------------|-----------------------------------------------------|------------------|-----|----------------------------|-------|

|                   | Input offset voltage in fast mode                 | Factory trim, $V_{DDA}$ > 2.7 V, $V_{IN} \ge 0.5 V$ | -                |     | 10                         | mV    |

|                   | Input offset voltage in slow mode                 | Factory trim, Vin $\ge 0.5 \text{ V}$               | -                |     | 9                          | mV    |

| V <sub>OS</sub>   | Input offset voltage in fast mode <sup>[53]</sup> | Custom trim                                         | -                | -   | 4                          | mV    |

|                   | Input offset voltage in slow mode <sup>[53]</sup> | Custom trim                                         | -                | _   | 4                          | mV    |

|                   | Input offset voltage in ultra<br>low-power mode   | V <sub>DDA</sub> ≤ 4.6 V                            | -                | ±12 | -                          | mV    |

| V <sub>HYST</sub> | Hysteresis                                        | Hysteresis enable mode                              | -                | 10  | 32                         | mV    |

| V <sub>ICM</sub>  | Input common mode voltage                         | High current / fast mode                            | V <sub>SSA</sub> | -   | V <sub>DDA</sub>           | V     |

|                   |                                                   | Low current / slow mode                             | V <sub>SSA</sub> | -   | V <sub>DDA</sub>           | V     |

|                   |                                                   | Ultra low power mode<br>V <sub>DDA</sub> ≤ 4.6 V    | V <sub>SSA</sub> | -   | V <sub>DDA</sub> –<br>1.15 |       |

| CMRR              | Common mode rejection ratio                       |                                                     | -                | 50  | _                          | dB    |

| I <sub>CMP</sub>  | High current mode/fast mode <sup>[54]</sup>       |                                                     | -                | _   | 400                        | μA    |

|                   | Low current mode/slow mode <sup>[54]</sup>        |                                                     | -                | -   | 100                        | μA    |

|                   | Ultra low-power mode <sup>[54]</sup>              | V <sub>DDA</sub> ≤ 4.6 V                            | -                | 6   | _                          | μA    |

#### Table 11-27. Comparator AC Specifications

| Parameter         | Description                                      | Conditions                                                        | Min | Тур | Max | Units |

|-------------------|--------------------------------------------------|-------------------------------------------------------------------|-----|-----|-----|-------|

| T <sub>RESP</sub> | Response time, high current mode <sup>[54]</sup> | 50 mV overdrive, measured<br>pin-to-pin                           | -   | 75  | 110 | ns    |

|                   | Response time, low current mode <sup>[54]</sup>  | 50 mV overdrive, measured pin-to-pin                              | -   | 155 | 200 | ns    |

|                   |                                                  | 50 mV overdrive, measured<br>pin-to-pin, V <sub>DDA</sub> ≤ 4.6 V | -   | 55  | _   | μs    |

#### Notes

53. The recommended procedure for using a custom trim value for the on-chip comparators can be found in the TRM.

54. Based on device characterization (Not production tested).

<sup>52.</sup> The resistance of the analog global and analog mux bus is high if V<sub>DDA</sub> ≤ 2.7 V, and the chip is in either sleep or hibernate mode. Use of analog global and analog mux bus under these conditions is not recommended.

#### 11.5.8 Mixer

The mixer is created using a SC/CT analog block; see the Mixer component data sheet in PSoC Creator for full electrical specifications and APIs.

#### Table 11-32. Mixer DC Specifications

| Parameter       | Description          | Conditions | Min | Тур | Max | Units |

|-----------------|----------------------|------------|-----|-----|-----|-------|

| V <sub>OS</sub> | Input offset voltage |            | -   | -   | 15  | mV    |

|                 | Quiescent current    |            | -   | 0.9 | 2   | mA    |

| G               | Gain                 |            | -   | 0   | -   | dB    |

#### Table 11-33. Mixer AC Specifications

| Parameter       | Description                | Conditions      | Min | Тур | Max | Units |

|-----------------|----------------------------|-----------------|-----|-----|-----|-------|

| f <sub>LO</sub> | Local oscillator frequency | Down mixer mode | -   | -   | 4   | MHz   |

| f <sub>in</sub> | Input signal frequency     | Down mixer mode | -   | -   | 14  | MHz   |

| f <sub>LO</sub> | Local oscillator frequency | Up mixer mode   | -   | -   | 1   | MHz   |

| f <sub>in</sub> | Input signal frequency     | Up mixer mode   | -   | -   | 1   | MHz   |

| SR              | Slew rate                  |                 | 3   | _   | -   | V/µs  |

#### 11.5.9 Transimpedance Amplifier

The TIA is created using a SC/CT analog block; see the TIA component data sheet in PSoC Creator for full electrical specifications and APIs.

#### Table 11-34. Transimpedance Amplifier (TIA) DC Specifications

| Parameter         | Description                           | Conditions           | Min | Тур | Max | Units |

|-------------------|---------------------------------------|----------------------|-----|-----|-----|-------|

| V <sub>IOFF</sub> | Input offset voltage                  |                      | -   | -   | 10  | mV    |

| Rconv             | Conversion resistance <sup>[56]</sup> | R = 20K; 40 pF load  | -25 | -   | +35 | %     |

|                   |                                       | R = 30K; 40 pF load  | -25 | -   | +35 | %     |

|                   |                                       | R = 40K; 40 pF load  | -25 | -   | +35 | %     |

|                   |                                       | R = 80K; 40 pF load  | -25 | -   | +35 | %     |

|                   |                                       | R = 120K; 40 pF load | -25 | -   | +35 | %     |

|                   |                                       | R = 250K; 40 pF load | -25 | -   | +35 | %     |

|                   |                                       | R= 500K; 40 pF load  | -25 | -   | +35 | %     |

|                   |                                       | R = 1M; 40 pF load   | -25 | -   | +35 | %     |

|                   | Quiescent current                     |                      | -   | 1.1 | 2   | mA    |

#### Table 11-35. Transimpedance Amplifier (TIA) AC Specifications

| Parameter | Description             | Conditions            | Min  | Тур | Max | Units |

|-----------|-------------------------|-----------------------|------|-----|-----|-------|

| BW        | Input bandwidth (-3 dB) | R = 20K; –40 pF load  | 1500 | -   | -   | kHz   |

|           |                         |                       |      |     |     |       |

|           |                         | R = 120K; –40 pF load | 240  | -   | -   | kHz   |

|           |                         | R = 1M; –40 pF load   | 25   | -   | -   | kHz   |

Note

<sup>56.</sup> Conversion resistance values are not calibrated. Calibrated values and details about calibration are provided in PSoC Creator component data sheets. External precision resistors can also be used.

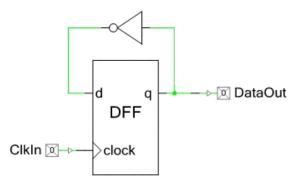

#### Figure 11-63. Clock to Output Performance

#### 11.7 Memory

Specifications are valid for –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C and T<sub>J</sub>  $\leq$  100 °C, except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted.

11.7.1 Flash

#### Table 11-53. Flash DC Specifications

| Parameter | Description               | Conditions           | Min  | Тур | Max | Units |

|-----------|---------------------------|----------------------|------|-----|-----|-------|

|           | Erase and program voltage | V <sub>DDD</sub> pin | 1.71 | -   | 5.5 | V     |

#### Table 11-54. Flash AC Specifications

| Parameter          | Description                                                                | Conditions                                                           | Min | Тур | Max | Units   |

|--------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------|-----|-----|-----|---------|

| T <sub>WRITE</sub> | Row write time (erase + program)                                           |                                                                      | -   | 15  | 20  | ms      |

| T <sub>ERASE</sub> | Row erase time                                                             |                                                                      | -   | 10  | 13  | ms      |

|                    | Row program time                                                           |                                                                      | -   | 5   | 7   | ms      |

| T <sub>BULK</sub>  | Bulk erase time (16 KB to 64 KB)                                           |                                                                      | -   | -   | 35  | ms      |

|                    | Sector erase time (8 KB to 16 KB)                                          |                                                                      | -   | -   | 15  | ms      |

| T <sub>PROG</sub>  | Total device programming time                                              | No overhead <sup>[59]</sup>                                          | -   | 1.5 | 2   | seconds |

|                    | Flash data retention time, retention period measured from last erase cycle | Average ambient temp.<br>$T_A \le 55$ °C, 100 K erase/program cycles | 20  | -   | -   | years   |

|                    |                                                                            | Average ambient temp.<br>$T_A \le 85$ °C, 10 K erase/program cycles  | 10  | -   | _   | years   |

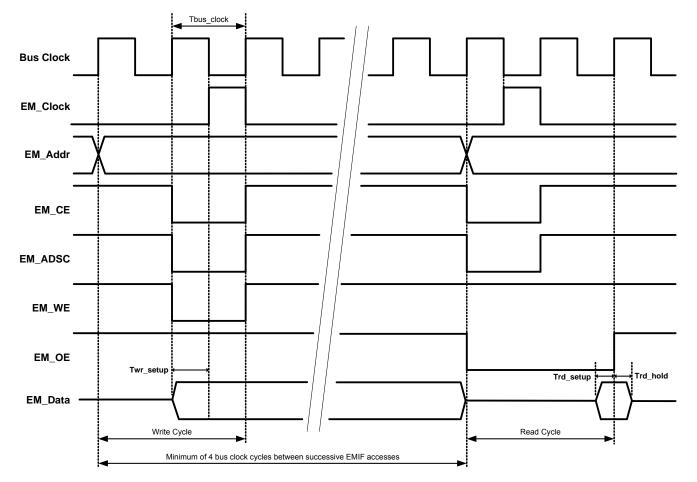

Figure 11-65. Synchronous Write and Read Cycle Timing, No Wait States

| Table 11-62. | Synchronous | Write and Read | Timing Specification | ations <sup>[63]</sup> |

|--------------|-------------|----------------|----------------------|------------------------|

|--------------|-------------|----------------|----------------------|------------------------|

| Parameter  | Description                                                    | Conditions | Min             | Тур | Max | Units |

|------------|----------------------------------------------------------------|------------|-----------------|-----|-----|-------|

| Fbus_clock | Bus clock frequency <sup>[64]</sup>                            |            | -               | -   | 33  | MHz   |

| Tbus_clock | Bus clock period <sup>[65]</sup>                               |            | 30.3            | _   | -   | ns    |

| Twr_Setup  | Time from EM_data valid to rising edge of<br>EM_Clock          |            | Tbus_clock – 10 | _   | -   | ns    |

| Trd_setup  | Time that EM_data must be valid before<br>rising edge of EM_OE |            | 5               | _   | -   | ns    |

| Trd_hold   | Time that EM_data must be valid after rising edge of EM_OE     |            | 5               | _   | -   | ns    |

- 63. Based on device characterization (Not production tested).

64. EMIF signal timings are limited by GPIO frequency limitations. See "GPIO" section on page 79.

65. EMIF output signals are generally synchronized to bus clock, so EMIF signal timings are dependent on bus clock frequency.

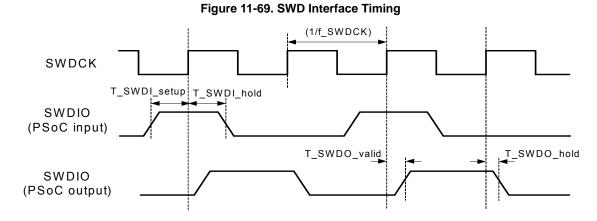

#### 11.8.5 SWD Interface

## Table 11-71. SWD Interface AC Specifications<sup>[71]</sup>

| Parameter    | Description                         | Conditions                                                  | Min | Тур | Max                 | Units |

|--------------|-------------------------------------|-------------------------------------------------------------|-----|-----|---------------------|-------|

| f_SWDCK      | SWDCLK frequency                    | $3.3~V \le V_{DDD} \le 5~V$                                 | _   | _   | 14 <sup>[72]</sup>  | MHz   |

|              |                                     | $1.71 \text{ V} \le \text{V}_{\text{DDD}} < 3.3 \text{ V}$  | _   | -   | 7 <sup>[72]</sup>   | MHz   |

|              |                                     | 1.71 V $\leq$ V <sub>DDD</sub> < 3.3 V, SWD over USBIO pins | _   | -   | 5.5 <sup>[72]</sup> | MHz   |

| T_SWDI_setup | SWDIO input setup before SWDCK high | T = 1/f_SWDCK max                                           | T/4 | _   | -                   | -     |

| T_SWDI_hold  | SWDIO input hold after SWDCK high   | T = 1/f_SWDCK max                                           | T/4 | _   | -                   | -     |

| T_SWDO_valid | SWDCK high to SWDIO output          | T = 1/f_SWDCK max                                           | 1   | I   | 2T/5                | _     |

## 11.8.6 SWV Interface

## Table 11-72. SWV Interface AC Specifications<sup>[71]</sup>

| Parameter | Description           | Conditions | Min | Тур | Max | Units |

|-----------|-----------------------|------------|-----|-----|-----|-------|

|           | SWV mode SWV bit rate |            | _   | _   | 33  | Mbit  |

71. Based on device characterization (Not production tested).

72. ff\_SWDCK must also be no more than 1/3 CPU clock frequency.

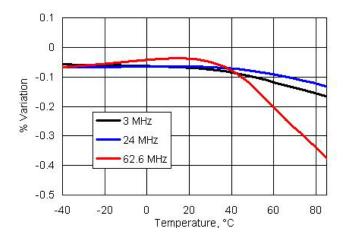

## Figure 11-71. IMO Frequency Variation vs. Temperature

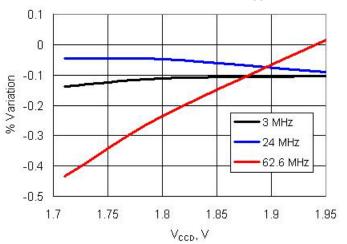

# Figure 11-72. IMO Frequency Variation vs. V<sub>CC</sub>

11.9.2 Internal Low-Speed Oscillator Table 11-75. ILO DC Specifications

| Parameter       | Description                       | Conditions                 | Min | Тур | Max | Units |

|-----------------|-----------------------------------|----------------------------|-----|-----|-----|-------|

|                 | Operating current <sup>[74]</sup> | F <sub>OUT</sub> = 1 kHz   | -   | -   | 1.7 | μA    |

| I <sub>CC</sub> |                                   | F <sub>OUT</sub> = 33 kHz  | -   | -   | 2.6 | μA    |

|                 |                                   | F <sub>OUT</sub> = 100 kHz | _   | -   | 2.6 | μA    |

|                 | Leakage current <sup>[74]</sup>   | Power down mode            | -   | -   | 15  | nA    |

# Table 11-76. ILO AC Specifications

| Parameter        | Description                              | Conditions | Min | Тур | Max | Units |

|------------------|------------------------------------------|------------|-----|-----|-----|-------|

|                  | Startup time, all frequencies Turbo mode |            | -   | -   | 2   | ms    |

| F <sub>ILO</sub> | ILO frequencies                          |            |     |     |     |       |

|                  | 100 kHz                                  |            | 45  | 100 | 200 | kHz   |

|                  | 1 kHz                                    |            | 0.5 | 1   | 2   | kHz   |

#### 11.9.5 External Clock Reference

# Table 11-81. External Clock Reference AC Specifications<sup>[76]</sup>

| Parameter | Description              | Conditions                         | Min | Тур | Max | Units |

|-----------|--------------------------|------------------------------------|-----|-----|-----|-------|

|           | External frequency range |                                    | 0   | -   | 33  | MHz   |

|           | Input duty cycle range   | Measured at V <sub>DDIO</sub> /2   | 30  | 50  | 70  | %     |

|           | Input edge rate          | V <sub>IL</sub> to V <sub>IH</sub> | 0.5 | -   | -   | V/ns  |

11.9.6 Phase-Locked Loop

## Table 11-82. PLL DC Specifications

| Parameter       | Description           | Conditions               | Min | Тур | Max | Units |

|-----------------|-----------------------|--------------------------|-----|-----|-----|-------|

| I <sub>DD</sub> | PLL operating current | In = 3 MHz, Out = 24 MHz | -   | 200 | —   | μA    |

#### Table 11-83. PLL AC Specifications

| Parameter   | Description                                | Conditions          | Min | Тур | Max | Units |

|-------------|--------------------------------------------|---------------------|-----|-----|-----|-------|

| Fpllin      | PLL input frequency <sup>[77]</sup>        |                     | 1   | _   | 48  | MHz   |

|             | PLL intermediate frequency <sup>[78]</sup> | Output of prescaler | 1   | _   | 3   | MHz   |

| Fpllout     | PLL output frequency <sup>[77]</sup>       |                     | 24  | -   | 50  | MHz   |

|             | Lock time at startup                       |                     | -   | -   | 250 | μs    |

| Jperiod-rms | Jitter (rms) <sup>[76]</sup>               |                     | -   | -   | 250 | ps    |

Notes

76. Based on device characterization (Not production tested).

77. This specification is guaranteed by testing the PLL across the specified range using the IMO as the source for the PLL.

78. PLL input divider, Q, must be set so that the input frequency is divided down to the intermediate frequency range. Value for Q ranges from 1 to 16.

#### Table 14-1. Acronyms Used in this Document (continued)

| Acronym           | Description                                                  |

|-------------------|--------------------------------------------------------------|

| PHUB              | peripheral hub                                               |

| PHY               | physical layer                                               |

| PICU              | port interrupt control unit                                  |

| PLA               | programmable logic array                                     |

| PLD               | programmable logic device, see also PAL                      |

| PLL               | phase-locked loop                                            |

| PMDD              | package material declaration data sheet                      |

| POR               | power-on reset                                               |

| PRES              | precise low-voltage reset                                    |

| PRS               | pseudo random sequence                                       |

| PS                | port read data register                                      |

| PSoC <sup>®</sup> | Programmable System-on-Chip™                                 |

| PSRR              | power supply rejection ratio                                 |

| PWM               | pulse-width modulator                                        |

| RAM               | random-access memory                                         |

| RISC              | reduced-instruction-set computing                            |

| RMS               | root-mean-square                                             |

| RTC               | real-time clock                                              |

| RTL               | register transfer language                                   |

| RTR               | remote transmission request                                  |

| RX                | receive                                                      |

| SAR               | successive approximation register                            |

| SC/CT             | switched capacitor/continuous time                           |

| SCL               | I <sup>2</sup> C serial clock                                |

| SDA               | I <sup>2</sup> C serial data                                 |

| S/H               | sample and hold                                              |

| SINAD             | signal to noise and distortion ratio                         |

| SIO               | special input/output, GPIO with advanced features. See GPIO. |

| SOC               | start of conversion                                          |

## Table 14-1. Acronyms Used in this Document (continued)

| Acronym | Description                                                               |

|---------|---------------------------------------------------------------------------|

| SOF     | start of frame                                                            |

| SPI     | Serial Peripheral Interface, a communications protocol                    |

| SR      | slew rate                                                                 |

| SRAM    | static random access memory                                               |

| SRES    | software reset                                                            |

| SWD     | serial wire debug, a test protocol                                        |

| SWV     | single-wire viewer                                                        |

| TD      | transaction descriptor, see also DMA                                      |

| THD     | total harmonic distortion                                                 |

| TIA     | transimpedance amplifier                                                  |

| TRM     | technical reference manual                                                |

| TTL     | transistor-transistor logic                                               |

| TX      | transmit                                                                  |

| UART    | Universal Asynchronous Transmitter Receiver, a<br>communications protocol |

| UDB     | universal digital block                                                   |

| USB     | Universal Serial Bus                                                      |

| USBIO   | USB input/output, PSoC pins used to connect to a USB port                 |

| VDAC    | voltage DAC, see also DAC, IDAC                                           |

| WDT     | watchdog timer                                                            |

| WOL     | write once latch, see also NVL                                            |

| WRES    | watchdog timer reset                                                      |

| XRES    | external reset I/O pin                                                    |

| XTAL    | crystal                                                                   |

# **15. Reference Documents**

PSoC® 3, PSoC® 5 Architecture TRM PSoC® 3 Registers TRM