Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

|                            | Observation                                                                |

| Product Status             | Obsolete                                                                   |

| Core Processor             | 8051                                                                       |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 50MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                    |

| Peripherals                | CapSense, DMA, LCD, POR, PWM, WDT                                          |

| Number of I/O              | 62                                                                         |

| Program Memory Size        | 32KB (32K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 4K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                               |

| Data Converters            | A/D 16x12b; D/A 2x8b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 100-LQFP                                                                   |

| Supplier Device Package    | 100-TQFP (14x14)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c3445axi-108 |

# 4.3.1.2 Logical Instructions

The logical instructions perform Boolean operations such as AND, OR, XOR on bytes, rotate of accumulator contents, and swap of nibbles in an accumulator. The Boolean operations on the bytes are performed on the bit-by-bit basis. Table 4-2 shows the list of logical instructions and their description.

Table 4-2. Logical Instructions

|      | Mnemonic      | Description                           | Bytes | Cycles |

|------|---------------|---------------------------------------|-------|--------|

| ANL  | A,Rn          | AND register to accumulator           | 1     | 1      |

| ANL  | A,Direct      | AND direct byte to accumulator        | 2     | 2      |

| ANL  | A,@Ri         | AND indirect RAM to accumulator       | 1     | 2      |

| ANL  | A,#data       | AND immediate data to accumulator     | 2     | 2      |

| ANL  | Direct, A     | AND accumulator to direct byte        | 2     | 3      |

| ANL  | Direct, #data | AND immediate data to direct byte     | 3     | 3      |

| ORL  | A,Rn          | OR register to accumulator            | 1     | 1      |

| ORL  | A,Direct      | OR direct byte to accumulator         | 2     | 2      |

| ORL  | A,@Ri         | OR indirect RAM to accumulator        | 1     | 2      |

| ORL  | A,#data       | OR immediate data to accumulator      | 2     | 2      |

| ORL  | Direct, A     | OR accumulator to direct byte         | 2     | 3      |

| ORL  | Direct, #data | OR immediate data to direct byte      | 3     | 3      |

| XRL  | A,Rn          | XOR register to accumulator           | 1     | 1      |

| XRL  | A,Direct      | XOR direct byte to accumulator        | 2     | 2      |

| XRL  | A,@Ri         | XOR indirect RAM to accumulator       | 1     | 2      |

| XRL  | A,#data       | XOR immediate data to accumulator     | 2     | 2      |

| XRL  | Direct, A     | XOR accumulator to direct byte        | 2     | 3      |

| XRL  | Direct, #data | XOR immediate data to direct byte     | 3     | 3      |

| CLR  | A             | Clear accumulator                     | 1     | 1      |

| CPL  | A             | Complement accumulator                | 1     | 1      |

| RL   | A             | Rotate accumulator left               | 1     | 1      |

| RLC  | Α             | Rotate accumulator left through carry | 1     | 1      |

| RR   | Α             | Rotate accumulator right              | 1     | 1      |

| RRC  | Α             | Rotate accumulator right though carry | 1     | 1      |

| SWAI | PA            | Swap nibbles within accumulator       | 1     | 1      |

Table 4-4. Boolean Instructions

| Mnemonic     | Description                             | Bytes | Cycles |

|--------------|-----------------------------------------|-------|--------|

| CLR C        | Clear carry                             | 1     | 1      |

| CLR bit      | Clear direct bit                        | 2     | 3      |

| SETB C       | Set carry                               | 1     | 1      |

| SETB bit     | Set direct bit                          | 2     | 3      |

| CPL C        | Complement carry                        | 1     | 1      |

| CPL bit      | Complement direct bit                   | 2     | 3      |

| ANL C, bit   | AND direct bit to carry                 | 2     | 2      |

| ANL C, /bit  | AND complement of direct bit to carry   | 2     | 2      |

| ORL C, bit   | OR direct bit to carry                  | 2     | 2      |

| ORL C, /bit  | OR complement of direct bit to carry    | 2     | 2      |

| MOV C, bit   | Move direct bit to carry                | 2     | 2      |

| MOV bit, C   | Move carry to direct bit                | 2     | 3      |

| JC rel       | Jump if carry is set                    | 2     | 3      |

| JNC rel      | Jump if no carry is set                 | 2     | 3      |

| JB bit, rel  | Jump if direct bit is set               | 3     | 5      |

| JNB bit, rel | Jump if direct bit is not set           | 3     | 5      |

| JBC bit, rel | Jump if direct bit is set and clear bit | 3     | 5      |

# 4.3.1.5 Program Branching Instructions

The 8051 supports a set of conditional and unconditional jump instructions that help to modify the program execution flow. Table 4-5 shows the list of jump instructions.

**Table 4-5. Jump Instructions**

| Mnemonic             | Description                                                  | Bytes | Cycles |

|----------------------|--------------------------------------------------------------|-------|--------|

| ACALL addr11         | Absolute subroutine call                                     | 2     | 4      |

| LCALL addr16         | Long subroutine call                                         | 3     | 4      |

| RET                  | Return from subroutine                                       | 1     | 4      |

| RETI                 | Return from interrupt                                        | 1     | 4      |

| AJMP addr11          | Absolute jump                                                | 2     | 3      |

| LJMP addr16          | Long jump                                                    | 3     | 4      |

| SJMP rel             | Short jump (relative address)                                | 2     | 3      |

| JMP @A + DPTR        | Jump indirect relative to DPTR                               | 1     | 5      |

| JZ rel               | Jump if accumulator is zero                                  | 2     | 4      |

| JNZ rel              | Jump if accumulator is nonzero                               | 2     | 4      |

| CJNE A,Direct, rel   | Compare direct byte to accumulator and jump if not equal     | 3     | 5      |

| CJNE A, #data, rel   | Compare immediate data to accumulator and jump if not equal  | 3     | 4      |

| CJNE Rn, #data, rel  | Compare immediate data to register and jump if not equal     | 3     | 4      |

| CJNE @Ri, #data, rel | Compare immediate data to indirect RAM and jump if not equal | 3     | 5      |

| DJNZ Rn,rel          | Decrement register and jump if not zero                      | 2     | 4      |

| DJNZ Direct, rel     | Decrement direct byte and jump if not zero                   |       | 5      |

| NOP No operation     |                                                              | 1     | 1      |

Document Number: 001-53304 Rev. \*Y Page 16 of 137

# PSoC® 3: CY8C34 Family Datasheet

### 5.7 Memory Map

The CY8C34 8051 memory map is very similar to the MCS-51 memory map.

#### 5.7.1 Code Space

The CY8C34 8051 code space is 64 KB. Only main flash exists in this space. See the "Flash Program Memory" section on page 22.

#### 5.7.2 Internal Data Space

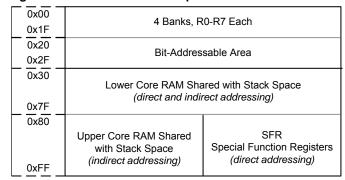

The CY8C34 8051 internal data space is 384 bytes, compressed within a 256-byte space. This space consists of 256 bytes of RAM (in addition to the SRAM mentioned in Static RAM on page 22) and a 128-byte space for Special Function Registers (SFRs). See Figure 5-2. The lowest 32 bytes are used for 4 banks of registers R0-R7. The next 16 bytes are bit-addressable.

Figure 5-2. 8051 Internal Data Space

In addition to the register or bit address modes used with the lower 48 bytes, the lower 128 bytes can be accessed with direct or indirect addressing. With direct addressing mode, the upper 128 bytes map to the SFRs. With indirect addressing mode, the upper 128 bytes map to RAM. Stack operations use indirect addressing; the 8051 stack space is 256 bytes. See the "Addressing Modes" section on page 12

#### 5.7.3 SFRs

The Special Function Register (SFR) space provides access to frequently accessed registers. The memory map for the SFR memory space is shown in Table 5-4.

Table 5-4. SFR Map

| Address | 0/8        | 1/9        | 2/A         | 3/B  | 4/C  | 5/D  | 6/E | 7/F |

|---------|------------|------------|-------------|------|------|------|-----|-----|

| 0×F8    | SFRPRT15DR | SFRPRT15PS | SFRPRT15SEL |      |      |      |     |     |

| 0×F0    | В          |            | SFRPRT12SEL |      |      |      |     |     |

| 0×E8    | SFRPRT12DR | SFRPRT12PS | MXAX        |      |      |      |     |     |

| 0×E0    | ACC        |            |             |      |      |      |     |     |

| 0×D8    | SFRPRT6DR  | SFRPRT6PS  | SFRPRT6SEL  |      |      |      |     |     |

| 0×D0    | PSW        |            |             |      |      |      |     |     |

| 0×C8    | SFRPRT5DR  | SFRPRT5PS  | SFRPRT5SEL  |      |      |      |     |     |

| 0×C0    | SFRPRT4DR  | SFRPRT4PS  | SFRPRT4SEL  |      |      |      |     |     |

| 0×B8    |            |            |             |      |      |      |     |     |

| 0×B0    | SFRPRT3DR  | SFRPRT3PS  | SFRPRT3SEL  |      |      |      |     |     |

| 0×A8    | IE         |            |             |      |      |      |     |     |

| 0×A0    | P2AX       |            | SFRPRT1SEL  |      |      |      |     |     |

| 0×98    | SFRPRT2DR  | SFRPRT2PS  | SFRPRT2SEL  |      |      |      |     |     |

| 0×90    | SFRPRT1DR  | SFRPRT1PS  |             | DPX0 |      | DPX1 |     |     |

| 0×88    |            | SFRPRT0PS  | SFRPRT0SEL  |      |      |      |     |     |

| 0×80    | SFRPRT0DR  | SP         | DPL0        | DPH0 | DPL1 | DPH1 | DPS |     |

Document Number: 001-53304 Rev. \*Y Page 25 of 137

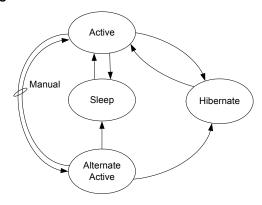

Figure 6-5. Power Mode Transitions

#### 6.2.1.1 Active Mode

Active mode is the primary operating mode of the device. When in active mode, the active configuration template bits control which available resources are enabled or disabled. When a resource is disabled, the digital clocks are gated, analog bias currents are disabled, and leakage currents are reduced as appropriate. User firmware can dynamically control subsystem power by setting and clearing bits in the active configuration template. The CPU can disable itself, in which case the CPU is automatically reenabled at the next wakeup event.

When a wakeup event occurs, the global mode is always returned to active, and the CPU is automatically enabled, regardless of its template settings. Active mode is the default global power mode upon boot.

#### 6.2.1.2 Alternate Active Mode

Alternate Active mode is very similar to Active mode. In alternate active mode, fewer subsystems are enabled, to reduce power consumption. One possible configuration is to turn off the CPU and flash, and run peripherals at full speed.

#### 6.2.1.3 Sleep Mode

Sleep mode reduces power consumption when a resume time of 15  $\mu$ s is acceptable. The wake time is used to ensure that the regulator outputs are stable enough to directly enter active mode.

#### 6.2.1.4 Hibernate Mode

In hibernate mode nearly all of the internal functions are disabled. Internal voltages are reduced to the minimal level to keep vital systems alive. Configuration state is preserved in hibernate mode and SRAM memory is retained. GPIOs configured as digital outputs maintain their previous values and external GPIO pin interrupt settings are preserved. The device can only return from hibernate mode in response to an external I/O interrupt. The resume time from hibernate mode is less than 100 µs.

To achieve an extremely low current, the hibernate regulator has limited capacity. This limits the frequency of any signal present on the input pins - no GPIO should toggle at a rate greater than 10 kHz while in hibernate mode. If pins must be toggled at a high rate while in a low power mode, use sleep mode instead.

#### 6.2.1.5 Wakeup Events

Wakeup events are configurable and can come from an interrupt or device reset. A wakeup event restores the system to active mode. Firmware enabled interrupt sources include internally generated interrupts, power supervisor, central timewheel, and I/O interrupts. Internal interrupt sources can come from a variety of peripherals, such as analog comparators and UDBs. The central timewheel provides periodic interrupts to allow the system to wake up, poll peripherals, or perform real-time functions. Reset event sources include the external reset I/O pin (XRES), WDT, and Precision Reset (PRES).

#### 6.2.2 Boost Converter

Applications that use a supply voltage of less than 1.71 V, such as solar panels or single cell battery supplies, may use the on-chip boost converter to generate a minimum of 1.8 V supply voltage. The boost converter may also be used in any system that requires a higher operating voltage than the supply provides such as driving 5.0 V LCD glass in a 3.3 V system. With the addition of an inductor, Schottky diode, and capacitors, it produces a selectable output voltage sourcing enough current to operate the PSoC and other on-board components.

The boost converter accepts an input voltage V<sub>BAT</sub> from 0.5 V to 3.6 V, and can start up with V<sub>BAT</sub> as low as 0.5 V. The converter provides a user configurable output voltage of 1.8 to 5.0 V (V<sub>OUT</sub>) in 100 mV increments. V<sub>BAT</sub> is typically less than V<sub>OUT</sub>; if V<sub>BAT</sub> is greater than or equal to V<sub>OUT</sub>, then V<sub>OUT</sub> will be slightly less than V<sub>BAT</sub> due to resistive losses in the boost converter. The block can deliver up to 50 mA (I<sub>BOOST</sub>) depending on configuration to both the PSoC device and external components. The sum of all current sinks in the design including the PSoC device, PSoC I/O pin loads, and external component loads must be less than the I<sub>BOOST</sub> specified maximum current.

Four pins are associated with the boost converter: VBAT, VSSB, VBOOST, and IND. The boosted output voltage is sensed at the VBOOST pin and must be connected directly to the chip's supply inputs; VDDA, VDDD, and VDDIO if used to power the PSoC device.

The boost converter requires four components in addition to those required in a non-boost design, as shown in Figure 6-6 on page 33. A 22 µF capacitor (CBAT) is required close to the VBAT pin to provide local bulk storage of the battery voltage and provide regulator stability. A diode between the battery and VBAT pin should not be used for reverse polarity protection because the diodes forward voltage drop reduces the  $V_{BAT}$  voltage. Between the VBAT and IND pins, an inductor of 4.7 μH, 10 μH, or 22 µH is required. The inductor value can be optimized to increase the boost converter efficiency based on input voltage, output voltage, temperature, and current. Inductor size is determined by following the design guidance in this chapter and electrical specifications. The inductor must be placed within 1 cm of the VBAT and IND pins and have a minimum saturation current of 750 mA. Between the IND and VBOOST pins, place a Schottky diode within 1 cm of the pins. The Schottky diode shall have a forward current rating of at least 1.0 A and a reverse voltage of at least 20 V. Connect a 22-µF bulk capacitor (CBOOST) close to VBOOST to provide regulator output stability. It is important to sum the total capacitance connected to the VBOOST pin and ensure the maximum  $C_{\mbox{\footnotesize{BOOST}}}$  specification is not exceeded. All capacitors must be rated for a minimum of 10 V to minimize capacitive losses due to voltage de-rating.

# PSoC® 3: CY8C34 Family Datasheet

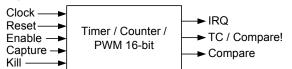

### 7.7 Timers, Counters, and PWMs

The Timer/Counter/PWM peripheral is a 16-bit dedicated peripheral providing three of the most common embedded peripheral features. As almost all embedded systems use some combination of timers, counters, and PWMs. Four of them have been included on this PSoC device family. Additional and more advanced functionality timers, counters, and PWMs can also be instantiated in Universal Digital Blocks (UDBs) as required. PSoC Creator allows you to choose the timer, counter, and PWM features that they require. The tool set utilizes the most optimal resources available.

The Timer/Counter/PWM peripheral can select from multiple clock sources, with input and output signals connected through the DSI routing. DSI routing allows input and output connections to any device pin and any internal digital signal accessible through the DSI. Each of the four instances has a compare output, terminal count output (optional complementary compare output), and programmable interrupt request line. The Timer/Counter/PWMs are configurable as free running, one shot, or Enable input controlled. The peripheral has timer reset and capture inputs, and a kill input for control of the comparator outputs. The peripheral supports full 16-bit capture.

Timer/Counter/PWM features include:

- 16-bit Timer/Counter/PWM (down count only)

- Selectable clock source

- PWM comparator (configurable for LT, LTE, EQ, GTE, GT)

- Period reload on start, reset, and terminal count

- Interrupt on terminal count, compare true, or capture

- Dynamic counter reads

- Timer capture mode

- Count while enable signal is asserted mode

- Free run mode

- One Shot mode (stop at end of period)

- Complementary PWM outputs with deadband

- PWM output kill

#### Figure 7-17. Timer/Counter/PWM

Document Number: 001-53304 Rev. \*Y Page 53 of 137

Analog local buses (abus) are routing resources located within the analog subsystem and are used to route signals between different analog blocks. There are eight abus routes in CY8C34, four in the left half (abusl [0:3]) and four in the right half (abusr [0:3]) as shown in Figure 8-2. Using the abus saves the analog globals and analog mux buses from being used for interconnecting the analog blocks.

Multiplexers and switches exist on the various buses to direct signals into and out of the analog blocks. A multiplexer can have only one connection on at a time, whereas a switch can have multiple connections on simultaneously. In Figure 8-2, multiplexers are indicated by grayed ovals and switches are indicated by transparent ovals.

#### 8.2 Delta-sigma ADC

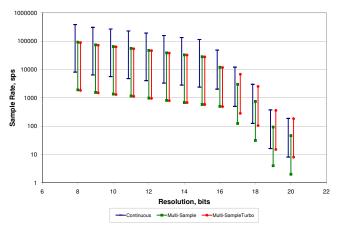

The CY8C34 device contains one delta-sigma ADC. This ADC offers differential input, high resolution and excellent linearity, making it a good ADC choice for measurement applications. The converter can be configured to output 12-bit resolution at data rates of up to 192 ksps. At a fixed clock rate, resolution can be traded for faster data rates as shown in Table 8-1 and Figure 8-3.

Table 8-1. Delta-sigma ADC Performance

| Bits | Maximum Sample Rate (sps) | SINAD (dB) |

|------|---------------------------|------------|

| 12   | 192 k                     | 66         |

| 8    | 384 k                     | 43         |

Figure 8-3. Delta-sigma ADC Sample Rates, Range = ±1.024 V

#### 8.2.1 Functional Description

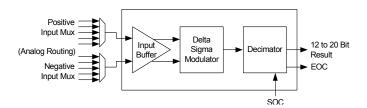

The ADC connects and configures three basic components, input buffer, delta-sigma modulator, and decimator. The basic block diagram is shown in Figure 8-4. The signal from the input muxes is delivered to the delta-sigma modulator either directly or through the input buffer. The delta-sigma modulator performs the actual analog to digital conversion. The modulator over-samples the input and generates a serial data stream output. This high speed data stream is not useful for most applications without some type of post processing, and so is passed to the decimator through the Analog Interface block. The decimator converts the

high speed serial data stream into parallel ADC results. The modulator/decimator frequency response is  $[(\sin x)/x]^4$ .

Figure 8-4. Delta-sigma ADC Block Diagram

Resolution and sample rate are controlled by the Decimator. Data is pipelined in the decimator; the output is a function of the last four samples. When the input multiplexer is switched, the output data is not valid until after the fourth sample after the switch.

#### 8.2.2 Operational Modes

The ADC can be configured by the user to operate in one of four modes: Single Sample, Multi Sample, Continuous, or Multi Sample (Turbo). All four modes are started by either a write to the start bit in a control register or an assertion of the Start of Conversion (SoC) signal. When the conversion is complete, a status bit is set and the output signal End of Conversion (EoC) asserts high and remains high until the value is read by either the DMA controller or the CPU.

#### 8.2.2.1 Single Sample

In Single Sample mode, the ADC performs one sample conversion on a trigger. In this mode, the ADC stays in standby state waiting for the SoC signal to be asserted. When SoC is signaled the ADC performs four successive conversions. The first three conversions prime the decimator. The ADC result is valid and available after the fourth conversion, at which time the EoC signal is generated. To detect the end of conversion, the system may poll a control register for status or configure the external EoC signal to generate an interrupt or invoke a DMA request. When the transfer is done the ADC reenters the standby state where it stays until another SoC event.

#### 8.2.2.2 Continuous

Continuous sample mode is used to take multiple successive samples of a single input signal. Multiplexing multiple inputs should not be done with this mode. There is a latency of three conversion times before the first conversion result is available. This is the time required to prime the decimator. After the first result, successive conversions are available at the selected sample rate.

## 8.2.2.3 Multi Sample

Multi sample mode is similar to continuous mode except that the ADC is reset between samples. This mode is useful when the input is switched between multiple signals. The decimator is re-primed between each sample so that previous samples do not affect the current conversion. Upon completion of a sample, the next sample is automatically initiated. The results can be transferred using either firmware polling, interrupt, or DMA.

More information on output formats is provided in the Technical Reference Manual.

#### 8.3.2 LUT

The CY8C34 family of devices contains four LUTs. The LUT is a two input, one output lookup table that is driven by any one or two of the comparators in the chip. The output of any LUT is routed to the digital system interface of the UDB array. From the digital system interface of the UDB array, these signals can be connected to UDBs, DMA controller, I/O, or the interrupt controller.

The LUT control word written to a register sets the logic function on the output. The available LUT functions and the associated control word is shown in Table 8-2.

Table 8-2. LUT Function vs. Program Word and Inputs

| Control Word | Output (A and B are LUT inputs) |

|--------------|---------------------------------|

| 0000b        | FALSE ('0')                     |

| 0001b        | A AND B                         |

| 0010b        | A AND (NOT B)                   |

| 0011b        | A                               |

| 0100b        | (NOT A) AND B                   |

| 0101b        | В                               |

| 0110b        | A XOR B                         |

| 0111b        | A OR B                          |

| 1000b        | A NOR B                         |

| 1001b        | A XNOR B                        |

| 1010b        | NOT <b>B</b>                    |

| 1011b        | A OR (NOT B)                    |

| 1100b        | NOT A                           |

| 1101b        | (NOT A) OR B                    |

| 1110b        | A NAND B                        |

| 1111b        | TRUE ('1')                      |

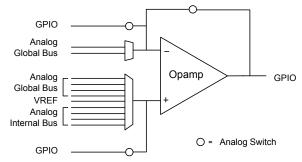

# 8.4 Opamps

The CY8C34 family of devices contains two general purpose opamps in a device.

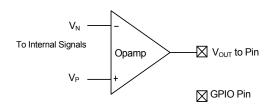

Figure 8-6. Opamp

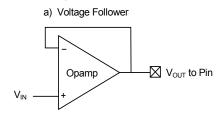

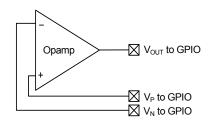

The opamp is uncommitted and can be configured as a gain stage or voltage follower, or output buffer on external or internal signals.

See Figure 8-7. In any configuration, the input and output signals can all be connected to the internal global signals and monitored with an ADC, or comparator. The configurations are implemented with switches between the signals and GPIO pins.

Figure 8-7. Opamp Configurations

b) External Uncommitted Opamp

c) Internal Uncommitted Opamp

The opamp has three speed modes, slow, medium, and fast. The slow mode consumes the least amount of quiescent power and the fast mode consumes the most power. The inputs are able to swing rail-to-rail. The output swing is capable of rail-to-rail operation at low current output, within 50 mV of the rails. When driving high current loads (about 25 mA) the output voltage may only get within 500 mV of the rails.

### 8.5 Programmable SC/CT Blocks

The CY8C34 family of devices contains two switched capacitor/continuous time (SC/CT) blocks in a device. Each switched capacitor/continuous time block is built around a single rail-to-rail high bandwidth opamp.

Switched capacitor is a circuit design technique that uses capacitors plus switches instead of resistors to create analog functions. These circuits work by moving charge between capacitors by opening and closing different switches. Nonoverlapping in phase clock signals control the switches, so that not all switches are ON simultaneously.

# 11.2 Device Level Specifications

Specifications are valid for  $-40~^{\circ}\text{C} \le T_A \le 85~^{\circ}\text{C}$  and  $T_J \le 100~^{\circ}\text{C}$ , except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted.

#### 11.2.1 Device Level Specifications

# Table 11-2. DC Specifications

| Parameter                           | Description                                                                        | Conditions                                                                  |             | Min  | <b>Typ</b> <sup>[25]</sup> | Max                                    | Units    |

|-------------------------------------|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------------|------|----------------------------|----------------------------------------|----------|

| $V_{DDA}$                           | Analog supply voltage and input to analog core regulator                           | Analog core regulat                                                         | or enabled  | 1.8  | _                          | 5.5                                    | V        |

| $V_{DDA}$                           | Analog supply voltage, analog regulator bypassed                                   | Analog core regulat                                                         | or disabled | 1.71 | 1.8                        | 1.89                                   | V        |

| $V_{\mathrm{DDD}}$                  | Digital supply voltage relative to V <sub>SSD</sub>                                | Digital core regulato                                                       | or enabled  | 1.8  | -                          | V <sub>DDA</sub> <sup>[21]</sup>       | V        |

| • טטט                               | Digital supply voltage relative to v <sub>SSD</sub>                                | Digital core regulate                                                       | or chabica  | ı    | 1                          | V <sub>DDA</sub> + 0.1 <sup>[27]</sup> | V        |

| $V_{DDD}$                           | Digital supply voltage, digital regulator bypassed                                 | Digital core regulato                                                       | or disabled | 1.71 | 1.8                        | 1.89                                   | <b>V</b> |

| V <sub>DDIO</sub> <sup>[22]</sup>   | I/O supply voltage relative to V <sub>SSIO</sub>                                   |                                                                             |             | 1.71 | 1                          | V <sub>DDA</sub> <sup>[21]</sup>       | V        |

| סוטט                                |                                                                                    |                                                                             |             | -    | _                          | V <sub>DDA</sub> + 0.1 <sup>[27]</sup> | •        |

| $V_{CCA}$                           | Direct analog core voltage input (Analog regulator bypass)                         | Analog core regulat                                                         | or disabled | 1.71 | 1.8                        | 1.89                                   | <b>V</b> |

| V <sub>CCD</sub>                    | Direct digital core voltage input (Digital regulator bypass)                       | Digital core regulator                                                      | or disabled | 1.71 | 1.8                        | 1.89                                   | ٧        |

|                                     | Active Mode                                                                        |                                                                             |             |      |                            |                                        |          |

|                                     | Only IMO and CPU clock enabled. CPU executing simple loop from instruction buffer. | $V_{DDX} = 2.7 \text{ V} = 5.5 \text{ V};$ $F_{CPU} = 6 \text{ MHz}^{[26]}$ | T = -40 °C  | 1    | 1.2                        | 2.9                                    |          |

|                                     |                                                                                    |                                                                             | T = 25 °C   | ı    | 1.2                        | 3.1                                    |          |

|                                     |                                                                                    |                                                                             | T = 85 °C   | -    | 4.9                        | 7.7                                    |          |

|                                     |                                                                                    | $V_{DDX} = 2.7 \text{ V} - 5.5 \text{ V};$ $F_{CPU} = 3 \text{ MHz}^{[26]}$ | T = -40 °C  | ı    | 1.3                        | 2.9                                    |          |

|                                     |                                                                                    |                                                                             | T = 25 °C   | -    | 1.6                        | 3.2                                    |          |

|                                     |                                                                                    |                                                                             | T = 85 °C   | ı    | 4.8                        | 7.5                                    |          |

|                                     |                                                                                    | $V_{DDX} = 2.7 V -$                                                         | T = -40 °C  | ı    | 2.1                        | 3.7                                    |          |

| roo 0.41                            |                                                                                    | 5.5 V;<br>F <sub>CPU</sub> = 6 MHz                                          | T = 25 °C   | ı    | 2.3                        | 3.9                                    |          |

| I <sub>DD</sub> <sup>[23, 24]</sup> |                                                                                    |                                                                             | T = 85 °C   | ı    | 5.6                        | 8.5                                    | mA       |

|                                     | IMO enabled, bus clock and CPU clock                                               | V <sub>DDX</sub> = 2.7 V –<br>5.5 V;                                        | T = -40 °C  | -    | 3.5                        | 5.2                                    |          |

|                                     | enabled. CPU executing program from flash.                                         | $F_{CPU} = 12 \text{ MHz}^{[26]}$                                           | T = 25 °C   | ı    | 3.8                        | 5.5                                    |          |

|                                     | ilasii.                                                                            |                                                                             | T = 85 °C   | ı    | 7.1                        | 9.8                                    |          |

|                                     |                                                                                    | V <sub>DDX</sub> = 2.7 V –<br>5.5 V;                                        | T = -40 °C  | ı    | 6.3                        | 8.1                                    |          |

|                                     |                                                                                    | $F_{CPU} = 24 \text{ MHz}^{[26]}$                                           | T = 25 °C   | ı    | 6.6                        | 8.3                                    |          |

|                                     |                                                                                    |                                                                             | T = 85 °C   | _    | 10                         | 13                                     |          |

|                                     |                                                                                    | V <sub>DDX</sub> = 2.7 V –<br>5.5 V;                                        | T = -40 °C  | ı    | 11.5                       | 13.5                                   |          |

|                                     |                                                                                    | $F_{CPU} = 48 \text{ MHz}^{[26]}$                                           | T = 25 °C   | ı    | 12                         | 14                                     |          |

|                                     |                                                                                    | GFU 13                                                                      | T = 85 °C   | _    | 15.5                       | 18.5                                   |          |

<sup>21.</sup> The power supplies can be brought up in any sequence however once stable V<sub>DDA</sub> must be greater than or equal to all other supplies.

22. The V<sub>DDIO</sub> supply voltage must be greater than the maximum voltage on the associated GPIO pins. Maximum voltage on GPIO pin ≤ V<sub>DDIO</sub> ≤ V<sub>DDA</sub>.

23. Total current for all power domains: digital (I<sub>DDA</sub>), analog (I<sub>DDA</sub>), and I/Os (I<sub>DDIO1, 1, 2, 3</sub>). Boost not included. All I/Os floating.

24. The current consumption of additional peripherals that are implemented only in programmed logic blocks can be found in their respective datasheets, available in PSoC Creator, the integrated design environment. To estimate total current, find the CPU current at the frequency of interest and add peripheral currents for your particular systems from the davise datasheet and companyed databater. particular system from the device datasheet and component datasheets. 25. V<sub>DDX</sub> = 3.3 V.

<sup>26.</sup> Based on device characterization (Not Production tested).

<sup>27.</sup> Guaranteed by design, not production tested.

# 11.3.3 Inductive Boost Regulator

Unless otherwise specified, operating conditions are:  $V_{BAT}$  = 0.5 V–3.6 V,  $V_{OUT}$  = 1.8 V–5.0 V,  $I_{OUT}$  = 0 mA–50 mA,  $L_{BOOST}$  = 4.7  $\mu$ H–22  $\mu$ H,  $C_{BOOST}$  = 22  $\mu$ F || 3 × 1.0  $\mu$ F || 3 × 0.1  $\mu$ F,  $C_{BAT}$  = 22  $\mu$ F,  $I_F$  = 1.0 A. Unless otherwise specified, all charts and graphs show typical values.

Table 11-6. Inductive Boost Regulator DC Specifications

| Parameter           | Description                            | Cone                          | ditions                                                               | Min  | Тур  | Max  | Units |

|---------------------|----------------------------------------|-------------------------------|-----------------------------------------------------------------------|------|------|------|-------|

| V <sub>OUT</sub>    | Boost output voltage <sup>[34]</sup>   | vsel = 1.8 V in regist        | ter BOOST_CR0                                                         | 1.71 | 1.8  | 1.89 | V     |

|                     |                                        | vsel = 1.9 V in regist        | ter BOOST_CR0                                                         | 1.81 | 1.90 | 2.00 | V     |

|                     |                                        | vsel = 2.0 V in regist        | ter BOOST_CR0                                                         | 1.90 | 2.00 | 2.10 | V     |

|                     |                                        | vsel = 2.4 V in regist        | ter BOOST_CR0                                                         | 2.16 | 2.40 | 2.64 | V     |

|                     |                                        | vsel = 2.7 V in regist        | ter BOOST_CR0                                                         | 2.43 | 2.70 | 2.97 | V     |

|                     |                                        | vsel = 3.0 V in regist        | ter BOOST_CR0                                                         | 2.70 | 3.00 | 3.30 | V     |

|                     |                                        | vsel = 3.3 V in regist        | ter BOOST_CR0                                                         | 2.97 | 3.30 | 3.63 | V     |

|                     |                                        | vsel = 3.6 V in regist        | ter BOOST_CR0                                                         | 3.24 | 3.60 | 3.96 | V     |

|                     |                                        | vsel = 5.0 V in regist        | ter BOOST_CR0                                                         | 4.50 | 5.00 | 5.50 | V     |

| $V_{BAT}$           | Input voltage to boost <sup>[35]</sup> | I <sub>OUT</sub> = 0 mA–5 mA  | vsel = 1.8 V-2.0 V,<br>T <sub>A</sub> = 0 °C-70 °C                    | 0.5  | _    | 0.8  | V     |

|                     |                                        | I <sub>OUT</sub> = 0 mA–15 mA | vsel = 1.8 V-5.0 V <sup>[36]</sup> ,<br>T <sub>A</sub> = -10 °C-85 °C | 1.6  | -    | 3.6  | V     |

|                     |                                        | I <sub>OUT</sub> = 0 mA–25 mA | vsel = 1.8 V–2.7 V,<br>T <sub>A</sub> = –10 °C–85 °C                  | 8.0  | _    | 1.6  | V     |

|                     |                                        | I <sub>OUT</sub> = 0 mA–50 mA | vsel = 1.8 V-3.3 V <sup>[36]</sup> ,<br>T <sub>A</sub> = -40 °C-85 °C | 1.8  | _    | 2.5  | V     |

|                     |                                        |                               | vsel = 1.8 V-3.3 V <sup>[36]</sup> ,<br>T <sub>A</sub> = -10 °C-85 °C | 1.3  | _    | 2.5  | V     |

|                     |                                        |                               | vsel = 2.5 V-5.0 V <sup>[36]</sup> ,<br>T <sub>A</sub> = -10 °C-85 °C | 2.5  | _    | 3.6  | V     |

| I <sub>OUT</sub>    | Output current                         | T <sub>A</sub> = 0 °C-70 °C   | V <sub>BAT</sub> = 0.5 V–0.8 V                                        | 0    | _    | 5    | mA    |

|                     |                                        | T <sub>A</sub> = -10 °C-85 °C | V <sub>BAT</sub> = 1.6 V–3.6 V                                        | 0    | _    | 15   | mA    |

|                     |                                        |                               | V <sub>BAT</sub> = 0.8 V–1.6 V                                        | 0    | _    | 25   | mA    |

|                     |                                        |                               | V <sub>BAT</sub> = 1.3 V–2.5 V                                        | 0    | _    | 50   | mA    |

|                     |                                        |                               | V <sub>BAT</sub> = 2.5 V–3.6 V                                        | 0    | _    | 50   | mA    |

|                     |                                        | T <sub>A</sub> = -40 °C-85 °C | 5,                                                                    | 0    | _    | 50   | mA    |

| l. s                | Inductor peak current                  | 14 10 0 00 0                  | VBAT 1.0 V Z.0 V                                                      |      |      | 700  | mA    |

| I <sub>LPK</sub>    | ·                                      | Department of the             |                                                                       |      | 250  |      |       |

| $I_Q$               | Quiescent current                      | Boost active mode             | ~ 1 uA                                                                | _    | 250  | _    | μΑ    |

| D                   | Leader Le                              | Boost sleep mode, I           | OUT > 1 µA                                                            |      | 25   | -    | μA    |

| Reg <sub>LOAD</sub> | Load regulation                        |                               |                                                                       | _    | _    | 10   | %     |

| Reg <sub>LINE</sub> | Line regulation                        |                               |                                                                       | -    | _    | 10   | %     |

<sup>34.</sup> Listed vsel options are characterized. Additional vsel options are valid and guaranteed by design.

35. The boost will start at all valid V<sub>BAT</sub> conditions including down to V<sub>BAT</sub> = 0.5 V.

36. If V<sub>BAT</sub> is greater than or equal to V<sub>OUT</sub> boost setting, then V<sub>OUT</sub> will be less than V<sub>BAT</sub> due to resistive losses in the boost circuit.

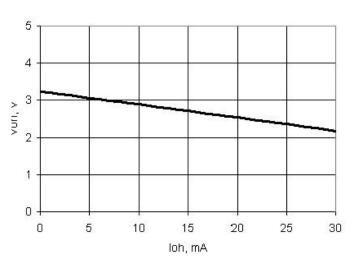

Figure 11-22. USBIO Output High Voltage and Current, GPIO Mode

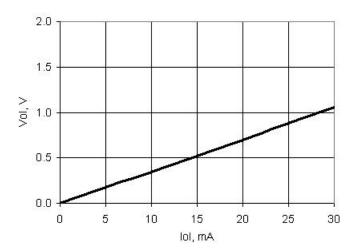

Figure 11-23. USBIO Output Low Voltage and Current, GPIO Mode

Table 11-15. USBIO AC Specifications

| Parameter | Description                                                 | Conditions                                           | Min        | Тур | Max           | Units |

|-----------|-------------------------------------------------------------|------------------------------------------------------|------------|-----|---------------|-------|

| Tdrate    | Full-speed data rate average bit rate                       |                                                      | 12 – 0.25% | 12  | 12 +<br>0.25% | MHz   |

| Tjr1      | Receiver data jitter tolerance to next transition           |                                                      | -8         | _   | 8             | ns    |

| Tjr2      | Receiver data jitter tolerance to pair transition           |                                                      | <b>-</b> 5 | _   | 5             | ns    |

| Tdj1      | Driver differential jitter to next transition               |                                                      | -3.5       | -   | 3.5           | ns    |

| Tdj2      | Driver differential jitter to pair transition               |                                                      | -4         | -   | 4             | ns    |

| Tfdeop    | Source jitter for differential transition to SE0 transition |                                                      | -2         | -   | 5             | ns    |

| Tfeopt    | Source SE0 interval of EOP                                  |                                                      | 160        | -   | 175           | ns    |

| Tfeopr    | Receiver SE0 interval of EOP                                |                                                      | 82         | -   | _             | ns    |

| Tfst      | Width of SE0 interval during differential transition        |                                                      | _          | _   | 14            | ns    |

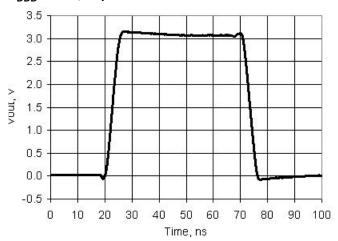

| Fgpio_out | GPIO mode output operating                                  | $3 \text{ V} \leq \text{V}_{DDD} \leq 5.5 \text{ V}$ | _          | -   | 20            | MHz   |

|           | frequency                                                   | V <sub>DDD</sub> = 1.71 V                            | _          | _   | 6             | MHz   |

| Tr_gpio   | Rise time, GPIO mode, 10%/90% V <sub>DDD</sub>              | V <sub>DDD</sub> > 3 V, 25 pF load                   | _          | -   | 12            | ns    |

|           |                                                             | V <sub>DDD</sub> = 1.71 V, 25 pF load                | _          | _   | 40            | ns    |

| Tf_gpio   | Fall time, GPIO mode, 90%/10% V <sub>DDD</sub>              | V <sub>DDD</sub> > 3 V, 25 pF load                   | _          | _   | 12            | ns    |

|           |                                                             | V <sub>DDD</sub> = 1.71 V, 25 pF load                | _          | _   | 40            | ns    |

Figure 11-24. USBIO Output Rise and Fall Times, GPIO Mode,  $\rm V_{DDD} = 3.3~V,\,25~pF~Load$

Table 11-16. USB Driver AC Specifications

| Parameter | Description                     | Conditions                                                                           | Min | Тур | Max  | Units |

|-----------|---------------------------------|--------------------------------------------------------------------------------------|-----|-----|------|-------|

| Tr        | Transition rise time            |                                                                                      | _   | _   | 20   | ns    |

| Tf        | Transition fall time            |                                                                                      | _   | _   | 20   | ns    |

| TR        | Rise/fall time matching         | V <sub>USB_5</sub> , V <sub>USB_3.3</sub> , see USB DC<br>Specifications on page 107 | 90% | _   | 111% |       |

| Vcrs      | Output signal crossover voltage |                                                                                      | 1.3 | _   | 2    | V     |

# 11.5.6 Current Digital-to-analog Converter (IDAC)

All specifications are based on use of the low-resistance IDAC output pins (see Pin Descriptions on page 11 for details). See the IDAC component data sheet in PSoC Creator for full electrical specifications and APIs.

Unless otherwise specified, all charts and graphs show typical values.

Table 11-28. IDAC DC Specifications

| Parameter        | Description                           | Conditions                                                                                                      | Min | Тур    | Max  | Units  |

|------------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----|--------|------|--------|

|                  | Resolution                            |                                                                                                                 | _   | _      | 8    | bits   |

| I <sub>OUT</sub> | Output current at code = 255          | Range = 2.04 mA, code = 255,<br>$V_{DDA} \ge 2.7$ V, Rload = 600 $\Omega$                                       | -   | 2.04   | -    | mA     |

|                  |                                       | Range = 2.04 mA, high speed mode, code = 255, $V_{DDA} \le 2.7$ V, Rload = 300 $\Omega$                         | _   | 2.04   | -    | mA     |

|                  |                                       | Range = 255 $\mu$ A, code = 255, Rload<br>= 600 $\Omega$                                                        | _   | 255    | -    | μΑ     |

|                  |                                       | Range = 31.875 $\mu$ A, code = 255,<br>Rload = 600 $\Omega$                                                     | _   | 31.875 | -    | μΑ     |

|                  | Monotonicity                          |                                                                                                                 | _   | _      | Yes  |        |

| Ezs              | Zero scale error                      |                                                                                                                 | _   | 0      | ±1   | LSB    |

| Eg               | Gain error                            | Range = 2.04 mA, 25 °C                                                                                          | _   | _      | ±2.5 | %      |

|                  |                                       | Range = 255 μA, 25 ° C                                                                                          | _   | _      | ±2.5 | %      |

|                  |                                       | Range = 31.875 μA, 25 ° C                                                                                       | _   | _      | ±3.5 | %      |

| TC_Eg            | Temperature coefficient of gain error | Range = 2.04 mA                                                                                                 | _   | _      | 0.04 | % / °C |

|                  |                                       | Range = 255 μA                                                                                                  | _   | _      | 0.04 | % / °C |

|                  |                                       | Range = 31.875 μA                                                                                               | _   | _      | 0.05 | % / °C |

| INL              | Integral nonlinearity                 | Sink mode, range = 255 $\mu$ A, Codes 8 – 255, Rload = 2.4 $k\Omega$ , Cload = 15 pF                            | -   | ±0.9   | ±1   | LSB    |

|                  |                                       | Source mode, range = 255 $\mu$ A,<br>Codes 8 – 255, Rload = 2.4 $k\Omega$ ,<br>Cload = 15 pF                    | -   | ±1.2   | ±1.6 | LSB    |

| DNL              | Differential nonlinearity             | Sink mode, range = 255 μA, Rload<br>= 2.4 kΩ, Cload = 15 pF                                                     | _   | ±0.3   | ±1   | LSB    |

|                  |                                       | Source mode, range = 255 $\mu$ A,<br>Rload = 2.4 $k\Omega$ , Cload = 15 pF                                      | _   | ±0.3   | ±1   | LSB    |

| Vcompliance      | Dropout voltage, source or sink mode  | Voltage headroom at max current, $R_{LOAD}$ to $V_{DDA}$ or $R_{LOAD}$ to $V_{SSA}$ , $V_{DIFF}$ from $V_{DDA}$ | 1   | -      | -    | V      |

Document Number: 001-53304 Rev. \*Y Page 94 of 137

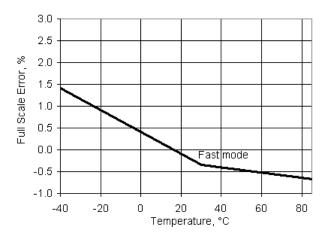

Figure 11-40. IDAC Full Scale Error vs Temperature, Range = 255  $\mu$ A, Source Mode

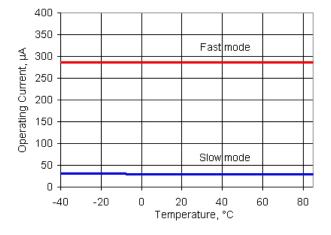

Figure 11-42. IDAC Operating Current vs Temperature, Range =  $255 \mu A$ , Code = 0, Source Mode

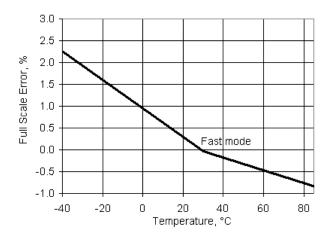

Figure 11-41. IDAC Full Scale Error vs Temperature, Range = 255  $\mu$ A, Sink Mode

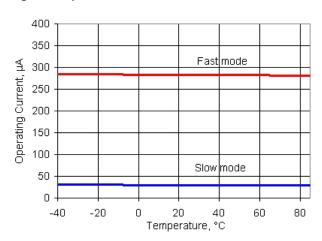

Figure 11-43. IDAC Operating Current vs Temperature, Range = 255 µA, Code = 0, Sink Mode

Table 11-29. IDAC AC Specifications

| Parameter           | Description              | Conditions                                                                                             | Min | Тур | Max | Units     |

|---------------------|--------------------------|--------------------------------------------------------------------------------------------------------|-----|-----|-----|-----------|

| F <sub>DAC</sub>    | Update rate              |                                                                                                        | _   | _   | 8   | Msps      |

| T <sub>SETTLE</sub> | Settling time to 0.5 LSB | Range = 31.875 $\mu$ A or 255 $\mu$ A, full scale transition, High speed mode, 600 $\Omega$ 15-pF load | -   | _   | 125 | ns        |

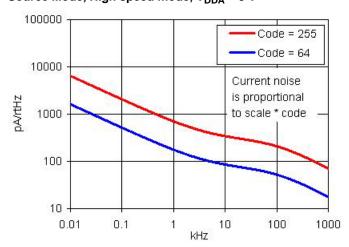

|                     | Current noise            | Range = 255 $\mu$ A, source mode,<br>High speed mode, V <sub>DDA</sub> = 5 V,<br>10 kHz                | -   | 340 | _   | pA/sqrtHz |

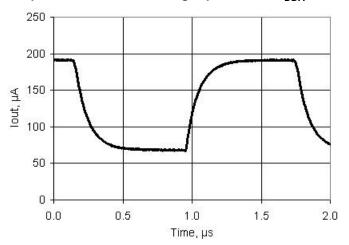

Figure 11-44. IDAC Step Response, Codes 0x40 - 0xC0, 255 µA Mode, Source Mode, High speed mode, V<sub>DDA</sub> = 5 V

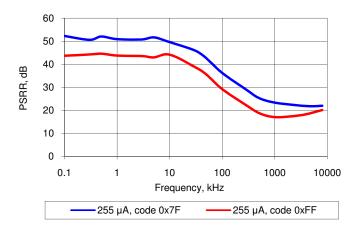

Figure 11-46. IDAC PSRR vs Frequency

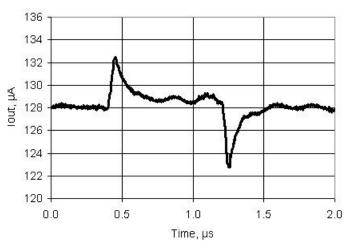

Figure 11-45. IDAC Glitch Response, Codes 0x7F - 0x80, 255  $\mu A$  Mode, Source Mode, High speed mode,  $V_{DDA} = 5$  V

Figure 11-47. IDAC Current Noise, 255  $\mu$ A Mode, Source Mode, High speed mode, V<sub>DDA</sub> = 5 V

Table 11-37. PGA AC Specifications

| Parameter      | Description         | Conditions                                                     | Min | Тур | Max | Units     |

|----------------|---------------------|----------------------------------------------------------------|-----|-----|-----|-----------|

| BW1            | –3 dB bandwidth     | Power mode = high,<br>gain = 1, input = 100 mV<br>peak-to-peak | 6.7 | 8   | _   | MHz       |

| SR1            | Slew rate           | Power mode = high,<br>gain = 1, 20% to 80%                     | 3   | _   | _   | V/µs      |

| e <sub>n</sub> | Input noise density | Power mode = high,<br>V <sub>DDA</sub> = 5 V, at 100 kHz       | _   | 43  | _   | nV/sqrtHz |

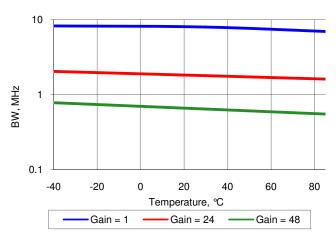

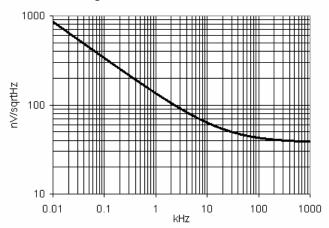

Figure 11-61. Bandwidth vs. Temperature, at Different Gain Settings, Power Mode = High

Figure 11-62. Noise vs. Frequency,  $V_{DDA}$  = 5 V, Power Mode = High

11.5.11 Temperature Sensor

Table 11-38. Temperature Sensor Specifications

| Parameter | Description          | Conditions              | Min | Тур | Max | Units |

|-----------|----------------------|-------------------------|-----|-----|-----|-------|

|           | Temp sensor accuracy | Range: -40 °C to +85 °C | -   | ±5  | ı   | °C    |

### 11.5.12 LCD Direct Drive

Table 11-39. LCD Direct Drive DC Specifications

| Parameter           | Description                                                                         | Conditions                                                                                                                                                                                                | Min | Тур                    | Max  | Units |

|---------------------|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------------|------|-------|

| I <sub>CC</sub>     | LCD system operating current                                                        | Device sleep mode with wakeup at 400-Hz rate to refresh LCDs, bus clock = 3 Mhz, V <sub>DDIO</sub> = V <sub>DDA</sub> = 3 V, 4 commons, 16 segments, 1/4 duty cycle, 50 Hz frame rate, no glass connected | -   | 38                     | -    | μА    |

| I <sub>CC SEG</sub> | Current per segment driver                                                          | Strong drive mode                                                                                                                                                                                         | _   | 260                    | -    | μA    |

| V <sub>BIAS</sub>   | LCD bias range (V <sub>BIAS</sub> refers to the main output voltage(V0) of LCD DAC) | $V_{DDA} \ge 3 \text{ V} \text{ and } V_{DDA} \ge V_{BIAS}$                                                                                                                                               | 2   | _                      | 5    | V     |

|                     | LCD bias step size                                                                  | $V_{DDA} \ge 3 \text{ V and } V_{DDA} \ge V_{BIAS}$                                                                                                                                                       | _   | 9.1 × V <sub>DDA</sub> | _    | mV    |

|                     | LCD capacitance per segment/common driver                                           | Drivers may be combined                                                                                                                                                                                   | _   | 500                    | 5000 | pF    |

|                     | Long term segment offset                                                            |                                                                                                                                                                                                           | _   | _                      | 20   | mV    |

| I <sub>OUT</sub>    | Output drive current per segment driver)                                            | V <sub>DDIO</sub> = 5.5 V, strong drive mode                                                                                                                                                              | 355 | _                      | 710  | μΑ    |

Table 11-40. LCD Direct Drive AC Specifications

| Parameter | Description    | Conditions | Min | Тур | Max | Units |

|-----------|----------------|------------|-----|-----|-----|-------|

| $f_{LCD}$ | LCD frame rate |            | 10  | 50  | 150 | Hz    |

# 11.8.3 Interrupt Controller

# Table 11-69. Interrupt Controller AC Specifications

| Parameter | Description                             | Conditions                                                              | Min | Тур | Max | Units   |

|-----------|-----------------------------------------|-------------------------------------------------------------------------|-----|-----|-----|---------|

|           | , , , , , , , , , , , , , , , , , , , , | Includes worse case completion of longest instruction DIV with 6 cycles | _   | _   | 25  | Tcy CPU |

### 11.8.4 JTAG Interface

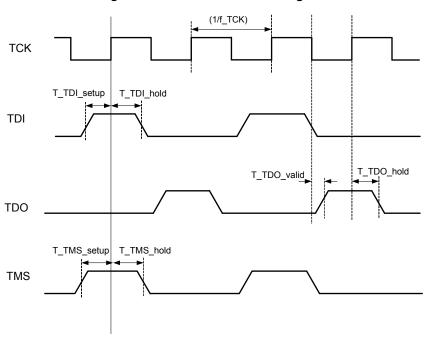

Figure 11-68. JTAG Interface Timing

Table 11-70. JTAG Interface AC Specifications<sup>[69]</sup>

| Parameter   | Description                  | Conditions                                           | Min        | Тур | Max                | Units |

|-------------|------------------------------|------------------------------------------------------|------------|-----|--------------------|-------|

| f_TCK       | TCK frequency                | $3.3 \text{ V} \leq \text{V}_{DDD} \leq 5 \text{ V}$ | _          | _   | 14 <sup>[70]</sup> | MHz   |

|             |                              | 1.71 V ≤ V <sub>DDD</sub> < 3.3 V                    | _          | -   | 7 <sup>[70]</sup>  | MHz   |

| T_TDI_setup | TDI setup before TCK high    |                                                      | (T/10) - 5 | _   | _                  | ns    |

| T_TMS_setup | TMS setup before TCK high    |                                                      | T/4        | _   | _                  |       |

| T_TDI_hold  | TDI, TMS hold after TCK high | T = 1/f_TCK max                                      | T/4        | -   | _                  |       |

| T_TDO_valid | TCK low to TDO valid         | T = 1/f_TCK max                                      | _          | -   | 2T/5               |       |

| T_TDO_hold  | TDO hold after TCK high      | T = 1/f_TCK max                                      | T/4        | -   | _                  |       |

<sup>69.</sup> Based on device characterization (Not production tested). 70. f\_TCK must also be no more than 1/3 CPU clock frequency.

### 11.8.5 SWD Interface

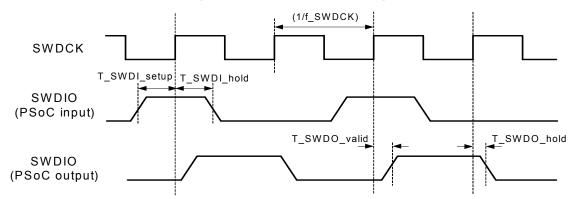

# Figure 11-69. SWD Interface Timing

Table 11-71. SWD Interface AC Specifications<sup>[71]</sup>

| Parameter    | Description                         | Conditions                                                                      | Min | Тур | Max                 | Units |

|--------------|-------------------------------------|---------------------------------------------------------------------------------|-----|-----|---------------------|-------|

| f_SWDCK      | SWDCLK frequency                    | $3.3 \text{ V} \leq \text{V}_{DDD} \leq 5 \text{ V}$                            | _   | _   | 14 <sup>[72]</sup>  | MHz   |

|              |                                     | 1.71 V ≤ V <sub>DDD</sub> < 3.3 V                                               | -   | _   | 7 <sup>[72]</sup>   | MHz   |

|              |                                     | $1.71 \text{ V} \le \text{V}_{\text{DDD}} < 3.3 \text{ V},$ SWD over USBIO pins | _   | _   | 5.5 <sup>[72]</sup> | MHz   |

| T_SWDI_setup | SWDIO input setup before SWDCK high | T = 1/f_SWDCK max                                                               | T/4 | _   | -                   | _     |

| T_SWDI_hold  | SWDIO input hold after SWDCK high   | T = 1/f_SWDCK max                                                               | T/4 | _   | -                   | _     |

| T_SWDO_valid | SWDCK high to SWDIO output          | T = 1/f_SWDCK max                                                               | _   | _   | 2T/5                | _     |

### 11.8.6 SWV Interface

# Table 11-72. SWV Interface AC Specifications<sup>[71]</sup>

| Parameter | Description           | Conditions | Min | Тур | Max | Units |

|-----------|-----------------------|------------|-----|-----|-----|-------|

|           | SWV mode SWV bit rate |            | _   | _   | 33  | Mbit  |

#### Notes

<sup>71.</sup> Based on device characterization (Not production tested).

<sup>72.</sup> ff\_SWDCK must also be no more than 1/3 CPU clock frequency.

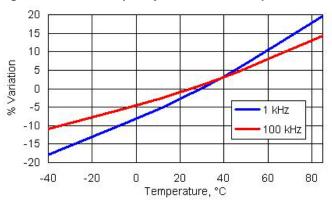

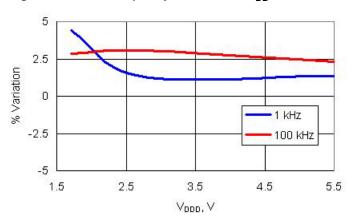

Figure 11-73. ILO Frequency Variation vs. Temperature

Figure 11-74. ILO Frequency Variation vs. V<sub>DD</sub>

# 11.9.3 MHz External Crystal Oscillator

For more information on crystal or ceramic resonator selection for the MHzECO, refer to application note AN54439: PSoC 3 and PSoC 5 External Oscillators..

Table 11-77. MHzECO DC Specifications

| Parameter       | Description                       | Conditions        | Min | Тур | Max | Units |

|-----------------|-----------------------------------|-------------------|-----|-----|-----|-------|

| I <sub>CC</sub> | Operating current <sup>[75]</sup> | 13.56 MHz crystal | -   | 3.8 | _   | mA    |

Table 11-78. MHzECO AC Specifications

| Parameter | Description             | Conditions | Min | Тур | Max | Units |

|-----------|-------------------------|------------|-----|-----|-----|-------|

| F         | Crystal frequency range |            | 4   | -   | 25  | MHz   |

### 11.9.4 kHz External Crystal Oscillator

# Table 11-79. kHzECO DC Specifications<sup>[75]</sup>

| Parameter       | Description       | Conditions                | Min | Тур  | Max | Units |

|-----------------|-------------------|---------------------------|-----|------|-----|-------|

| I <sub>CC</sub> | Operating current | Low-power mode; CL = 6 pF | _   | 0.25 | 1.0 | μΑ    |

| DL              | Drive level       |                           | _   | _    | 1   | μW    |

# Table 11-80. kHzECO AC Specifications

| Parameter       | Description  | Conditions      | Min | Тур    | Max | Units |

|-----------------|--------------|-----------------|-----|--------|-----|-------|

| F               | Frequency    |                 | _   | 32.768 | -   | kHz   |

| T <sub>ON</sub> | Startup time | High-power mode | _   | 1      | _   | S     |

#### Note

5.70±0.10

TOP VIEW SIDE VIEW BOTTOM VIEW 8.00±0.10 52 68 PIN 1 DOT 0.40±0.05 UUUUU 0.20±0.05 17 35 0.05 MAX 1.00 MAX -0.40+0.10

Figure 13-3. 68-pin QFN 8 × 8 with 0.4 mm Pitch Package Outline (Sawn Version)

### NOTES:

- 1. MATCH AREA IS SOLDERABLE EXPOSED METAL.

- 2. REFERENCE JEDEC#: MO-220

- 3. PACKAGE WEIGHT: 17  $\pm$  2mg

- 4. ALL DIMENSIONS ARE IN MILLIMETERS

001-09618 \*E

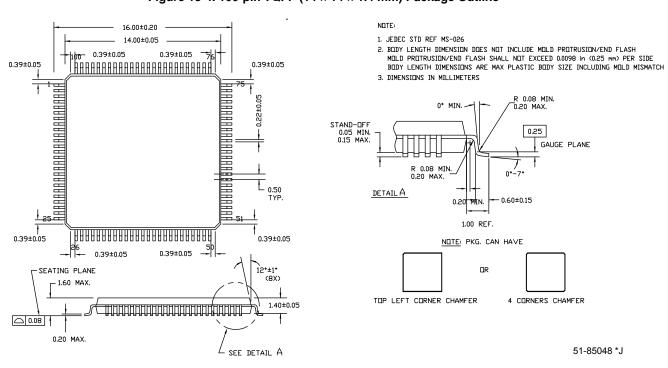

Figure 13-4. 100-pin TQFP (14 x 14 x 1.4 mm) Package Outline

0.08

# PSoC® 3: CY8C34 Family Datasheet

| Revision | ECN     | Submission<br>Date | Orig. of<br>Change | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|----------|---------|--------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| *V       | 4708125 | 03/31/2015         | MKEA               | Added INL4 and DNL4 specs in VDAC DC Specifications. Updated Figure 6-11. Added second note after Figure 6-4. Added a reference to Fig 6-1 in Section 6.1.1 and Section 6.1.2. Updated Section 6.2.2. Added Section 7.8.1. Updated Boost specifications.                                                                                                                                                                                                 |  |

| *W       | 4807497 | 06/23/2015         | MKEA               | Added reference to code examples in More Information. Updated typ value of TWRITE from 2 to 10 in EEPROM AC specs table. Changed "Device supply for USB operation" to "Device supply (VDDD) for USB operation" in USB DC Specifications. Clarified power supply sequencing and margin for VDDA and VDDD. Updated Serial Wire Debug Interface with limitations of debugging on Port 15. Updated Section 11.7.5. Updated Delta-sigma ADC DC Specifications |  |

| *X       | 4932879 | 09/24/2015         | MKEA               | Changed the Regulator Output Capacitor min and max from "-" to 0.9 and 1.7 respectively.  Added reference to AN54439 in Section 11.9.3.  Added MHz ECO DC specs table.  Removed references to IPOR rearm issues in Section 6.3.1.1.  Table 6-1: Changed DSI Fmax to 33 MHz.  Figure 6-1: Changed External I/O or DSI to 0-33 MHz.  Table 11-10: Changed Fgpioin Max to 33 MHz.  Table 11-12: Changed Fsioin Max to 33 MHz.                               |  |

| *Y       | 5322536 | 06/27/2016         | MKEA               | Updated More Information. Corrected typos in External Electrical Connections. Added links to CAD Libraries in Section 2.                                                                                                                                                                                                                                                                                                                                 |  |