#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

·XF

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | 8051                                                                        |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 50MHz                                                                       |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART                          |

| Peripherals                | CapSense, DMA, LCD, POR, PWM, WDT                                           |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 32KB (32K x 8)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 4K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                                |

| Data Converters            | A/D 16x12b; D/A 2x8b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 48-VFQFN Exposed Pad                                                        |

| Supplier Device Package    | 48-QFN (7x7)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c3445lti-078t |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

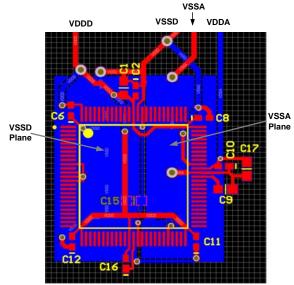

# Figure 2-8. Example PCB Layout for 100-pin TQFP Part for Optimal Analog Performance

# 3. Pin Descriptions

## IDAC0, IDAC2

Low resistance output pin for high current DACs (IDAC).

#### OpAmp0out, OpAmp2out

High current output of uncommitted opamp<sup>[11]</sup>.

#### Extref0, Extref1

External reference input to the analog system.

#### Opamp0-, Opamp2-

Inverting input to uncommitted opamp.

#### Opamp0+, Opamp2+

Noninverting input to uncommitted opamp.

#### GPIO

General purpose I/O pin provides interfaces to the CPU, digital peripherals, analog peripherals, interrupts, LCD segment drive, and CapSense<sup>[11]</sup>.

#### I2C0: SCL, I2C1: SCL

$I^2C$  SCL line providing wake from sleep on an address match. Any I/O pin can be used for  $I^2C$  SCL if wake from sleep is not required.

## I2C0: SDA, I2C1: SDA

$I^2C$  SDA line providing wake from sleep on an address match. Any I/O pin can be used for  $I^2C$  SDA if wake from sleep is not required.

## Ind

Inductor connection to boost pump.

#### kHz XTAL: Xo, kHz XTAL: Xi

32.768-kHz crystal oscillator pin.

Note

11. GPIOs with opamp outputs are not recommended for use with CapSense.

## MHz XTAL: Xo, MHz XTAL: Xi

4- to 25-MHz crystal oscillator pin.

## nTRST

Optional JTAG test reset programming and debug port connection to reset the JTAG connection.

## SIO

Special I/O provides interfaces to the CPU, digital peripherals and interrupts with a programmable high threshold voltage, analog comparator, high sink current, and high impedance state when the device is unpowered.

#### SWDCK

Serial wire debug clock programming and debug port connection.

## SWDIO

Serial wire debug input and output programming and debug port connection.

## SWV

Single wire viewer debug output.

# тск

JTAG test clock programming and debug port connection.

## TDI

JTAG test data In programming and debug port connection.

## TDO

JTAG test data out programming and debug port connection.

## TMS

JTAG test mode select programming and debug port connection.

## 4.3.1.2 Logical Instructions

The logical instructions perform Boolean operations such as AND, OR, XOR on bytes, rotate of accumulator contents, and swap of nibbles in an accumulator. The Boolean operations on the bytes are performed on the bit-by-bit basis. Table 4-2 shows the list of logical instructions and their description.

## Table 4-2. Logical Instructions

|     | Mnemonic      | Description                           | Bytes | Cycles |

|-----|---------------|---------------------------------------|-------|--------|

| ANL | A,Rn          | AND register to accumulator           | 1     | 1      |

| ANL | A,Direct      | AND direct byte to accumulator        | 2     | 2      |

| ANL | A,@Ri         | AND indirect RAM to accumulator       | 1     | 2      |

| ANL | A,#data       | AND immediate data to accumulator     | 2     | 2      |

| ANL | Direct, A     | AND accumulator to direct byte        | 2     | 3      |

| ANL | Direct, #data | AND immediate data to direct byte     | 3     | 3      |

| ORL | A,Rn          | OR register to accumulator            | 1     | 1      |

| ORL | A,Direct      | OR direct byte to accumulator         | 2     | 2      |

| ORL | A,@Ri         | OR indirect RAM to accumulator        | 1     | 2      |

| ORL | A,#data       | OR immediate data to accumulator      | 2     | 2      |

| ORL | Direct, A     | OR accumulator to direct byte         | 2     | 3      |

| ORL | Direct, #data | OR immediate data to direct byte      | 3     | 3      |

| XRL | A,Rn          | XOR register to accumulator           | 1     | 1      |

| XRL | A,Direct      | XOR direct byte to accumulator        | 2     | 2      |

| XRL | A,@Ri         | XOR indirect RAM to accumulator       | 1     | 2      |

| XRL | A,#data       | XOR immediate data to accumulator     | 2     | 2      |

| XRL | Direct, A     | XOR accumulator to direct byte        | 2     | 3      |

| XRL | Direct, #data | XOR immediate data to direct byte     | 3     | 3      |

| CLR | Α             | Clear accumulator                     | 1     | 1      |

| CPL | A             | Complement accumulator                | 1     | 1      |

| RL  | А             | Rotate accumulator left               | 1     | 1      |

| RLC | A             | Rotate accumulator left through carry | 1     | 1      |

| RR  | A             | Rotate accumulator right              | 1     | 1      |

| RRC | А             | Rotate accumulator right though carry | 1     | 1      |

| SWA | PA            | Swap nibbles within accumulator       | 1     | 1      |

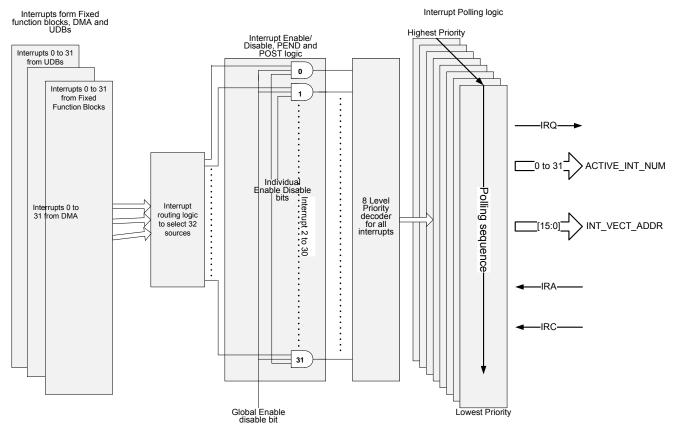

- 6: CPU acknowledges the interrupt request

- 7: ISR address is read by CPU for branching

- 8, 9: PEND and POST bits are cleared respectively after receiving the IRA from core

- 10: IRA bit is cleared after completing the current instruction and starting the instruction execution from ISR location (takes 7 cycles)

- 11: IRC is set to indicate the completion of ISR, Active int. status is restored with previous status

The total interrupt latency (ISR execution)

- = POST + PEND + IRQ + IRA + Completing current instruction and branching

- = 1+1+1+2+7 cycles

- = 12 cycles

Figure 4-3. Interrupt Structure

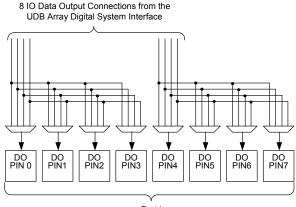

## 7.4.1 I/O Port Routing

There are a total of 20 DSI routes to a typical 8-bit I/O port, 16 for data and four for drive strength control.

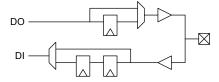

When an I/O pin is connected to the routing, there are two primary connections available, an input and an output. In conjunction with drive strength control, this can implement a bidirectional I/O pin. A data output signal has the option to be single synchronized (pipelined) and a data input signal has the option to be double synchronized. The synchronization clock is the master clock (see Figure 6-1). Normally all inputs from pins are synchronized as this is required if the CPU interacts with the signal or any signal derived from it. Asynchronous inputs have rare uses. An example of this is a feed through of combinational PLD logic from input pins to output pins.

#### Figure 7-11. I/O Pin Synchronization Routing

#### Figure 7-12. I/O Pin Output Connectivity

Port i

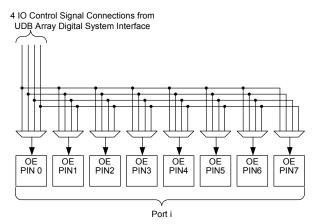

There are four more DSI connections to a given I/O port to implement dynamic output enable control of pins. This connectivity gives a range of options, from fully ganged 8-bits controlled by one signal, to up to four individually controlled pins. The output enable signal is useful for creating tri-state bidirectional pins and buses.

## Figure 7-13. I/O Pin Output Enable Connectivity

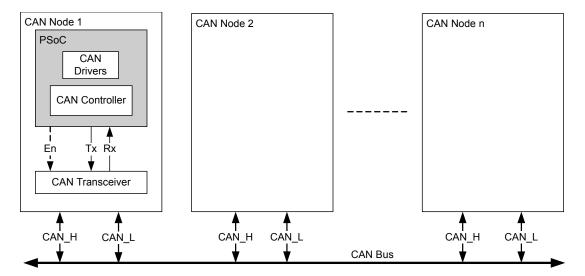

# 7.5 CAN

The CAN peripheral is a fully functional Controller Area Network (CAN) supporting communication baud rates up to 1 Mbps. The CAN controller implements the CAN2.0A and CAN2.0B specifications as defined in the Bosch specification and conforms to the ISO-11898-1 standard. The CAN protocol was originally designed for automotive applications with a focus on a high level of fault detection. This ensures high communication reliability at a low cost. Because of its success in automotive applications, CAN is used as a standard communication protocol for motion oriented machine control networks (CANOpen) and factory automation applications (DeviceNet). The CAN controller features allow the efficient implementation of higher level protocols without affecting the performance of the microcontroller CPU. Full configuration support is provided in PSoC Creator.

Figure 7-14. CAN Bus System Implementation

#### 7.5.1 CAN Features

- CAN2.0A/B protocol implementation ISO 11898 compliant

Standard and extended frames with up to 8 bytes of data per frame

- Message filter capabilities

- Remote Transmission Request (RTR) support

- Programmable bit rate up to 1 Mbps

- Listen Only mode

- SW readable error counter and indicator

- Sleep mode: Wake the device from sleep with activity on the Rx pin

- Supports two or three wire interface to external transceiver (Tx, Rx, and Enable). The three-wire interface is compatible with the Philips PHY; the PHY is not included on-chip. The three wires can be routed to any I/O

- Enhanced interrupt controller

- CAN receive and transmit buffers status

- CAN controller error status including BusOff

- Receive path

- **□** 16 receive buffers each with its own message filter

- Enhanced hardware message filter implementation that covers the ID, IDE and RTR

- DeviceNet addressing support

- Multiple receive buffers linkable to build a larger receive message array

- a Automatic transmission request (RTR) response handler

- Lost received message notification

- Transmit path

- Eight transmit buffers

- Programmable transmit priority

- Round robin

- · Fixed priority

- Message transmissions abort capability

7.5.2 Software Tools Support

CAN Controller configuration integrated into PSoC Creator:

- CAN Configuration walkthrough with bit timing analyzer

- Receive filter setup

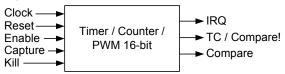

# 7.7 Timers, Counters, and PWMs

The Timer/Counter/PWM peripheral is a 16-bit dedicated peripheral providing three of the most common embedded peripheral features. As almost all embedded systems use some combination of timers, counters, and PWMs. Four of them have been included on this PSoC device family. Additional and more advanced functionality timers, counters, and PWMs can also be instantiated in Universal Digital Blocks (UDBs) as required. PSoC Creator allows you to choose the timer, counter, and PWM features that they require. The tool set utilizes the most optimal resources available.

The Timer/Counter/PWM peripheral can select from multiple clock sources, with input and output signals connected through the DSI routing. DSI routing allows input and output connections to any device pin and any internal digital signal accessible through the DSI. Each of the four instances has a compare output, terminal count output (optional complementary compare output), and programmable interrupt request line. The Timer/Counter/PWMs are configurable as free running, one shot, or Enable input controlled. The peripheral has timer reset and capture inputs, and a kill input for control of the comparator outputs. The peripheral supports full 16-bit capture.

Timer/Counter/PWM features include:

- 16-bit Timer/Counter/PWM (down count only)

- Selectable clock source

- PWM comparator (configurable for LT, LTE, EQ, GTE, GT)

- Period reload on start, reset, and terminal count

- Interrupt on terminal count, compare true, or capture

- Dynamic counter reads

- Timer capture mode

- Count while enable signal is asserted mode

- Free run mode

- One Shot mode (stop at end of period)

- Complementary PWM outputs with deadband

- PWM output kill

#### Figure 7-17. Timer/Counter/PWM

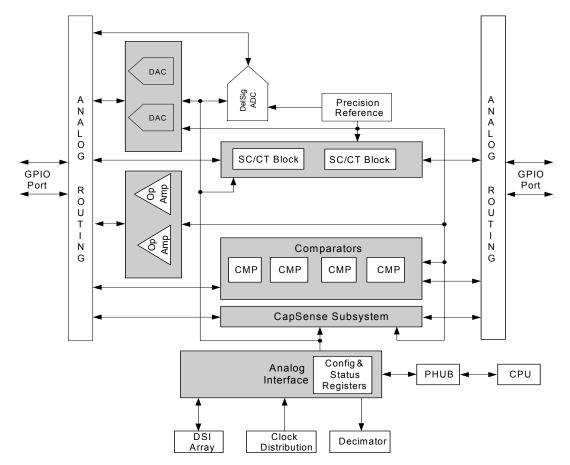

# 8. Analog Subsystem

The analog programmable system creates application specific combinations of both standard and advanced analog signal processing blocks. These blocks are then interconnected to each other and also to any pin on the device, providing a high level of design flexibility and IP security. The features of the analog subsystem are outlined here to provide an overview of capabilities and architecture.

- Flexible, configurable analog routing architecture provided by analog globals, analog mux bus, and analog local buses.

- High resolution Delta-Sigma ADC.

- Two 8-bit DACs that provide either voltage or current output.

- Four comparators with optional connection to configurable LUT outputs.

- Two configurable switched capacitor/continuous time (SC/CT) blocks for functions that include opamp, unity gain buffer, programmable gain amplifier, transimpedance amplifier, and mixer.

- Two opamps for internal use and connection to GPIO that can be used as high current output buffers.

- CapSense subsystem to enable capacitive touch sensing.

- Precision reference for generating an accurate analog voltage for internal analog blocks.

## Figure 8-1. Analog Subsystem Block Diagram

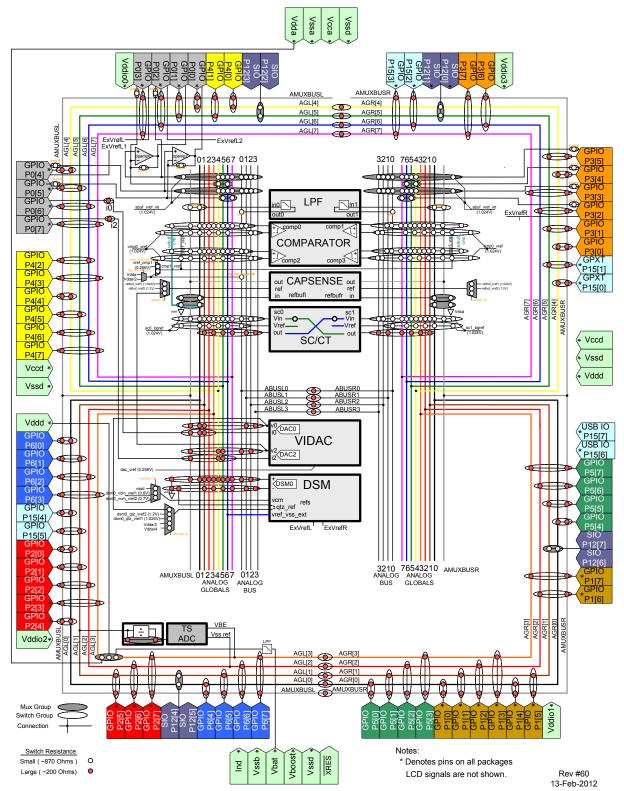

Figure 8-2. CY8C34 Analog Interconnect

To preserve detail of this figure, this figure is best viewed with a PDF display program or printed on a 11" × 17" paper.

Analog local buses (abus) are routing resources located within the analog subsystem and are used to route signals between different analog blocks. There are eight abus routes in CY8C34, four in the left half (abusl [0:3]) and four in the right half (abusr [0:3]) as shown in Figure 8-2. Using the abus saves the analog globals and analog mux buses from being used for interconnecting the analog blocks.

Multiplexers and switches exist on the various buses to direct signals into and out of the analog blocks. A multiplexer can have only one connection on at a time, whereas a switch can have multiple connections on simultaneously. In Figure 8-2, multiplexers are indicated by grayed ovals and switches are indicated by transparent ovals.

## 8.2 Delta-sigma ADC

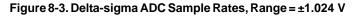

The CY8C34 device contains one delta-sigma ADC. This ADC offers differential input, high resolution and excellent linearity, making it a good ADC choice for measurement applications. The converter can be configured to output 12-bit resolution at data rates of up to 192 ksps. At a fixed clock rate, resolution can be traded for faster data rates as shown in Table 8-1 and Figure 8-3.

| Bits | Maximum Sample Rate<br>(sps) | SINAD (dB) |

|------|------------------------------|------------|

| 12   | 192 k                        | 66         |

| 8    | 384 k                        | 43         |

#### 8.2.1 Functional Description

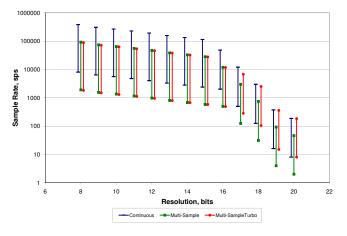

The ADC connects and configures three basic components, input buffer, delta-sigma modulator, and decimator. The basic block diagram is shown in Figure 8-4. The signal from the input muxes is delivered to the delta-sigma modulator either directly or through the input buffer. The delta-sigma modulator performs the actual analog to digital conversion. The modulator over-samples the input and generates a serial data stream output. This high speed data stream is not useful for most applications without some type of post processing, and so is passed to the decimator through the Analog Interface block. The decimator converts the high speed serial data stream into parallel ADC results. The modulator/decimator frequency response is  $[(\sin x)/x]^4$ .

#### Figure 8-4. Delta-sigma ADC Block Diagram

Resolution and sample rate are controlled by the Decimator. Data is pipelined in the decimator; the output is a function of the last four samples. When the input multiplexer is switched, the output data is not valid until after the fourth sample after the switch.

#### 8.2.2 Operational Modes

The ADC can be configured by the user to operate in one of four modes: Single Sample, Multi Sample, Continuous, or Multi Sample (Turbo). All four modes are started by either a write to the start bit in a control register or an assertion of the Start of Conversion (SoC) signal. When the conversion is complete, a status bit is set and the output signal End of Conversion (EoC) asserts high and remains high until the value is read by either the DMA controller or the CPU.

#### 8.2.2.1 Single Sample

In Single Sample mode, the ADC performs one sample conversion on a trigger. In this mode, the ADC stays in standby state waiting for the SoC signal to be asserted. When SoC is signaled the ADC performs four successive conversions. The first three conversions prime the decimator. The ADC result is valid and available after the fourth conversion, at which time the EoC signal is generated. To detect the end of conversion, the system may poll a control register for status or configure the external EoC signal to generate an interrupt or invoke a DMA request. When the transfer is done the ADC reenters the standby state where it stays until another SoC event.

#### 8.2.2.2 Continuous

Continuous sample mode is used to take multiple successive samples of a single input signal. Multiplexing multiple inputs should not be done with this mode. There is a latency of three conversion times before the first conversion result is available. This is the time required to prime the decimator. After the first result, successive conversions are available at the selected sample rate.

#### 8.2.2.3 Multi Sample

Multi sample mode is similar to continuous mode except that the ADC is reset between samples. This mode is useful when the input is switched between multiple signals. The decimator is re-primed between each sample so that previous samples do not affect the current conversion. Upon completion of a sample, the next sample is automatically initiated. The results can be transferred using either firmware polling, interrupt, or DMA.

More information on output formats is provided in the Technical Reference Manual.

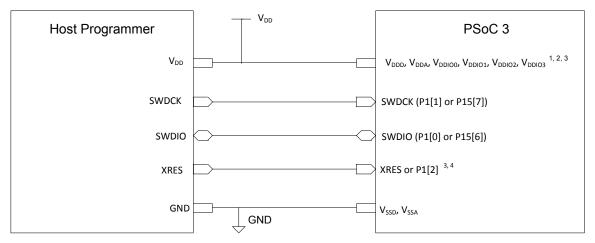

# 9.2 Serial Wire Debug Interface

The SWD interface is the preferred alternative to the JTAG interface. It requires only two pins instead of the four or five needed by JTAG. SWD provides all of the programming and debugging features of JTAG at the same speed. SWD does not provide access to scan chains or device chaining. The SWD clock frequency can be up to 1/3 of the CPU clock frequency.

SWD uses two pins, either two of the JTAG pins (TMS and TCK) or the USBIO D+ and D– pins. The USBIO pins are useful for in system programming of USB solutions that would otherwise require a separate programming connector. One pin is used for the data clock and the other is used for data input and output.

SWD can be enabled on only one of the pin pairs at a time. This only happens if, within 8  $\mu$ s (key window) after reset, that pin pair

(JTAG or USB) receives a predetermined acquire sequence of 1s and 0s. If the NVL latches are set for SWD (see Section 5.5), this sequence need not be applied to the JTAG pin pair. The acquire sequence must always be applied to the USB pin pair.

SWD is used for debugging or for programming the flash memory.

The SWD interface can be enabled from the JTAG interface or disabled, allowing its pins to be used as GPIO. Unlike JTAG, the SWD interface can always be reacquired on any device during the key window. It can then be used to reenable the JTAG interface, if desired. When using SWD or JTAG pins as standard GPIO, make sure that the GPIO functionality and PCB circuits do not interfere with SWD or JTAG use.

## Figure 9-2. SWD Interface Connections between PSoC 3 and Programmer

<sup>1</sup> The voltage levels of the Host Programmer and the PSoC 3 voltage domains involved in Programming should be the same. XRES pin (XRES\_N or P1[2]) is powered by V<sub>DDI01</sub>. The USB SWD pins are powered by V<sub>DDD</sub>. So for Programming using the USB SWD pins with XRES pin, the V<sub>DDD</sub>, V<sub>DDI01</sub> of PSoC 3 should be at the same voltage level as Host V<sub>DD</sub>. Rest of PSoC 3 voltage domains (V<sub>DDA</sub>, V<sub>DDI00</sub>, V<sub>DDI02</sub>, V<sub>DDI03</sub>) need not be at the same voltage level as host Programmer. The Port 1 SWD pins are powered by V<sub>DDI01</sub>. So V<sub>DDI01</sub> of PSoC 3 should be at same voltage level as host Programmer. The Port 1 SWD pins are powered by V<sub>DDI01</sub>. So V<sub>DDI01</sub> of PSoC 3 voltage domains (V<sub>DDA</sub>, V<sub>DDI02</sub>, V<sub>DDI02</sub>, V<sub>DDI03</sub>) need not be at the same voltage level as host Programming. Rest of PSoC 3 voltage domains (V<sub>DDD</sub>, V<sub>DDA</sub>, V<sub>DDI00</sub>, V<sub>DDI02</sub>, V<sub>DDI01</sub>, Rest of PSoC 3 voltage domains (V<sub>DDD</sub>, V<sub>DDA</sub>, V<sub>DDI02</sub>, V<sub>DDI03</sub>) need not be at the same voltage level as host Programmer.

<sup>2</sup> Vdda must be greater than or equal to all other power supplies (Vddd, Vddio's) in PSoC 3.

- <sup>3</sup> For Power cycle mode Programming, XRES pin is not required. But the Host programmer must have the capability to toggle power (Vddd, Vdda, All Vddio's) to PSoC 3. This may typically require external interface circuitry to toggle power which will depend on the programming setup. The power supplies can be brought up in any sequence, however, once stable, VDDA must be greater than or equal to all other supplies.

- <sup>4</sup> P1[2] will be configured as XRES by default only for 48-pin devices (without dedicated XRES pin). For devices with dedicated XRES pin, P1[2] is GPIO pin by default. So use P1[2] as Reset pin only for 48pin devices, but use dedicated XRES pin for rest of devices.

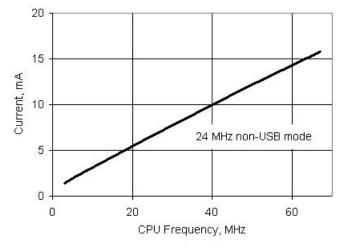

Figure 11-1. Active Mode Current vs  $F_{CPU}$ ,  $V_{DD}$  = 3.3 V, Temperature = 25 °C

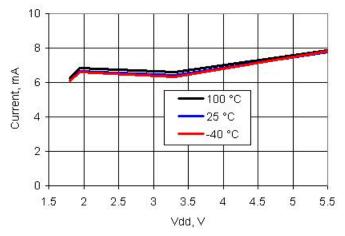

Figure 11-3. Active Mode Current vs V<sub>DD</sub> and Temperature, F<sub>CPU</sub> = 24 MHz

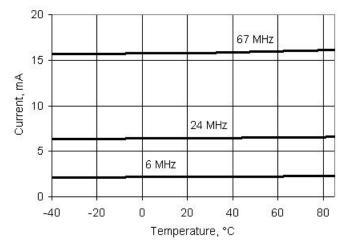

Figure 11-2. Active Mode Current vs Temperature and F<sub>CPU</sub>,  $V_{DD} = 3.3 V$

#### Notes

28. If V<sub>CCD</sub> and V<sub>CCA</sub> are externally regulated, the voltage difference between V<sub>CCD</sub> and V<sub>CCA</sub> must be less than 50 mV.

29. Sleep timer generates periodic interrupts to wake up the CPU. This specification applies only to those times that the CPU is off.

30. Externally regulated mode.

- 31. Based on device characterization (not production tested).

- 32. Based on device characterization (not production tested). USBIO pins tied to ground (VSSD).

# 11.4.4 XRES

## Table 11-17. XRES DC Specifications

| Parameter       | Description                                                   | Conditions | Min                   | Тур | Max                   | Units |

|-----------------|---------------------------------------------------------------|------------|-----------------------|-----|-----------------------|-------|

| V <sub>IH</sub> | Input voltage high threshold                                  |            | $0.7 \times V_{DDIO}$ | -   | -                     | V     |

| V <sub>IL</sub> | Input voltage low threshold                                   |            | -                     | -   | $0.3 \times V_{DDIO}$ | V     |

| Rpullup         | Pull-up resistor                                              |            | 3.5                   | 5.6 | 8.5                   | kΩ    |

| C <sub>IN</sub> | Input capacitance <sup>[46]</sup>                             |            | -                     | 3   | -                     | pF    |

| V <sub>H</sub>  | Input voltage hysteresis<br>(Schmitt-Trigger) <sup>[46]</sup> |            | -                     | 100 | _                     | mV    |

| Idiode          | Current through protection diode to $V_{DDIO}$ and $V_{SSIO}$ |            | -                     | _   | 100                   | μA    |

## Table 11-18. XRES AC Specifications

| Parameter          | Description       | Conditions | Min | Тур | Max | Units |

|--------------------|-------------------|------------|-----|-----|-----|-------|

| T <sub>RESET</sub> | Reset pulse width |            | 1   | -   | -   | μs    |

<sup>46.</sup> Based on device characterization (Not production tested).

# 11.5 Analog Peripherals

Specifications are valid for –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C and T<sub>J</sub>  $\leq$  100 °C, except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted.

## 11.5.1 Opamp

# Table 11-19. Opamp DC Specifications

| Parameter         | Description                                 | Conditions                                                                                                                                                                                                      | Min                     | Тур  | Max                     | Units |

|-------------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------|-------------------------|-------|

| V <sub>IOFF</sub> | Input offset voltage                        |                                                                                                                                                                                                                 | -                       | -    | 2                       | mV    |

| Vos               | Input offset voltage                        |                                                                                                                                                                                                                 | -                       | -    | 2.5                     | mV    |

|                   |                                             | Operating temperature –40 °C to 70 °C                                                                                                                                                                           | -                       | -    | 2                       | mV    |

| TCVos             | Input offset voltage drift with temperature | Power mode = high                                                                                                                                                                                               | -                       | -    | ±30                     | µV/°C |

| Ge1               | Gain error, unity gain buffer mode          | Rload = 1 kΩ                                                                                                                                                                                                    | -                       | -    | ±0.1                    | %     |

| Cin               | Input capacitance                           | Routing from pin                                                                                                                                                                                                | -                       | -    | 18                      | pF    |

| Vo                | Output voltage range                        | 1 mA, source or sink, power mode = high                                                                                                                                                                         | V <sub>SSA</sub> + 0.05 | -    | V <sub>DDA</sub> – 0.05 | V     |

| lout              | Output current capability, source or sink   | $V_{SSA}$ + 500 mV $\leq$ Vout $\leq$ V <sub>DDA</sub><br>-500 mV, V <sub>DDA</sub> > 2.7 V                                                                                                                     | 25                      | -    | -                       | mA    |

|                   |                                             | $\label{eq:VSSA} \begin{array}{l} \text{V}_{\text{SSA}} \mbox{ + 500 mV} \leq \mbox{Vout} \leq \mbox{V}_{\text{DDA}} \\ -500 \mbox{ mV}, \mbox{ 1.7 V} \mbox{ = V}_{\text{DDA}} \leq \mbox{ 2.7 V} \end{array}$ | 16                      | -    | -                       | mA    |

| ldd               | Quiescent current                           | Power mode = min                                                                                                                                                                                                | -                       | 250  | 400                     | uA    |

|                   |                                             | Power mode = low                                                                                                                                                                                                | -                       | 250  | 400                     | uA    |

|                   |                                             | Power mode = med                                                                                                                                                                                                | -                       | 330  | 950                     | uA    |

|                   |                                             | Power mode = high                                                                                                                                                                                               | -                       | 1000 | 2500                    | uA    |

| CMRR              | Common mode rejection ratio                 |                                                                                                                                                                                                                 | 80                      | -    | -                       | dB    |

| PSRR              | Power supply rejection ratio                | $V_{DDA} \ge 2.7 V$                                                                                                                                                                                             | 85                      | -    | -                       | dB    |

|                   |                                             | V <sub>DDA</sub> < 2.7 V                                                                                                                                                                                        | 70                      | -    | -                       | dB    |

| I <sub>IB</sub>   | Input bias current <sup>[47]</sup>          | 25 °C                                                                                                                                                                                                           | -                       | 10   | -                       | pА    |

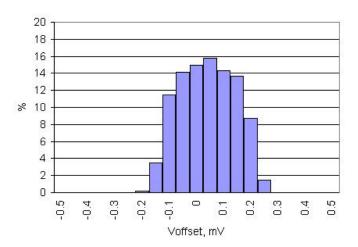

Figure 11-25. Opamp Voffset Histogram, 3388 samples/847 parts, 25 °C,  $V_{DDA}$  = 5 V

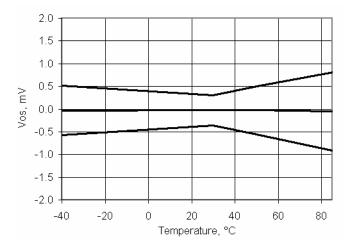

Figure 11-26. Opamp Voffset vs Temperature, V<sub>DDA</sub> = 5V

#### Note

47. Based on device characterization (Not production tested).

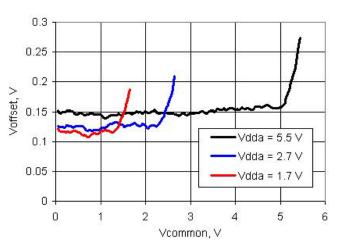

Figure 11-27. Opamp Voffset vs Vcommon and V<sub>DDA</sub>, 25 °C

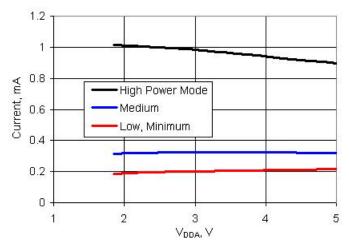

Figure 11-29. Opamp Operating Current vs  $V_{\mbox{\scriptsize DDA}}$  and Power Mode

Table 11-20. Opamp AC Specifications

| Parameter      | Description            | Conditions                                               | Min | Тур | Max | Units     |

|----------------|------------------------|----------------------------------------------------------|-----|-----|-----|-----------|

| GBW            | Gain-bandwidth product | Power mode = minimum, 15 pF load                         | 1   | -   | -   | MHz       |

|                |                        | Power mode = low, 15 pF load                             | 2   | -   | -   | MHz       |

|                |                        | Power mode = medium, 200 pF load                         | 1   | -   | -   | MHz       |

|                |                        | Power mode = high, 200 pF load                           | 3   | -   | -   | MHz       |

| SR             | Slew rate, 20% - 80%   | Power mode = low, 15 pF load                             | 1.1 | -   | -   | V/µs      |

|                |                        | Power mode = medium, 200 pF load                         | 0.9 | -   | -   | V/µs      |

|                |                        | Power mode = high, 200 pF load                           | 3   | -   | -   | V/µs      |

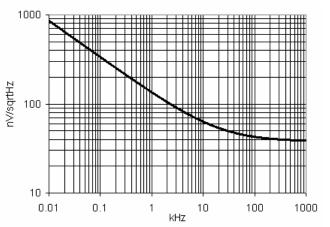

| e <sub>n</sub> | Input noise density    | Power mode = high, V <sub>DDA</sub> = 5 V,<br>at 100 kHz | _   | 45  | -   | nV/sqrtHz |

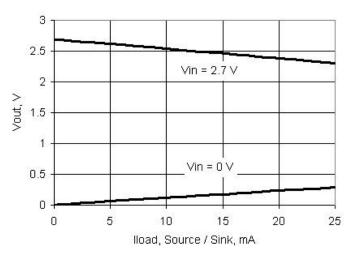

Figure 11-28. Opamp Output Voltage vs Load Current and Temperature, High Power Mode, 25 °C,  $V_{DDA}$  = 2.7 V

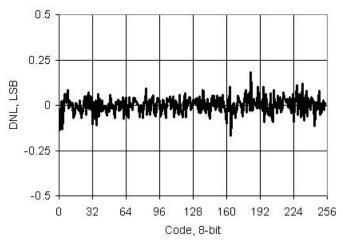

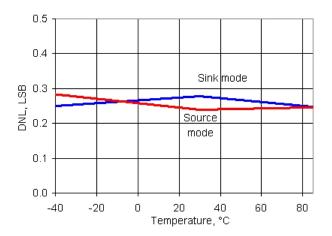

Figure 11-36. IDAC DNL vs Input Code, Range = 255  $\mu$ A, Source Mode

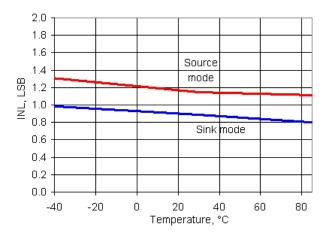

Figure 11-38. IDAC INL vs Temperature, Range = 255  $\mu A$ , High speed mode

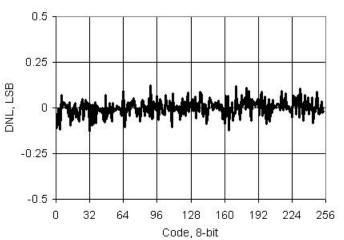

Figure 11-37. IDAC DNL vs Input Code, Range = 255  $\mu\text{A},$  Sink Mode

Figure 11-39. IDAC DNL vs Temperature, Range = 255  $\mu\text{A},$  High speed mode

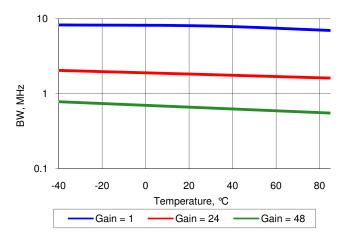

## Table 11-37. PGA AC Specifications

| Parameter      | Description         | Conditions                                                     | Min | Тур | Max | Units     |

|----------------|---------------------|----------------------------------------------------------------|-----|-----|-----|-----------|

| BW1            | –3 dB bandwidth     | Power mode = high,<br>gain = 1, input = 100 mV<br>peak-to-peak | 6.7 | 8   | -   | MHz       |

| SR1            | Slew rate           | Power mode = high,<br>gain = 1, 20% to 80%                     | 3   | _   | _   | V/µs      |

| e <sub>n</sub> | Input noise density | Power mode = high,<br>V <sub>DDA</sub> = 5 V, at 100 kHz       | -   | 43  | _   | nV/sqrtHz |

# Figure 11-61. Bandwidth vs. Temperature, at Different Gain Settings, Power Mode = High

Figure 11-62. Noise vs. Frequency,  $V_{DDA} = 5 V$ , Power Mode = High

## 11.5.11 Temperature Sensor

#### Table 11-38. Temperature Sensor Specifications

| Parameter | Description          | Conditions              | Min | Тур | Max | Units |

|-----------|----------------------|-------------------------|-----|-----|-----|-------|

|           | Temp sensor accuracy | Range: –40 °C to +85 °C | _   | ±5  | -   | °C    |

## 11.5.12 LCD Direct Drive

## Table 11-39. LCD Direct Drive DC Specifications

| Parameter           | Description                                                                         | Conditions                                                                                                                                                                                 | Min | Тур                    | Max  | Units |

|---------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------------|------|-------|

| I <sub>CC</sub>     | LCD system operating current                                                        | Device sleep mode with wakeup at 400-Hz rate to refresh LCDs, bus clock = 3 Mhz, $V_{DDIO} = V_{DDA} = 3 V$ , 4 commons, 16 segments, 1/4 duty cycle, 50 Hz frame rate, no glass connected | _   | 38                     | -    | μΑ    |

| I <sub>CC SEG</sub> | Current per segment driver                                                          | Strong drive mode                                                                                                                                                                          | -   | 260                    | -    | μA    |

| V <sub>BIAS</sub>   | LCD bias range (V <sub>BIAS</sub> refers to the main output voltage(V0) of LCD DAC) | $V_{DDA} \ge 3 \text{ V} \text{ and } V_{DDA} \ge V_{BIAS}$                                                                                                                                | 2   | -                      | 5    | V     |

|                     | LCD bias step size                                                                  | $V_{DDA} \ge 3 \text{ V} \text{ and } V_{DDA} \ge V_{BIAS}$                                                                                                                                | -   | 9.1 × V <sub>DDA</sub> | -    | mV    |

|                     | LCD capacitance per<br>segment/common driver                                        | Drivers may be combined                                                                                                                                                                    | _   | 500                    | 5000 | pF    |

|                     | Long term segment offset                                                            |                                                                                                                                                                                            | -   | -                      | 20   | mV    |

| I <sub>OUT</sub>    | Output drive current per segment driver)                                            | V <sub>DDIO</sub> = 5.5 V, strong drive mode                                                                                                                                               | 355 | -                      | 710  | μA    |

#### Table 11-40. LCD Direct Drive AC Specifications

| Parameter        | Description    | Conditions | Min | Тур | Max | Units |

|------------------|----------------|------------|-----|-----|-----|-------|

| f <sub>LCD</sub> | LCD frame rate |            | 10  | 50  | 150 | Hz    |

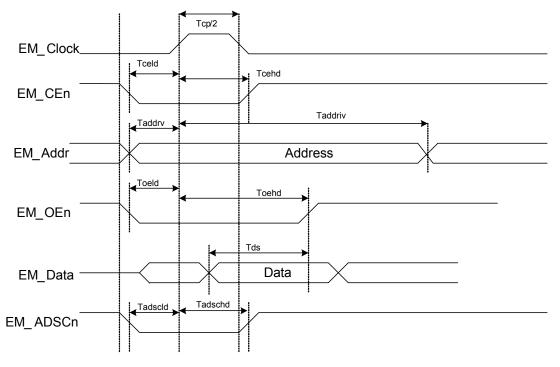

Figure 11-66. Synchronous Read Cycle Timing

# Table 11-63. Synchronous Read Cycle Specifications

| Parameter | Description                       | Conditions          | Min     | Тур | Max | Units |

|-----------|-----------------------------------|---------------------|---------|-----|-----|-------|

| Т         | EMIF clock period <sup>[66]</sup> | $V_{DDA} \ge 3.3 V$ | 30.3    | -   | -   | ns    |

| Tcp/2     | EM_Clock pulse high               |                     | T/2     | -   | -   | ns    |

| Tceld     | EM_CEn low to EM_Clock high       |                     | 5       | -   | -   | ns    |

| Tcehd     | EM_Clock high to EM_CEn high      |                     | T/2 – 5 | -   | -   | ns    |

| Taddrv    | EM_Addr valid to EM_Clock high    |                     | 5       | -   | -   | ns    |

| Taddriv   | EM_Clock high to EM_Addr invalid  |                     | T/2 – 5 | -   | -   | ns    |

| Toeld     | EM_OEn low to EM_Clock high       |                     | 5       | -   | -   | ns    |

| Toehd     | EM_Clock high to EM_OEn high      |                     | Т       | -   | -   | ns    |

| Tds       | Data valid before EM_OEn high     |                     | T + 15  | -   | -   | ns    |

| Tadscld   | EM_ADSCn low to EM_Clock high     |                     | 5       | -   | -   | ns    |

| Tadschd   | EM_Clock high to EM_ADSCn high    |                     | T/2 – 5 | _   | _   | ns    |

# 11.9 Clocking

Specifications are valid for –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C and T<sub>J</sub>  $\leq$  100 °C, except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted.

11.9.1 Internal Main Oscillator

## Table 11-73. IMO DC Specifications

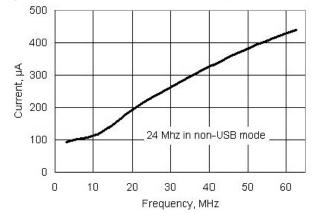

| Parameter | Description           | Conditions                         | Min | Тур | Max | Units |  |

|-----------|-----------------------|------------------------------------|-----|-----|-----|-------|--|

|           | Supply current        |                                    |     |     |     |       |  |

|           | 24 MHz – USB mode     | With oscillator locking to USB bus | -   | -   | 500 | μA    |  |

|           | 24 MHz – non USB mode |                                    | _   | -   | 300 | μA    |  |

|           | 12 MHz                |                                    | -   | -   | 200 | μA    |  |

|           | 6 MHz                 |                                    | -   | -   | 180 | μA    |  |

|           | 3 MHz                 |                                    | -   | -   | 150 | μA    |  |

## Figure 11-70. IMO Current vs. Frequency

## Table 11-74. IMO AC Specifications

| Parameter | Description                                 | Conditions                                   | Min   | Тур | Max  | Units |  |  |  |

|-----------|---------------------------------------------|----------------------------------------------|-------|-----|------|-------|--|--|--|

| FIMO      | IMO frequency stability (with factory trim) |                                              |       |     |      |       |  |  |  |

|           | 24 MHz – Non USB mode                       |                                              | -4    | -   | 4    | %     |  |  |  |

|           | 24 MHz – USB mode                           | With oscillator locking to USB bus           | -0.25 | _   | 0.25 | %     |  |  |  |

|           | 12 MHz                                      |                                              | -3    | -   | 3    | %     |  |  |  |

|           | 6 MHz                                       |                                              | -2    | _   | 2    | %     |  |  |  |

|           | 3 MHz                                       |                                              | -2    | _   | 2    | %     |  |  |  |

|           | Startup time <sup>[73]</sup>                | From enable (during normal system operation) | -     | _   | 13   | μs    |  |  |  |

| Јр-р      | Jitter (peak to peak) <sup>[73]</sup>       |                                              |       |     |      |       |  |  |  |

|           | F = 24 MHz                                  |                                              | -     | 0.9 | _    | ns    |  |  |  |

|           | F = 3 MHz                                   |                                              | I     | 1.6 | _    | ns    |  |  |  |

| Jperiod   | Jitter (long term) <sup>[73]</sup>          |                                              |       |     |      |       |  |  |  |

|           | F = 24 MHz                                  |                                              | _     | 0.9 | -    | ns    |  |  |  |

|           | F = 3 MHz                                   |                                              | -     | 12  | -    | ns    |  |  |  |

Note

73. Based on device characterization (Not production tested).

| Revision | ECN     | Submission<br>Date | Orig. of<br>Change | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------|---------|--------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| *N       | 3645908 | 06/14/2012         | MKEA               | Added paragraph clarifying that to achieve low hibernate current, you must limit the frequency of IO input signals.         Revised description of IPOR and clarified PRES term.         Changed footnote to state that all GPIO input voltages - not just analog voltages - must be less than Vddio.         Updated 100-TQFP package drawing         Clarified description of opamp lout spec         Changed "compliant with I2C" to "compatible with I2C"         Updated 48-OFN package drawing         Changed reset status register description text to clarify that not all reset sources are in the register         Updated example PCB layout figure         Removed text stating that FTW is a wakeup source         Changed onp rate spec from 1 V/ns to 0.066 V/µs         Added "based on char" footnote to voltage monitors response time spec         Changed analog global spec descriptions and values         Added spec for ESDhbm for when Vssa and Vssd are separate         Added text describing flash cache, and updated related text         Changed comparator specs and conditions         Added a statement about support for JTAG programmers and file formats.         Changed text and added figures describing Vddio source and sink         Added text doscribing Vddio source and sink         Added text on adjustability of buzz frequency         Updated terminology for "master" and "system" clock         Deleted the text "debug operations are possible while the device is res |

| *0       | 3648803 | 06/18/2012         | WKA/               | No changes. EROS update.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Description Document | Description Title: PSoC <sup>®</sup> 3: CY8C34 Family Datasheet Programmable System-on-Chip (PSoC <sup>®</sup> ) (continued)<br>Document Number: 001-53304 |                    |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Revision             | ECN                                                                                                                                                        | Submission<br>Date | Orig. of<br>Change | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| *V                   | 4708125                                                                                                                                                    | 03/31/2015         | MKEA               | Added INL4 and DNL4 specs in VDAC DC Specifications.<br>Updated Figure 6-11.<br>Added second note after Figure 6-4.<br>Added a reference to Fig 6-1 in Section 6.1.1 and Section 6.1.2.<br>Updated Section 6.2.2.<br>Added Section 7.8.1.<br>Updated Boost specifications.                                                                                                                                                                                                    |  |  |  |

| *W                   | 4807497                                                                                                                                                    | 06/23/2015         | MKEA               | Added reference to code examples in More Information.<br>Updated typ value of TWRITE from 2 to 10 in EEPROM AC specs table.<br>Changed "Device supply for USB operation" to "Device supply (VDDD) for USB<br>operation" in USB DC Specifications.<br>Clarified power supply sequencing and margin for VDDA and VDDD.<br>Updated Serial Wire Debug Interface with limitations of debugging on Port 15.<br>Updated Section 11.7.5.<br>Updated Delta-sigma ADC DC Specifications |  |  |  |

| *X                   | 4932879                                                                                                                                                    | 09/24/2015         | MKEA               | Changed the Regulator Output Capacitor min and max from "-" to 0.9 and 1.1,<br>respectively.<br>Added reference to AN54439 in Section 11.9.3.<br>Added MHz ECO DC specs table.<br>Removed references to IPOR rearm issues in Section 6.3.1.1.<br>Table 6-1: Changed DSI Fmax to 33 MHz.<br>Figure 6-1: Changed External I/O or DSI to 0-33 MHz.<br>Table 11-10: Changed Fgpioin Max to 33 MHz.<br>Table 11-12: Changed Fsioin Max to 33 MHz.                                  |  |  |  |

| *Y                   | 5322536                                                                                                                                                    | 06/27/2016         | MKEA               | Updated More Information.<br>Corrected typos in External Electrical Connections.<br>Added links to CAD Libraries in Section 2.                                                                                                                                                                                                                                                                                                                                                |  |  |  |