Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | 8051                                                                       |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 50MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                    |

| Peripherals                | CapSense, DMA, LCD, POR, PWM, WDT                                          |

| Number of I/O              | 38                                                                         |

| Program Memory Size        | 32KB (32K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 4K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                               |

| Data Converters            | A/D 16x12b; D/A 2x8b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 68-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 68-QFN (8x8)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c3445lti-081 |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 4.3.1.3 Data Transfer Instructions

The data transfer instructions are of three types: the core RAM, xdata RAM, and the lookup tables. The core RAM transfer includes transfer between any two core RAM locations or SFRs. These instructions can use direct, indirect, register, and immediate addressing. The xdata RAM transfer includes only the transfer between the accumulator and the xdata RAM location. It can use only indirect addressing. The lookup tables involve nothing but the read of program memory using the Indexed addressing mode. Table 4-3 lists the various data transfer instructions available.

## 4.3.1.4 Boolean Instructions

The 8051 core has a separate bit addressable memory location. It has 128 bits of bit-addressable RAM and a set of SFRs that are bit addressable. The instruction set includes the whole menu of bit operations such as move, set, clear, toggle, OR, and AND instructions and the conditional jump instructions. Table 4-4 on page 16 lists the available Boolean instructions.

Dutes Cusies

| Table 4-3. Data Transfer Instructions |  |  |  |

|---------------------------------------|--|--|--|

| Mnemonic                              |  |  |  |

|      | Mnemonic       | Description                                            | Bytes | Cycles |

|------|----------------|--------------------------------------------------------|-------|--------|

| MOV  | A,Rn           | Move register to accumulator                           | 1     | 1      |

| MOV  | A,Direct       | Move direct byte to accumulator                        | 2     | 2      |

| MOV  | A,@Ri          | Move indirect RAM to accumulator                       | 1     | 2      |

| MOV  | A,#data        | Move immediate data to accumulator                     | 2     | 2      |

| MOV  | Rn,A           | Move accumulator to register                           | 1     | 1      |

| MOV  | Rn,Direct      | Move direct byte to register                           | 2     | 3      |

| MOV  | Rn, #data      | Move immediate data to register                        | 2     | 2      |

| MOV  | Direct, A      | Move accumulator to direct byte                        | 2     | 2      |

| MOV  | Direct, Rn     | Move register to direct byte                           | 2     | 2      |

| MOV  | Direct, Direct | Move direct byte to direct byte                        | 3     | 3      |

| MOV  | Direct, @Ri    | Move indirect RAM to direct byte                       | 2     | 3      |

| MOV  | Direct, #data  | Move immediate data to direct byte                     | 3     | 3      |

| MOV  | @Ri, A         | Move accumulator to indirect RAM                       | 1     | 2      |

| MOV  | @Ri, Direct    | Move direct byte to indirect RAM                       | 2     | 3      |

| MOV  | @Ri, #data     | Move immediate data to indirect RAM                    | 2     | 2      |

| MOV  | DPTR, #data16  | Load data pointer with 16-bit constant                 | 3     | 3      |

| MOVC | CA, @A+DPTR    | Move code byte relative to DPTR to accumulator         | 1     | 5      |

| MOVC | C A, @A + PC   | Move code byte relative to PC to accumulator           | 1     | 4      |

| MOVX | ( A,@Ri        | Move external RAM (8-bit) to accumulator               | 1     | 4      |

| MOVX | ( A, @DPTR     | Move external RAM (16-bit) to accumulator              | 1     | 3      |

| MOVX | ( @Ri, A       | Move accumulator to external RAM (8-bit)               | 1     | 5      |

| MOVX | ( @DPTR, A     | Move accumulator to external RAM (16-bit)              | 1     | 4      |

| PUSH | Direct         | Push direct byte onto stack                            | 2     | 3      |

| POP  | Direct         | Pop direct byte from stack                             | 2     | 2      |

| XCH  | A, Rn          | Exchange register with accumulator                     | 1     | 2      |

| XCH  | A, Direct      | Exchange direct byte with accumulator                  | 2     | 3      |

| XCH  | A, @Ri         | Exchange indirect RAM with accumulator                 | 1     | 3      |

| XCHD | A, @Ri         | Exchange low order indirect digit RAM with accumulator | 1     | 3      |

Description

#### Table 4-4. Boolean Instructions

| Mnemonic Description |                                         | Bytes | Cycles |

|----------------------|-----------------------------------------|-------|--------|

| CLR C                | Clear carry                             | 1     | 1      |

| CLR bit              | Clear direct bit                        | 2     | 3      |

| SETB C               | Set carry                               | 1     | 1      |

| SETB bit             | Set direct bit                          | 2     | 3      |

| CPL C                | Complement carry                        | 1     | 1      |

| CPL bit              | Complement direct bit                   | 2     | 3      |

| ANL C, bit           | AND direct bit to carry                 | 2     | 2      |

| ANL C, /bit          | AND complement of direct bit to carry   | 2     | 2      |

| ORL C, bit           | OR direct bit to carry                  | 2     | 2      |

| ORL C, /bit          | OR complement of direct bit to carry    | 2     | 2      |

| MOV C, bit           | Move direct bit to carry                | 2     | 2      |

| MOV bit, C           | Move carry to direct bit                | 2     | 3      |

| JC rel               | Jump if carry is set                    | 2     | 3      |

| JNC rel              | Jump if no carry is set                 |       | 3      |

| JB bit, rel          | Jump if direct bit is set               | 3     | 5      |

| JNB bit, rel         | Jump if direct bit is not set           | 3     | 5      |

| JBC bit, rel         | Jump if direct bit is set and clear bit | 3     | 5      |

## 4.3.1.5 Program Branching Instructions

The 8051 supports a set of conditional and unconditional jump instructions that help to modify the program execution flow. Table 4-5 shows the list of jump instructions.

## Table 4-5. Jump Instructions

| Mnemonic             | Description                                                  | Bytes | Cycles |

|----------------------|--------------------------------------------------------------|-------|--------|

| ACALL addr11         | Absolute subroutine call                                     | 2     | 4      |

| LCALL addr16         | Long subroutine call                                         | 3     | 4      |

| RET                  | Return from subroutine                                       | 1     | 4      |

| RETI                 | Return from interrupt                                        | 1     | 4      |

| AJMP addr11          | Absolute jump                                                | 2     | 3      |

| LJMP addr16          | Long jump                                                    | 3     | 4      |

| SJMP rel             | Short jump (relative address)                                | 2     | 3      |

| JMP @A + DPTR        | Jump indirect relative to DPTR                               | 1     | 5      |

| JZ rel               | Jump if accumulator is zero                                  | 2     | 4      |

| JNZ rel              | Jump if accumulator is nonzero                               | 2     | 4      |

| CJNE A,Direct, rel   | Compare direct byte to accumulator and jump if not equal     | 3     | 5      |

| CJNE A, #data, rel   | Compare immediate data to accumulator and jump if not equal  | 3     | 4      |

| CJNE Rn, #data, rel  | Compare immediate data to register and jump if not equal     | 3     | 4      |

| CJNE @Ri, #data, rel | Compare immediate data to indirect RAM and jump if not equal | 3     | 5      |

| DJNZ Rn,rel          | Decrement register and jump if not zero                      | 2     | 4      |

| DJNZ Direct, rel     | Decrement direct byte and jump if not zero                   | 3     | 5      |

| NOP                  | No operation                                                 | 1     | 1      |

## 5. Memory

## 5.1 Static RAM

CY8C34 Static RAM (SRAM) is used for temporary data storage. Up to 8 KB of SRAM is provided and can be accessed by the 8051 or the DMA controller. See Memory Map on page 25. Simultaneous access of SRAM by the 8051 and the DMA controller is possible if different 4-KB blocks are accessed.

## 5.2 Flash Program Memory

Flash memory in PSoC devices provides nonvolatile storage for user firmware, user configuration data, bulk data storage, and optional ECC data. The main flash memory area contains up to 64 KB of user program space.

Up to an additional 8 KB of flash space is available for Error Correcting Codes (ECC). If ECC is not used this space can store device configuration data and bulk user data. User code may not be run out of the ECC flash memory section. ECC can correct one bit error and detect two bit errors per 8 bytes of firmware memory; an interrupt can be generated when an error is detected.

The CPU reads instructions located in flash through a cache controller. This improves instruction execution rate and reduces system power consumption by requiring less frequent flash access. The cache has 8 lines at 64 bytes per line for a total of 512 bytes. It is fully associative, automatically controls flash power, and can be enabled or disabled. If ECC is enabled, the cache controller also performs error checking and correction, and interrupt generation.

Flash programming is performed through a special interface and preempts code execution out of flash. The flash programming interface performs flash erasing, programming and setting code protection levels. Flash in-system serial programming (ISSP), typically used for production programming, is possible through both the SWD and JTAG interfaces. In-system programming, typically used for bootloaders, is also possible using serial interfaces such as I<sup>2</sup>C, USB, UART, and SPI, or any communications protocol.

#### 5.3 Flash Security

All PSoC devices include a flexible flash-protection model that prevents access and visibility to on-chip flash memory. This prevents duplication or reverse engineering of proprietary code. Flash memory is organized in blocks, where each block contains 256 bytes of program or data and 32 bytes of ECC or configuration data. A total of up to 256 blocks is provided on 64-KB flash devices.

The device offers the ability to assign one of four protection levels to each row of flash. Table 5-1 lists the protection modes available. Flash protection levels can only be changed by performing a complete flash erase. The Full Protection and Field Upgrade settings disable external access (through a debugging tool such as PSoC Creator, for example). If your application requires code update through a boot loader, then use the Field Upgrade setting. Use the Unprotected setting only when no security is needed in your application. The PSoC device also offers an advanced security feature called Device Security which permanently disables all test, programming, and debug ports, protecting your application from external access (see the "Device Security" section on page 68). For more information about how to take full advantage of the security features in PSoC, see the PSoC 3 TRM.

#### Table 5-1. Flash Protection

| Protection<br>Setting | Allowed                                              | Not Allowed                              |

|-----------------------|------------------------------------------------------|------------------------------------------|

| Unprotected           | External read and write<br>+ internal read and write | -                                        |

| Factory<br>Upgrade    | External write + internal read and write             | External read                            |

| Field Upgrade         | Internal read and write                              | External read and write                  |

| Full Protection       | Internal read                                        | External read and write + internal write |

#### Disclaimer

Note the following details of the flash code protection features on Cypress devices.

Cypress products meet the specifications contained in their particular Cypress data sheets. Cypress believes that its family of products is one of the most secure families of its kind on the market today, regardless of how they are used. There may be methods, unknown to Cypress, that can breach the code protection features. Any of these methods, to our knowledge, would be dishonest and possibly illegal. Neither Cypress nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Cypress is willing to work with the customer who is concerned about the integrity of their code. Code protection is constantly evolving. We at Cypress are committed to continuously improving the code protection features of our products.

## 5.4 EEPROM

PSoC EEPROM memory is a byte-addressable nonvolatile memory. The CY8C34 has up to 2 KB of EEPROM memory to store user data. Reads from EEPROM are random access at the byte level. Reads are done directly; writes are done by sending write commands to an EEPROM programming interface. CPU code execution can continue from flash during EEPROM writes. EEPROM is erasable and writeable at the row level. The EEPROM is divided into 128 rows of 16 bytes each. The factory default values of all EEPROM bytes are 0.

Because the EEPROM is mapped to the 8051 xdata space, the CPU cannot execute out of EEPROM. There is no ECC hardware associated with EEPROM. If ECC is required it must be handled in firmware.

It can take as much as 20 milliseconds to write to EEPROM or flash. During this time the device should not be reset, or unexpected changes may be made to portions of EEPROM or flash. Reset sources (see *Section 6.3.1*) include XRES pin, software reset, and watchdog; care should be taken to make sure that these are not inadvertently activated. In addition, the low voltage detect circuits should be configured to generate an interrupt instead of a reset.

## 5.5 Nonvolatile Latches (NVLs)

PSoC has a 4-byte array of nonvolatile latches (NVLs) that are used to configure the device at reset. The NVL register map is shown in Table 5-2.

Table 5-2. Device Configuration NVL Register Map

| Register Address | 7       | 6                                        | 5                         | 4                         | 3     | 2        | 1         | 0 |

|------------------|---------|------------------------------------------|---------------------------|---------------------------|-------|----------|-----------|---|

| 0x00             | PRT3RE  | M[1:0] PRT2RDM[1:0] PRT1RDM[1:0] PRT0RDM |                           | PRT2RDM[1:0] PRT1RDM[1:0] |       | RDM[1:0] |           |   |

| 0x01             | PRT12R  | DM[1:0]                                  | PRT6RDM[1:0] PRT5RDM[1:0] |                           | PRT4  | RDM[1:0] |           |   |

| 0x02             | XRESMEN | DBGEN                                    |                           |                           |       | PRT18    | 5RDM[1:0] |   |

| 0x03             |         | DIG_PHS_I                                | DLY[3:0] ECCEN DPS        |                           | [1:0] |          |           |   |

The details for individual fields and their factory default settings are shown in Table 5-3:.

### Table 5-3. Fields and Factory Default Settings

| Field            | Description                                                                                                                                  | Settings                                                                                                                      |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| PRTxRDM[1:0]     | Controls reset drive mode of the corresponding IO port. See "Reset Configuration" on page 42. All pins of the port are set to the same mode. | 00b (default) - high impedance analog<br>01b - high impedance digital<br>10b - resistive pull up<br>11b - resistive pull down |

| XRESMEN          | Controls whether pin P1[2] is used as a GPIO or as<br>an external reset. See "Pin Descriptions" on page 11,<br>XRES description.             | 0 (default for 68-pin 72-pin, and 100-pin parts) - GPIO<br>1 (default for 48-pin parts) - external reset                      |

| DBGEN            | Debug Enable allows access to the debug system, for third-party programmers.                                                                 | 0 - access disabled<br>1 (default) - access enabled                                                                           |

| DPS[1:0]         | Controls the usage of various P1 pins as a debug port.<br>See "Programming, Debug Interfaces, Resources" on<br>page 65.                      |                                                                                                                               |

| ECCEN            | Controls whether ECC flash is used for ECC or for general configuration and data storage. See "Flash Program Memory" on page 22.             | 0 - ECC disabled<br>1 (default) - ECC enabled                                                                                 |

| DIG_PHS_DLY[3:0] | Selects the digital clock phase delay.                                                                                                       | See the TRM for details.                                                                                                      |

Although PSoC Creator provides support for modifying the device configuration NVLs, the number of NVL erase / write cycles is limited – see "Nonvolatile Latches (NVL))" on page 109.

The CY8C34 family provides the standard set of registers found on industry standard 8051 devices. In addition, the CY8C34 devices add SFRs to provide direct access to the I/O ports on the device. The following sections describe the SFRs added to the CY8C34 family.

#### 5.7.4 XData Space Access SFRs

The 8051 core features dual DPTR registers for faster data transfer operations. The data pointer select SFR, DPS, selects which data pointer register, DPTR0 or DPTR1, is used for the following instructions:

- MOVX @DPTR, A

- MOVX A, @DPTR

- MOVC A, @A+DPTR

- JMP @A+DPTR

- INC DPTR

- MOV DPTR, #data16

The extended data pointer SFRs, DPX0, DPX1, MXAX, and P2AX, hold the most significant parts of memory addresses during access to the xdata space. These SFRs are used only with the MOVX instructions.

During a MOVX instruction using the DPTR0/DPTR1 register, the most significant byte of the address is always equal to the contents of DPX0/DPX1. During a MOVX instruction using the R0 or R1 register, the most significant byte of the address is always equal to the contents of MXAX, and the next most significant byte is always equal to the contents of P2AX.

#### 5.7.5 I/O Port SFRs

The I/O ports provide digital input sensing, output drive, pin interrupts, connectivity for analog inputs and outputs, LCD, and access to peripherals through the DSI. Full information on I/O ports is found in I/O System and Routing on page 36.

I/O ports are linked to the CPU through the PHUB and are also available in the SFRs. Using the SFRs allows faster access to a limited set of I/O port registers, while using the PHUB allows boot configuration and access to all I/O port registers.

Each SFR supported I/O port provides three SFRs:

- SFRPRTxDR sets the output data state of the port (where x is port number and includes ports 0-6, 12 and 15)

- The SFRPRTxSEL selects whether the PHUB PRTxDR register or the SFRPRTxDR controls each pin's output buffer within the port. If a SFRPRTxSEL[y] bit is high, the corresponding SFRPRTxDR[y] bit sets the output state for that pin. If a SFRPRTxSEL[y] bit is low, the corresponding PRTxDR[y] bit sets the output state of the pin (where y varies from 0 to 7).

- The SFRPRTxPS is a read only register that contains pin state values of the port pins.

#### 5.7.5.1 xdata Space

The 8051 xdata space is 24-bit, or 16 MB in size. The majority of this space is not "external"—it is used by on-chip components. See Table 5-5. External, that is, off-chip, memory can be accessed using the EMIF. See External Memory Interface on page 24.

| Address Range            | Purpose                                               |  |  |  |  |

|--------------------------|-------------------------------------------------------|--|--|--|--|

| 0×00 0000 – 0×00 1FFF    |                                                       |  |  |  |  |

| 0×00 4000 – 0×00 42FF    | Clocking, PLLs, and oscillators                       |  |  |  |  |

| 0×00 4300 – 0×00 43FF    | Power management                                      |  |  |  |  |

| 0×00 4400 – 0×00 44FF    | Interrupt controller                                  |  |  |  |  |

| 0×00 4500 – 0×00 45FF    | Ports interrupt control                               |  |  |  |  |

| 0×00 4700 – 0×00 47FF    | Flash programming interface                           |  |  |  |  |

| 0×00 4800 - 0×00 48FF    | Cache controller                                      |  |  |  |  |

| 0×00 4900 – 0×00 49FF    | I <sup>2</sup> C controller                           |  |  |  |  |

| 0×00 4E00 – 0×00<br>4EFF | Decimator                                             |  |  |  |  |

| 0×00 4F00 – 0×00<br>4FFF | Fixed timer/counter/PWMs                              |  |  |  |  |

| 0×00 5000 – 0×00 51FF    | I/O ports control                                     |  |  |  |  |

| 0×00 5400 – 0×00 54FF    | External Memory Interface (EMIF)<br>control registers |  |  |  |  |

| 0×00 5800 – 0×00 5FFF    | Analog Subsystem interface                            |  |  |  |  |

| 0×00 6000 – 0×00 60FF    | USB controller                                        |  |  |  |  |

| 0×006400-0×006FFF        | UDB Working Registers                                 |  |  |  |  |

| 0×007000-0×007FFF        | PHUB configuration                                    |  |  |  |  |

| 0×008000-0×008FFF        | EEPROM                                                |  |  |  |  |

| 0×00 A000 – 0×00<br>A400 | CAN                                                   |  |  |  |  |

| 0×01 0000 – 0×01<br>FFFF | Digital Interconnect configuration                    |  |  |  |  |

| 0×05 0220 – 0×05 02F0    | Debug controller                                      |  |  |  |  |

| 0×08 0000 – 0×08 1FFF    | Flash ECC bytes                                       |  |  |  |  |

| 0×80 0000 – 0×FF<br>FFFF | External Memory Interface                             |  |  |  |  |

## 6. System Integration

## 6.1 Clocking System

The clocking system generates, divides, and distributes clocks throughout the PSoC system. For the majority of systems, no external crystal is required. The IMO and PLL together can generate up to a 50 MHz clock, accurate to  $\pm 2$  percent over voltage and temperature. Additional internal and external clock sources allow each design to optimize accuracy, power, and cost. Any of the clock sources can be used to generate other clock frequencies in the 16-bit clock dividers and UDBs for anything the user wants, for example a UART baud rate generator.

Clock generation and distribution is automatically configured through the PSoC Creator IDE graphical interface. This is based on the complete system's requirements. It greatly speeds the design process. PSoC Creator allows you to build clocking systems with minimal input. You can specify desired clock frequencies and accuracies, and the software locates or builds a clock that meets the required specifications. This is possible because of the programmability inherent in PSoC.

Key features of the clocking system include:

- Seven general purpose clock sources

- 3- to 24-MHz IMO, ±2 percent at 3 MHz

- □ 4- to 25-MHz external crystal oscillator (MHzECO)

- Clock doubler provides a doubled clock frequency output for the USB block, see USB Clock Domain on page 30

- DSI signal from an external I/O pin or other logic

- 24- to 50- MHz fractional PLL sourced from IMO, MHzECO, or DSI

- I kHz, 33 kHz, 100 kHz ILO for Watch Dog Timer (WDT) and Sleep Timer

- 32.768-kHz external crystal oscillator (kHzECO) for RTC

- IMO has a USB mode that auto locks to the USB bus clock requiring no external crystal for USB. (USB equipped parts only)

- Independently sourced clock in all clock dividers

- Eight 16-bit clock dividers for the digital system

- Four 16-bit clock dividers for the analog system

- Dedicated 16-bit divider for the bus clock

- Dedicated 4-bit divider for the CPU clock

- Automatic clock configuration in PSoC Creator

| Source  | Fmin   | Tolerance at Fmin                | Fmax    | Tolerance at Fmax | Startup Time                          |

|---------|--------|----------------------------------|---------|-------------------|---------------------------------------|

| IMO     | 3 MHz  | ±2% over voltage and temperature | 24 MHz  | ±4%               | 13 µs max                             |

| MHzECO  | 4 MHz  | Crystal dependent                | 25 MHz  | Crystal dependent | 5 ms typ, max is<br>crystal dependent |

| DSI     | 0 MHz  | Input dependent                  | 33 MHz  | Input dependent   | Input dependent                       |

| PLL     | 24 MHz | Input dependent                  | 50 MHz  | Input dependent   | 250 µs max                            |

| Doubler | 48 MHz | Input dependent                  | 48 MHz  | Input dependent   | 1 µs max                              |

| ILO     | 1 kHz  | -50%, +100%                      | 100 kHz | -55%, +100%       | 15 ms max in lowest power mode        |

| kHzECO  | 32 kHz | Crystal dependent                | 32 kHz  | Crystal dependent | 500 ms typ, max is crystal dependent  |

## Table 6-1. Oscillator Summary

## 6.4 I/O System and Routing

PSoC I/Os are extremely flexible. Every GPIO has analog and digital I/O capability. All I/Os have a large number of drive modes, which are set at POR. PSoC also provides up to four individual I/O voltage domains through the VDDIO pins.

There are two types of I/O pins on every device; those with USB provide a third type. Both General Purpose I/O (GPIO) and Special I/O (SIO) provide similar digital functionality. The primary differences are their analog capability and drive strength. Devices that include USB also provide two USBIO pins that support specific USB functionality as well as limited GPIO capability.

All I/O pins are available for use as digital inputs and outputs for both the CPU and digital peripherals. In addition, all I/O pins can generate an interrupt. The flexible and advanced capabilities of the PSoC I/O, combined with any signal to any pin routability, greatly simplify circuit design and board layout. All GPIO pins can be used for analog input, CapSense<sup>[13]</sup>, and LCD segment drive, while SIO pins are used for voltages in excess of VDDA and for programmable output voltages.

- Features supported by both GPIO and SIO:

- User programmable port reset state

- □ Separate I/O supplies and voltages for up to four groups of I/O

- Digital peripherals use DSI to connect the pins

- Input or output or both for CPU and DMA

- Eight drive modes

- Every pin can be an interrupt source configured as rising edge, falling edge or both edges. If required, level sensitive interrupts are supported through the DSI

- Dedicated port interrupt vector for each port

- Slew rate controlled digital output drive mode

- Access port control and configuration registers on either port basis or pin basis

- Separate port read (PS) and write (DR) data registers to avoid read modify write errors

- Special functionality on a pin by pin basis

- Additional features only provided on the GPIO pins:

- LCD segment drive on LCD equipped devices

- CapSense<sup>[13]</sup>

- Analog input and output capability

- Continuous 100 µA clamp current capability

- Standard drive strength down to 1.7 V

- Additional features only provided on SIO pins:

- B Higher drive strength than GPIO

- $\blacksquare$  Hot swap capability (5 V tolerance at any operating V\_{DD})

- Programmable and regulated high input and output drive levels down to 1.2 V

- D No analog input, CapSense, or LCD capability

- Dver voltage tolerance up to 5.5 V

- □ SIO can act as a general purpose analog comparator

- USBIO features:

- □ Full speed USB 2.0 compliant I/O

- Highest drive strength for general purpose use

- □ Input, output, or both for CPU and DMA

- □ Input, output, or both for digital peripherals

- Digital output (CMOS) drive mode

- Each pin can be an interrupt source configured as rising edge, falling edge, or both edges

<sup>13.</sup> GPIOs with opamp outputs are not recommended for use with CapSense

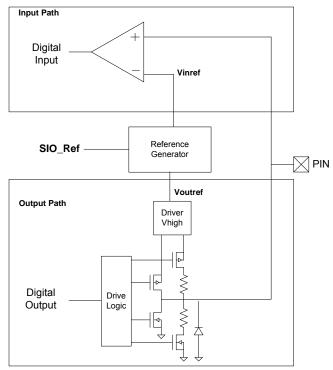

## Figure 6-13. SIO Reference for Input and Output

#### 6.4.13 SIO as Comparator

This section applies only to SIO pins. The adjustable input level feature of the SIOs as explained in the Adjustable Input Level section can be used to construct a comparator. The threshold for the comparator is provided by the SIO's reference generator. The reference generator has the option to set the analog signal routed through the analog global line as threshold for the comparator. Note that a pair of SIO pins share the same threshold.

The digital input path in Figure 6-10 on page 38 illustrates this functionality. In the figure, 'Reference level' is the analog signal routed through the analog global. The hysteresis feature can also be enabled for the input buffer of the SIO, which increases noise immunity for the comparator.

#### 6.4.14 Hot Swap

This section applies only to SIO pins. SIO pins support 'hot swap' capability to plug into an application without loading the signals that are connected to the SIO pins even when no power is applied to the PSoC device. This allows the unpowered PSoC to maintain a high impedance load to the external device while also preventing the PSoC from being powered through a SIO pin's protection diode.

Powering the device up or down while connected to an operational I2C bus may cause transient states on the SIO pins. The overall I2C bus design should take this into account.

#### 6.4.15 Over Voltage Tolerance

All I/O pins provide an over voltage tolerance feature at any operating  $V_{\text{DD}}.$

- There are no current limitations for the SIO pins as they present a high impedance load to the external circuit where VDDIO ≤ VIN ≤ 5.5 V.

- The GPIO pins must be limited to 100 µA using a current limiting resistor. GPIO pins clamp the pin voltage to approximately one diode above the Vddio supply where Vddio ≤ V<sub>IN</sub> ≤ VDDA.

- In case of a GPIO pin configured for analog input/output, the analog voltage on the pin must not exceed the Vddio supply voltage to which the GPIO belongs.

A common application for this feature is connection to a bus such as I<sup>2</sup>C where different devices are running from different supply voltages. In the I<sup>2</sup>C case, the PSoC chip is configured into the Open Drain, Drives Low mode for the SIO pin. This allows an external pull-up to pull the I<sup>2</sup>C bus voltage above the PSoC pin supply. For example, the PSoC chip could operate at 1.8 V, and an external device could run from 5 V. Note that the SIO pin's V<sub>IH</sub> and V<sub>IL</sub> levels are determined by the associated Vddio supply pin.

The SIO pin must be in one of the following modes: 0 (high impedance analog), 1 (high impedance digital), or 4 (open drain drives low). See Figure 6-12 for details. Absolute maximum ratings for the device must be observed for all I/O pins.

#### 6.4.16 Reset Configuration

While reset is active all I/Os are reset to and held in the High Impedance Analog state. After reset is released, the state can be reprogrammed on a port-by-port basis to pull-down or pull-up. To ensure correct reset operation, the port reset configuration data is stored in special nonvolatile registers. The stored reset data is automatically transferred to the port reset configuration registers at reset release.

#### 6.4.17 Low-Power Functionality

In all low-power modes the I/O pins retain their state until the part is awakened and changed or reset. To awaken the part, use a pin interrupt, because the port interrupt logic continues to function in all low-power modes.

#### 6.4.18 Special Pin Functionality

Some pins on the device include additional special functionality in addition to their GPIO or SIO functionality. The specific special function pins are listed in Pinouts on page 6. The special features are:

#### Digital

- 4 to 25 MHz crystal oscillator

- □ 32.768-kHz crystal oscillator

- Wake from sleep on I<sup>2</sup>C address match. Any pin can be used for I<sup>2</sup>C if wake from sleep is not required.

- JTAG interface pins

- SWD interface pins

- SWV interface pins

- External reset

- Analog

- Deamp inputs and outputs

- High current IDAC outputs

- External reference inputs

The bits of the control register, which may be written to by the system bus, are used to drive into the routing matrix, and thus provide firmware with the opportunity to control the state of UDB processing. The status register is read-only and it allows internal UDB state to be read out onto the system bus directly from internal routing. This allows firmware to monitor the state of UDB processing. Each bit of these registers has programmable connections to the routing matrix and routing connections are made depending on the requirements of the application.

#### 7.2.3.1 Usage Examples

As an example of control input, a bit in the control register can be allocated as a function enable bit. There are multiple ways to enable a function. In one method the control bit output would be routed to the clock control block in one or more UDBs and serve as a clock enable for the selected UDB blocks. A status example is a case where a PLD or datapath block generated a condition, such as a "compare true" condition that is captured and latched by the status register and then read (and cleared) by CPU firmware.

#### 7.2.3.2 Clock Generation

Each subcomponent block of a UDB including the two PLDs, the datapath, and Status and Control, has a clock selection and control block. This promotes a fine granularity with respect to allocating clocking resources to UDB component blocks and allows unused UDB resources to be used by other functions for maximum system efficiency.

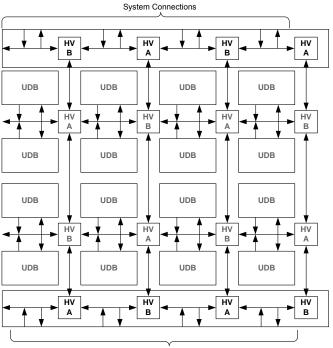

## 7.3 UDB Array Description

Figure 7-7 shows an example of a 16 UDB array. In addition to the array core, there are a DSI routing interfaces at the top and bottom of the array. Other interfaces that are not explicitly shown include the system interfaces for bus and clock distribution. The UDB array includes multiple horizontal and vertical routing channels each comprised of 96 wires. The wire connections to UDBs, at horizontal/vertical intersection and at the DSI interface are highly permutable providing efficient automatic routing in PSoC Creator. Additionally the routing allows wire by wire segmentation along the vertical and horizontal routing to further increase routing flexibility and capability.

#### Figure 7-7. Digital System Interface Structure

System Connections

#### 7.3.1 UDB Array Programmable Resources

Figure 7-8 shows an example of how functions are mapped into a bank of 16 UDBs. The primary programmable resources of the UDB are two PLDs, one datapath and one status/control register. These resources are allocated independently, because they have independently selectable clocks, and therefore unused blocks are allocated to other unrelated functions.

An example of this is the 8-bit Timer in the upper left corner of the array. This function only requires one datapath in the UDB, and therefore the PLD resources may be allocated to another function. A function such as a Quadrature Decoder may require more PLD logic than one UDB can supply and in this case can utilize the unused PLD blocks in the 8-bit Timer UDB. Programmable resources in the UDB array are generally homogeneous so functions can be mapped to arbitrary boundaries in the array.

Analog local buses (abus) are routing resources located within the analog subsystem and are used to route signals between different analog blocks. There are eight abus routes in CY8C34, four in the left half (abusl [0:3]) and four in the right half (abusr [0:3]) as shown in Figure 8-2. Using the abus saves the analog globals and analog mux buses from being used for interconnecting the analog blocks.

Multiplexers and switches exist on the various buses to direct signals into and out of the analog blocks. A multiplexer can have only one connection on at a time, whereas a switch can have multiple connections on simultaneously. In Figure 8-2, multiplexers are indicated by grayed ovals and switches are indicated by transparent ovals.

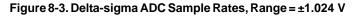

## 8.2 Delta-sigma ADC

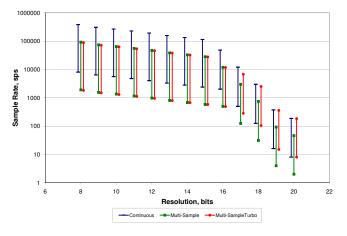

The CY8C34 device contains one delta-sigma ADC. This ADC offers differential input, high resolution and excellent linearity, making it a good ADC choice for measurement applications. The converter can be configured to output 12-bit resolution at data rates of up to 192 ksps. At a fixed clock rate, resolution can be traded for faster data rates as shown in Table 8-1 and Figure 8-3.

| Bits | Maximum Sample Rate<br>(sps) | SINAD (dB) |

|------|------------------------------|------------|

| 12   | 192 k                        | 66         |

| 8    | 384 k                        | 43         |

#### 8.2.1 Functional Description

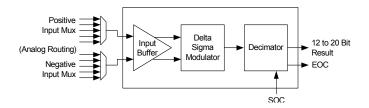

The ADC connects and configures three basic components, input buffer, delta-sigma modulator, and decimator. The basic block diagram is shown in Figure 8-4. The signal from the input muxes is delivered to the delta-sigma modulator either directly or through the input buffer. The delta-sigma modulator performs the actual analog to digital conversion. The modulator over-samples the input and generates a serial data stream output. This high speed data stream is not useful for most applications without some type of post processing, and so is passed to the decimator through the Analog Interface block. The decimator converts the high speed serial data stream into parallel ADC results. The modulator/decimator frequency response is  $[(\sin x)/x]^4$ .

#### Figure 8-4. Delta-sigma ADC Block Diagram

Resolution and sample rate are controlled by the Decimator. Data is pipelined in the decimator; the output is a function of the last four samples. When the input multiplexer is switched, the output data is not valid until after the fourth sample after the switch.

#### 8.2.2 Operational Modes

The ADC can be configured by the user to operate in one of four modes: Single Sample, Multi Sample, Continuous, or Multi Sample (Turbo). All four modes are started by either a write to the start bit in a control register or an assertion of the Start of Conversion (SoC) signal. When the conversion is complete, a status bit is set and the output signal End of Conversion (EoC) asserts high and remains high until the value is read by either the DMA controller or the CPU.

#### 8.2.2.1 Single Sample

In Single Sample mode, the ADC performs one sample conversion on a trigger. In this mode, the ADC stays in standby state waiting for the SoC signal to be asserted. When SoC is signaled the ADC performs four successive conversions. The first three conversions prime the decimator. The ADC result is valid and available after the fourth conversion, at which time the EoC signal is generated. To detect the end of conversion, the system may poll a control register for status or configure the external EoC signal to generate an interrupt or invoke a DMA request. When the transfer is done the ADC reenters the standby state where it stays until another SoC event.

#### 8.2.2.2 Continuous

Continuous sample mode is used to take multiple successive samples of a single input signal. Multiplexing multiple inputs should not be done with this mode. There is a latency of three conversion times before the first conversion result is available. This is the time required to prime the decimator. After the first result, successive conversions are available at the selected sample rate.

#### 8.2.2.3 Multi Sample

Multi sample mode is similar to continuous mode except that the ADC is reset between samples. This mode is useful when the input is switched between multiple signals. The decimator is re-primed between each sample so that previous samples do not affect the current conversion. Upon completion of a sample, the next sample is automatically initiated. The results can be transferred using either firmware polling, interrupt, or DMA.

More information on output formats is provided in the Technical Reference Manual.

## 8.7 CapSense

The CapSense system provides a versatile and efficient means for measuring capacitance in applications such as touch sense buttons, sliders, proximity detection, etc. The CapSense system uses a configuration of system resources, including a few hardware functions primarily targeted for CapSense. Specific resource usage is detailed in the CapSense component in PSoC Creator.

A capacitive sensing method using a delta-sigma modulator (CSD) is used. It provides capacitance sensing using a switched capacitor technique with a delta-sigma modulator to convert the sensing current to a digital code.

### 8.8 Temp Sensor

Die temperature is used to establish programming parameters for writing flash. Die temperature is measured using a dedicated sensor based on a forward biased transistor. The temperature sensor has its own auxiliary ADC.

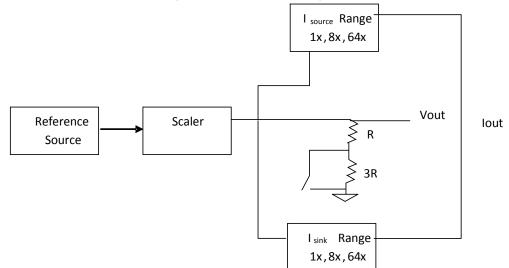

## 8.9 DAC

The CY8C34 parts contain two Digital to Analog Convertors (DACs). Each DAC is 8-bit and can be configured for either voltage or current output. The DACs support CapSense, power supply regulation, and waveform generation. Each DAC has the following features:

- Adjustable voltage or current output in 255 steps

- Programmable step size (range selection)

- Eight bits of calibration to correct ± 25 percent of gain error

- Source and sink option for current output

- High and low speed / power modes

- 8 Msps conversion rate for current output

- 1 Msps conversion rate for voltage output

- Monotonic in nature

- Data and strobe inputs can be provided by the CPU or DMA, or routed directly from the DSI

- Dedicated low-resistance output pin for high-current mode

#### Figure 8-11. DAC Block Diagram

#### 8.9.1 Current DAC

The current DAC (IDAC) can be configured for the ranges 0 to 31.875  $\mu$ A, 0 to 255  $\mu$ A, and 0 to 2.04 mA. The IDAC can be configured to source or sink current.

#### 8.9.2 Voltage DAC

For the voltage DAC (VDAC), the current DAC output is routed through resistors. The two ranges available for the VDAC are 0 to 1.02 V and 0 to 4.08 V. In voltage mode any load connected to the output of a DAC should be purely capacitive (the output of the VDAC is not buffered).

## 8.10 Up/Down Mixer

In continuous time mode, the SC/CT block components are used to build an up or down mixer. Any mixing application contains an input signal frequency and a local oscillator frequency. The polarity of the clock, Fclk, switches the amplifier between inverting or noninverting gain. The output is the product of the input and the switching function from the local oscillator, with frequency components at the local oscillator plus and minus the signal frequency (Fclk + Fin and Fclk – Fin) and reduced-level frequency components at odd integer multiples of the local oscillator frequency. The local oscillator frequency is provided by the selected clock source for the mixer.

Continuous time up and down mixing works for applications with input signals and local oscillator frequencies up to 1 MHz.

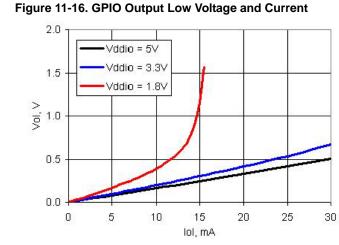

5 4 Voh, V 3 2 Vddio = 5V Vddio = 3.3V 1 Vddio = 1.8V 0 10 0 5 15 20 25 30 loh, mA

## Figure 11-15. GPIO Output High Voltage and Current

## Table 11-10. GPIO AC Specifications

| Parameter | Description                                                                             | Conditions                            | Min | Тур | Max | Units |

|-----------|-----------------------------------------------------------------------------------------|---------------------------------------|-----|-----|-----|-------|

| TriseF    | Rise time in Fast Strong Mode <sup>[41]</sup>                                           | 3.3 V V <sub>DDIO</sub> Cload = 25 pF | -   | -   | 6   | ns    |

| TfallF    | Fall time in Fast Strong Mode <sup>[41]</sup>                                           | 3.3 V V <sub>DDIO</sub> Cload = 25 pF | -   | -   | 6   | ns    |

| TriseS    | Rise time in Slow Strong Mode <sup>[41]</sup>                                           | 3.3 V V <sub>DDIO</sub> Cload = 25 pF | -   | -   | 60  | ns    |

| TfallS    | Fall time in Slow Strong Mode <sup>[41]</sup>                                           | 3.3 V V <sub>DDIO</sub> Cload = 25 pF | -   | -   | 60  | ns    |

|           | GPIO output operating frequency                                                         |                                       |     |     |     |       |

|           | $2.7 \text{ V} \leq \text{V}_{\text{DDIO}} \leq 5.5 \text{ V}$ , fast strong drive mode | 90/10% V <sub>DDIO</sub> into 25 pF   | -   | -   | 33  | MHz   |

| Fgpioout  | $1.71 \text{ V} \leq \text{V}_{\text{DDIO}} < 2.7 \text{ V}$ , fast strong drive mode   | 90/10% V <sub>DDIO</sub> into 25 pF   | -   | -   | 20  | MHz   |

|           | $3.3 \text{ V} \leq \text{V}_{\text{DDIO}} \leq 5.5 \text{ V}$ , slow strong drive mode | 90/10% V <sub>DDIO</sub> into 25 pF   | -   | -   | 7   | MHz   |

|           | 1.71 V $\leq$ V <sub>DDIO</sub> < 3.3 V, slow strong drive mode                         | 90/10% V <sub>DDIO</sub> into 25 pF   | -   | -   | 3.5 | MHz   |

| Fgpioin   | GPIO input operating frequency                                                          |                                       | 1   |     |     |       |

| gpioin    | 1.71 V ≤ V <sub>DDIO</sub> ≤ 5.5 V                                                      | 90/10% V <sub>DDIO</sub>              | -   | -   | 33  | MHz   |

<sup>41.</sup> Based on device characterization (Not production tested).

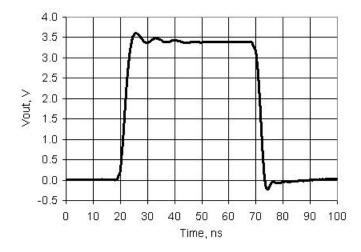

## Table 11-12. SIO AC Specifications (continued)

| Parameter | Description                                                                                        | Conditions                               | Min | Тур | Max | Units |

|-----------|----------------------------------------------------------------------------------------------------|------------------------------------------|-----|-----|-----|-------|

|           | SIO output operating frequency                                                                     |                                          |     |     |     |       |

|           | 2.7 V < V <sub>DDIO</sub> < 5.5 V, Unregulated<br>output (GPIO) mode, fast strong<br>drive mode    | 90/10% V <sub>DDIO</sub> into 25 pF      | _   | -   | 33  | MHz   |

|           | 1.71 V < V <sub>DDIO</sub> < 2.7 V, Unregu-<br>lated output (GPIO) mode, fast<br>strong drive mode | 90/10% V <sub>DDIO</sub> into 25 pF      | _   | -   | 16  | MHz   |

| Fsioout   | 3.3 V < V <sub>DDIO</sub> < 5.5 V, Unregulated<br>output (GPIO) mode, slow strong<br>drive mode    | 90/10% V <sub>DDIO</sub> into 25 pF      | _   | -   | 5   | MHz   |

| FSIOOUL   | 1.71 V < V <sub>DDIO</sub> < 3.3 V, Unregu-<br>lated output (GPIO) mode, slow<br>strong drive mode | 90/10% V <sub>DDIO</sub> into 25 pF      | -   | -   | 4   | MHz   |

|           | 2.7 V < V <sub>DDIO</sub> < 5.5 V, Regulated output mode, fast strong drive mode                   | Output continuously switching into 25 pF | -   | -   | 20  | MHz   |

|           | 1.71 V < V <sub>DDIO</sub> < 2.7 V, Regulated output mode, fast strong drive mode                  | Output continuously switching into 25 pF | -   | -   | 10  | MHz   |

|           | 1.71 V < V <sub>DDIO</sub> < 5.5 V, Regulated<br>output mode, slow strong drive<br>mode            | Output continuously switching into 25 pF | -   | -   | 2.5 | MHz   |

| Fsioin    | SIO input operating frequency                                                                      | •                                        | •   | · · |     |       |

| 1510111   | 1.71 V <u>≤</u> V <sub>DDIO</sub> <u>≤</u> 5.5 V                                                   | 90/10% V <sub>DDIO</sub>                 | -   | -   | 33  | MHz   |

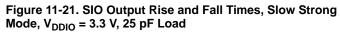

# Figure 11-20. SIO Output Rise and Fall Times, Fast Strong Mode, $V_{DDIO}$ = 3.3 V, 25 pF Load

## Table 11-13. SIO Comparator Specifications<sup>[45]</sup>

| Parameter | Description                    | Conditions                | Min | Тур | Max | Units |

|-----------|--------------------------------|---------------------------|-----|-----|-----|-------|

| Vos       | Offset voltage                 | V <sub>DDIO</sub> = 2 V   | -   | -   | 68  | mV    |

|           |                                | V <sub>DDIO</sub> = 2.7 V | -   | _   | 72  |       |

|           |                                | V <sub>DDIO</sub> = 5.5 V | -   | _   | 82  |       |

| TCVos     | Offset voltage drift with temp |                           | -   | -   | 250 | µV/°C |

| CMRR      | Common mode rejection ratio    | V <sub>DDIO</sub> = 2 V   | 30  | -   | -   | dB    |

|           |                                | V <sub>DDIO</sub> = 2.7 V | 35  | _   | _   |       |

|           |                                | V <sub>DDIO</sub> = 5.5 V | 40  | -   | -   | 1     |

| Tresp     | Response time                  |                           | -   | -   | 30  | ns    |

## 11.4.3 USBIO

For operation in GPIO mode, the standard range for V<sub>DDD</sub> applies, see Device Level Specifications on page 71.

## Table 11-14. USBIO DC Specifications

| Parameter            | Description                            | Conditions                                                | Min            | Тур | Max            | Units |

|----------------------|----------------------------------------|-----------------------------------------------------------|----------------|-----|----------------|-------|

| Rusbi                | USB D+ pull-up resistance              | With idle bus                                             | 0.900          | -   | 1.575          | kΩ    |

| Rusba                | USB D+ pull-up resistance              | While receiving traffic                                   | 1.425          | -   | 3.090          | kΩ    |

| Vohusb               | Static output high                     | 15 k $\Omega$ ±5% to $V_{SS},$ internal pull-up enabled   | 2.8            | -   | 3.6            | V     |

| Volusb               | Static output low                      | 15 k $\Omega$ ±5% to V $_{SS}$ , internal pull-up enabled | -              | -   | 0.3            | V     |

| Vihgpio              | Input voltage high, GPIO mode          | $V_{DDD} \ge 3 V$                                         | 2              | -   | -              | V     |

| Vilgpio              | Input voltage low, GPIO mode           | $V_{DDD} \ge 3 V$                                         | -              | -   | 0.8            | V     |

| Vohgpio              | Output voltage high, GPIO mode         | $I_{OH}$ = 4 mA, $V_{DDD} \ge 3 V$                        | 2.4            | -   | -              | V     |

| Volgpio              | Output voltage low, GPIO mode          | $I_{OL}$ = 4 mA, $V_{DDD} \ge 3 V$                        | _              | -   | 0.3            | V     |

| Vdi                  | Differential input sensitivity         | (D+) – (D–)                                               | -              | -   | 0.2            | V     |

| Vcm                  | Differential input common mode range   |                                                           | 0.8            | -   | 2.5            | V     |

| Vse                  | Single ended receiver threshold        |                                                           | 0.8            | _   | 2              | V     |

| Rps2                 | PS/2 pull-up resistance                | In PS/2 mode, with PS/2 pull-up enabled                   | 3              | -   | 7              | kΩ    |

| Rext                 | External USB series resistor           | In series with each USB pin                               | 21.78<br>(–1%) | 22  | 22.22<br>(+1%) | Ω     |

| Zo                   | USB driver output impedance            | Including Rext                                            | 28             | _   | 44             | Ω     |

| C <sub>IN</sub>      | USB transceiver input capacitance      |                                                           | -              | -   | 20             | pF    |

| I <sub>IL</sub> [45] | Input leakage current (absolute value) | 25 °C, V <sub>DDD</sub> = 3.0 V                           | -              | _   | 2              | nA    |

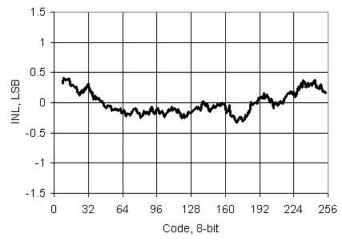

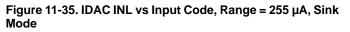

## 11.5.6 Current Digital-to-analog Converter (IDAC)

All specifications are based on use of the low-resistance IDAC output pins (see Pin Descriptions on page 11 for details). See the IDAC component data sheet in PSoC Creator for full electrical specifications and APIs.

Unless otherwise specified, all charts and graphs show typical values.

## Table 11-28. IDAC DC Specifications

| Parameter        | Description                           | Conditions                                                                                                                          | Min | Тур    | Max  | Units  |

|------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----|--------|------|--------|

|                  | Resolution                            |                                                                                                                                     | _   | -      | 8    | bits   |

| I <sub>OUT</sub> | Output current at code = 255          | $\begin{array}{l} \mbox{Range = 2.04 mA, code = 255,} \\ \mbox{V}_{\mbox{DDA}} \geq 2.7 \mbox{ V, Rload = 600 } \Omega \end{array}$ | _   | 2.04   | -    | mA     |

|                  |                                       | Range = 2.04 mA, high speed mode, code = 255, $V_{DDA} \le 2.7$ V, Rload = 300 $\Omega$                                             | -   | 2.04   | -    | mA     |

|                  |                                       | Range = 255 $\mu$ A, code = 255, Rload<br>= 600 $\Omega$                                                                            | _   | 255    | _    | μA     |

|                  |                                       | Range = 31.875 $\mu$ A, code = 255,<br>Rload = 600 $\Omega$                                                                         | -   | 31.875 | _    | μA     |

|                  | Monotonicity                          |                                                                                                                                     | _   | -      | Yes  |        |

| Ezs              | Zero scale error                      |                                                                                                                                     | _   | 0      | ±1   | LSB    |

| Eg               | Gain error                            | Range = 2.04 mA, 25 °C                                                                                                              | _   | -      | ±2.5 | %      |

|                  |                                       | Range = 255 µA, 25 ° C                                                                                                              | _   | -      | ±2.5 | %      |

|                  |                                       | Range = 31.875 µA, 25 ° C                                                                                                           | _   | -      | ±3.5 | %      |

| TC_Eg            | Temperature coefficient of gain error | Range = 2.04 mA                                                                                                                     | _   | -      | 0.04 | % / °C |

|                  |                                       | Range = 255 µA                                                                                                                      | _   | -      | 0.04 | % / °C |

|                  |                                       | Range = 31.875 µA                                                                                                                   | _   | -      | 0.05 | % / °C |

| INL              | Integral nonlinearity                 | Sink mode, range = 255 $\mu$ A, Codes<br>8 – 255, Rload = 2.4 k $\Omega$ , Cload =<br>15 pF                                         | _   | ±0.9   | ±1   | LSB    |

|                  |                                       | Source mode, range = 255 $\mu$ A,<br>Codes 8 – 255, Rload = 2.4 k $\Omega$ ,<br>Cload = 15 pF                                       | -   | ±1.2   | ±1.6 | LSB    |

| DNL              | Differential nonlinearity             | Sink mode, range = 255 $\mu$ A, Rload<br>= 2.4 k $\Omega$ , Cload = 15 pF                                                           | -   | ±0.3   | ±1   | LSB    |

|                  |                                       | Source mode, range = 255 $\mu$ A,<br>Rload = 2.4 k $\Omega$ , Cload = 15 pF                                                         | _   | ±0.3   | ±1   | LSB    |

| Vcompliance      | Dropout voltage, source or sink mode  | Voltage headroom at max current, $R_{LOAD}$ to $V_{DDA}$ or $R_{LOAD}$ to $V_{SSA},$ $V_{DIFF}$ from $V_{DDA}$                      | 1   | -      | -    | V      |

Table 11-28. IDAC DC Specifications (continued)

| Parameter       | Description                                      | Conditions                                         | Min | Тур | Max | Units |

|-----------------|--------------------------------------------------|----------------------------------------------------|-----|-----|-----|-------|

| I <sub>DD</sub> | Operating current, code = 0                      | Low speed mode, source mode, range = 31.875 µA     | _   | 44  | 100 | μA    |

|                 |                                                  | Low speed mode, source mode, range = 255 µA,       | _   | 33  | 100 | μA    |

|                 |                                                  | Low speed mode, source mode,<br>range = 2.04 mA    | -   | 33  | 100 | μA    |

|                 |                                                  | Low speed mode, sink mode,<br>range = 31.875 µA    | -   | 36  | 100 | μA    |

|                 |                                                  | Low speed mode, sink mode,<br>range = 255 µA       | _   | 33  | 100 | μA    |

|                 |                                                  | Low speed mode, sink mode,<br>range = 2.04 mA      | -   | 33  | 100 | μA    |

|                 |                                                  | High speed mode, source mode,<br>range = 31.875 μA | -   | 310 | 500 | μA    |

|                 |                                                  | High speed mode, source mode, range = 255 µA       | -   | 305 | 500 | μA    |

|                 |                                                  | High speed mode, source mode,<br>range = 2.04 mA   | -   | 305 | 500 | μA    |

|                 | High speed mode, sink mode,<br>range = 31.875 μA | _                                                  | 310 | 500 | μA  |       |

|                 |                                                  | High speed mode, sink mode,<br>range = 255 µA      | _   | 300 | 500 | μA    |

|                 |                                                  | High speed mode, sink mode,<br>range = 2.04 mA     | -   | 300 | 500 | μA    |

# Figure 11-34. IDAC INL vs Input Code, Range = 255 $\mu$ A, Source Mode

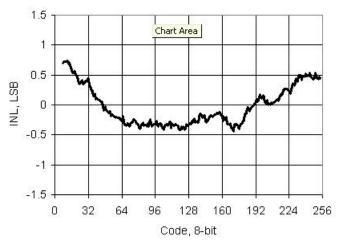

### 11.7.5 External Memory Interface

Figure 11-64. Asynchronous Write and Read Cycle Timing, No Wait States

| Table 11-61. | Asynchronous Write and R | Read Timing Specifications <sup>[60]</sup> |

|--------------|--------------------------|--------------------------------------------|

|--------------|--------------------------|--------------------------------------------|

| Parameter  | Description                                                  | Conditions | Min             | Тур | Max | Units |

|------------|--------------------------------------------------------------|------------|-----------------|-----|-----|-------|

| Fbus_clock | Bus clock frequency <sup>[61]</sup>                          |            | -               | -   | 33  | MHz   |

| Tbus_clock | Bus clock period <sup>[62]</sup>                             |            | 30.3            | -   | -   | ns    |

| Twr_Setup  | Time from EM_data valid to rising edge of<br>EM_WE and EM_CE |            | Tbus_clock – 10 | _   | -   | ns    |

| Trd_setup  | Time that EM_data must be valid before rising edge of EM_OE  |            | 5               | _   | -   | ns    |

| Trd_hold   | Time that EM_data must be valid after rising edge of EM_OE   |            | 5               | _   | _   | ns    |

Notes

- 60. Based on device characterization (Not production tested).

61. EMIF signal timings are limited by GPIO frequency limitations. See "GPIO" section on page 79.

62. EMIF output signals are generally synchronized to bus clock, so EMIF signal timings are dependent on bus clock frequency.

□ 6: 64 KB

## **12.1 Part Numbering Conventions**

PSoC 3 devices follow the part numbering convention described here. All fields are single character alphanumeric (0, 1, 2, ..., 9, A, B, ..., Z) unless stated otherwise.

| CY8Cabcdefg-xxx                                                                   |                                                                                                            |

|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| ■ a: Architecture<br>□ 3: PSoC 3<br>□ 5: PSoC 5                                   | <ul> <li>■ ef: Package code</li> <li>□ Two character alphanumeric</li> <li>□ AX: TQFP</li> </ul>           |

| <ul> <li>b: Family group within architecture</li> <li>4: CY8C34 family</li> </ul> | □ LT: QFN<br>□ PV: SSOP                                                                                    |

| □ 6: CY8C36 family<br>□ 8: CY8C38 family                                          | <ul><li>g: Temperature range</li><li>□ C: commercial</li></ul>                                             |

| ■ c: Speed grade<br>□ 4: 50 MHz                                                   | □ I: industrial<br>□ A: automotive                                                                         |

| □ 6: 67 MHz                                                                       | ■ xxx: Peripheral set                                                                                      |

| ■ d: Flash capacity<br>□ 4: 16 KB<br>□ 5: 32 KB                                   | <ul> <li>Three character numeric</li> <li>No meaning is associated with these three characters.</li> </ul> |

| Example          | $\begin{array}{c c} CY8C & 3 & 4 & 4 & 6 \\ \hline CY8C & 3 & 4 & 4 & 6 \\ \hline \end{array} \begin{array}{c} P & V & I \\ \hline \end{array} \begin{array}{c} - x & x \\ \hline \end{array}$ | x |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|                  | Cypress Prefix                                                                                                                                                                                 |   |

| 3: PSoC 3        | Architecture                                                                                                                                                                                   |   |

| 4: CY8C34 Family | Family Group within Architecture                                                                                                                                                               |   |

| 4: 50 MHz        | Speed Grade                                                                                                                                                                                    |   |

| 6: 64 KB         | Flash Capacity                                                                                                                                                                                 |   |

| PV: SSOP         | Package Code                                                                                                                                                                                   |   |

| I: Industrial    | Temperature Range ————————————————————————————————————                                                                                                                                         |   |

|                  | Peripheral Set                                                                                                                                                                                 |   |

Tape and reel versions of these devices are available and are marked with a "T" at the end of the part number.

All devices in the PSoC 3 CY8C34 family comply to RoHS-6 specifications, demonstrating the commitment by Cypress to lead-free products. Lead (Pb) is an alloying element in solders that has resulted in environmental concerns due to potential toxicity. Cypress uses nickel-palladium-gold (NiPdAu) technology for the majority of leadframe-based packages.

A high level review of the Cypress Pb-free position is available on our website. Specific package information is also available. Package Material Declaration data sheets (PMDDs) identify all substances contained within Cypress packages. PMDDs also confirm the absence of many banned substances. The information in the PMDDs will help Cypress customers plan for recycling or other "end of life" requirements.

# 13. Packaging

## Table 13-1. Package Characteristics

| Parameter       | Description                          | Conditions | Min | Тур   | Max | Units   |

|-----------------|--------------------------------------|------------|-----|-------|-----|---------|

| T <sub>A</sub>  | Operating ambient temperature        |            | -40 | 25.00 | 85  | °C      |

| Tj              | Operating junction temperature       |            | -40 | -     | 100 | °C      |

| T <sub>JA</sub> | Package $\theta_{JA}$ (48-pin SSOP)  |            | -   | 49    | -   | °C/Watt |

| T <sub>JA</sub> | Package $\theta_{JA}$ (48-pin QFN)   |            | -   | 14    | -   | °C/Watt |

| T <sub>JA</sub> | Package $\theta_{JA}$ (68-pin QFN)   |            | -   | 15    | _   | °C/Watt |

| T <sub>JA</sub> | Package $\theta_{JA}$ (100-pin TQFP) |            | -   | 34    | -   | °C/Watt |

| T <sub>JC</sub> | Package $\theta_{JC}$ (48-pin SSOP)  |            | -   | 24    | -   | °C/Watt |

| T <sub>JC</sub> | Package $\theta_{JC}$ (48-pin QFN)   |            | -   | 15    | _   | °C/Watt |

| T <sub>JC</sub> | Package $\theta_{JC}$ (68-pin QFN)   |            | -   | 13    | -   | °C/Watt |

| T <sub>JC</sub> | Package $\theta_{JC}$ (100-pin TQFP) |            | -   | 10    | -   | °C/Watt |

### Table 13-2. Solder Reflow Peak Temperature

| Package      | Maximum Peak<br>Temperature | Maximum Time at Peak<br>Temperature |

|--------------|-----------------------------|-------------------------------------|

| 48-pin SSOP  | 260 °C                      | 30 seconds                          |

| 48-pin QFN   | 260 °C                      | 30 seconds                          |

| 68-pin QFN   | 260 °C                      | 30 seconds                          |

| 100-pin TQFP | 260 °C                      | 30 seconds                          |

Table 13-3. Package Moisture Sensitivity Level (MSL), IPC/JEDEC J-STD-2

| Package      | MSL   |

|--------------|-------|

| 48-pin SSOP  | MSL 3 |

| 48-pin QFN   | MSL 3 |

| 68-pin QFN   | MSL 3 |

| 100-pin TQFP | MSL 3 |

| Documen  | Description Title: PSoC <sup>®</sup> 3: CY8C34 Family Datasheet Programmable System-on-Chip (PSoC <sup>®</sup> ) (continued)<br>Document Number: 001-53304 |                    |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|