#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | 8051                                                                        |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 50MHz                                                                       |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART                          |

| Peripherals                | CapSense, DMA, LCD, POR, PWM, WDT                                           |

| Number of I/O              | 62                                                                          |

| Program Memory Size        | 64KB (64K x 8)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 2K x 8                                                                      |

| RAM Size                   | 8K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                                |

| Data Converters            | A/D 16x12b; D/A 2x8b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 100-LQFP                                                                    |

| Supplier Device Package    | 100-TQFP (14x14)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c3446axi-105t |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **More Information**

Cypress provides a wealth of data at www.cypress.com to help you to select the right PSoC device for your design, and to help you to quickly and effectively integrate the device into your design. For a comprehensive list of resources, see the knowledge base article KBA86521, How to Design with PSoC 3, PSoC 4, and PSoC 5LP. Following is an abbreviated list for PSoC 3:

- Overview: PSoC Portfolio, PSoC Roadmap

- Product Selectors: PSoC 1, PSoC 3, PSoC 4, PSoC 5LP In addition, PSoC Creator includes a device selection tool.

- Application notes: Cypress offers a large number of PSoC application notes and code examples covering a broad range of topics, from basic to advanced level. Recommended application notes for getting started with PSoC 3 are:

- AN54181: Getting Started With PSoC 3

- AN61290: Hardware Design Considerations

- AN57821: Mixed Signal Circuit Board Layout

- AN58304: Pin Selection for Analog Designs

- AN81623: Digital Design Best Practices

- AN73854: Introduction To Bootloaders

using the PSoC Creator IDE C compiler

- Development Kits:

- CY8CKIT-030 is designed for analog performance, for developing high-precision analog, low-power, and low-voltage applications.

- CY8CKIT-001 provides a common development platform for any one of the PSoC 1, PSoC 3, PSoC 4, or PSoC 5LP families of devices.

- The MiniProg3 device provides an interface for flash programming and debug.

- Technical Reference Manuals (TRM)

- Architecture TRM

- Registers TRM

- Programming Specification

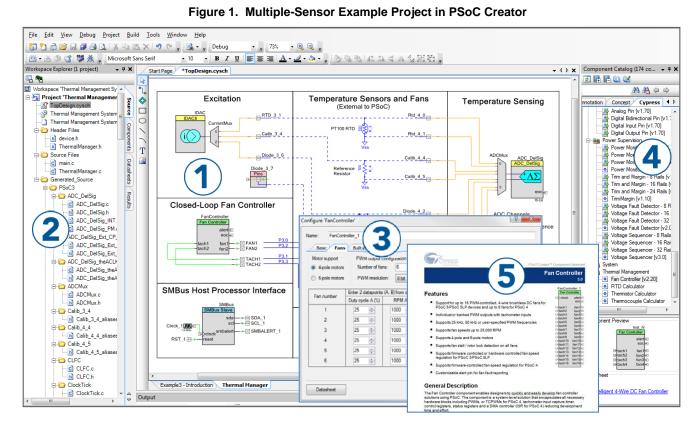

# PSoC Creator

PSoC Creator is a free Windows-based Integrated Design Environment (IDE). It enables concurrent hardware and firmware design of PSoC 3, PSoC 4, and PSoC 5LP based systems. Create designs using classic, familiar schematic capture supported by over 100 pre-verified, production-ready PSoC Components; see the list of component datasheets. With PSoC Creator, you can:

1. Drag and drop component icons to build your hardware system design in the main design workspace

2. Codesign your application firmware with the PSoC hardware,

- 3. Configure components using the configuration tools

- 4. Explore the library of 100+ components

- 5. Review component datasheets

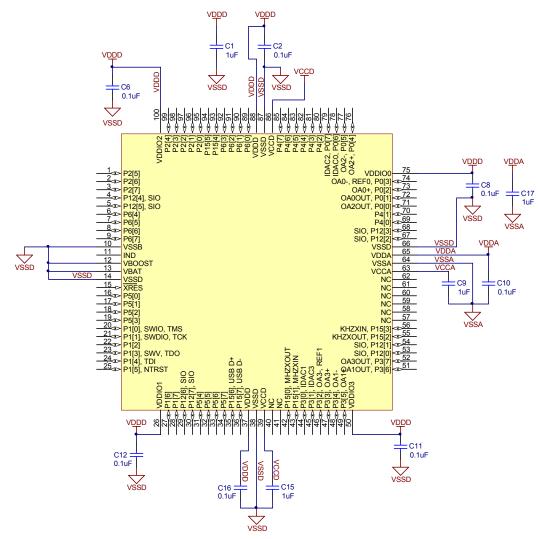

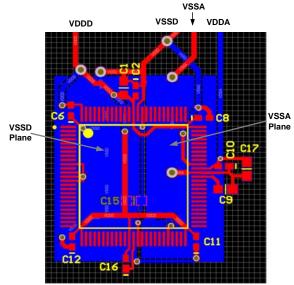

Figure 2-7 and Figure 2-8 on page 11 show an example schematic and an example PCB layout, for the 100-pin TQFP part, for optimal analog performance on a two-layer board.

- The two pins labeled VDDD must be connected together.

- The two pins labeled VCCD must be connected together, with capacitance added, as shown in Figure 2-7 and Power System on page 30. The trace between the two VCCD pins should be as short as possible.

- The two pins labeled VSSD must be connected together.

For information on circuit board layout issues for mixed signals, refer to the application note AN57821 - Mixed Signal Circuit Board Layout Considerations for PSoC® 3 and PSoC 5.

### Figure 2-7. Example Schematic for 100-pin TQFP Part With Power Connections

**Note** The two VCCD pins must be connected together with as short a trace as possible. A trace under the device is recommended, as shown in Figure 2-8 on page 11.

For more information on pad layout, refer to http://www.cypress.com/cad-resources/psoc-3-cad-libraries.

## Figure 2-8. Example PCB Layout for 100-pin TQFP Part for Optimal Analog Performance

# 3. Pin Descriptions

### IDAC0, IDAC2

Low resistance output pin for high current DACs (IDAC).

#### OpAmp0out, OpAmp2out

High current output of uncommitted opamp<sup>[11]</sup>.

#### Extref0, Extref1

External reference input to the analog system.

#### Opamp0-, Opamp2-

Inverting input to uncommitted opamp.

#### Opamp0+, Opamp2+

Noninverting input to uncommitted opamp.

#### GPIO

General purpose I/O pin provides interfaces to the CPU, digital peripherals, analog peripherals, interrupts, LCD segment drive, and CapSense<sup>[11]</sup>.

#### I2C0: SCL, I2C1: SCL

$I^2C$  SCL line providing wake from sleep on an address match. Any I/O pin can be used for  $I^2C$  SCL if wake from sleep is not required.

## I2C0: SDA, I2C1: SDA

$I^2C$  SDA line providing wake from sleep on an address match. Any I/O pin can be used for  $I^2C$  SDA if wake from sleep is not required.

## Ind

Inductor connection to boost pump.

### kHz XTAL: Xo, kHz XTAL: Xi

32.768-kHz crystal oscillator pin.

Note

11. GPIOs with opamp outputs are not recommended for use with CapSense.

### MHz XTAL: Xo, MHz XTAL: Xi

4- to 25-MHz crystal oscillator pin.

## nTRST

Optional JTAG test reset programming and debug port connection to reset the JTAG connection.

### SIO

Special I/O provides interfaces to the CPU, digital peripherals and interrupts with a programmable high threshold voltage, analog comparator, high sink current, and high impedance state when the device is unpowered.

#### SWDCK

Serial wire debug clock programming and debug port connection.

## SWDIO

Serial wire debug input and output programming and debug port connection.

## SWV

Single wire viewer debug output.

## тск

JTAG test clock programming and debug port connection.

## TDI

JTAG test data In programming and debug port connection.

## TDO

JTAG test data out programming and debug port connection.

## TMS

JTAG test mode select programming and debug port connection.

## 4.4 DMA and PHUB

The PHUB and the DMA controller are responsible for data transfer between the CPU and peripherals, and also data transfers between peripherals. The PHUB and DMA also control device configuration during boot. The PHUB consists of:

- A central hub that includes the DMA controller, arbiter, and router

- Multiple spokes that radiate outward from the hub to most peripherals

There are two PHUB masters: the CPU and the DMA controller. Both masters may initiate transactions on the bus. The DMA channels can handle peripheral communication without CPU intervention. The arbiter in the central hub determines which DMA channel is the highest priority if there are multiple requests.

#### 4.4.1 PHUB Features

- CPU and DMA controller are both bus masters to the PHUB

- Eight Multi-layer AHB Bus parallel access paths (spokes) for peripheral access

- Simultaneous CPU and DMA access to peripherals located on different spokes

- Simultaneous DMA source and destination burst transactions on different spokes

- Supports 8, 16, 24, and 32-bit addressing and data

### Table 4-6. PHUB Spokes and Peripherals

| PHUB Spokes | Peripherals                                                                                         |

|-------------|-----------------------------------------------------------------------------------------------------|

| 0           | SRAM                                                                                                |

| 1           | IOs, PICU, EMIF                                                                                     |

| 2           | PHUB local configuration, Power manager,<br>Clocks, IC, SWV, EEPROM, Flash<br>programming interface |

| 3           | Analog interface and trim, Decimator                                                                |

| 4           | USB, CAN, I <sup>2</sup> C, Timers, Counters, and PWMs                                              |

| 5           | Reserved                                                                                            |

| 6           | UDBs group 1                                                                                        |

| 7           | UDBs group 2                                                                                        |

### 4.4.2 DMA Features

- Twenty-four DMA channels

- Each channel has one or more Transaction Descriptors (TDs) to configure channel behavior. Up to 128 total TDs can be defined

- TDs can be dynamically updated

- Eight levels of priority per channel

- Any digitally routable signal, the CPU, or another DMA channel, can trigger a transaction

- Each channel can generate up to two interrupts per transfer

- Transactions can be stalled or canceled

- Supports transaction size of infinite or 1 to 64 KB

- TDs may be nested and/or chained for complex transactions

#### 4.4.3 Priority Levels

The CPU always has higher priority than the DMA controller when their accesses require the same bus resources. Due to the system architecture, the CPU can never starve the DMA. DMA channels of higher priority (lower priority number) may interrupt current DMA transfers. In the case of an interrupt, the current transfer is allowed to complete its current transaction. To ensure latency limits when multiple DMA accesses are requested simultaneously, a fairness algorithm guarantees an interleaved minimum percentage of bus bandwidth for priority levels 2 through 7. Priority levels 0 and 1 do not take part in the fairness algorithm and may use 100 percent of the bus bandwidth. If a tie occurs on two DMA requests of the same priority level, a simple round robin method is used to evenly share the allocated bandwidth. The round robin allocation can be disabled for each DMA channel, allowing it to always be at the head of the line. Priority levels 2 to 7 are guaranteed the minimum bus bandwidth shown in Table 4-7 after the CPU and DMA priority levels 0 and 1 have satisfied their requirements.

#### Table 4-7. Priority Levels

| Priority Level | % Bus Bandwidth |

|----------------|-----------------|

| 0              | 100.0           |

| 1              | 100.0           |

| 2              | 50.0            |

| 3              | 25.0            |

| 4              | 12.5            |

| 5              | 6.2             |

| 6              | 3.1             |

| 7              | 1.5             |

When the fairness algorithm is disabled, DMA access is granted based solely on the priority level; no bus bandwidth guarantees are made.

#### 4.4.4 Transaction Modes Supported

The flexible configuration of each DMA channel and the ability to chain multiple channels allow the creation of both simple and complex use cases. General use cases include, but are not limited to:

### 4.4.4.1 Simple DMA

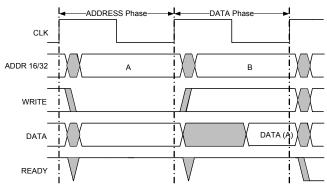

In a simple DMA case, a single TD transfers data between a source and sink (peripherals or memory location). The basic timing diagrams of DMA read and write cycles are shown in Figure 4-1. For more description on other transfer modes, refer to the Technical Reference Manual.

#### Basic DMA Read Transfer without wait states

#### 4.4.4.2 Auto Repeat DMA

Auto repeat DMA is typically used when a static pattern is repetitively read from system memory and written to a peripheral. This is done with a single TD that chains to itself.

#### 4.4.4.3 Ping Pong DMA

A ping pong DMA case uses double buffering to allow one buffer to be filled by one client while another client is consuming the data previously received in the other buffer. In its simplest form, this is done by chaining two TDs together so that each TD calls the opposite TD when complete.

#### 4.4.4.4 Circular DMA

Circular DMA is similar to ping pong DMA except it contains more than two buffers. In this case there are multiple TDs; after the last TD is complete it chains back to the first TD.

#### 4.4.4.5 Scatter Gather DMA

In the case of scatter gather DMA, there are multiple noncontiguous sources or destinations that are required to effectively carry out an overall DMA transaction. For example, a packet may need to be transmitted off of the device and the packet elements, including the header, payload, and trailer, exist in various noncontiguous locations in memory. Scatter gather DMA allows the segments to be concatenated together by using multiple TDs in a chain. The chain gathers the data from the multiple locations. A similar concept applies for the reception of data onto the device. Certain parts of the received data may need to be scattered to various locations in memory for software processing convenience. Each TD in the chain specifies the location for each discrete element in the chain.

#### 4.4.4.6 Packet Queuing DMA

Packet queuing DMA is similar to scatter gather DMA but specifically refers to packet protocols. With these protocols, there may be separate configuration, data, and status phases associated with sending or receiving a packet.

For instance, to transmit a packet, a memory mapped configuration register can be written inside a peripheral, specifying the overall length of the ensuing data phase. The CPU

### Figure 4-1. DMA Timing Diagram

can set up this configuration information anywhere in system memory and copy it with a simple TD to the peripheral. After the configuration phase, a data phase TD (or a series of data phase TDs) can begin (potentially using scatter gather). When the data phase TD(s) finish, a status phase TD can be invoked that reads some memory mapped status information from the peripheral and copies it to a location in system memory specified by the CPU for later inspection. Multiple sets of configuration, data, and status phase "subchains" can be strung together to create larger chains that transmit multiple packets in this way. A similar concept exists in the opposite direction to receive the packets.

#### 4.4.4.7 Nested DMA

One TD may modify another TD, as the TD configuration space is memory mapped similar to any other peripheral. For example, a first TD loads a second TD's configuration and then calls the second TD. The second TD moves data as required by the application. When complete, the second TD calls the first TD, which again updates the second TD's configuration. This process repeats as often as necessary.

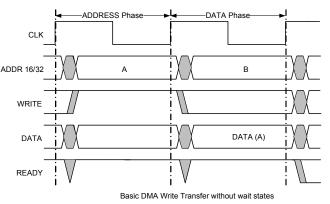

#### 4.5 Interrupt Controller

The interrupt controller provides a mechanism for hardware resources to change program execution to a new address, independent of the current task being executed by the main code. The interrupt controller provides enhanced features not found on original 8051 interrupt controllers:

- Thirty two interrupt vectors

- Jumps directly to ISR anywhere in code space with dynamic vector addresses

- Multiple sources for each vector

- Flexible interrupt to vector matching

- Each interrupt vector is independently enabled or disabled

- Each interrupt can be dynamically assigned one of eight priorities

- Eight level nestable interrupts

- 6: CPU acknowledges the interrupt request

- 7: ISR address is read by CPU for branching

- 8, 9: PEND and POST bits are cleared respectively after receiving the IRA from core

- 10: IRA bit is cleared after completing the current instruction and starting the instruction execution from ISR location (takes 7 cycles)

- 11: IRC is set to indicate the completion of ISR, Active int. status is restored with previous status

The total interrupt latency (ISR execution)

- = POST + PEND + IRQ + IRA + Completing current instruction and branching

- = 1+1+1+2+7 cycles

- = 12 cycles

Figure 4-3. Interrupt Structure

### 6.4.5 Pin Interrupts

All GPIO and SIO pins are able to generate interrupts to the system. All eight pins in each port interface to their own Port Interrupt Control Unit (PICU) and associated interrupt vector. Each pin of the port is independently configurable to detect rising edge, falling edge, both edge interrupts, or to not generate an interrupt.

Depending on the configured mode for each pin, each time an interrupt event occurs on a pin, its corresponding status bit of the interrupt status register is set to "1" and an interrupt request is sent to the interrupt controller. Each PICU has its own interrupt vector in the interrupt controller and the pin status register providing easy determination of the interrupt source down to the pin level.

Port pin interrupts remain active in all sleep modes allowing the PSoC device to wake from an externally generated interrupt.

While level sensitive interrupts are not directly supported; Universal Digital Blocks (UDB) provide this functionality to the system when needed.

#### 6.4.6 Input Buffer Mode

GPIO and SIO input buffers can be configured at the port level for the default CMOS input thresholds or the optional LVTTL input thresholds. All input buffers incorporate Schmitt triggers for input hysteresis. Additionally, individual pin input buffers can be disabled in any drive mode.

#### 6.4.7 I/O Power Supplies

Up to four I/O pin power supplies are provided depending on the device and package. Each I/O supply must be less than or equal to the voltage on the chip's analog (VDDA) pin. This feature allows users to provide different I/O voltage levels for different pins on the device. Refer to the specific device package pinout to determine VDDIO capability for a given port and pin.

The SIO port pins support an additional regulated high output capability, as described in Adjustable Output Level.

#### 6.4.8 Analog Connections

These connections apply only to GPIO pins. All GPIO pins may be used as analog inputs or outputs. The analog voltage present on the pin must not exceed the VDDIO supply voltage to which the GPIO belongs. Each GPIO may connect to one of the analog global busses or to one of the analog mux buses to connect any pin to any internal analog resource such as ADC or comparators. In addition, select pins provide direct connections to specific analog features such as the high current DACs or uncommitted opamps.

#### 6.4.9 CapSense

This section applies only to GPIO pins. All GPIO pins may be used to create CapSense buttons and sliders<sup>[15]</sup>. See the "CapSense" section on page 64 for more information.

#### 6.4.10 LCD Segment Drive

This section applies only to GPIO pins. All GPIO pins may be used to generate Segment and Common drive signals for direct glass drive of LCD glass. See the "LCD Direct Drive" section on page 63 for details.

#### 6.4.11 Adjustable Output Level

This section applies only to SIO pins. SIO port pins support the ability to provide a regulated high output level for interface to external signals that are lower in voltage than the SIO's respective VDDIO. SIO pins are individually configurable to output either the standard VDDIO level or the regulated output, which is based on an internally generated reference. Typically a voltage DAC (VDAC) is used to generate the reference (see Figure 6-13). The "DAC" section on page 64 has more details on VDAC use and reference routing to the SIO pins. Resistive pull-up and pull-down drive modes are not available with SIO in regulated output mode.

#### 6.4.12 Adjustable Input Level

This section applies only to SIO pins. SIO pins by default support the standard CMOS and LVTTL input levels but also support a differential mode with programmable levels. SIO pins are grouped into pairs. Each pair shares a reference generator block which, is used to set the digital input buffer reference level for interface to external signals that differ in voltage from VDDIO. The reference sets the pins voltage threshold for a high logic level (see Figure 6-13). Available input thresholds are:

- 0.5 × VDDIO

- 0.4 × VDDIO

- 0.5 × VREF

- VREF

Typically a voltage DAC (VDAC) generates the V<sub>REF</sub> reference. "DAC" section on page 64 has more details on VDAC use and reference routing to the SIO pins.

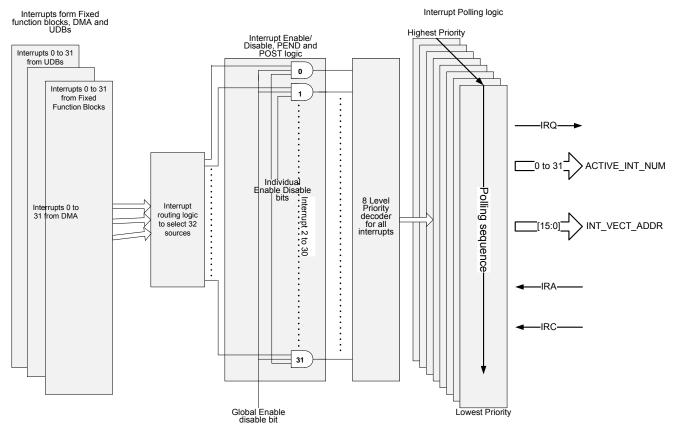

## 7.2.2 Datapath Module

The datapath contains an 8-bit single cycle ALU, with associated compare and condition generation logic. This datapath block is optimized to implement embedded functions, such as timers, counters, integrators, PWMs, PRS, CRC, shifters and dead band generators and many others.

### 7.2.2.1 Working Registers

The datapath contains six primary working registers, which are accessed by CPU firmware or DMA during normal operation.

| Table 7-1. | Working | Datapath | Registers |

|------------|---------|----------|-----------|

|------------|---------|----------|-----------|

| Name      | Function       | Description                                                                                                                                                                                                                   |

|-----------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0 and A1 | Accumulators   | These are sources and sinks for the ALU and also sources for the compares.                                                                                                                                                    |

| D0 and D1 | Data Registers | These are sources for the ALU and sources for the compares.                                                                                                                                                                   |

| F0 and F1 | FIFOs          | These are the primary interface to<br>the system bus. They can be a<br>data source for the data registers<br>and accumulators or they can<br>capture data from the accumu-<br>lators or ALU. Each FIFO is four<br>bytes deep. |

#### 7.2.2.2 Dynamic Configuration RAM

Dynamic configuration is the ability to change the datapath function and internal configuration on a cycle-by-cycle basis, under sequencer control. This is implemented using the 8-word × 16-bit configuration RAM, which stores eight unique 16-bit wide configurations. The address input to this RAM controls the sequence, and can be routed from any block connected to the UDB routing matrix, most typically PLD logic, I/O pins, or from the outputs of this or other datapath blocks.

### ALU

The ALU performs eight general purpose functions. They are:

- Increment

- Decrement

- Add

- Subtract

- Logical AND

The bits of the control register, which may be written to by the system bus, are used to drive into the routing matrix, and thus provide firmware with the opportunity to control the state of UDB processing. The status register is read-only and it allows internal UDB state to be read out onto the system bus directly from internal routing. This allows firmware to monitor the state of UDB processing. Each bit of these registers has programmable connections to the routing matrix and routing connections are made depending on the requirements of the application.

#### 7.2.3.1 Usage Examples

As an example of control input, a bit in the control register can be allocated as a function enable bit. There are multiple ways to enable a function. In one method the control bit output would be routed to the clock control block in one or more UDBs and serve as a clock enable for the selected UDB blocks. A status example is a case where a PLD or datapath block generated a condition, such as a "compare true" condition that is captured and latched by the status register and then read (and cleared) by CPU firmware.

#### 7.2.3.2 Clock Generation

Each subcomponent block of a UDB including the two PLDs, the datapath, and Status and Control, has a clock selection and control block. This promotes a fine granularity with respect to allocating clocking resources to UDB component blocks and allows unused UDB resources to be used by other functions for maximum system efficiency.

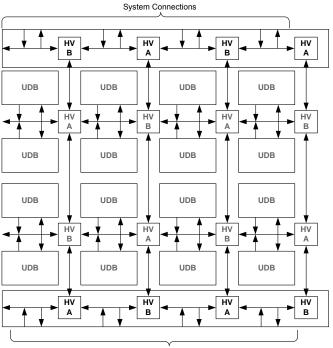

## 7.3 UDB Array Description

Figure 7-7 shows an example of a 16 UDB array. In addition to the array core, there are a DSI routing interfaces at the top and bottom of the array. Other interfaces that are not explicitly shown include the system interfaces for bus and clock distribution. The UDB array includes multiple horizontal and vertical routing channels each comprised of 96 wires. The wire connections to UDBs, at horizontal/vertical intersection and at the DSI interface are highly permutable providing efficient automatic routing in PSoC Creator. Additionally the routing allows wire by wire segmentation along the vertical and horizontal routing to further increase routing flexibility and capability.

#### Figure 7-7. Digital System Interface Structure

System Connections

### 7.3.1 UDB Array Programmable Resources

Figure 7-8 shows an example of how functions are mapped into a bank of 16 UDBs. The primary programmable resources of the UDB are two PLDs, one datapath and one status/control register. These resources are allocated independently, because they have independently selectable clocks, and therefore unused blocks are allocated to other unrelated functions.

An example of this is the 8-bit Timer in the upper left corner of the array. This function only requires one datapath in the UDB, and therefore the PLD resources may be allocated to another function. A function such as a Quadrature Decoder may require more PLD logic than one UDB can supply and in this case can utilize the unused PLD blocks in the 8-bit Timer UDB. Programmable resources in the UDB array are generally homogeneous so functions can be mapped to arbitrary boundaries in the array.

## Table 11-2. DC Specifications (continued)

| Parameter | Description                                                       | Conditions                                                               |                         | Min | <b>Typ</b> <sup>[25]</sup> | Max | Units    |

|-----------|-------------------------------------------------------------------|--------------------------------------------------------------------------|-------------------------|-----|----------------------------|-----|----------|

|           | Sleep Mode <sup>[28]</sup>                                        |                                                                          |                         |     |                            |     |          |

|           | CPU = OFF                                                         | V <sub>DD</sub> = V <sub>DDIO</sub> =                                    | T = -40 °C              | _   | 1.1                        | 2.3 | μA       |

|           |                                                                   | 4.5 V - 5.5 V                                                            | T = 25 °C               | _   | 1.1                        | 2.2 |          |

|           | mode)<br>Sleep timer = ON (= ILO ON at 1 kHz) <sup>[29]</sup>     |                                                                          | T = 85 °C               | _   | 15                         | 30  |          |

|           | WDT = OFF                                                         | V <sub>DD</sub> = V <sub>DDIO</sub> =                                    | T = -40 °C              | _   | 1                          | 2.2 |          |

|           | I2C Wake = OFF                                                    | 2.7 V – 3.6 V                                                            | T = 25 °C               | _   | 1                          | 2.1 |          |

|           | Comparator = OFF<br>POR = ON                                      |                                                                          | T = 85 °C               | _   | 12                         | 28  |          |

|           | Boost = OFF                                                       | $V_{DD} = V_{DDIO} = _{root}$                                            | T = 25 °C               | _   | 2.2                        | 4.2 |          |

|           | SIO pins in single ended input, unregu-<br>lated output mode      | $1.71 \text{ V} - 1.95 \text{ V}^{[30]}$                                 | 1-23 0                  |     | 2.2                        | 7.2 |          |

|           | Comparator = ON<br>CPU = OFF                                      | V <sub>DD</sub> = V <sub>DDIO</sub> =<br>2.7 V – 3.6 V <sup>[31]</sup>   | T = 25 °C               | -   | 2.2                        | 2.7 |          |

|           | RTC = OFF                                                         |                                                                          |                         |     |                            |     |          |

|           | Sleep timer = OFF                                                 |                                                                          |                         |     |                            |     |          |

|           | WDT = OFF<br>I2C Wake = OFF                                       |                                                                          |                         |     |                            |     |          |

|           | POR = ON                                                          |                                                                          |                         |     |                            |     |          |

|           | Boost = OFF                                                       |                                                                          |                         |     |                            |     |          |

|           | SIO pins in single ended input, unregu-<br>lated output mode      |                                                                          |                         |     |                            |     |          |

|           | I2C Wake = ON                                                     | V <sub>DD</sub> = V <sub>DDIO</sub> =<br>2.7 V – 3.6 V <sup>[31]</sup>   | T = 25 °C               | -   | 2.2                        | 2.8 |          |

|           | CPU = OFF<br>RTC = OFF                                            | 2.7 V – 3.6 V <sup>[31]</sup>                                            |                         |     |                            |     |          |

|           | Sleep timer = OFF                                                 |                                                                          |                         |     |                            |     |          |

|           | WDT = OFF                                                         |                                                                          |                         |     |                            |     |          |

|           | Comparator = OFF                                                  |                                                                          |                         |     |                            |     |          |

|           | POR = ON<br>Boost = OFF                                           |                                                                          |                         |     |                            |     |          |

|           | SIO pins in single ended input, unregu-                           |                                                                          |                         |     |                            |     |          |

|           | lated output mode                                                 |                                                                          |                         |     |                            |     |          |

|           | Hibernate Mode <sup>[28]</sup>                                    |                                                                          | T (0.00                 | -   |                            |     |          |

|           | Hibernate mode current<br>All regulators and oscillators off      | V <sub>DD</sub> = V <sub>DDIO</sub> =<br>4.5 V - 5.5 V                   | T = -40 °C<br>T = 25 °C | -   | 0.2                        | 1.5 | μΑ       |

|           | SRAM retention                                                    |                                                                          |                         | -   | 0.5                        | 1.5 |          |

|           | GPIO interrupts are active<br>Boost = OFF                         |                                                                          | T = 85 °C               | _   | 4.1                        | 5.3 |          |

|           | SIO pins in single ended input, unregu-                           | V <sub>DD</sub> = V <sub>DDIO</sub> =<br>2.7 V – 3.6 V                   | T = -40 °C              | -   | 0.2                        | 1.5 |          |

|           | lated output                                                      |                                                                          | T = 25 °C               | -   | 0.2                        | 1.5 |          |

|           | mode                                                              |                                                                          | T = 85 °C               | -   | 3.2                        | 4.2 |          |

|           |                                                                   | V <sub>DD</sub> = V <sub>DDIO</sub> =<br>1.71 V – 1.95 V <sup>[30]</sup> | T = -40 °C              | _   | 0.2                        | 1.5 |          |

|           |                                                                   |                                                                          | T = 25 °C               | _   | 0.3                        | 1.5 | _        |

|           |                                                                   |                                                                          | T = 85 °C               | -   | 3.3                        | 4.3 | <u> </u> |

| DDAR      | Analog current consumption while device is reset <sup>[32]</sup>  | 55.1                                                                     |                         | -   | 0.3                        | 0.6 | mA       |

|           |                                                                   | V <sub>DDA</sub> > 3.6 V                                                 |                         | -   | 1.4                        | 3.3 | mA       |

| DDDR      | Digital current consumption while device is reset <sup>[32]</sup> | 000                                                                      |                         | _   | 1.1                        | 3.1 | mA       |

|           | 16261                                                             | $V_{DDD} > 3.6 V$                                                        |                         | -   | 0.7                        | 3.1 | mA       |

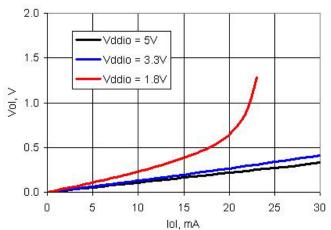

5 4 Voh, V 3 2 Vddio = 5V Vddio = 3.3V 1 Vddio = 1.8V 0 10 0 5 15 20 25 30 loh, mA

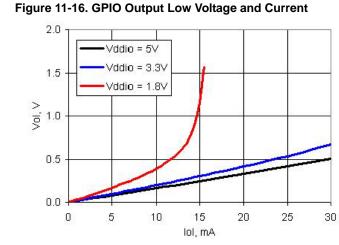

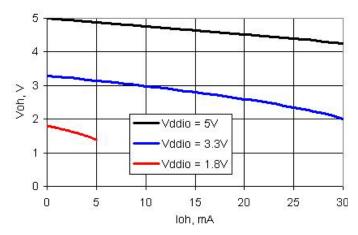

## Figure 11-15. GPIO Output High Voltage and Current

## Table 11-10. GPIO AC Specifications

| Parameter | Description                                                                             | Conditions                            | Min | Тур | Max | Units |

|-----------|-----------------------------------------------------------------------------------------|---------------------------------------|-----|-----|-----|-------|

| TriseF    | Rise time in Fast Strong Mode <sup>[41]</sup>                                           | 3.3 V V <sub>DDIO</sub> Cload = 25 pF | -   | -   | 6   | ns    |

| TfallF    | Fall time in Fast Strong Mode <sup>[41]</sup>                                           | 3.3 V V <sub>DDIO</sub> Cload = 25 pF | -   | -   | 6   | ns    |

| TriseS    | Rise time in Slow Strong Mode <sup>[41]</sup>                                           | 3.3 V V <sub>DDIO</sub> Cload = 25 pF | -   | -   | 60  | ns    |

| TfallS    | Fall time in Slow Strong Mode <sup>[41]</sup>                                           | 3.3 V V <sub>DDIO</sub> Cload = 25 pF | -   | -   | 60  | ns    |

| Fgpioout  | GPIO output operating frequency                                                         |                                       |     |     |     |       |

|           | $2.7 \text{ V} \leq \text{V}_{\text{DDIO}} \leq 5.5 \text{ V}$ , fast strong drive mode | 90/10% V <sub>DDIO</sub> into 25 pF   | -   | -   | 33  | MHz   |

|           | $1.71 \text{ V} \leq \text{V}_{\text{DDIO}} < 2.7 \text{ V}$ , fast strong drive mode   | 90/10% V <sub>DDIO</sub> into 25 pF   | -   | -   | 20  | MHz   |

|           | $3.3 \text{ V} \leq \text{V}_{\text{DDIO}} \leq 5.5 \text{ V}$ , slow strong drive mode | 90/10% V <sub>DDIO</sub> into 25 pF   | -   | -   | 7   | MHz   |

|           | 1.71 V $\leq$ V <sub>DDIO</sub> < 3.3 V, slow strong drive mode                         | 90/10% V <sub>DDIO</sub> into 25 pF   | -   | -   | 3.5 | MHz   |

| Fgpioin   | GPIO input operating frequency                                                          |                                       | 1   |     |     |       |

| gpioin    | 1.71 V ≤ V <sub>DDIO</sub> ≤ 5.5 V                                                      | 90/10% V <sub>DDIO</sub>              | -   | -   | 33  | MHz   |

<sup>41.</sup> Based on device characterization (Not production tested).

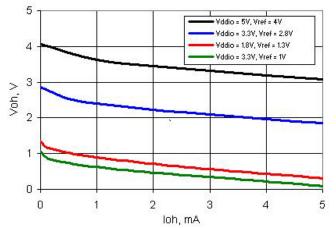

Figure 11-17. SIO Output High Voltage and Current, Unregulated Mode

Figure 11-19. SIO Output High Voltage and Current, Regulated Mode

Table 11-12. SIO AC Specifications

| Parameter | Description                                            | Conditions                               | Min | Тур | Max | Units |

|-----------|--------------------------------------------------------|------------------------------------------|-----|-----|-----|-------|

| TriseF    | Rise time in Fast Strong Mode (90/10%) <sup>[44]</sup> | Cload = 25 pF, V <sub>DDIO</sub> = 3.3 V | -   | -   | 12  | ns    |

| TfallF    | Fall time in Fast Strong Mode (90/10%) <sup>[44]</sup> | Cload = 25 pF, V <sub>DDIO</sub> = 3.3 V | -   | -   | 12  | ns    |

| TriseS    | Rise time in Slow Strong Mode (90/10%) <sup>[44]</sup> | Cload = 25 pF, V <sub>DDIO</sub> = 3.0 V | -   | -   | 75  | ns    |

| TfallS    | Fall time in Slow Strong Mode (90/10%) <sup>[44]</sup> | Cload = 25 pF, V <sub>DDIO</sub> = 3.0 V | _   | _   | 60  | ns    |

## 11.4.4 XRES

## Table 11-17. XRES DC Specifications

| Parameter       | Description                                                   | Conditions | Min                   | Тур | Max                   | Units |

|-----------------|---------------------------------------------------------------|------------|-----------------------|-----|-----------------------|-------|

| V <sub>IH</sub> | Input voltage high threshold                                  |            | $0.7 \times V_{DDIO}$ | -   | -                     | V     |

| V <sub>IL</sub> | Input voltage low threshold                                   |            | -                     | -   | $0.3 \times V_{DDIO}$ | V     |

| Rpullup         | Pull-up resistor                                              |            | 3.5                   | 5.6 | 8.5                   | kΩ    |

| C <sub>IN</sub> | Input capacitance <sup>[46]</sup>                             |            | -                     | 3   | -                     | pF    |

| V <sub>H</sub>  | Input voltage hysteresis<br>(Schmitt-Trigger) <sup>[46]</sup> |            | -                     | 100 | _                     | mV    |

| Idiode          | Current through protection diode to $V_{DDIO}$ and $V_{SSIO}$ |            | -                     | _   | 100                   | μA    |

## Table 11-18. XRES AC Specifications

| Parameter          | Description       | Conditions | Min | Тур | Max | Units |

|--------------------|-------------------|------------|-----|-----|-----|-------|

| T <sub>RESET</sub> | Reset pulse width |            | 1   | -   | -   | μs    |

<sup>46.</sup> Based on device characterization (Not production tested).

## 11.5 Analog Peripherals

Specifications are valid for –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C and T<sub>J</sub>  $\leq$  100 °C, except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted.

## 11.5.1 Opamp

## Table 11-19. Opamp DC Specifications

| Parameter         | Description                                 | Conditions                                                                                                                                                                                                      | Min                     | Тур                                                                                                     | Max                     | Units |

|-------------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|---------------------------------------------------------------------------------------------------------|-------------------------|-------|

| V <sub>IOFF</sub> | Input offset voltage                        |                                                                                                                                                                                                                 | -                       | -                                                                                                       | 2                       | mV    |

| Vos               | Input offset voltage                        |                                                                                                                                                                                                                 | -                       | -                                                                                                       | 2.5                     | mV    |

|                   |                                             | Operating temperature –40 °C to 70 °C                                                                                                                                                                           | -                       | -                                                                                                       | 2                       | mV    |

| TCVos             | Input offset voltage drift with temperature | Power mode = high                                                                                                                                                                                               | -                       | -                                                                                                       | ±30                     | µV/°C |

| Ge1               | Gain error, unity gain buffer mode          | Rload = 1 kΩ                                                                                                                                                                                                    | -                       | -                                                                                                       | ±0.1                    | %     |

| Cin               | Input capacitance                           | Routing from pin                                                                                                                                                                                                | -                       | -                                                                                                       | 18                      | pF    |

| Vo                | Output voltage range                        | 1 mA, source or sink, power mode = high                                                                                                                                                                         | V <sub>SSA</sub> + 0.05 | -                                                                                                       | V <sub>DDA</sub> – 0.05 | V     |

| lout              | Output current capability, source or sink   | $V_{SSA}$ + 500 mV $\leq$ Vout $\leq$ V <sub>DDA</sub><br>-500 mV, V <sub>DDA</sub> > 2.7 V                                                                                                                     | 25                      | -                                                                                                       | -                       | mA    |

|                   |                                             | $\label{eq:VSSA} \begin{array}{l} \text{V}_{\text{SSA}} \mbox{ + 500 mV} \leq \mbox{Vout} \leq \mbox{V}_{\text{DDA}} \\ -500 \mbox{ mV}, \mbox{ 1.7 V} \mbox{ = V}_{\text{DDA}} \leq \mbox{ 2.7 V} \end{array}$ | 16                      | $ \begin{array}{c cccc} - & 2.5 \\ - & 2 \\ \hline - & \pm 30 \\ - & \pm 0.1 \\ - & 18 \\ \end{array} $ | mA                      |       |

| ldd               | Quiescent current                           | Power mode = min                                                                                                                                                                                                | -                       | 250                                                                                                     | 400                     | uA    |

|                   |                                             | Power mode = low                                                                                                                                                                                                | -                       | 250                                                                                                     | 400                     | uA    |

|                   |                                             | Power mode = med                                                                                                                                                                                                | -                       | 330                                                                                                     | 950                     | uA    |

|                   |                                             | Power mode = high                                                                                                                                                                                               | -                       | 1000                                                                                                    | 2500                    | uA    |

| CMRR              | Common mode rejection ratio                 |                                                                                                                                                                                                                 | 80                      | -                                                                                                       | -                       | dB    |

| PSRR              | Power supply rejection ratio                | $V_{DDA} \ge 2.7 V$                                                                                                                                                                                             | 85                      | -                                                                                                       | -                       | dB    |

|                   |                                             | V <sub>DDA</sub> < 2.7 V                                                                                                                                                                                        | 70                      | -                                                                                                       | -                       | dB    |

| I <sub>IB</sub>   | Input bias current <sup>[47]</sup>          | 25 °C                                                                                                                                                                                                           | -                       | 10                                                                                                      | -                       | pА    |

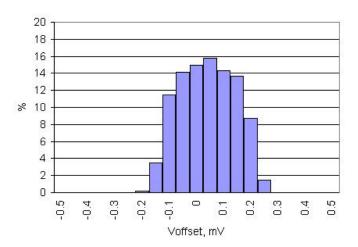

Figure 11-25. Opamp Voffset Histogram, 3388 samples/847 parts, 25 °C,  $V_{DDA}$  = 5 V

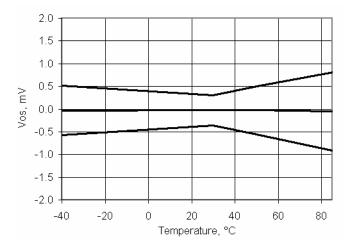

Figure 11-26. Opamp Voffset vs Temperature, V<sub>DDA</sub> = 5V

#### Note

47. Based on device characterization (Not production tested).

## 11.5.7 Voltage Digital to Analog Converter (VDAC)

See the VDAC component datasheet in PSoC Creator for full electrical specifications and APIs.

Unless otherwise specified, all charts and graphs show typical values.

## Table 11-30. VDAC DC Specifications

| Parameter        | Description                               | Conditions                        | Min | Тур  | Max  | Units   |

|------------------|-------------------------------------------|-----------------------------------|-----|------|------|---------|

|                  | Resolution                                |                                   | -   | 8    | -    | bits    |

| INL1             | Integral nonlinearity                     | 1 V scale                         | -   | ±2.1 | ±2.5 | LSB     |

| INL4             | Integral nonlinearity <sup>[55]</sup>     | 4 V scale                         | -   | ±2.1 | ±2.5 | LSB     |

| DNL1             | Differential nonlinearity                 | 1 V scale                         | -   | ±0.3 | ±1   | LSB     |

| DNL4             | Differential nonlinearity <sup>[55]</sup> | 4 V scale                         | -   | ±0.3 | ±1   | LSB     |

| Rout             | Output resistance                         | 1 V scale                         | -   | 4    | -    | kΩ      |

|                  |                                           | 4 V scale                         | -   | 16   | -    | kΩ      |

| V <sub>OUT</sub> | Output voltage range, code = 255          | 1 V scale                         | -   | 1.02 | -    | V       |

|                  |                                           | 4 V scale, V <sub>DDA</sub> = 5 V | -   | 4.08 | -    | V       |

|                  | Monotonicity                              |                                   | -   | -    | Yes  | -       |

| V <sub>OS</sub>  | Zero scale error                          |                                   | -   | 0    | ±0.9 | LSB     |

| Eg               | Gain error                                | 1 V scale                         | -   | -    | ±2.5 | %       |

|                  |                                           | 4 V scale                         | -   | -    | ±2.5 | %       |

| TC_Eg            | Temperature coefficient, gain error       | 1 V scale                         | -   | -    | 0.03 | %FSR/°C |

|                  |                                           | 4 V scale                         | -   | -    | 0.03 | %FSR/°C |

| I <sub>DD</sub>  | Operating current                         | Low speed mode                    | -   | -    | 100  | μA      |

|                  |                                           | High speed mode                   | -   | -    | 500  | μA      |

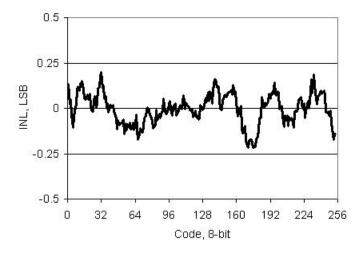

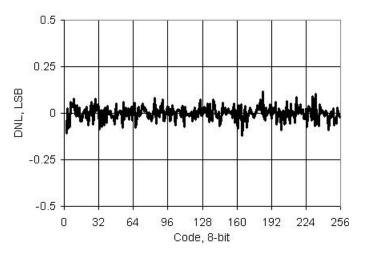

## Figure 11-48. VDAC INL vs Input Code, 1 V Mode

## Figure 11-49. VDAC DNL vs Input Code, 1 V Mode

Note 55. Based on device characterization (Not production tested).

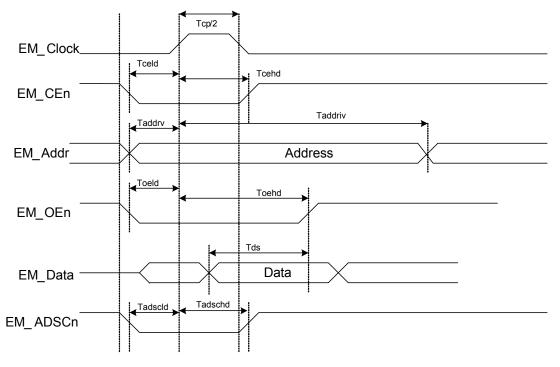

Figure 11-66. Synchronous Read Cycle Timing

## Table 11-63. Synchronous Read Cycle Specifications

| Parameter | Description                       | Conditions          | Min     | Тур | Max | Units |

|-----------|-----------------------------------|---------------------|---------|-----|-----|-------|

| Т         | EMIF clock period <sup>[66]</sup> | $V_{DDA} \ge 3.3 V$ | 30.3    | -   | -   | ns    |

| Tcp/2     | EM_Clock pulse high               |                     | T/2     | _   | -   | ns    |

| Tceld     | EM_CEn low to EM_Clock high       |                     | 5       | -   | -   | ns    |

| Tcehd     | EM_Clock high to EM_CEn high      |                     | T/2 – 5 | -   | -   | ns    |

| Taddrv    | EM_Addr valid to EM_Clock high    |                     | 5       | -   | -   | ns    |

| Taddriv   | EM_Clock high to EM_Addr invalid  |                     | T/2 – 5 | -   | -   | ns    |

| Toeld     | EM_OEn low to EM_Clock high       |                     | 5       | -   | -   | ns    |

| Toehd     | EM_Clock high to EM_OEn high      |                     | Т       | -   | -   | ns    |

| Tds       | Data valid before EM_OEn high     |                     | T + 15  | -   | -   | ns    |

| Tadscld   | EM_ADSCn low to EM_Clock high     |                     | 5       | -   | -   | ns    |

| Tadschd   | EM_Clock high to EM_ADSCn high    |                     | T/2 – 5 | -   | _   | ns    |

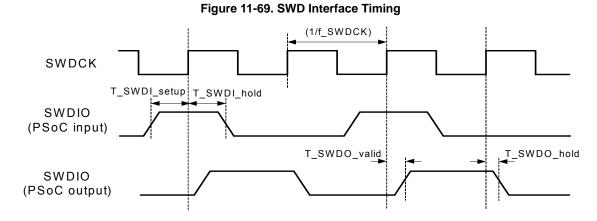

### 11.8.5 SWD Interface

## Table 11-71. SWD Interface AC Specifications<sup>[71]</sup>

| Parameter    | Description                         | Conditions                                                  | Min | Тур | Max                 | Units |

|--------------|-------------------------------------|-------------------------------------------------------------|-----|-----|---------------------|-------|

| f_SWDCK      | SWDCLK frequency                    | $3.3~V \leq V_{DDD} \leq 5~V$                               | -   | -   | 14 <sup>[72]</sup>  | MHz   |

|              |                                     | $1.71 \text{ V} \le \text{V}_{\text{DDD}} < 3.3 \text{ V}$  | -   | -   | 7 <sup>[72]</sup>   | MHz   |

|              |                                     | 1.71 V $\leq$ V <sub>DDD</sub> < 3.3 V, SWD over USBIO pins | _   | _   | 5.5 <sup>[72]</sup> | MHz   |

| T_SWDI_setup | SWDIO input setup before SWDCK high | T = 1/f_SWDCK max                                           | T/4 | -   | -                   | -     |

| T_SWDI_hold  | SWDIO input hold after SWDCK high   | T = 1/f_SWDCK max                                           | T/4 | -   | -                   | -     |

| T_SWDO_valid | SWDCK high to SWDIO output          | T = 1/f_SWDCK max                                           | I   | _   | 2T/5                | _     |

## 11.8.6 SWV Interface

## Table 11-72. SWV Interface AC Specifications<sup>[71]</sup>

| Parameter | Description           | Conditions | Min | Тур | Max | Units |

|-----------|-----------------------|------------|-----|-----|-----|-------|

|           | SWV mode SWV bit rate |            | -   | _   | 33  | Mbit  |

71. Based on device characterization (Not production tested).

72. ff\_SWDCK must also be no more than 1/3 CPU clock frequency.

# 11.9 Clocking

Specifications are valid for –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C and T<sub>J</sub>  $\leq$  100 °C, except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted.

11.9.1 Internal Main Oscillator

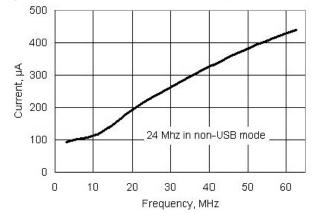

### Table 11-73. IMO DC Specifications

| Parameter | Description           | Conditions                         | Min | Тур | Max | Units |

|-----------|-----------------------|------------------------------------|-----|-----|-----|-------|

|           | Supply current        |                                    |     |     |     |       |

|           | 24 MHz – USB mode     | With oscillator locking to USB bus | -   | -   | 500 | μA    |

|           | 24 MHz – non USB mode |                                    | _   | _   | 300 | μA    |

|           | 12 MHz                |                                    | -   | _   | 200 | μA    |

|           | 6 MHz                 |                                    | -   | _   | 180 | μA    |

|           | 3 MHz                 |                                    | -   | _   | 150 | μΑ    |

### Figure 11-70. IMO Current vs. Frequency

### Table 11-74. IMO AC Specifications

| Parameter        | Description                                | Description Conditions Min                   |       |     |      |    |  |

|------------------|--------------------------------------------|----------------------------------------------|-------|-----|------|----|--|

|                  | IMO frequency stability (with factory trim | )                                            |       |     |      |    |  |

|                  | 24 MHz – Non USB mode                      |                                              | -4    | -   | 4    | %  |  |

| -                | 24 MHz – USB mode                          | With oscillator locking to USB bus           | -0.25 | _   | 0.25 | %  |  |

| F <sub>IMO</sub> | 12 MHz                                     |                                              | -3    | -   | 3    | %  |  |

|                  | 6 MHz                                      |                                              | -2    | _   | 2    | %  |  |

|                  | 3 MHz                                      |                                              | -2    | _   | 2    | %  |  |

|                  | Startup time <sup>[73]</sup>               | From enable (during normal system operation) | -     | _   | 13   | μs |  |

|                  | Jitter (peak to peak) <sup>[73]</sup>      |                                              |       |     |      | 1  |  |

| Jp-p             | F = 24 MHz                                 |                                              | -     | 0.9 | _    | ns |  |

|                  | F = 3 MHz                                  |                                              | 1     | 1.6 | _    | ns |  |

|                  | Jitter (long term) <sup>[73]</sup>         | · · · · · · · · · · · · · · · · · · ·        |       | I   | 1    |    |  |

| Jperiod          | F = 24 MHz                                 |                                              | _     | 0.9 | -    | ns |  |

|                  | F = 3 MHz                                  |                                              | -     | 12  | -    | ns |  |

Note

73. Based on device characterization (Not production tested).

# **12. Ordering Information**

In addition to the features listed in Table 12-1, every CY8C34 device includes: a precision on-chip voltage reference, precision oscillators, flash, ECC, DMA, a fixed function I<sup>2</sup>C, 4 KB trace RAM, JTAG/SWD programming and debug, external memory interface, and more. In addition to these features, the flexible UDBs and analog subsection support a wide range of peripherals. To assist you in selecting the ideal part, PSoC Creator makes a part recommendation after you choose the components required by your application. All CY8C34 derivatives incorporate device and flash security in user-selectable security levels; see the TRM for details.

| Table 12-1. | CY8C34 | Family with | Single C | vcle 8051 |

|-------------|--------|-------------|----------|-----------|

|             | 010004 | i anny with |          |           |

|                 | -               | NCU        | l Coi     | re          |                   |                | Ana | log        |                                        |        |     |          |                      | Dig              | gital  |          |           | I/O  | [81] |       |              |                         |

|-----------------|-----------------|------------|-----------|-------------|-------------------|----------------|-----|------------|----------------------------------------|--------|-----|----------|----------------------|------------------|--------|----------|-----------|------|------|-------|--------------|-------------------------|

| Part Number     | CPU Speed (MHz) | Flash (KB) | SRAM (KB) | EEPROM (KB) | LCD Segment Drive | ADC            | DAC | Comparator | SC/CT<br>Analog Blocks <sup>[79]</sup> | Opamps | DFB | CapSense | UDBs <sup>[80]</sup> | 16-bit Timer/PWM | FS USB | CAN 2.0b | Total I/O | GPIO | SIO  | USBIO | Package      | JTAG ID <sup>[82]</sup> |

| 16 KB Flash     |                 |            |           |             |                   |                |     |            |                                        |        |     |          |                      |                  |        |          |           |      |      |       |              |                         |

| CY8C3444LTI-110 | 50              | 16         | 2         | 0.5         | ~                 | 12-bit Del-Sig | 2   | 4          | 2                                      | 2      | -   | ~        | 16                   | 4                | -      | -        | 46        | 38   | 8    | 0     | 68-pin QFN   | 0×1E06E069              |

| CY8C3444LTI-119 | 50              | 16         | 2         | 0.5         | 2                 | 12-bit Del-Sig | 2   | 4          | 2                                      | 2      | -   | ~        | 16                   | 4                | -      | -        | 29        | 25   | 4    | 0     | 48-pin QFN   | 0×1E077069              |

| CY8C3444PVI-100 | 50              | 16         | 2         | 0.5         | ۲                 | 12-bit Del-Sig | 2   | 4          | 2                                      | 2      | -   | ~        | 16                   | 4                | -      | -        | 29        | 25   | 4    | 0     | 48-pin SSOP  | 0×1E064069              |

| 32 KB Flash     |                 |            |           |             |                   |                |     |            |                                        |        |     |          |                      |                  |        |          |           |      |      |       |              |                         |

| CY8C3445AXI-104 | 50              | 32         | 4         | 1           | ~                 | 12-bit Del-Sig | 2   | 4          | 2                                      | 2      | -   | ~        | 20                   | 4                | -      | -        | 70        | 62   | 8    | 0     | 100-pin TQFP | 0×1E068069              |

| CY8C3445LTI-079 | 50              | 32         | 4         | 1           | 2                 | 12-bit Del-Sig | 2   | 4          | 2                                      | 2      | -   | ~        | 20                   | 4                | -      | -        | 46        | 38   | 8    | 0     | 68-pin QFN   | 0×1E04F069              |

| CY8C3445LTI-078 | 50              | 32         | 4         | 1           | 2                 | 12-bit Del-Sig | 2   | 4          | 2                                      | 2      | -   | ~        | 20                   | 4                | -      | -        | 29        | 25   | 4    | 0     | 48-pin QFN   | 0×1E04E069              |

| CY8C3445PVI-094 | 50              | 32         | 4         | 1           | ۲                 | 12-bit Del-Sig | 2   | 4          | 2                                      | 2      | -   | >        | 20                   | 4                | -      | -        | 29        | 25   | 4    | 0     | 48-pin SSOP  | 0×1E05E069              |

| CY8C3445AXI-108 | 50              | 32         | 4         | 1           | >                 | 12-bit Del-Sig | 2   | 4          | 2                                      | 2      | -   | ~        | 20                   | 4                | ~      | -        | 72        | 62   | 8    | 2     | 100-pin TQFP | 0×1E06C069              |

| CY8C3445LTI-081 | 50              | 32         | 4         | 1           | >                 | 12-bit Del-Sig | 2   | 4          | 2                                      | 2      | -   | ~        | 20                   | 4                | ~      | -        | 48        | 38   | 8    | 2     | 68-pin QFN   | 0×1E051069              |

| CY8C3445PVI-090 | 50              | 32         | 4         | 1           | >                 | 12-bit Del-Sig | 2   | 4          | 2                                      | 2      | -   | ~        | 20                   | 4                | ~      | -        | 31        | 25   | 4    | 2     | 48-pin SSOP  | 0×1E05A069              |

| 64 KB Flash     |                 |            |           |             |                   |                |     |            |                                        |        |     |          |                      |                  |        |          |           |      |      |       |              |                         |

| CY8C3446LTI-073 | 50              | 64         | 8         | 2           | >                 | 12-bit Del-Sig | 2   | 4          | 2                                      | 2      | -   | ~        | 24                   | 4                | ~      | -        | 31        | 25   | 4    | 2     | 48-pin QFN   | 0×1E049069              |

| CY8C3446LTI-074 | 50              | 64         | 8         | 2           | >                 | 12-bit Del-Sig | 2   | 4          | 2                                      | 2      | -   | >        | 24                   | 4                | -      | -        | 46        | 38   | 8    | 0     | 68-pin QFN   | 0×1E04A069              |

| CY8C3446LTI-083 | 50              | 64         | 8         | 2           | >                 | 12-bit Del-Sig | 2   | 4          | 2                                      | 2      | -   | ~        | 24                   | 4                | -      | -        | 29        | 25   | 4    | 0     | 48-pin QFN   | 0x1E053069              |

| CY8C3446AXI-099 | 50              | 64         | 8         | 2           | >                 | 12-bit Del-Sig | 2   | 4          | 2                                      | 2      | -   | >        | 24                   | 4                | ~      | -        | 72        | 62   | 8    | 2     | 100-pin TQFP | 0×1E063069              |

| CY8C3446AXI-105 | 50              | 64         | 8         | 2           | ~                 | 12-bit Del-Sig | 2   | 4          | 2                                      | 2      | -   | 2        | 24                   | 4                | -      | 1        | 70        | 62   | 8    | 0     | 100-pin TQFP | 0x1E069069              |

| CY8C3446LTI-085 | 50              | 64         | 8         | 2           | ~                 | 12-bit Del-Sig | 2   | 4          | 2                                      | 2      | -   | ~        | 24                   | 4                | ~      | -        | 48        | 38   | 8    | 2     | 68-pin QFN   | 0×1E055069              |

| CY8C3446PVI-076 | 50              | 64         | 8         | 2           | ~                 | 12-bit Del-Sig | 2   | 4          | 2                                      | 2      | -   | ~        | 24                   | 4                | ~      | -        | 31        | 25   | 4    | 2     | 48-pin SSOP  | 0×1E04C069              |

| CY8C3446PVI-102 | 50              | 64         | 8         | 2           | ~                 | 12-bit Del-Sig | 2   | 4          | 2                                      | 2      | -   | ~        | 24                   | 4                | -      | ~        | 29        | 25   | 4    | 0     | 48-pin SSOP  | 0x1E066069              |

Notes

79. Analog blocks support a wide variety of functionality including TIA, PGA, and mixers. See the Example Peripherals on page 43 for more information on how analog blocks can be used.

80. UDBs support a wide variety of functionality including SPI, LIN, UART, timer, counter, PWM, PRS, and others. Individual functions may use a fraction of a UDB or multiple UDBs. Multiple functions can share a single UDB. See the Example Peripherals on page 43 for more information on how UDBs can be used.

81. The I/O Count includes all types of digital I/O: GPIO, SIO, and the two USB I/O. See the I/O System and Routing on page 36 for details on the functionality of each of these types of I/O.

82. The JTAG ID has three major fields. The most significant nibble (left digit) is the version, followed by a 2 byte part number and a 3 nibble manufacturer ID.

| Revision | ECN     | Submission<br>Date | Orig. of<br>Change | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------|---------|--------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| *P       | 3732521 | 09/03/2012         | MKEA               | Replaced I <sub>DDDR</sub> and I <sub>DDAR</sub> specs in Table 11-2, "DC Specifications," on page 71 that were dropped out in "N revision.<br>Updated Table 11-32, "Mixer DC Specifications," on page 102, V <sub>OS</sub> Max value from 10 to 15.<br>Updated Table 11-21, "12-bit Delta-sigma ADC DC Specifications," on page 91, I <sub>DD 12</sub> Max value from 1.4 to 1.95 mA<br>Replaced PSoC <sup>®</sup> 3 Programming AN62391 with TRM in footnote #59 and Section Table 9., "Programming, Debug Interfaces, Resources," on page 65<br>Removed Figure 11-8 (Efficiency vs Vout)<br>Removed 62-MHz sub-row in Table 11-2, "DC Specifications," on page 71<br>Updated Table 11-19, "Opamp DC Specifications," on page 71<br>Updated Table 11-19, "Opamp DC Specifications," on page 71<br>Updated conditions for Storage Temperature in Table 11-1, "Absolute Maximum<br>Ratings DC Specifications[18]," on page 70<br>Updated conditions and min values for NVL data retention time in Table 11-58,<br>"NVL AC Specifications," on page 109.<br>Updated Table 11-75, "ILO DC Specifications," on page 118.<br>Removed following pruned parts from "Ordering Information" section on<br>page 121.<br>CY8C3446AXI-105<br>CY8C3446EVI-091<br>CY8C3446FVI-091<br>CY8C3446PVI-102<br>Updated PSoC 3 boost circuit value throughout the document.<br>Updated PSoC 3 boost circuit value throughout the document.<br>Updated package diagram 51-85061 to *F revision. |

| *Q       | 3922905 | 03/06/2013         | MKEA               | Updated I <sub>DD_XX</sub> parameters under Table 11-21, "12-bit Delta-sigma ADC DC Specifications," on page 91.<br>Updated I <sup>2</sup> C section and updated GPIO and SIO DC specification tables.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |