Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Dataila                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Details                    |                                                                             |

| Product Status             | Active                                                                      |

| Core Processor             | 8051                                                                        |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 50MHz                                                                       |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                     |

| Peripherals                | CapSense, DMA, LCD, POR, PWM, WDT                                           |

| Number of I/O              | 38                                                                          |

| Program Memory Size        | 64KB (64K x 8)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 2K x 8                                                                      |

| RAM Size                   | 8K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                                |

| Data Converters            | A/D 16x12b; D/A 2x8b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 68-VFQFN Exposed Pad                                                        |

| Supplier Device Package    | 68-QFN (8x8)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c3446lti-085t |

Figure 2-8. Example PCB Layout for 100-pin TQFP Part for Optimal Analog Performance

## 3. Pin Descriptions

#### IDAC0, IDAC2

Low resistance output pin for high current DACs (IDAC).

## OpAmp0out, OpAmp2out

High current output of uncommitted opamp<sup>[11]</sup>.

#### Extref0, Extref1

External reference input to the analog system.

#### Opamp0-, Opamp2-

Inverting input to uncommitted opamp.

#### Opamp0+, Opamp2+

Noninverting input to uncommitted opamp.

## **GPIO**

General purpose I/O pin provides interfaces to the CPU, digital peripherals, analog peripherals, interrupts, LCD segment drive, and CapSense<sup>[11]</sup>.

#### 12C0: SCL, I2C1: SCL

I<sup>2</sup>C SCL line providing wake from sleep on an address match. Any I/O pin can be used for I<sup>2</sup>C SCL if wake from sleep is not required.

#### 12C0: SDA, I2C1: SDA

$I^2C$  SDA line providing wake from sleep on an address match. Any I/O pin can be used for  $I^2C$  SDA if wake from sleep is not required.

#### Ind

Inductor connection to boost pump.

## kHz XTAL: Xo, kHz XTAL: Xi

32.768-kHz crystal oscillator pin.

#### Note

11. GPIOs with opamp outputs are not recommended for use with CapSense.

#### MHz XTAL: Xo, MHz XTAL: Xi

4- to 25-MHz crystal oscillator pin.

#### nTRST

Optional JTAG test reset programming and debug port connection to reset the JTAG connection.

#### SIO

Special I/O provides interfaces to the CPU, digital peripherals and interrupts with a programmable high threshold voltage, analog comparator, high sink current, and high impedance state when the device is unpowered.

#### **SWDCK**

Serial wire debug clock programming and debug port connection.

#### **SWDIO**

Serial wire debug input and output programming and debug port connection.

#### **SWV**

Single wire viewer debug output.

#### **TCK**

JTAG test clock programming and debug port connection.

#### TD

JTAG test data In programming and debug port connection.

#### TDO

JTAG test data out programming and debug port connection.

## TMS

JTAG test mode select programming and debug port connection.

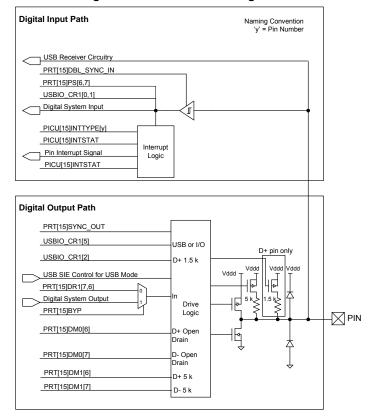

## USBIO, D+

Provides D+ connection directly to a USB 2.0 bus. May be used as a digital I/O pin. Pins are Do Not Use (DNU) on devices without USB.

#### USBIO, D-

Provides D— connection directly to a USB 2.0 bus. May be used as a digital I/O pin. Pins are No Connect (NC) on devices without USB.

#### **VBOOST**

Power sense connection to boost pump.

#### **VBAT**

Battery supply to boost pump.

#### VCCA

Output of the analog core regulator or the input to the analog core. Requires a 1uF capacitor to VSSA. The regulator output is not designed to drive external circuits. Note that if you use the device with an external core regulator (externally regulated mode), the voltage applied to this pin must not exceed the allowable range of 1.71 V to 1.89 V. When using the internal core regulator, (internally regulated mode, the default), do not tie any power to this pin. For details see Power System on page 30.

#### VCCD

Output of the digital core regulator or the input to the digital core. The two VCCD pins must be shorted together, with the trace between them as short as possible, and a 1uF capacitor to VSSD. The regulator output is not designed to drive external circuits. Note that if you use the device with an external core regulator (externally regulated mode), the voltage applied to this pin must not exceed the allowable range of 1.71 V to 1.89 V. When using the internal core regulator (internally regulated mode, the default), do not tie any power to this pin. For details see Power System on page 30.

#### **VDDA**

Supply for all analog peripherals and analog core regulator. VDDA must be the highest voltage present on the device. All other supply pins must be less than or equal to VDDA.

#### **VDDD**

Supply for all digital peripherals and digital core regulator. VDDD must be less than or equal to VDDA.

#### VSSA

Ground for all analog peripherals.

#### **VSSB**

Ground connection for boost pump.

#### VSSD

Ground for all digital logic and I/O pins.

## VDDIO0, VDDIO1, VDDIO2, VDDIO3

Supply for I/O pins. See pinouts for specific I/O pin to VDDIO mapping. Each VDDIO must be tied to a valid operating voltage (1.71 V to 5.5 V), and must be less than or equal to VDDA.

## XRES (and configurable XRES)

External reset pin. Active low with internal pull-up. Pin P1[2] may be configured to be a XRES pin; see "Nonvolatile Latches (NVLs)" on page 23.

## 4. CPU

#### 4.1 8051 CPU

The CY8C34 devices use a single cycle 8051 CPU, which is fully compatible with the original MCS-51 instruction set. The CY8C34 family uses a pipelined RISC architecture, which executes most instructions in 1 to 2 cycles to provide peak performance of up to 24 MIPS with an average of 2 cycles per instruction. The single cycle 8051 CPU runs ten times faster than a standard 8051 processor.

The 8051 CPU subsystem includes these features:

- Single cycle 8051 CPU

- Up to 64 KB of flash memory, up to 2 KB of EEPROM, and up to 8 KB of SRAM

- 512-byte instruction cache between CPU and flash

- Programmable nested vector interrupt controller

- Direct memory access (DMA) controller

- Peripheral HUB (PHUB)

- External memory interface (EMIF)

#### 4.2 Addressing Modes

The following addressing modes are supported by the 8051:

- Direct Addressing: The operand is specified by a direct 8-bit address field. Only the internal RAM and the SFRs can be accessed using this mode.

- Indirect Addressing: The instruction specifies the register which contains the address of the operand. The registers R0 or R1 are used to specify the 8-bit address, while the data pointer (DPTR) register is used to specify the 16-bit address.

- Register Addressing: Certain instructions access one of the registers (R0 to R7) in the specified register bank. These instructions are more efficient because there is no need for an address field.

- Register Specific Instructions: Some instructions are specific to certain registers. For example, some instructions always act on the accumulator. In this case, there is no need to specify the operand.

- Immediate Constants: Some instructions carry the value of the constants directly instead of an address.

- Indexed Addressing: This type of addressing can be used only for a read of the program memory. This mode uses the Data Pointer as the base and the accumulator value as an offset to read a program memory.

- Bit Addressing: In this mode, the operand is one of 256 bits.

Table 4-4. Boolean Instructions

| Mnemonic     | Description                             | Bytes | Cycles |

|--------------|-----------------------------------------|-------|--------|

| CLR C        | Clear carry                             | 1     | 1      |

| CLR bit      | Clear direct bit                        | 2     | 3      |

| SETB C       | Set carry                               | 1     | 1      |

| SETB bit     | Set direct bit                          | 2     | 3      |

| CPL C        | Complement carry                        | 1     | 1      |

| CPL bit      | Complement direct bit                   | 2     | 3      |

| ANL C, bit   | AND direct bit to carry                 | 2     | 2      |

| ANL C, /bit  | AND complement of direct bit to carry   | 2     | 2      |

| ORL C, bit   | OR direct bit to carry                  | 2     | 2      |

| ORL C, /bit  | OR complement of direct bit to carry    | 2     | 2      |

| MOV C, bit   | Move direct bit to carry                | 2     | 2      |

| MOV bit, C   | Move carry to direct bit                | 2     | 3      |

| JC rel       | Jump if carry is set                    | 2     | 3      |

| JNC rel      | Jump if no carry is set                 | 2     | 3      |

| JB bit, rel  | Jump if direct bit is set               | 3     | 5      |

| JNB bit, rel | Jump if direct bit is not set           | 3     | 5      |

| JBC bit, rel | Jump if direct bit is set and clear bit | 3     | 5      |

## 4.3.1.5 Program Branching Instructions

The 8051 supports a set of conditional and unconditional jump instructions that help to modify the program execution flow. Table 4-5 shows the list of jump instructions.

**Table 4-5. Jump Instructions**

| Mnemonic             | Description                                                  | Bytes | Cycles |

|----------------------|--------------------------------------------------------------|-------|--------|

| ACALL addr11         | Absolute subroutine call                                     | 2     | 4      |

| LCALL addr16         | Long subroutine call                                         | 3     | 4      |

| RET                  | Return from subroutine                                       | 1     | 4      |

| RETI                 | Return from interrupt                                        | 1     | 4      |

| AJMP addr11          | Absolute jump                                                | 2     | 3      |

| LJMP addr16          | Long jump                                                    | 3     | 4      |

| SJMP rel             | Short jump (relative address)                                | 2     | 3      |

| JMP @A + DPTR        | Jump indirect relative to DPTR                               | 1     | 5      |

| JZ rel               | Jump if accumulator is zero                                  | 2     | 4      |

| JNZ rel              | Jump if accumulator is nonzero                               | 2     | 4      |

| CJNE A,Direct, rel   | Compare direct byte to accumulator and jump if not equal     | 3     | 5      |

| CJNE A, #data, rel   | Compare immediate data to accumulator and jump if not equal  | 3     | 4      |

| CJNE Rn, #data, rel  | Compare immediate data to register and jump if not equal     | 3     | 4      |

| CJNE @Ri, #data, rel | Compare immediate data to indirect RAM and jump if not equal | 3     | 5      |

| DJNZ Rn,rel          | Decrement register and jump if not zero                      | 2     | 4      |

| DJNZ Direct, rel     | Decrement direct byte and jump if not zero                   | 3     | 5      |

| NOP                  | No operation                                                 | 1     | 1      |

Document Number: 001-53304 Rev. \*Y Page 16 of 137

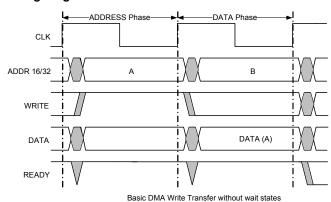

#### 4.4.4.1 Simple DMA

In a simple DMA case, a single TD transfers data between a source and sink (peripherals or memory location). The basic timing diagrams of DMA read and write cycles are shown in Figure 4-1. For more description on other transfer modes, refer to the Technical Reference Manual.

ADDRESS Phase DATA Phase

CLK

ADDR 16/32

A

B

DATA

DATA

DATA

A

DATA

READY

Figure 4-1. DMA Timing Diagram

#### 4.4.4.2 Auto Repeat DMA

Auto repeat DMA is typically used when a static pattern is repetitively read from system memory and written to a peripheral. This is done with a single TD that chains to itself.

Basic DMA Read Transfer without wait states

## 4.4.4.3 Ping Pong DMA

A ping pong DMA case uses double buffering to allow one buffer to be filled by one client while another client is consuming the data previously received in the other buffer. In its simplest form, this is done by chaining two TDs together so that each TD calls the opposite TD when complete.

#### 4.4.4.4 Circular DMA

Circular DMA is similar to ping pong DMA except it contains more than two buffers. In this case there are multiple TDs; after the last TD is complete it chains back to the first TD.

#### 4.4.4.5 Scatter Gather DMA

In the case of scatter gather DMA, there are multiple noncontiguous sources or destinations that are required to effectively carry out an overall DMA transaction. For example, a packet may need to be transmitted off of the device and the packet elements, including the header, payload, and trailer, exist in various noncontiguous locations in memory. Scatter gather DMA allows the segments to be concatenated together by using multiple TDs in a chain. The chain gathers the data from the multiple locations. A similar concept applies for the reception of data onto the device. Certain parts of the received data may need to be scattered to various locations in memory for software processing convenience. Each TD in the chain specifies the location for each discrete element in the chain.

#### 4.4.4.6 Packet Queuing DMA

Packet queuing DMA is similar to scatter gather DMA but specifically refers to packet protocols. With these protocols, there may be separate configuration, data, and status phases associated with sending or receiving a packet.

For instance, to transmit a packet, a memory mapped configuration register can be written inside a peripheral, specifying the overall length of the ensuing data phase. The CPU

can set up this configuration information anywhere in system memory and copy it with a simple TD to the peripheral. After the configuration phase, a data phase TD (or a series of data phase TDs) can begin (potentially using scatter gather). When the data phase TD(s) finish, a status phase TD can be invoked that reads some memory mapped status information from the peripheral and copies it to a location in system memory specified by the CPU for later inspection. Multiple sets of configuration, data, and status phase "subchains" can be strung together to create larger chains that transmit multiple packets in this way. A similar concept exists in the opposite direction to receive the packets.

#### 4.4.4.7 Nested DMA

One TD may modify another TD, as the TD configuration space is memory mapped similar to any other peripheral. For example, a first TD loads a second TD's configuration and then calls the second TD. The second TD moves data as required by the application. When complete, the second TD calls the first TD, which again updates the second TD's configuration. This process repeats as often as necessary.

#### 4.5 Interrupt Controller

The interrupt controller provides a mechanism for hardware resources to change program execution to a new address, independent of the current task being executed by the main code. The interrupt controller provides enhanced features not found on original 8051 interrupt controllers:

- Thirty two interrupt vectors

- Jumps directly to ISR anywhere in code space with dynamic vector addresses

- Multiple sources for each vector

- Flexible interrupt to vector matching

- Each interrupt vector is independently enabled or disabled

- Each interrupt can be dynamically assigned one of eight priorities

- Eight level nestable interrupts

#### 6.2.1 Power Modes

PSoC 3 devices have four different power modes, as shown in Table 6-2 and Table 6-3. The power modes allow a design to easily provide required functionality and processing power while simultaneously minimizing power consumption and maximizing battery life in low-power and portable devices.

PSoC 3 power modes, in order of decreasing power consumption are:

- Active

- Alternate Active

- Sleep

- Hibernate

Table 6-2. Power Modes

Active is the main processing mode. Its functionality is configurable. Each power controllable subsystem is enabled or disabled by using separate power configuration template registers. In alternate active mode, fewer subsystems are enabled, reducing power. In sleep mode most resources are disabled regardless of the template settings. Sleep mode is optimized to provide timed sleep intervals and RTC functionality. The lowest power mode is hibernate, which retains register and SRAM state, but no clocks, and allows wakeup only from I/O pins. Figure 6-5 on page 32 illustrates the allowable transitions between power modes. Sleep and hibernate modes should not be entered until all VDDIO supplies are at valid voltage levels.

| <b>Power Modes</b>  | Description                                                                                                                                                                                                   | <b>Entry Condition</b>                     | Wakeup Source                                           | Active Clocks         | Regulator                                                                                                             |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|---------------------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------|

| Active              | Primary mode of operation, all peripherals available (programmable)                                                                                                                                           | Wakeup, reset,<br>manual register<br>entry | Any interrupt                                           | Any<br>(programmable) | All regulators available. Digital and analog regulators can be disabled if external regulation used.                  |

| Alternate<br>Active | Similar to Active mode, and is<br>typically configured to have fewer<br>peripherals active to reduce<br>power. One possible<br>configuration is to use the UDBs<br>for processing, with the CPU<br>turned off | Manual register entry                      | Any interrupt                                           | Any<br>(programmable) | All regulators available. Digital and analog regulators can be disabled if external regulation used.                  |

| Sleep               | All subsystems automatically disabled                                                                                                                                                                         | Manual register entry                      | Comparator,<br>PICU, I <sup>2</sup> C, RTC,<br>CTW, LVD | ILO/kHzECO            | Both digital and analog regulators buzzed. Digital and analog regulators can be disabled if external regulation used. |

| Hibernate           | All subsystems automatically disabled Lowest power consuming mode with all peripherals and internal regulators disabled, except hibernate regulator is enabled Configuration and memory contents retained     | Manual register<br>entry                   | PICU                                                    |                       | Only hibernate regulator active.                                                                                      |

**Table 6-3. Power Modes Wakeup Time and Power Consumption**

| Sleep<br>Modes      | Wakeup<br>Time | Current<br>(typ)       | Code<br>Execution | Digital<br>Resources | Analog<br>Resources | Clock Sources<br>Available | Wakeup Sources                                          | Reset<br>Sources  |

|---------------------|----------------|------------------------|-------------------|----------------------|---------------------|----------------------------|---------------------------------------------------------|-------------------|

| Active              | _              | 1.2 mA <sup>[12]</sup> | Yes               | All                  | All                 | All                        | _                                                       | All               |

| Alternate<br>Active | -              | _                      | User<br>defined   | All                  | All                 | All                        | -                                                       | All               |

| Sleep               | <15 µs         | 1 μΑ                   | No                | I <sup>2</sup> C     | Comparator          | ILO/kHzECO                 | Comparator,<br>PICU, I <sup>2</sup> C, RTC,<br>CTW, LVD | XRES, LVD,<br>WDR |

| Hibernate           | <100 µs        | 200 nA                 | No                | None                 | None                | None                       | PICU                                                    | XRES              |

#### Note

Document Number: 001-53304 Rev. \*Y

<sup>12.</sup> Bus clock off. Execute from cache at 6 MHz. See Table 11-2 on page 71.

**Digital Input Path** Naming Convention PRT[x]SIO\_HYST\_EN 'x' = Port Number 'y' = Pin Number PRT[x]SIO\_DIFF Buffer Thresholds Reference Level PRT[x]DBL\_SYNC\_IN PRT[x]PS Digital System Input PICU[x]INTTYPE[y] Input Buffer Disable PICU[x]INTSTAT Interrupt Pin Interrupt Signal Logic PICU[x]INTSTAT **Digital Output Path** Reference Level PRT[x]SIO\_CFG PRT[x]SLW Vhigh PRT[x]SYNC\_OUT PRT[x]DR In Digital System Output PRT[x]BYP PRT[x]DM2 Drive Slew - PIN PRT[x]DM1 Logic PRT[x]DM0 **Bidirectional Control** PRT[x]BIE OE

Figure 6-10. SIO Input/Output Block Diagram

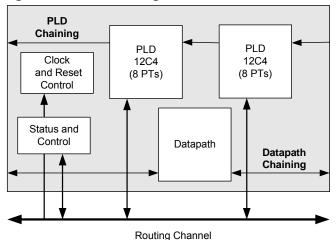

## 7.2 Universal Digital Block

The Universal Digital Block (UDB) represents an evolutionary step to the next generation of PSoC embedded digital peripheral functionality. The architecture in first generation PSoC digital blocks provides coarse programmability in which a few fixed functions with a small number of options are available. The new UDB architecture is the optimal balance between configuration granularity and efficient implementation. A cornerstone of this approach is to provide the ability to customize the devices digital operation to match application requirements.

To achieve this, UDBs consist of a combination of uncommitted logic (PLD), structured logic (Datapath), and a flexible routing scheme to provide interconnect between these elements, I/O connections, and other peripherals. UDB functionality ranges from simple self contained functions that are implemented in one UDB, or even a portion of a UDB (unused resources are available for other functions), to more complex functions that require multiple UDBs. Examples of basic functions are timers, counters, CRC generators, PWMs, dead band generators, and communications functions, such as UARTs, SPI, and I<sup>2</sup>C. Also, the PLD blocks and connectivity provide full featured general purpose programmable logic within the limits of the available resources.

Figure 7-2. UDB Block Diagram

The main component blocks of the UDB are:

- PLD blocks There are two small PLDs per UDB. These blocks take inputs from the routing array and form registered or combinational sum-of-products logic. PLDs are used to implement state machines, state bits, and combinational logic equations. PLD configuration is automatically generated from graphical primitives.

- Datapath Module This 8-bit wide datapath contains structured logic to implement a dynamically configurable ALU, a variety of compare configurations and condition generation. This block also contains input/output FIFOs, which are the primary parallel data interface between the CPU/DMA system and the UDB.

- Status and Control Module The primary role of this block is to provide a way for CPU firmware to interact and synchronize with UDB operation.

- Clock and Reset Module This block provides the UDB clocks and reset selection and control.

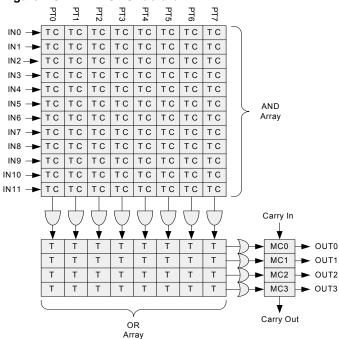

#### 7.2.1 PLD Module

The primary purpose of the PLD blocks is to implement logic expressions, state machines, sequencers, lookup tables, and decoders. In the simplest use model, consider the PLD blocks as a standalone resource onto which general purpose RTL is synthesized and mapped. The more common and efficient use model is to create digital functions from a combination of PLD and datapath blocks, where the PLD implements only the random logic and state portion of the function while the datapath (ALU) implements the more structured elements.

Figure 7-3. PLD 12C4 Structure

One 12C4 PLD block is shown in Figure 7-3. This PLD has 12 inputs, which feed across eight product terms. Each product term (AND function) can be from 1 to 12 inputs wide, and in a given product term, the true (T) or complement (C) of each input can be selected. The product terms are summed (OR function) to create the PLD outputs. A sum can be from 1 to 8 product terms wide. The 'C' in 12C4 indicates that the width of the OR gate (in this case 8) is constant across all outputs (rather than variable as in a 22V10 device). This PLA like structure gives maximum flexibility and insures that all inputs and outputs are permutable for ease of allocation by the software tools. There are two 12C4 PLDs in each UDB.

Document Number: 001-53304 Rev. \*Y Page 45 of 137

## 7.4.1 I/O Port Routing

There are a total of 20 DSI routes to a typical 8-bit I/O port, 16 for data and four for drive strength control.

When an I/O pin is connected to the routing, there are two primary connections available, an input and an output. In conjunction with drive strength control, this can implement a bidirectional I/O pin. A data output signal has the option to be single synchronized (pipelined) and a data input signal has the option to be double synchronized. The synchronization clock is the master clock (see Figure 6-1). Normally all inputs from pins are synchronized as this is required if the CPU interacts with the signal or any signal derived from it. Asynchronous inputs have rare uses. An example of this is a feed through of combinational PLD logic from input pins to output pins.

Figure 7-11. I/O Pin Synchronization Routing

Figure 7-12. I/O Pin Output Connectivity

8 IO Data Output Connections from the UDB Array Digital System Interface

DO DO DO DO DO PIN1 PIN2 PIN3 PIN4 PIN5 PIN6 PIN7

Port i

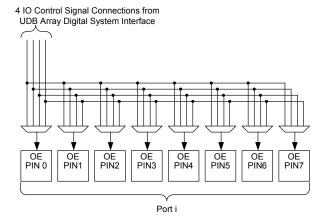

There are four more DSI connections to a given I/O port to implement dynamic output enable control of pins. This connectivity gives a range of options, from fully ganged 8-bits controlled by one signal, to up to four individually controlled pins. The output enable signal is useful for creating tri-state bidirectional pins and buses.

Figure 7-13. I/O Pin Output Enable Connectivity

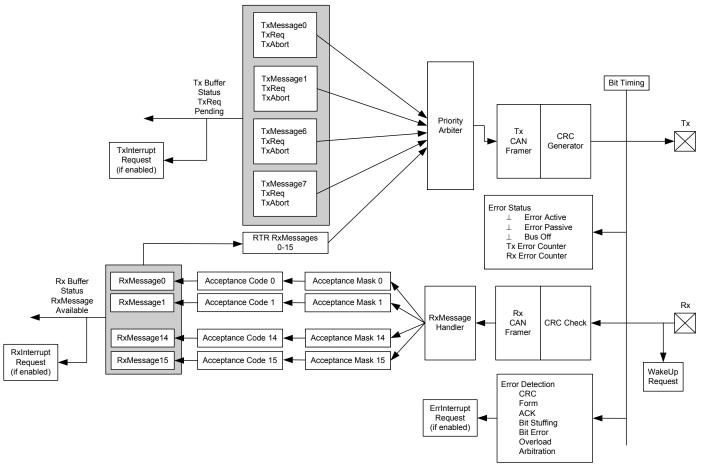

#### 7.5 CAN

The CAN peripheral is a fully functional Controller Area Network (CAN) supporting communication baud rates up to 1 Mbps. The CAN controller implements the CAN2.0A and CAN2.0B specifications as defined in the Bosch specification and conforms to the ISO-11898-1 standard. The CAN protocol was originally designed for automotive applications with a focus on a high level of fault detection. This ensures high communication reliability at a low cost. Because of its success in automotive applications, CAN is used as a standard communication protocol for motion oriented machine control networks (CANOpen) and factory automation applications (DeviceNet). The CAN controller features allow the efficient implementation of higher level protocols without affecting the performance of the microcontroller CPU. Full configuration support is provided in PSoC Creator.

Document Number: 001-53304 Rev. \*Y

Figure 7-15. CAN Controller Block Diagram

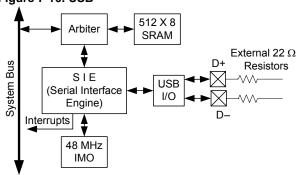

## 7.6 USB

PSoC includes a dedicated Full-Speed (12 Mbps) USB 2.0 transceiver supporting all four USB transfer types: control, interrupt, bulk, and isochronous. PSoC Creator provides full configuration support. USB interfaces to hosts through two dedicated USBIO pins, which are detailed in the "I/O System and Routing" section on page 36.

USB includes the following features:

- Eight unidirectional data endpoints

- One bidirectional control endpoint 0 (EP0)

- Shared 512-byte buffer for the eight data endpoints

- Dedicated 8-byte buffer for EP0

- Three memory modes

- Manual Memory Management with No DMA Access

- □ Manual Memory Management with Manual DMA Access

- □ Automatic Memory Management with Automatic DMA Access

- Internal 3.3-V regulator for transceiver

- Internal 48 MHz main oscillator mode that auto locks to USB bus clock, requiring no external crystal for USB (USB equipped parts only)

- Interrupts on bus and each endpoint event, with device wakeup

- USB Reset, Suspend, and Resume operations

- Bus powered and self powered modes

Figure 7-16. USB

#### 8.3.2 LUT

The CY8C34 family of devices contains four LUTs. The LUT is a two input, one output lookup table that is driven by any one or two of the comparators in the chip. The output of any LUT is routed to the digital system interface of the UDB array. From the digital system interface of the UDB array, these signals can be connected to UDBs, DMA controller, I/O, or the interrupt controller.

The LUT control word written to a register sets the logic function on the output. The available LUT functions and the associated control word is shown in Table 8-2.

Table 8-2. LUT Function vs. Program Word and Inputs

| Control Word | Output (A and B are LUT inputs) |

|--------------|---------------------------------|

| 0000b        | FALSE ('0')                     |

| 0001b        | A AND B                         |

| 0010b        | A AND (NOT B)                   |

| 0011b        | A                               |

| 0100b        | (NOT A) AND B                   |

| 0101b        | В                               |

| 0110b        | A XOR B                         |

| 0111b        | A OR B                          |

| 1000b        | A NOR B                         |

| 1001b        | A XNOR B                        |

| 1010b        | NOT <b>B</b>                    |

| 1011b        | A OR (NOT B)                    |

| 1100b        | NOT A                           |

| 1101b        | (NOT A) OR B                    |

| 1110b        | A NAND B                        |

| 1111b        | TRUE ('1')                      |

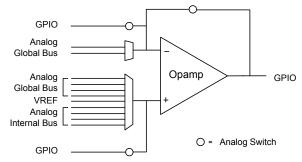

## 8.4 Opamps

The CY8C34 family of devices contains two general purpose opamps in a device.

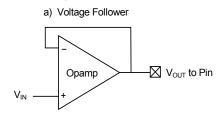

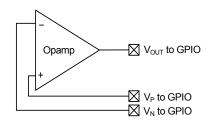

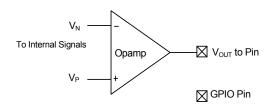

Figure 8-6. Opamp

The opamp is uncommitted and can be configured as a gain stage or voltage follower, or output buffer on external or internal signals.

See Figure 8-7. In any configuration, the input and output signals can all be connected to the internal global signals and monitored with an ADC, or comparator. The configurations are implemented with switches between the signals and GPIO pins.

Figure 8-7. Opamp Configurations

b) External Uncommitted Opamp

c) Internal Uncommitted Opamp

The opamp has three speed modes, slow, medium, and fast. The slow mode consumes the least amount of quiescent power and the fast mode consumes the most power. The inputs are able to swing rail-to-rail. The output swing is capable of rail-to-rail operation at low current output, within 50 mV of the rails. When driving high current loads (about 25 mA) the output voltage may only get within 500 mV of the rails.

## 8.5 Programmable SC/CT Blocks

The CY8C34 family of devices contains two switched capacitor/continuous time (SC/CT) blocks in a device. Each switched capacitor/continuous time block is built around a single rail-to-rail high bandwidth opamp.

Switched capacitor is a circuit design technique that uses capacitors plus switches instead of resistors to create analog functions. These circuits work by moving charge between capacitors by opening and closing different switches. Nonoverlapping in phase clock signals control the switches, so that not all switches are ON simultaneously.

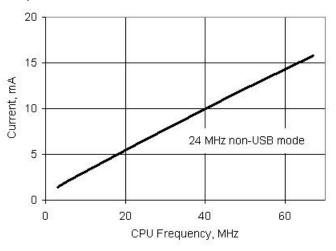

Figure 11-1. Active Mode Current vs  $F_{CPU}$ ,  $V_{DD}$  = 3.3 V, Temperature = 25 °C

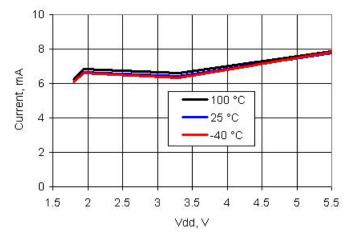

Figure 11-3. Active Mode Current vs V<sub>DD</sub> and Temperature, F<sub>CPU</sub> = 24 MHz

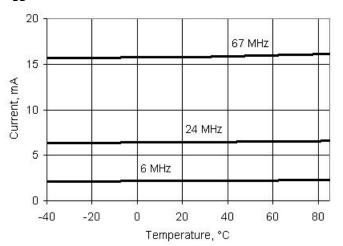

Figure 11-2. Active Mode Current vs Temperature and F<sub>CPU</sub>,  $V_{DD} = 3.3 \text{ V}$

- 28. If  $V_{CCD}$  and  $V_{CCA}$  are externally regulated, the voltage difference between  $V_{CCD}$  and  $V_{CCA}$  must be less than 50 mV. 29. Sleep timer generates periodic interrupts to wake up the CPU. This specification applies only to those times that the CPU is off.

- 30. Externally regulated mode.

- 31. Based on device characterization (not production tested).

- 32. Based on device characterization (not production tested). USBIO pins tied to ground (VSSD).

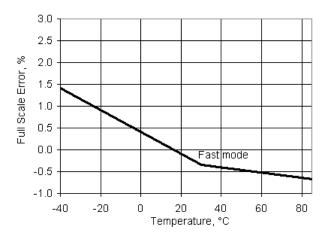

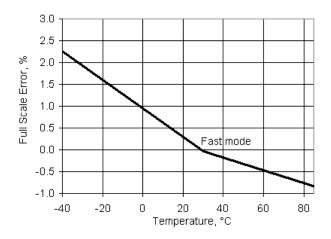

Figure 11-40. IDAC Full Scale Error vs Temperature, Range = 255  $\mu$ A, Source Mode

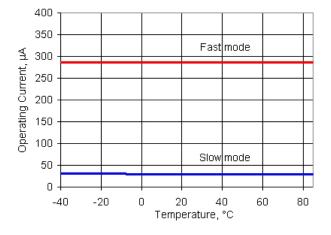

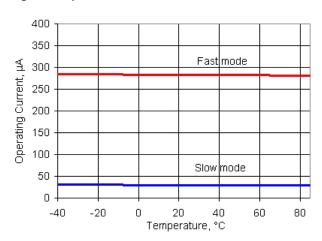

Figure 11-42. IDAC Operating Current vs Temperature, Range =  $255 \mu A$ , Code = 0, Source Mode

Figure 11-41. IDAC Full Scale Error vs Temperature, Range = 255  $\mu$ A, Sink Mode

Figure 11-43. IDAC Operating Current vs Temperature, Range = 255 µA, Code = 0, Sink Mode

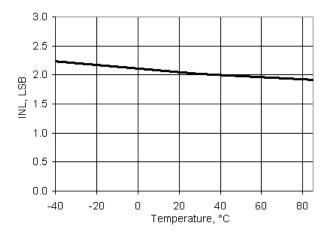

Figure 11-50. VDAC INL vs Temperature, 1 V Mode

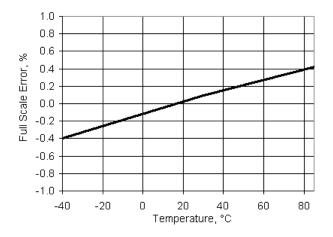

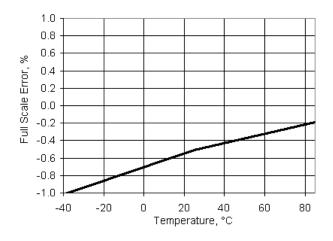

Figure 11-52. VDAC Full Scale Error vs Temperature, 1 V Mode

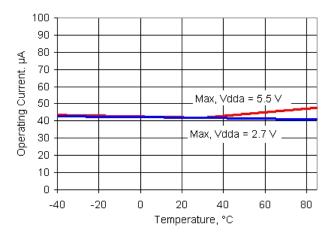

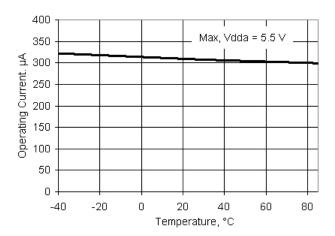

Figure 11-54. VDAC Operating Current vs Temperature, 1V Mode, Low speed mode

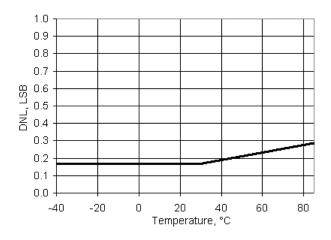

Figure 11-51. VDAC DNL vs Temperature, 1 V Mode

Figure 11-53. VDAC Full Scale Error vs Temperature, 4 V Mode

Figure 11-55. VDAC Operating Current vs Temperature, 1 V Mode, High speed mode

## 11.7.2 EEPROM

## Table 11-55. EEPROM DC Specifications

| Parameter | Description               | Conditions | Min  | Тур | Max | Units |

|-----------|---------------------------|------------|------|-----|-----|-------|

|           | Erase and program voltage |            | 1.71 | 1   | 5.5 | V     |

## Table 11-56. EEPROM AC Specifications

| Parameter          | Description                                                                 | Conditions                                                               | Min | Тур | Max | Units |

|--------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------------------|-----|-----|-----|-------|

| T <sub>WRITE</sub> | Single row erase/write cycle time                                           |                                                                          | _   | 10  | 20  | ms    |

|                    | EEPROM data retention time, retention period measured from last erase cycle | Average ambient temp, T <sub>A</sub> ≤ 25 °C, 1M erase/program cycles    | 20  | _   | _   | years |

|                    |                                                                             | Average ambient temp, T <sub>A</sub> ≤ 55 °C, 100 K erase/program cycles | 20  | _   | _   |       |

|                    |                                                                             | Average ambient temp. $T_A \le 85$ °C, 10 K erase/program cycles         | 10  | _   | _   |       |

## 11.7.3 Nonvolatile Latches (NVL))

## Table 11-57. NVL DC Specifications

| Parameter | Description               | Conditions           | Min  | Тур | Max | Units |

|-----------|---------------------------|----------------------|------|-----|-----|-------|

|           | Erase and program voltage | V <sub>DDD</sub> pin | 1.71 | 1   | 5.5 | V     |

## Table 11-58. NVL AC Specifications

| Parameter | Description             | Conditions                                   | Min | Тур | Max | Units                       |

|-----------|-------------------------|----------------------------------------------|-----|-----|-----|-----------------------------|

|           |                         | Programmed at 25 °C                          | 1K  | -   | -   | program/<br>erase<br>cycles |

|           |                         | Programmed at 0 °C to 70 °C                  | 100 | -   | _   | program/<br>erase<br>cycles |

|           | NVL data retention time | Average ambient temp. T <sub>A</sub> ≤ 55 °C | 20  | _   | _   | years                       |

|           |                         | Average ambient temp. T <sub>A</sub> ≤ 85 °C | 10  | _   | _   | years                       |

## 11.7.4 SRAM

## Table 11-59. SRAM DC Specifications

| Parameter  | Description            | Conditions | Min | Тур | Max | Units |

|------------|------------------------|------------|-----|-----|-----|-------|

| $V_{SRAM}$ | SRAM retention voltage |            | 1.2 | _   | -   | V     |

## Table 11-60. SRAM AC Specifications

| Parameter         | Description              | Conditions | Min | Тур | Max   | Units |

|-------------------|--------------------------|------------|-----|-----|-------|-------|

| F <sub>SRAM</sub> | SRAM operating frequency |            | DC  | 1   | 50.01 | MHz   |

Document Number: 001-53304 Rev. \*Y Page 109 of 137

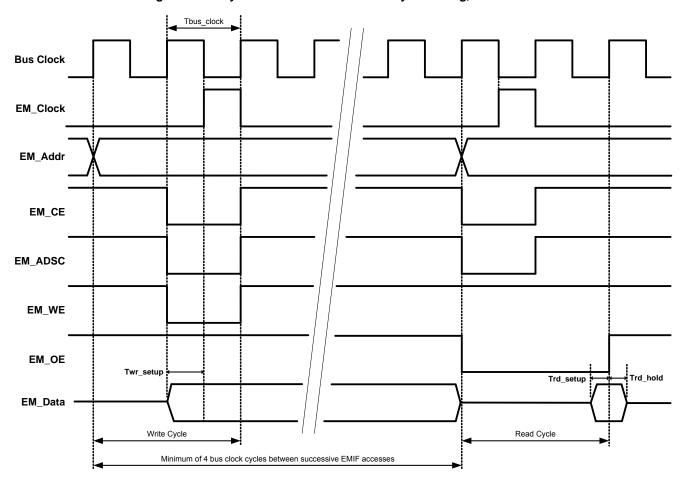

Figure 11-65. Synchronous Write and Read Cycle Timing, No Wait States

Table 11-62. Synchronous Write and Read Timing Specifications<sup>[63]</sup>

| Parameter  | Description                                                 | Conditions | Min             | Тур | Max | Units |

|------------|-------------------------------------------------------------|------------|-----------------|-----|-----|-------|

| Fbus_clock | Bus clock frequency <sup>[64]</sup>                         |            | _               | _   | 33  | MHz   |

| Tbus_clock | Bus clock period <sup>[65]</sup>                            |            | 30.3            | _   | _   | ns    |

| Twr_Setup  | Time from EM_data valid to rising edge of EM_Clock          |            | Tbus_clock - 10 | -   | _   | ns    |

| Trd_setup  | Time that EM_data must be valid before rising edge of EM_OE |            | 5               | -   | _   | ns    |

| Trd_hold   | Time that EM_data must be valid after rising edge of EM_OE  |            | 5               | _   | -   | ns    |

#### Notes

<sup>63.</sup> Based on device characterization (Not production tested).

64. EMIF signal timings are limited by GPIO frequency limitations. See "GPIO" section on page 79.

65. EMIF output signals are generally synchronized to bus clock, so EMIF signal timings are dependent on bus clock frequency.

## 13. Packaging

**Table 13-1. Package Characteristics**

| Parameter      | Description                            | Conditions | Min | Тур   | Max | Units   |

|----------------|----------------------------------------|------------|-----|-------|-----|---------|

| T <sub>A</sub> | Operating ambient temperature          |            | -40 | 25.00 | 85  | °C      |

| TJ             | Operating junction temperature         |            | -40 | _     | 100 | °C      |

| $T_{JA}$       | Package θ <sub>JA</sub> (48-pin SSOP)  |            | -   | 49    | _   | °C/Watt |

| $T_{JA}$       | Package θ <sub>JA</sub> (48-pin QFN)   |            | -   | 14    | _   | °C/Watt |

| $T_JA$         | Package θ <sub>JA</sub> (68-pin QFN)   |            | -   | 15    | _   | °C/Watt |

| $T_{JA}$       | Package θ <sub>JA</sub> (100-pin TQFP) |            | -   | 34    | _   | °C/Watt |

| $T_{JC}$       | Package θ <sub>JC</sub> (48-pin SSOP)  |            | -   | 24    | -   | °C/Watt |

| $T_{JC}$       | Package θ <sub>JC</sub> (48-pin QFN)   |            | -   | 15    | _   | °C/Watt |

| $T_{JC}$       | Package θ <sub>JC</sub> (68-pin QFN)   |            | -   | 13    | _   | °C/Watt |

| $T_JC$         | Package θ <sub>JC</sub> (100-pin TQFP) |            | -   | 10    | _   | °C/Watt |

Table 13-2. Solder Reflow Peak Temperature

| Package      | Maximum Peak<br>Temperature | Maximum Time at Peak<br>Temperature |

|--------------|-----------------------------|-------------------------------------|

| 48-pin SSOP  | 260 °C                      | 30 seconds                          |

| 48-pin QFN   | 260 °C                      | 30 seconds                          |

| 68-pin QFN   | 260 °C                      | 30 seconds                          |

| 100-pin TQFP | 260 °C                      | 30 seconds                          |

Table 13-3. Package Moisture Sensitivity Level (MSL), IPC/JEDEC J-STD-2

| Package      | MSL   |

|--------------|-------|

| 48-pin SSOP  | MSL 3 |

| 48-pin QFN   | MSL 3 |

| 68-pin QFN   | MSL 3 |

| 100-pin TQFP | MSL 3 |

Document Number: 001-53304 Rev. \*Y Page 123 of 137

## 14. Acronyms

Table 14-1. Acronyms Used in this Document

|                  | cronyms Used in this Document                                                                   |  |  |

|------------------|-------------------------------------------------------------------------------------------------|--|--|

| Acronym          | Description                                                                                     |  |  |

| abus             | analog local bus                                                                                |  |  |

| ADC              | analog-to-digital converter                                                                     |  |  |

| AG               | analog global                                                                                   |  |  |

| АНВ              | AMBA (advanced microcontroller bus architecture) high-performance bus, an ARM data transfer bus |  |  |

| ALU              | arithmetic logic unit                                                                           |  |  |

| AMUXBUS          | analog multiplexer bus                                                                          |  |  |

| API              | application programming interface                                                               |  |  |

| APSR             | application program status register                                                             |  |  |

| ARM <sup>®</sup> | advanced RISC machine, a CPU architecture                                                       |  |  |

| ATM              | automatic thump mode                                                                            |  |  |

| BW               | bandwidth                                                                                       |  |  |

| CAN              | Controller Area Network, a communications protocol                                              |  |  |

| CMRR             | common-mode rejection ratio                                                                     |  |  |

| CPU              | central processing unit                                                                         |  |  |

| CRC              | cyclic redundancy check, an error-checking protocol                                             |  |  |

| DAC              | digital-to-analog converter, see also IDAC, VDAC                                                |  |  |

| DFB              | digital filter block                                                                            |  |  |

| DIO              | digital input/output, GPIO with only digital capabilities, no analog. See GPIO.                 |  |  |

| DMA              | direct memory access, see also TD                                                               |  |  |

| DNL              | differential nonlinearity, see also INL                                                         |  |  |

| DNU              | do not use                                                                                      |  |  |

| DR               | port write data registers                                                                       |  |  |

| DSI              | digital system interconnect                                                                     |  |  |

| DWT              | data watchpoint and trace                                                                       |  |  |

| ECC              | error correcting code                                                                           |  |  |

| ECO              | external crystal oscillator                                                                     |  |  |

| EEPROM           | electrically erasable programmable read-only memory                                             |  |  |

| EMI              | electromagnetic interference                                                                    |  |  |

| EMIF             | external memory interface                                                                       |  |  |

| EOC              | end of conversion                                                                               |  |  |

| EOF              | end of frame                                                                                    |  |  |

| EPSR             | execution program status register                                                               |  |  |

| ESD              | electrostatic discharge                                                                         |  |  |

| ETM              | embedded trace macrocell                                                                        |  |  |

Table 14-1. Acronyms Used in this Document (continued)

| Acronym                  | Description                                            |  |  |

|--------------------------|--------------------------------------------------------|--|--|

|                          | ·                                                      |  |  |

| FIR                      | finite impulse response, see also IIR                  |  |  |

| FPB                      | flash patch and breakpoint                             |  |  |

| FS                       | full-speed                                             |  |  |

| GPIO                     | general-purpose input/output, applies to a PSoC pin    |  |  |

| HVI                      | high-voltage interrupt, see also LVI, LVD              |  |  |

| IC                       | integrated circuit                                     |  |  |

| IDAC                     | current DAC, see also DAC, VDAC                        |  |  |

| IDE                      | integrated development environment                     |  |  |

| I <sup>2</sup> C, or IIC | Inter-Integrated Circuit, a communications protocol    |  |  |

| IIR                      | infinite impulse response, see also FIR                |  |  |

| ILO                      | internal low-speed oscillator, see also IMO            |  |  |

| IMO                      | internal main oscillator, see also ILO                 |  |  |

| INL                      | integral nonlinearity, see also DNL                    |  |  |

| I/O                      | input/output, see also GPIO, DIO, SIO, USBIO           |  |  |

| IPOR                     | initial power-on reset                                 |  |  |

| IPSR                     | interrupt program status register                      |  |  |

| IRQ                      | interrupt request                                      |  |  |

| ITM                      | instrumentation trace macrocell                        |  |  |

| LCD                      | liquid crystal display                                 |  |  |

| LIN                      | Local Interconnect Network, a communications protocol. |  |  |

| LR                       | link register                                          |  |  |

| LUT                      | lookup table                                           |  |  |

| LVD                      | low-voltage detect, see also LVI                       |  |  |

| LVI                      | low-voltage interrupt, see also HVI                    |  |  |

| LVTTL                    | low-voltage transistor-transistor logic                |  |  |

| MAC                      | multiply-accumulate                                    |  |  |

| MCU                      | microcontroller unit                                   |  |  |

| MISO                     | master-in slave-out                                    |  |  |

| NC                       | no connect                                             |  |  |

| NMI                      | nonmaskable interrupt                                  |  |  |

| NRZ                      | non-return-to-zero                                     |  |  |

| NVIC                     | nested vectored interrupt controller                   |  |  |

| NVL                      | nonvolatile latch, see also WOL                        |  |  |

| opamp                    | operational amplifier                                  |  |  |

| PAL                      | programmable array logic, see also PLD                 |  |  |

| PC                       | program counter                                        |  |  |

| PCB                      | printed circuit board                                  |  |  |

| PGA                      | programmable gain amplifier                            |  |  |

| 1                        | I .                                                    |  |  |

Document Number: 001-53304 Rev. \*Y Page 126 of 137

Table 14-1. Acronyms Used in this Document (continued)

| Acronym           | Description                                                  |  |  |

|-------------------|--------------------------------------------------------------|--|--|

| PHUB              | peripheral hub                                               |  |  |

| PHY               | physical layer                                               |  |  |

| PICU              | port interrupt control unit                                  |  |  |

| PLA               | programmable logic array                                     |  |  |

| PLD               | programmable logic device, see also PAL                      |  |  |

| PLL               | phase-locked loop                                            |  |  |

| PMDD              | package material declaration data sheet                      |  |  |

| POR               | power-on reset                                               |  |  |

| PRES              | precise low-voltage reset                                    |  |  |

| PRS               | pseudo random sequence                                       |  |  |

| PS                | port read data register                                      |  |  |

| PSoC <sup>®</sup> | Programmable System-on-Chip™                                 |  |  |

| PSRR              | power supply rejection ratio                                 |  |  |

| PWM               | pulse-width modulator                                        |  |  |

| RAM               | random-access memory                                         |  |  |

| RISC              | reduced-instruction-set computing                            |  |  |

| RMS               | root-mean-square                                             |  |  |

| RTC               | real-time clock                                              |  |  |

| RTL               | register transfer language                                   |  |  |

| RTR               | remote transmission request                                  |  |  |

| RX                | receive                                                      |  |  |

| SAR               | successive approximation register                            |  |  |

| SC/CT             | switched capacitor/continuous time                           |  |  |

| SCL               | I <sup>2</sup> C serial clock                                |  |  |

| SDA               | I <sup>2</sup> C serial data                                 |  |  |

| S/H               | sample and hold                                              |  |  |

| SINAD             | signal to noise and distortion ratio                         |  |  |

| SIO               | special input/output, GPIO with advanced features. See GPIO. |  |  |

| SOC               | start of conversion                                          |  |  |

Table 14-1. Acronyms Used in this Document (continued)

| Acronym | Description                                                            |  |  |

|---------|------------------------------------------------------------------------|--|--|

| SOF     | start of frame                                                         |  |  |

| SPI     | Serial Peripheral Interface, a communications protocol                 |  |  |

| SR      | slew rate                                                              |  |  |

| SRAM    | static random access memory                                            |  |  |

| SRES    | software reset                                                         |  |  |

| SWD     | serial wire debug, a test protocol                                     |  |  |

| SWV     | single-wire viewer                                                     |  |  |

| TD      | transaction descriptor, see also DMA                                   |  |  |

| THD     | total harmonic distortion                                              |  |  |

| TIA     | transimpedance amplifier                                               |  |  |

| TRM     | technical reference manual                                             |  |  |

| TTL     | transistor-transistor logic                                            |  |  |

| TX      | transmit                                                               |  |  |

| UART    | Universal Asynchronous Transmitter Receiver, a communications protocol |  |  |

| UDB     | universal digital block                                                |  |  |

| USB     | Universal Serial Bus                                                   |  |  |

| USBIO   | USB input/output, PSoC pins used to connect to a USB port              |  |  |

| VDAC    | voltage DAC, see also DAC, IDAC                                        |  |  |

| WDT     | watchdog timer                                                         |  |  |

| WOL     | write once latch, see also NVL                                         |  |  |

| WRES    | watchdog timer reset                                                   |  |  |

| XRES    | external reset I/O pin                                                 |  |  |

| XTAL    | crystal                                                                |  |  |

## 15. Reference Documents

PSoC® 3, PSoC® 5 Architecture TRM PSoC® 3 Registers TRM

Document Number: 001-53304 Rev. \*Y Page 127 of 137

| Revision | ECN     | Submission<br>Date | Orig. of<br>Change                                                             | Description of Change                                                                                                                                |

|----------|---------|--------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| *D       | 2903576 | 04/01/10           | MKEA                                                                           | Updated Vb pin in PCB Schematic                                                                                                                      |

|          |         |                    |                                                                                | Updated Tstartup parameter in AC Specifications table                                                                                                |

|          |         |                    |                                                                                | Added Load regulation and Line regulation parameters to Inductive Boost                                                                              |

|          |         |                    |                                                                                | Regulator DC Specifications table                                                                                                                    |

|          |         |                    |                                                                                | Updated I <sub>CC</sub> parameter in LCD Direct Drive DC Specs table                                                                                 |

|          |         |                    |                                                                                | In page 1, updated internal oscillator range under Precision programmable clocking                                                                   |

|          |         |                    |                                                                                | to start from 3 MHz                                                                                                                                  |

|          |         |                    |                                                                                | Updated I <sub>OUT</sub> parameter in LCD Direct Drive DC Specs table Updated Table 6-2 and Table 6-3                                                |

|          |         |                    |                                                                                | Removed DFB block in Figure 1-1.                                                                                                                     |

|          |         |                    |                                                                                | Added bullets on CapSense in page 1; added CapSense column in Section 12                                                                             |

|          |         |                    |                                                                                | Removed some references to footnote [1]                                                                                                              |

|          |         |                    |                                                                                | Changed INC_Rn cycles from 3 to 2 (Table 4-1)                                                                                                        |

|          |         |                    |                                                                                | Added footnote in PLL AC Specification table                                                                                                         |

|          |         |                    |                                                                                | Added PLL intermediate frequency row with footnote in PLL AC Specs table                                                                             |

|          |         |                    |                                                                                | Added UDBs subsection under 11.6 Digital Peripherals                                                                                                 |

|          |         |                    |                                                                                | Updated Figure 2-6 (PCB Layout)                                                                                                                      |

|          |         |                    |                                                                                | Updated Pin Descriptions section and modified Figures 6-6, 6-8, 6-9                                                                                  |

|          |         |                    |                                                                                | Updated LVD in Tables 6-2 and 6-3; modified Low-power modes bullet in page                                                                           |

|          |         |                    |                                                                                | Added note to Figures 2-5 and 6-2; Updated Figure 6-2 to add capacitors for V <sub>D</sub>                                                           |

|          |         |                    |                                                                                | and V <sub>DDD</sub> pins.                                                                                                                           |

|          |         |                    |                                                                                | Updated boost converter section (6.2.2) Updated Tstartup values in Table 11-3.                                                                       |

|          |         |                    |                                                                                | Removed IPOR rows from Table 11-67.                                                                                                                  |

|          |         |                    |                                                                                | Updated 6.3.1.1, Power Voltage Level Monitors.                                                                                                       |

|          |         |                    |                                                                                | Updated section 5.2 and Table 11-2 to correct suggestion of execution from flas                                                                      |

|          |         |                    |                                                                                | Updated IMO max frequency in Figure 6-1, Table 11-77, and Table 11-78.                                                                               |

|          |         |                    |                                                                                | Updated V <sub>REF</sub> specs in Table 11-21.                                                                                                       |

|          |         |                    |                                                                                | Updated IDAC uncompensated gain error in Table 11-25.                                                                                                |

|          |         |                    |                                                                                | Updated Delay from Interrupt signal input to ISR code execution from ISR code                                                                        |

|          |         |                    |                                                                                | Table 11-57. Removed other line in table.                                                                                                            |

|          |         |                    |                                                                                | Added sentence to last paragraph of section 6.1.1.3.                                                                                                 |

|          |         |                    |                                                                                | Updated T <sub>RESP</sub> , high and low-power modes, in Table 11-24.                                                                                |

|          |         |                    |                                                                                | Updated f_TCK values in Table 11-72 and f_SWDCK values in Table 11-73.                                                                               |

|          |         |                    |                                                                                | Updated SNR condition in Table 11-20.                                                                                                                |

|          |         |                    |                                                                                | Updated sleep wakeup time in Table 6-3 and Tsleep in Table 11-3. Added 1.71 V <= V <sub>DDD</sub> < 3.3 V, SWD over USBIO pins value to Table 11-73. |

|          |         |                    | Removed mention of hibernate reset (HRES) from page 1 features, Table 6-3,     |                                                                                                                                                      |

|          |         |                    |                                                                                | Section 6.2.1.4, Section 6.3, and Section 6.3.1.1. Change PPOR/PRES to TBE                                                                           |

|          |         |                    |                                                                                | in Section 6.3.1.1, Section 6.4.1.6 (changed PPOR to reset), Table 11-3 (changed                                                                     |

|          |         |                    |                                                                                | PPOR to PRES), Table 11-67 (changed title, values TBD), and Table 11-68                                                                              |

|          |         |                    |                                                                                | (changed PPOR TR to PRES TR).                                                                                                                        |

|          |         |                    | Added sentence saying that LVD circuits can generate a reset to Section 6.3.1. |                                                                                                                                                      |

|          |         |                    |                                                                                | Changed I <sub>DD</sub> values on page 1, page 5, and Table 11-2.                                                                                    |

|          |         |                    |                                                                                | Changed resume time value in Section 6.2.1.3.                                                                                                        |

|          |         |                    |                                                                                | Changed ESD HBM value in Table 11-1.                                                                                                                 |

|          |         |                    |                                                                                | Changed sample rate row in Table 11-20. Removed V <sub>DDA</sub> = 1.65 V rows and                                                                   |

|          |         |                    |                                                                                | changed BWag value in Table 11-22.                                                                                                                   |

|          |         |                    |                                                                                | Changed V <sub>IOFF</sub> values and changed CMRR value in Table 11-23. Changed INL max value in Table 11-27.                                        |

|          |         |                    |                                                                                | Added max value to the Quiescent current specs in Tables 11-29 and 11-31.                                                                            |

|          |         |                    |                                                                                | Changed occurrences of "Block" to "Row" and deleted the "ECC not included"                                                                           |

|          |         |                    |                                                                                | footnote in Table 11-55.                                                                                                                             |

|          |         |                    |                                                                                | Changed max response time value in Tables 11-68 and 11-70.                                                                                           |

|          |         |                    |                                                                                | Changed the Startup time in Table 11-78.                                                                                                             |

|          |         |                    |                                                                                | Added condition to intermediate frequency row in Table 11-84.                                                                                        |

|          |         |                    |                                                                                | Added row to Table 11-68.                                                                                                                            |

|          |         |                    |                                                                                | Added brown out note to Section 11.8.1.                                                                                                              |

| Revision | t Number: (<br>ECN | Submission Date | Orig. of<br>Change | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------|--------------------|-----------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| *E       | 2938381            | 05/27/10        | MKEA               | Replaced V <sub>DDIO</sub> with V <sub>DDD</sub> in USBIO diagram and specification tables, added text in USBIO section of Electrical Specifications.  Added Table 13-2 (Package MSL)  Modified Tstorag condition and changed max spec to 100  Added bullet (Pass) under ALU (section 7.2.2.2)  Added figures for kHzECO and MHzECO in the External Oscillator section Updated Figure 6-1(Clocking Subsystem diagram)  Removed CPUCLK_DIV in table 5-2, Deleted Clock Divider SFR subsection Updated PSoC Creator Framework image  Updated SIO DC Specifications (V <sub>IH</sub> and V <sub>IL</sub> parameters)  Updated bullets in Clocking System and Clocking Distribution sections Updated Figure 8-2  Updated PCB Layout and Schematic, updated as per MTRB review comments Updated Table 6-3 (power changed to current)  In 32kHz EC DC Specifications table, changed I <sub>CC</sub> Max to 0.25  In IMO DC Specifications table, updated Supply Current values Updated GPIO DC Specs table  Modified to support a maximum 50MHz CPU speed |

| *F       | 2958674            | 06/22/10        | SHEA               | Minor ECN to post data sheet to external website                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |