Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                    |

| Core Processor             | 8051                                                                        |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 50MHz                                                                       |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                     |

| Peripherals                | CapSense, DMA, LCD, POR, PWM, WDT                                           |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 64KB (64K x 8)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 2K x 8                                                                      |

| RAM Size                   | 8K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                                |

| Data Converters            | A/D 16x12b; D/A 2x8b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 48-BSSOP (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 48-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c3446pvi-076t |

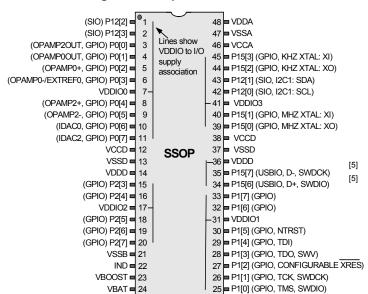

Figure 2-3. 48-pin SSOP Part Pinout

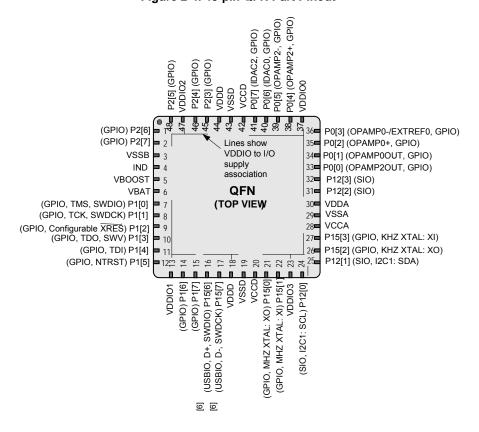

Figure 2-4. 48-pin QFN Part Pinout<sup>[7]</sup>

VBAT = 24

- Pins are Do Not Use (DNU) on devices without USB. The pin must be left floating.

- Pins are Do Not Use (DNU) on devices without USB. The pin must be left floating.

- The center pad on the QFN package should be connected to digital ground (VSSD) for best mechanical, thermal, and electrical performance. If not connected to ground, it should be electrically floated and not connected to any other signal. For more information, see AN72845, Design Guidelines for QFN Devices.

#### 4.3.1.3 Data Transfer Instructions

The data transfer instructions are of three types: the core RAM, xdata RAM, and the lookup tables. The core RAM transfer includes transfer between any two core RAM locations or SFRs. These instructions can use direct, indirect, register, and immediate addressing. The xdata RAM transfer includes only the transfer between the accumulator and the xdata RAM location. It can use only indirect addressing. The lookup tables involve nothing but the read of program memory using the Indexed addressing mode. Table 4-3 lists the various data transfer instructions available.

4.3.1.4 Boolean Instructions

The 8051 core has a separate bit addressable memory location. It has 128 bits of bit-addressable RAM and a set of SFRs that are bit addressable. The instruction set includes the whole menu of bit operations such as move, set, clear, toggle, OR, and AND instructions and the conditional jump instructions. Table 4-4 on page 16 lists the available Boolean instructions.

Table 4-3. Data Transfer Instructions

| N      | <b>I</b> nemonic | Description                                            | Bytes | Cycles |

|--------|------------------|--------------------------------------------------------|-------|--------|

| MOV A  | .,Rn             | Move register to accumulator                           | 1     | 1      |

| MOV A  | ,Direct          | Move direct byte to accumulator                        | 2     | 2      |

| MOV A  | .,@Ri            | Move indirect RAM to accumulator                       | 1     | 2      |

| MOV A  | ,#data           | Move immediate data to accumulator                     | 2     | 2      |

| MOV R  | Rn,A             | Move accumulator to register                           | 1     | 1      |

| MOV R  | Rn,Direct        | Move direct byte to register                           | 2     | 3      |

| MOV R  | Rn, #data        | Move immediate data to register                        | 2     | 2      |

| MOV D  | Direct, A        | Move accumulator to direct byte                        | 2     | 2      |

| MOV D  | Direct, Rn       | Move register to direct byte                           | 2     | 2      |

| MOV D  | Direct, Direct   | Move direct byte to direct byte                        | 3     | 3      |

| MOV D  | Direct, @Ri      | Move indirect RAM to direct byte                       | 2     | 3      |

| MOV D  | Direct, #data    | Move immediate data to direct byte                     | 3     | 3      |

| MOV @  | DRi, A           | Move accumulator to indirect RAM                       | 1     | 2      |

| MOV @  | Ri, Direct       | Move direct byte to indirect RAM                       | 2     | 3      |

| MOV @  | DRi, #data       | Move immediate data to indirect RAM                    | 2     | 2      |

| MOV D  | PTR, #data16     | Load data pointer with 16-bit constant                 | 3     | 3      |

| MOVC A | A, @A+DPTR       | Move code byte relative to DPTR to accumulator         | 1     | 5      |

| MOVC A | A, @A + PC       | Move code byte relative to PC to accumulator           | 1     | 4      |

| MOVX A | A,@Ri            | Move external RAM (8-bit) to accumulator               | 1     | 4      |

| MOVX A | A, @DPTR         | Move external RAM (16-bit) to accumulator              | 1     | 3      |

| MOVX @ | ®Ri, A           | Move accumulator to external RAM (8-bit)               | 1     | 5      |

| MOVX @ | DPTR, A          | Move accumulator to external RAM (16-bit)              | 1     | 4      |

| PUSH D | Direct           | Push direct byte onto stack                            | 2     | 3      |

| POP D  | Direct           | Pop direct byte from stack                             | 2     | 2      |

| XCH A  | A, Rn            | Exchange register with accumulator                     | 1     | 2      |

| XCH A  | A, Direct        | Exchange direct byte with accumulator                  | 2     | 3      |

| XCH A  | A, @Ri           | Exchange indirect RAM with accumulator                 | 1     | 3      |

| XCHD A | ., @Ri           | Exchange low order indirect digit RAM with accumulator | 1     | 3      |

Document Number: 001-53304 Rev. \*Y Page 15 of 137

**Table 4-8. Interrupt Vector Table**

| #  | Fixed Function            | DMA               | UDB          |

|----|---------------------------|-------------------|--------------|

| 0  | LVD                       | phub_termout0[0]  | udb_intr[0]  |

| 1  | Cache/ECC                 | phub_termout0[1]  | udb_intr[1]  |

| 2  | Reserved                  | phub_termout0[2]  | udb_intr[2]  |

| 3  | Sleep (Pwr Mgr)           | phub_termout0[3]  | udb_intr[3]  |

| 4  | PICU[0]                   | phub_termout0[4]  | udb_intr[4]  |

| 5  | PICU[1]                   | phub_termout0[5]  | udb_intr[5]  |

| 6  | PICU[2]                   | phub_termout0[6]  | udb_intr[6]  |

| 7  | PICU[3]                   | phub_termout0[7]  | udb_intr[7]  |

| 8  | PICU[4]                   | phub_termout0[8]  | udb_intr[8]  |

| 9  | PICU[5]                   | phub_termout0[9]  | udb_intr[9]  |

| 10 | PICU[6]                   | phub_termout0[10] | udb_intr[10] |

| 11 | PICU[12]                  | phub_termout0[11] | udb_intr[11] |

| 12 | PICU[15]                  | phub_termout0[12] | udb_intr[12] |

| 13 | Comparators<br>Combined   | phub_termout0[13] | udb_intr[13] |

| 14 | Switched Caps<br>Combined | phub_termout0[14] | udb_intr[14] |

| 15 | I <sup>2</sup> C          | phub_termout0[15] | udb_intr[15] |

| 16 | CAN                       | phub_termout1[0]  | udb_intr[16] |

| 17 | Timer/Counter0            | phub_termout1[1]  | udb_intr[17] |

| 18 | Timer/Counter1            | phub_termout1[2]  | udb_intr[18] |

| 19 | Timer/Counter2            | phub_termout1[3]  | udb_intr[19] |

| 20 | Timer/Counter3            | phub_termout1[4]  | udb_intr[20] |

| 21 | USB SOF Int               | phub_termout1[5]  | udb_intr[21] |

| 22 | USB Arb Int               | phub_termout1[6]  | udb_intr[22] |

| 23 | USB Bus Int               | phub_termout1[7]  | udb_intr[23] |

| 24 | USB Endpoint[0]           | phub_termout1[8]  | udb_intr[24] |

| 25 | USB Endpoint Data         | phub_termout1[9]  | udb_intr[25] |

| 26 | Reserved                  | phub_termout1[10] | udb_intr[26] |

| 27 | LCD                       | phub_termout1[11] | udb_intr[27] |

| 28 | Reserved                  | phub_termout1[12] | udb_intr[28] |

| 29 | Decimator Int             | phub_termout1[13] | udb_intr[29] |

| 30 | PHUB Error Int            | phub_termout1[14] | udb_intr[30] |

| 31 | EEPROM Fault Int          | phub_termout1[15] | udb_intr[31] |

### 6. System Integration

#### 6.1 Clocking System

The clocking system generates, divides, and distributes clocks throughout the PSoC system. For the majority of systems, no external crystal is required. The IMO and PLL together can generate up to a 50 MHz clock, accurate to ±2 percent over voltage and temperature. Additional internal and external clock sources allow each design to optimize accuracy, power, and cost. Any of the clock sources can be used to generate other clock frequencies in the 16-bit clock dividers and UDBs for anything the user wants, for example a UART baud rate generator.

Clock generation and distribution is automatically configured through the PSoC Creator IDE graphical interface. This is based on the complete system's requirements. It greatly speeds the design process. PSoC Creator allows you to build clocking systems with minimal input. You can specify desired clock frequencies and accuracies, and the software locates or builds a clock that meets the required specifications. This is possible because of the programmability inherent in PSoC.

Key features of the clocking system include:

- Seven general purpose clock sources

- □ 3- to 24-MHz IMO, ±2 percent at 3 MHz

- □ 4- to 25-MHz external crystal oscillator (MHzECO)

- Clock doubler provides a doubled clock frequency output for the USB block, see USB Clock Domain on page 30

- □ DSI signal from an external I/O pin or other logic

- 24- to 50- MHz fractional PLL sourced from IMO, MHzECO, or DSI

- 1 kHz, 33 kHz, 100 kHz ILO for Watch Dog Timer (WDT) and Sleep Timer

- □ 32.768-kHz external crystal oscillator (kHzECO) for RTC

- IMO has a USB mode that auto locks to the USB bus clock requiring no external crystal for USB. (USB equipped parts only)

- Independently sourced clock in all clock dividers

- Eight 16-bit clock dividers for the digital system

- Four 16-bit clock dividers for the analog system

- Dedicated 16-bit divider for the bus clock

- Dedicated 4-bit divider for the CPU clock

- Automatic clock configuration in PSoC Creator

Table 6-1. Oscillator Summary

| Source  | Fmin   | Tolerance at Fmin                | Fmax    | Tolerance at Fmax   | Startup Time                         |

|---------|--------|----------------------------------|---------|---------------------|--------------------------------------|

| IMO     | 3 MHz  | ±2% over voltage and temperature | 24 MHz  | ±4%                 | 13 µs max                            |

| MHzECO  | 4 MHz  | Crystal dependent                | 25 MHz  | Crystal dependent   | 5 ms typ, max is crystal dependent   |

| DSI     | 0 MHz  | Input dependent                  | 33 MHz  | Input dependent     | Input dependent                      |

| PLL     | 24 MHz | Input dependent                  | 50 MHz  | Input dependent     | 250 µs max                           |

| Doubler | 48 MHz | Input dependent                  | 48 MHz  | Input dependent     | 1 μs max                             |

| ILO     | 1 kHz  | <b>-50%</b> , <b>+100%</b>       | 100 kHz | -55%, <b>+</b> 100% | 15 ms max in lowest power mode       |

| kHzECO  | 32 kHz | Crystal dependent                | 32 kHz  | Crystal dependent   | 500 ms typ, max is crystal dependent |

Document Number: 001-53304 Rev. \*Y Page 27 of 137

#### 6.4 I/O System and Routing

PSoC I/Os are extremely flexible. Every GPIO has analog and digital I/O capability. All I/Os have a large number of drive modes, which are set at POR. PSoC also provides up to four individual I/O voltage domains through the VDDIO pins.

There are two types of I/O pins on every device; those with USB provide a third type. Both General Purpose I/O (GPIO) and Special I/O (SIO) provide similar digital functionality. The primary differences are their analog capability and drive strength. Devices that include USB also provide two USBIO pins that support specific USB functionality as well as limited GPIO capability.

All I/O pins are available for use as digital inputs and outputs for both the CPU and digital peripherals. In addition, all I/O pins can generate an interrupt. The flexible and advanced capabilities of the PSoC I/O, combined with any signal to any pin routability, greatly simplify circuit design and board layout. All GPIO pins can be used for analog input, CapSense<sup>[13]</sup>, and LCD segment drive, while SIO pins are used for voltages in excess of VDDA and for programmable output voltages.

- Features supported by both GPIO and SIO:

- □ User programmable port reset state

- □ Separate I/O supplies and voltages for up to four groups of I/O

- Digital peripherals use DSI to connect the pins

- Input or output or both for CPU and DMA

- Eight drive modes

- □ Every pin can be an interrupt source configured as rising edge, falling edge or both edges. If required, level sensitive interrupts are supported through the DSI

- Dedicated port interrupt vector for each port

- □ Slew rate controlled digital output drive mode

- Access port control and configuration registers on either port basis or pin basis

- □ Separate port read (PS) and write (DR) data registers to avoid read modify write errors

- □ Special functionality on a pin by pin basis

- Additional features only provided on the GPIO pins:

- LCD segment drive on LCD equipped devices

- □ CapSense<sup>[13]</sup>

- Analog input and output capability

- □ Continuous 100 µA clamp current capability

- Standard drive strength down to 1.7 V

- Additional features only provided on SIO pins:

- □ Higher drive strength than GPIO

- $\blacksquare$  Hot swap capability (5 V tolerance at any operating  $V_{DD}$ )

- □ Programmable and regulated high input and output drive levels down to 1.2 V

- No analog input, CapSense, or LCD capability

- Over voltage tolerance up to 5.5 V

- SIO can act as a general purpose analog comparator

- USBIO features:

- □ Full speed USB 2.0 compliant I/O

- □ Highest drive strength for general purpose use

- □ Input, output, or both for CPU and DMA

- □ Input, output, or both for digital peripherals

- □ Digital output (CMOS) drive mode

- □ Each pin can be an interrupt source configured as rising edge, falling edge, or both edges

Document Number: 001-53304 Rev. \*Y

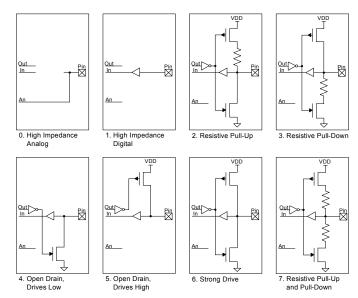

#### 6.4.1 Drive Modes

Each GPIO and SIO pin is individually configurable into one of the eight drive modes listed in Table 6-6. Three configuration bits are used for each pin (DM[2:0]) and set in the PRTxDM[2:0] registers. Figure 6-12 depicts a simplified pin view based on each of the eight drive modes. Table 6-6 shows the I/O pin's drive state based on the port data register value or digital array signal if bypass mode is selected. Note that the actual I/O pin voltage is determined by a combination of the selected drive mode and the load at the pin. For example, if a GPIO pin is configured for resistive pull-up mode and driven high while the pin is floating, the voltage measured at the pin is a high logic state. If the same GPIO pin is externally tied to ground then the voltage unmeasured at the pin is a low logic state.

Figure 6-12. Drive Mode

The 'Out' connection is driven from either the Digital System (when the Digital Output terminal is connected) or the Data Register

When HW connection is disabled).

The 'In' connection drives the Pin State register, and the Digital System if the Digital Input terminal is enabled and connected. The 'An' connection connects to the Analog System.

Table 6-6. Drive Modes

| Diagram | Drive Mode                                      | PRT×DM2 | PRT×DM1 | PRT×DM0 | PRT×DR = 1    | PRT×DR = 0   |

|---------|-------------------------------------------------|---------|---------|---------|---------------|--------------|

| 0       | High impedence analog                           | 0       | 0       | 0       | High Z        | High Z       |

| 1       | High Impedance digital                          | 0       | 0       | 1       | High Z        | High Z       |

| 2       | Resistive pull-up <sup>[14]</sup>               | 0       | 1       | 0       | Res High (5K) | Strong Low   |

| 3       | Resistive pull-down <sup>[14]</sup>             | 0       | 1       | 1       | Strong High   | Res Low (5K) |

| 4       | Open drain, drives low                          | 1       | 0       | 0       | High Z        | Strong Low   |

| 5       | Open drain, drive high                          | 1       | 0       | 1       | Strong High   | High Z       |

| 6       | Strong drive                                    | 1       | 1       | 0       | Strong High   | Strong Low   |

| 7       | Resistive pull-up and pull-down <sup>[14]</sup> | 1       | 1       | 1       | Res High (5K) | Res Low (5K) |

#### Note

<sup>14.</sup> Resistive pull-up and pull-down are not available with SIO in regulated output mode.

#### 7.1.3 Example System Function Components

The following is a sample of the system function components available in PSoC Creator for the CY8C34 family. The exact amount of hardware resources (UDBs, SC/CT blocks, routing, RAM, flash) used by a component varies with the features selected in PSoC Creator for the component.

- CapSense

- LCD Drive

- LCD Control

#### 7.1.4 Designing with PSoC Creator

#### 7.1.4.1 More Than a Typical IDE

A successful design tool allows for the rapid development and deployment of both simple and complex designs. It reduces or eliminates any learning curve. It makes the integration of a new design into the production stream straightforward.

PSoC Creator is that design tool.

PSoC Creator is a full featured Integrated Development Environment (IDE) for hardware and software design. It is optimized specifically for PSoC devices and combines a modern, powerful software development platform with a sophisticated graphical design tool. This unique combination of tools makes PSoC Creator the most flexible embedded design platform available.

Graphical design entry simplifies the task of configuring a particular part. You can select the required functionality from an extensive catalog of components and place it in your design. All components are parameterized and have an editor dialog that allows you to tailor functionality to your needs.

PSoC Creator automatically configures clocks and routes the I/O to the selected pins and then generates APIs to give the application complete control over the hardware. Changing the PSoC device configuration is as simple as adding a new component, setting its parameters, and rebuilding the project.

At any stage of development you are free to change the hardware configuration and even the target processor. To retarget your application (hardware and software) to new devices, even from 8- to 32-bit families, just select the new device and rebuild.

You also have the ability to change the C compiler and evaluate an alternative. Components are designed for portability and are validated against all devices, from all families, and against all supported tool chains. Switching compilers is as easy as editing the from the project options and rebuilding the application with no errors from the generated APIs or boot code.

#### 7.1.4.2 Component Catalog

The component catalog is a repository of reusable design elements that select device functionality and customize your PSoC device. It is populated with an impressive selection of content; from simple primitives such as logic gates and device registers, through the digital timers, counters and PWMs, plus analog components such as ADC, DACs, and filters, and communication protocols, such as I<sup>2</sup>C, USB, and CAN. See Example Peripherals on page 43 for more details about available peripherals. All content is fully characterized and carefully documented in data sheets with code examples, AC/DC specifications, and user code ready APIs.

#### 7.1.4.3 Design Reuse

The symbol editor gives you the ability to develop reusable components that can significantly reduce future design time. Just draw a symbol and associate that symbol with your proven design. PSoC Creator allows for the placement of the new symbol anywhere in the component catalog along with the content provided by Cypress. You can then reuse your content as many times as you want, and in any number of projects, without ever having to revisit the details of the implementation.

#### 7.1.4.4 Software Development

Anchoring the tool is a modern, highly customizable user interface. It includes project management and integrated editors for C and assembler source code, as well the design entry tools.

Project build control leverages compiler technology from top commercial vendors such as ARM<sup>®</sup> Limited, Keil™, and CodeSourcery (GNU). Free versions of Keil C51 and GNU C Compiler (GCC) for ARM, with no restrictions on code size or end product distribution, are included with the tool distribution. Upgrading to more optimizing compilers is a snap with support for the professional Keil C51 product and ARM RealView™ compiler.

#### 7.1.4.5 Nonintrusive Debugging

With JTAG (4-wire) and SWD (2-wire) debug connectivity available on all devices, the PSoC Creator debugger offers full control over the target device with minimum intrusion. Breakpoints and code execution commands are all readily available from toolbar buttons and an impressive lineup of windows—register, locals, watch, call stack, memory and peripherals—make for an unparalleled level of visibility into the system.

PSoC Creator contains all the tools necessary to complete a design, and then to maintain and extend that design for years to come. All steps of the design flow are carefully integrated and optimized for ease-of-use and to maximize productivity.

The bits of the control register, which may be written to by the system bus, are used to drive into the routing matrix, and thus provide firmware with the opportunity to control the state of UDB processing. The status register is read-only and it allows internal UDB state to be read out onto the system bus directly from internal routing. This allows firmware to monitor the state of UDB processing. Each bit of these registers has programmable connections to the routing matrix and routing connections are made depending on the requirements of the application.

#### 7.2.3.1 Usage Examples

As an example of control input, a bit in the control register can be allocated as a function enable bit. There are multiple ways to enable a function. In one method the control bit output would be routed to the clock control block in one or more UDBs and serve as a clock enable for the selected UDB blocks. A status example is a case where a PLD or datapath block generated a condition, such as a "compare true" condition that is captured and latched by the status register and then read (and cleared) by CPU firmware.

#### 7.2.3.2 Clock Generation

Each subcomponent block of a UDB including the two PLDs, the datapath, and Status and Control, has a clock selection and control block. This promotes a fine granularity with respect to allocating clocking resources to UDB component blocks and allows unused UDB resources to be used by other functions for maximum system efficiency.

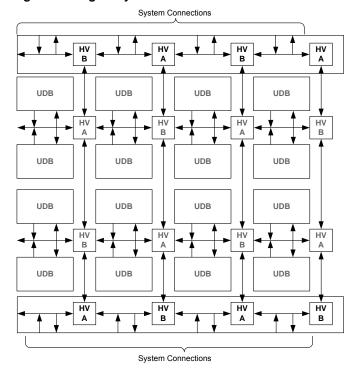

#### 7.3 UDB Array Description

Figure 7-7 shows an example of a 16 UDB array. In addition to the array core, there are a DSI routing interfaces at the top and bottom of the array. Other interfaces that are not explicitly shown include the system interfaces for bus and clock distribution. The UDB array includes multiple horizontal and vertical routing channels each comprised of 96 wires. The wire connections to UDBs, at horizontal/vertical intersection and at the DSI interface are highly permutable providing efficient automatic routing in PSoC Creator. Additionally the routing allows wire by wire segmentation along the vertical and horizontal routing to further increase routing flexibility and capability.

Figure 7-7. Digital System Interface Structure

## 7.3.1 UDB Array Programmable Resources

Figure 7-8 shows an example of how functions are mapped into a bank of 16 UDBs. The primary programmable resources of the UDB are two PLDs, one datapath and one status/control register. These resources are allocated independently, because they have independently selectable clocks, and therefore unused blocks are allocated to other unrelated functions.

An example of this is the 8-bit Timer in the upper left corner of the array. This function only requires one datapath in the UDB, and therefore the PLD resources may be allocated to another function. A function such as a Quadrature Decoder may require more PLD logic than one UDB can supply and in this case can utilize the unused PLD blocks in the 8-bit Timer UDB. Programmable resources in the UDB array are generally homogeneous so functions can be mapped to arbitrary boundaries in the array.

The TIA configuration is used for applications where an external sensor's output is current as a function of some type of stimulus such as temperature, light, magnetic flux etc. In a common application, the voltage DAC output can be connected to the  $V_{REF}$  TIA input to allow calibration of the external sensor bias current by adjusting the voltage DAC output voltage.

#### 8.6 LCD Direct Drive

The PSoC Liquid Crystal Display (LCD) driver system is a highly configurable peripheral designed to allow PSoC to directly drive a broad range of LCD glass. All voltages are generated on chip, eliminating the need for external components. With a high multiplex ratio of up to 1/16, the CY8C34 family LCD driver system can drive a maximum of 736 segments. The PSoC LCD driver module was also designed with the conservative power budget of portable devices in mind, enabling different LCD drive modes and power down modes to conserve power.

PSoC Creator provides an LCD segment drive component. The component wizard provides easy and flexible configuration of LCD resources. You can specify pins for segments and commons along with other options. The software configures the device to meet the required specifications. This is possible because of the programmability inherent to PSoC devices.

Key features of the PSoC LCD segment system are:

- LCD panel direct driving

- Type A (standard) and Type B (low-power) waveform support

- Wide operating voltage range support (2 V to 5 V) for LCD panels

- Static, 1/2, 1/3, 1/4, 1/5 bias voltage levels

- Internal bias voltage generation through internal resistor ladder

- Up to 62 total common and segment outputs

- Up to 1/16 multiplex for a maximum of 16 backplane/common outputs

- Up to 62 front plane/segment outputs for direct drive

- Drives up to 736 total segments (16 backplane × 46 front plane)

- Up to 64 levels of software controlled contrast

- Ability to move display data from memory buffer to LCD driver through DMA (without CPU intervention)

- Adjustable LCD refresh rate from 10 Hz to 150 Hz

- Ability to invert LCD display for negative image

- Three LCD driver drive modes, allowing power optimization

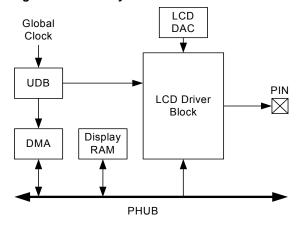

Figure 8-10. LCD System

#### 8.6.1 LCD Segment Pin Driver

Each GPIO pin contains an LCD driver circuit. The LCD driver buffers the appropriate output of the LCD DAC to directly drive the glass of the LCD. A register setting determines whether the pin is a common or segment. The pin's LCD driver then selects one of the six bias voltages to drive the I/O pin, as appropriate for the display data.

#### 8.6.2 Display Data Flow

The LCD segment driver system reads display data and generates the proper output voltages to the LCD glass to produce the desired image. Display data resides in a memory buffer in the system SRAM. Each time you need to change the common and segment driver voltages, the next set of pixel data moves from the memory buffer into the Port Data Registers via DMA.

#### 8.6.3 UDB and LCD Segment Control

A UDB is configured to generate the global LCD control signals and clocking. This set of signals is routed to each LCD pin driver through a set of dedicated LCD global routing channels. In addition to generating the global LCD control signals, the UDB also produces a DMA request to initiate the transfer of the next frame of LCD data.

#### 8.6.4 LCD DAC

The LCD DAC generates the contrast control and bias voltage for the LCD system. The LCD DAC produces up to five LCD drive voltages plus ground, based on the selected bias ratio. The bias voltages are driven out to GPIO pins on a dedicated LCD bias bus, as required.

#### 9.3 Debug Features

Using the JTAG or SWD interface, the CY8C34 supports the following debug features:

- Halt and single-step the CPU

- View and change CPU and peripheral registers, and RAM addresses

- Eight program address breakpoints

- One memory access breakpoint—break on reading or writing any memory address and data value

- Break on a sequence of breakpoints (non recursive)

- Debugging at the full speed of the CPU

- Compatible with PSoC Creator and MiniProg3 programmer and debugger

- Standard JTAG programming and debugging interfaces make CY8C34 compatible with other popular third-party tools (for example, ARM / Keil)

#### 9.4 Trace Features

The CY8C34 supports the following trace features when using JTAG or SWD:

- Trace the 8051 program counter (PC), accumulator register (ACC), and one SFR / 8051 core RAM register

- Trace depth up to 1000 instructions if all registers are traced, or 2000 instructions if only the PC is traced (on devices that include trace memory)

- Program address trigger to start tracing

- Trace windowing, that is, only trace when the PC is within a given range

- Two modes for handling trace buffer full: continuous (overwriting the oldest trace data) or break when trace buffer is full

#### 9.5 Single Wire Viewer Interface

The SWV interface is closely associated with SWD but can also be used independently. SWV data is output on the JTAG interface's TDO pin. If using SWV, you must configure the device for SWD, not JTAG. SWV is not supported with the JTAG interface.

SWV is ideal for application debug where it is helpful for the firmware to output data similar to 'printf' debugging on PCs. The SWV is ideal for data monitoring, because it requires only a single pin and can output data in standard UART format or Manchester encoded format. For example, it can be used to tune a PID control loop in which the output and graphing of the three error terms greatly simplifies coefficient tuning.

The following features are supported in SWV:

- 32 virtual channels, each 32 bits long

- Simple, efficient packing and serializing protocol

- Supports standard UART format (N81)

#### 9.6 Programming Features

The JTAG and SWD interfaces provide full programming support. The entire device can be erased, programmed, and

verified. You can increase flash protection levels to protect firmware IP. Flash protection can only be reset after a full device erase. Individual flash blocks can be erased, programmed, and verified, if block security settings permit.

#### 9.7 Device Security

PSoC 3 offers an advanced security feature called device security, which permanently disables all test, programming, and debug ports, protecting your application from external access. The device security is activated by programming a 32-bit key (0x50536F43) to a Write Once Latch (WOL).

The WOL is a type of nonvolatile latch (NVL). The cell itself is an NVL with additional logic wrapped around it. Each WOL device contains four bytes (32 bits) of data. The wrapper outputs a '1' if a super-majority (28 of 32) of its bits match a pre-determined pattern (0×50536F43); it outputs a '0' if this majority is not reached. When the output is 1, the Write Once NV latch locks the part out of Debug and Test modes; it also permanently gates off the ability to erase or alter the contents of the latch. Matching all bits is intentionally not required, so that single (or few) bit failures do not deassert the WOL output. The state of the NVL bits after wafer processing is truly random with no tendency toward 1 or 0.

The WOL only locks the part after the correct 32-bit key (0×50536F43) is loaded into the NVL's volatile memory, programmed into the NVL's nonvolatile cells, and the part is reset. The output of the WOL is only sampled on reset and used to disable the access. This precaution prevents anyone from reading, erasing, or altering the contents of the internal memory.

The user can write the key into the WOL to lock out external access only if no flash protection is set (see "Flash Security" on page 22). However, after setting the values in the WOL, a user still has access to the part until it is reset. Therefore, a user can write the key into the WOL, program the flash protection data, and then reset the part to lock it.

If the device is protected with a WOL setting, Cypress cannot perform failure analysis and, therefore, cannot accept RMAs from customers. The WOL can be read out via SWD port to electrically identify protected parts. The user can write the key in WOL to lock out external access only if no flash protection is set. For more information on how to take full advantage of the security features in PSoC see the PSoC 3 TRM.

#### Disclaimer

Note the following details of the flash code protection features on Cypress devices.

Cypress products meet the specifications contained in their particular Cypress data sheets. Cypress believes that its family of products is one of the most secure families of its kind on the market today, regardless of how they are used. There may be methods, unknown to Cypress, that can breach the code protection features. Any of these methods, to our knowledge, would be dishonest and possibly illegal. Neither Cypress nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Cypress is willing to work with the customer who is concerned about the integrity of their code. Code protection is constantly evolving. We at Cypress are committed to continuously improving the code protection features of our products.

Document Number: 001-53304 Rev. \*Y Page 68 of 137

### 11.4 Inputs and Outputs

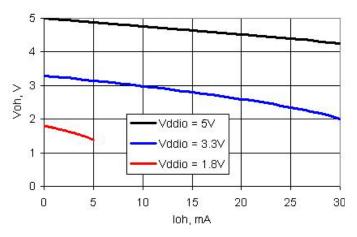

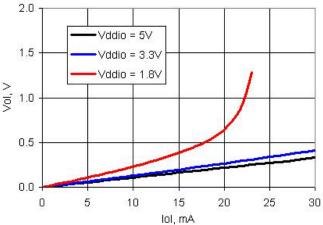

Specifications are valid for  $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$  and  $T_{J} \le 100~^{\circ}\text{C}$ , except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted. Unless otherwise specified, all charts and graphs show typical values.

When the power supplies ramp up, there are low-impedance connections between each GPIO pin and its  $V_{DDIO}$  supply. This causes the pin voltages to track  $V_{DDIO}$  until both  $V_{DDIO}$  and  $V_{DDA}$  reach the IPOR voltage, which can be as high as 1.45 V. At that point, the low-impedance connections no longer exist and the pins change to their normal NVL settings.

#### 11.4.1 GPIO

#### Table 11-9. GPIO DC Specifications

| Parameter       | Description                                                   | Conditions                                               | Min                     | Тур | Max                   | Units |

|-----------------|---------------------------------------------------------------|----------------------------------------------------------|-------------------------|-----|-----------------------|-------|

| V <sub>IH</sub> | Input voltage high threshold                                  | CMOS Input, PRT[×]CTL = 0                                | $0.7 \times V_{DDIO}$   | _   | _                     | V     |

| V <sub>IL</sub> | Input voltage low threshold                                   | CMOS Input, PRT[×]CTL = 0                                | _                       | _   | $0.3 \times V_{DDIO}$ | V     |

| V <sub>IH</sub> | Input voltage high threshold                                  | LVTTL Input, PRT[×]CTL = 1,V <sub>DDIO</sub> < 2.7 V     | $0.7 \times V_{DDIO}$   | -   | -                     | V     |

| V <sub>IH</sub> | Input voltage high threshold                                  | LVTTL Input, PRT[ $\times$ ]CTL = 1, $V_{DDIO} \ge 2.7V$ | 2.0                     | -   | -                     | V     |

| V <sub>IL</sub> | Input voltage low threshold                                   | LVTTL Input, PRT[×]CTL = 1,V <sub>DDIO</sub> < 2.7 V     | _                       | _   | $0.3 \times V_{DDIO}$ | V     |

| V <sub>IL</sub> | Input voltage low threshold                                   | LVTTL Input, PRT[ $\times$ ]CTL = 1, $V_{DDIO} \ge 2.7V$ | _                       | -   | 0.8                   | V     |

| V <sub>OH</sub> | Output voltage high                                           | I <sub>OH</sub> = 4 mA at 3.3 V <sub>DDIO</sub>          | V <sub>DDIO</sub> – 0.6 | -   | -                     | V     |

|                 |                                                               | I <sub>OH</sub> = 1 mA at 1.8 V <sub>DDIO</sub>          | V <sub>DDIO</sub> – 0.5 | _   | _                     | V     |

| V <sub>OL</sub> | Output voltage low                                            | I <sub>OL</sub> = 8 mA at 3.3 V <sub>DDIO</sub>          | _                       | -   | 0.6                   | V     |

|                 |                                                               | I <sub>OL</sub> = 4 mA at 1.8 V <sub>DDIO</sub>          | _                       | -   | 0.6                   | V     |

|                 |                                                               | I <sub>OL</sub> = 3 mA at 3.3 V <sub>DDIO</sub>          | _                       | _   | 0.4                   | V     |

| Rpullup         | Pull-up resistor                                              |                                                          | 3.5                     | 5.6 | 8.5                   | kΩ    |

| Rpulldown       | Pull-down resistor                                            |                                                          | 3.5                     | 5.6 | 8.5                   | kΩ    |

| I <sub>IL</sub> | Input leakage current (absolute value) <sup>[39]</sup>        | 25 °C, V <sub>DDIO</sub> = 3.0 V                         | _                       | _   | 2                     | nA    |

| C <sub>IN</sub> | Input capacitance <sup>[39]</sup>                             | GPIOs not shared with opamp outputs, MHz ECO or kHzECO   | _                       | 4   | 7                     | pF    |

|                 |                                                               | GPIOs shared with MHz ECO or kHzECO <sup>[40]</sup>      | _                       | 5   | 7                     | pF    |

|                 |                                                               | GPIOs shared with opamp outputs                          | _                       | -   | 18                    | pF    |

| V <sub>H</sub>  | Input voltage hysteresis (Schmitt-Trigger) <sup>[39]</sup>    |                                                          | -                       | 40  | -                     | mV    |

| Idiode          | Current through protection diode to $V_{DDIO}$ and $V_{SSIO}$ |                                                          | _                       | _   | 100                   | μΑ    |

| Rglobal         | Resistance pin to analog global bus                           | 25 °C, V <sub>DDIO</sub> = 3.0 V                         | _                       | 320 | _                     | Ω     |

| Rmux            | Resistance pin to analog mux bus                              | 25 °C, V <sub>DDIO</sub> = 3.0 V                         | _                       | 220 | _                     | Ω     |

#### Notes

<sup>39.</sup> Based on device characterization (Not production tested).

<sup>40.</sup> For information on designing with PSoC oscillators, refer to the application note, AN54439 - PSoC® 3 and PSoC 5 External Oscillator.

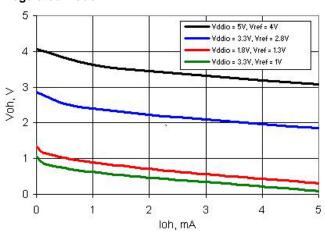

Figure 11-18. SIO Output Low Voltage and Current,

Figure 11-17. SIO Output High Voltage and Current, **Unregulated Mode**

Vddio = 5V 1.5 Vddio = 3.3V

**Unregulated Mode**

Figure 11-19. SIO Output High Voltage and Current, **Regulated Mode**

Table 11-12. SIO AC Specifications

| Parameter | Description                                            | Conditions                               | Min | Тур | Max | Units |

|-----------|--------------------------------------------------------|------------------------------------------|-----|-----|-----|-------|

| TriseF    | Rise time in Fast Strong Mode (90/10%) <sup>[44]</sup> | Cload = 25 pF, V <sub>DDIO</sub> = 3.3 V | -   | _   | 12  | ns    |

| TfallF    | Fall time in Fast Strong Mode (90/10%) <sup>[44]</sup> | Cload = 25 pF, V <sub>DDIO</sub> = 3.3 V | -   | _   | 12  | ns    |

| TriseS    | Rise time in Slow Strong Mode (90/10%) <sup>[44]</sup> | Cload = 25 pF, V <sub>DDIO</sub> = 3.0 V | -   | _   | 75  | ns    |

| TfallS    | Fall time in Slow Strong Mode (90/10%) <sup>[44]</sup> | Cload = 25 pF, V <sub>DDIO</sub> = 3.0 V | -   | _   | 60  | ns    |

<sup>44.</sup> Based on device characterization (Not production tested).

### 11.5 Analog Peripherals

Specifications are valid for  $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$  and  $T_{J} \le 100~^{\circ}\text{C}$ , except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted.

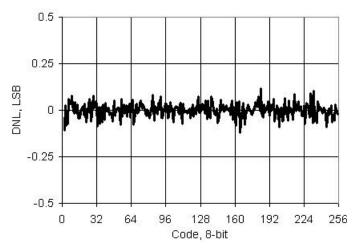

#### 11.5.1 Opamp

Table 11-19. Opamp DC Specifications

| Parameter         | Description                                 | Conditions                                                                                               | Min                     | Тур  | Max                     | Units   |

|-------------------|---------------------------------------------|----------------------------------------------------------------------------------------------------------|-------------------------|------|-------------------------|---------|

| V <sub>IOFF</sub> | Input offset voltage                        |                                                                                                          | -                       | -    | 2                       | mV      |

| Vos               | Input offset voltage                        |                                                                                                          | _                       | _    | 2.5                     | mV      |

|                   |                                             | Operating temperature –40 °C to 70 °C                                                                    | _                       | _    | 2                       | mV      |

| TCVos             | Input offset voltage drift with temperature | Power mode = high                                                                                        | _                       | _    | ±30                     | μV / °C |

| Ge1               | Gain error, unity gain buffer mode          | Rload = $1 \text{ k}\Omega$                                                                              | _                       | _    | ±0.1                    | %       |

| Cin               | Input capacitance                           | Routing from pin                                                                                         | _                       | _    | 18                      | pF      |

| Vo                | Output voltage range                        | 1 mA, source or sink, power mode = high                                                                  | V <sub>SSA</sub> + 0.05 | _    | V <sub>DDA</sub> – 0.05 | V       |

| lout              | Output current capability, source or sink   | $V_{SSA}$ + 500 mV $\leq$ Vout $\leq$ V <sub>DDA</sub><br>-500 mV, V <sub>DDA</sub> > 2.7 V              | 25                      | -    | -                       | mA      |

|                   |                                             | $V_{SSA}$ + 500 mV $\leq$ Vout $\leq$ V <sub>DDA</sub><br>-500 mV, 1.7 V = V <sub>DDA</sub> $\leq$ 2.7 V | 16                      | -    | -                       | mA      |

| Idd               | Quiescent current                           | Power mode = min                                                                                         | _                       | 250  | 400                     | uA      |

|                   |                                             | Power mode = low                                                                                         | =                       | 250  | 400                     | uA      |

|                   |                                             | Power mode = med                                                                                         | -                       | 330  | 950                     | uA      |

|                   |                                             | Power mode = high                                                                                        | -                       | 1000 | 2500                    | uA      |

| CMRR              | Common mode rejection ratio                 |                                                                                                          | 80                      | _    | _                       | dB      |

| PSRR              | Power supply rejection ratio                | $V_{DDA} \ge 2.7 \text{ V}$                                                                              | 85                      | -    | -                       | dB      |

|                   |                                             | V <sub>DDA</sub> < 2.7 V                                                                                 | 70                      | -    | -                       | dB      |

| I <sub>IB</sub>   | Input bias current <sup>[47]</sup>          | 25 °C                                                                                                    | -                       | 10   | _                       | pА      |

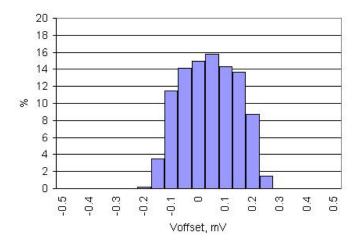

Figure 11-25. Opamp Voffset Histogram, 3388 samples/847 parts, 25  $^{\circ}\text{C},\,\text{V}_{\text{DDA}}$  = 5 V

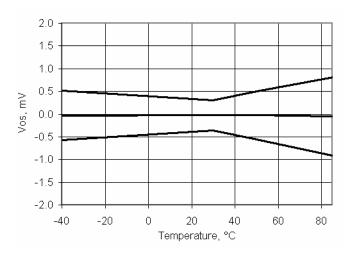

Figure 11-26. Opamp Voffset vs Temperature,  $V_{DDA} = 5V$

Page 88 of 137

#### Note

47. Based on device characterization (Not production tested).

Document Number: 001-53304 Rev. \*Y

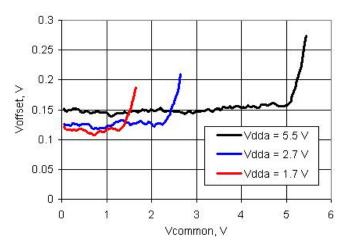

Figure 11-27. Opamp Voffset vs Vcommon and  $V_{DDA}$ , 25 °C

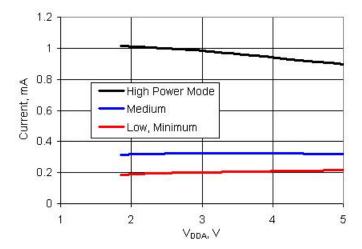

Figure 11-29. Opamp Operating Current vs  $V_{DDA}$  and Power Mode

Table 11-20. Opamp AC Specifications

| Parameter      | Description            | Conditions                                            | Min | Тур | Max | Units     |

|----------------|------------------------|-------------------------------------------------------|-----|-----|-----|-----------|

| GBW            | Gain-bandwidth product | Power mode = minimum, 15 pF load                      | 1   | _   | _   | MHz       |

|                |                        | Power mode = low, 15 pF load                          | 2   | _   | _   | MHz       |

|                |                        | Power mode = medium, 200 pF load                      | 1   | _   | _   | MHz       |

|                |                        | Power mode = high, 200 pF load                        | 3   | _   | _   | MHz       |

| SR             | Slew rate, 20% - 80%   | Power mode = low, 15 pF load                          | 1.1 | _   | _   | V/µs      |

|                |                        | Power mode = medium, 200 pF load                      | 0.9 | _   | _   | V/µs      |

|                |                        | Power mode = high, 200 pF load                        | 3   | _   | _   | V/µs      |

| e <sub>n</sub> | Input noise density    | Power mode = high, V <sub>DDA</sub> = 5 V, at 100 kHz | 1   | 45  | _   | nV/sqrtHz |

Figure 11-28. Opamp Output Voltage vs Load Current and Temperature, High Power Mode, 25  $^{\circ}$ C, V<sub>DDA</sub> = 2.7 V

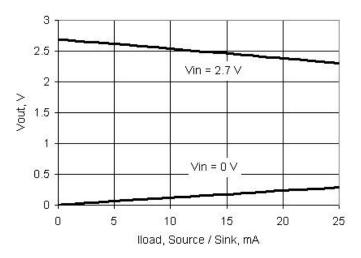

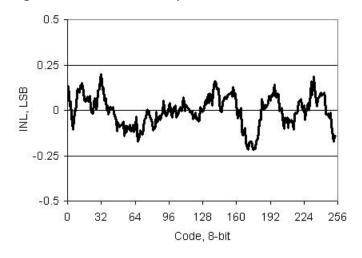

### 11.5.7 Voltage Digital to Analog Converter (VDAC)

See the VDAC component datasheet in PSoC Creator for full electrical specifications and APIs.

Unless otherwise specified, all charts and graphs show typical values.

Table 11-30. VDAC DC Specifications

| Parameter        | Description                               | Conditions                        | Min | Тур  | Max  | Units     |

|------------------|-------------------------------------------|-----------------------------------|-----|------|------|-----------|

|                  | Resolution                                |                                   | _   | 8    | -    | bits      |

| INL1             | Integral nonlinearity                     | 1 V scale                         | _   | ±2.1 | ±2.5 | LSB       |

| INL4             | Integral nonlinearity <sup>[55]</sup>     | 4 V scale                         | _   | ±2.1 | ±2.5 | LSB       |

| DNL1             | Differential nonlinearity                 | 1 V scale                         | _   | ±0.3 | ±1   | LSB       |

| DNL4             | Differential nonlinearity <sup>[55]</sup> | 4 V scale                         | _   | ±0.3 | ±1   | LSB       |

| Rout             | Output resistance                         | 1 V scale                         | _   | 4    | _    | kΩ        |

|                  |                                           | 4 V scale                         | _   | 16   | _    | kΩ        |

| V <sub>OUT</sub> | Output voltage range, code = 255          | 1 V scale                         | _   | 1.02 | _    | V         |

|                  |                                           | 4 V scale, V <sub>DDA</sub> = 5 V | _   | 4.08 | _    | V         |

|                  | Monotonicity                              |                                   | _   | -    | Yes  | _         |

| V <sub>OS</sub>  | Zero scale error                          |                                   | _   | 0    | ±0.9 | LSB       |

| Eg               | Gain error                                | 1 V scale                         | _   | -    | ±2.5 | %         |

|                  |                                           | 4 V scale                         | _   | -    | ±2.5 | %         |

| TC_Eg            | Temperature coefficient, gain error       | 1 V scale                         | _   | -    | 0.03 | %FSR / °C |

|                  |                                           | 4 V scale                         | _   | _    | 0.03 | %FSR / °C |

| I <sub>DD</sub>  | Operating current                         | Low speed mode                    | _   | _    | 100  | μA        |

|                  |                                           | High speed mode                   | _   | _    | 500  | μA        |

Figure 11-48. VDAC INL vs Input Code, 1 V Mode

Figure 11-49. VDAC DNL vs Input Code, 1 V Mode

#### Note

55. Based on device characterization (Not production tested).

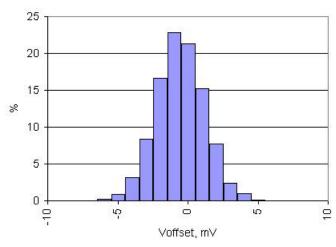

### 11.5.10 Programmable Gain Amplifier

The PGA is created using a SC/CT analog block; see the PGA component data sheet in PSoC Creator for full electrical specifications and APIs.

Unless otherwise specified, operating conditions are:

- Operating temperature = 25 °C for typical values

- Unless otherwise specified, all charts and graphs show typical values

Table 11-36. PGA DC Specifications

| Parameter | Description                                 | Conditions                                                                        | Min                     | Тур | Max                     | Units       |

|-----------|---------------------------------------------|-----------------------------------------------------------------------------------|-------------------------|-----|-------------------------|-------------|

| Vin       | Input voltage range                         | Power mode = minimum                                                              | Vssa                    | _   | $V_{DDA}$               | V           |

| Vos       | Input offset voltage                        | Power mode = high,<br>gain = 1                                                    | _                       | _   | 10                      | mV          |

| TCVos     | Input offset voltage drift with temperature | Power mode = high,<br>gain = 1                                                    | -                       | -   | ±30                     | μV/°C       |

| Ge1       | Gain error, gain = 1                        |                                                                                   | _                       | -   | ±0.15                   | %           |

| Ge16      | Gain error, gain = 16                       |                                                                                   | _                       | -   | ±2.5                    | %           |

| Ge50      | Gain error, gain = 50                       |                                                                                   | _                       | _   | ±5                      | %           |

| Vonl      | DC output nonlinearity                      | Gain = 1                                                                          | _                       | _   | ±0.01                   | % of<br>FSR |

| Cin       | Input capacitance                           |                                                                                   | _                       | _   | 7                       | pF          |

| Voh       | Output voltage swing                        | Power mode = high,<br>gain = 1, Rload = 100 kΩ<br>to $V_{DDA}$ / 2                | V <sub>DDA</sub> – 0.15 | -   | _                       | V           |

| Vol       | Output voltage swing                        | Power mode = high,<br>gain = 1, Rload = 100 k $\Omega$<br>to V <sub>DDA</sub> / 2 | -                       | -   | V <sub>SSA</sub> + 0.15 | V           |

| Vsrc      | Output voltage under load                   | lload = 250 μA, V <sub>DDA</sub> ≥ 2.7V, power mode = high                        | -                       | _   | 300                     | mV          |

| ldd       | Operating current                           | Power mode = high                                                                 | _                       | 1.5 | 1.65                    | mA          |

| PSRR      | Power supply rejection ratio                |                                                                                   | 48                      | _   | _                       | dB          |

Figure 11-60. PGA Voffset Histogram, 4096 samples/ 1024 parts

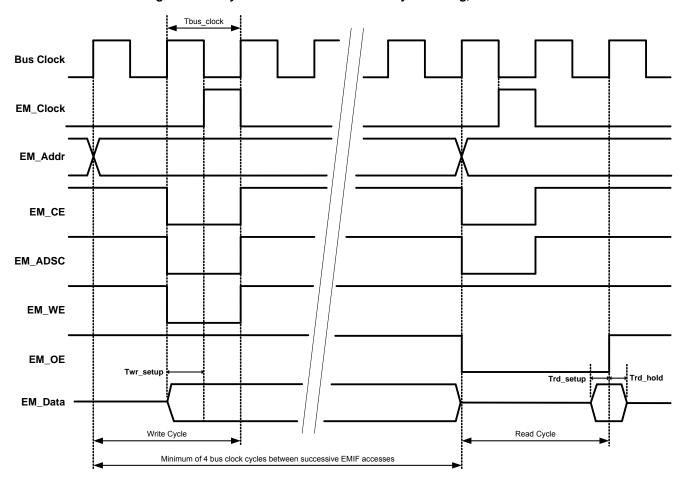

Figure 11-65. Synchronous Write and Read Cycle Timing, No Wait States

Table 11-62. Synchronous Write and Read Timing Specifications<sup>[63]</sup>

| Parameter  | Description                                                 | Conditions | Min             | Тур | Max | Units |

|------------|-------------------------------------------------------------|------------|-----------------|-----|-----|-------|

| Fbus_clock | Bus clock frequency <sup>[64]</sup>                         |            | _               | _   | 33  | MHz   |

| Tbus_clock | Bus clock period <sup>[65]</sup>                            |            | 30.3            | _   | _   | ns    |

| Twr_Setup  | Time from EM_data valid to rising edge of EM_Clock          |            | Tbus_clock - 10 | _   | _   | ns    |

| Trd_setup  | Time that EM_data must be valid before rising edge of EM_OE |            | 5               | -   | _   | ns    |

| Trd_hold   | Time that EM_data must be valid after rising edge of EM_OE  |            | 5               | _   | -   | ns    |

#### Notes

<sup>63.</sup> Based on device characterization (Not production tested).

64. EMIF signal timings are limited by GPIO frequency limitations. See "GPIO" section on page 79.

65. EMIF output signals are generally synchronized to bus clock, so EMIF signal timings are dependent on bus clock frequency.

0.395 0.420 0.292 0.299 DIMENSIONS IN INCHES MIN. PKG. WEIGHT: REFER TO PMDD SPEC. 0.620 SEATING PLANE .010 0.088 0.092 GAUGE PLANE 0.004 0.0<u>25</u> BSC 0.008 0.0135 0.008 51-85061 \*F

Figure 13-1. 48-pin (300 mil) SSOP Package Outline

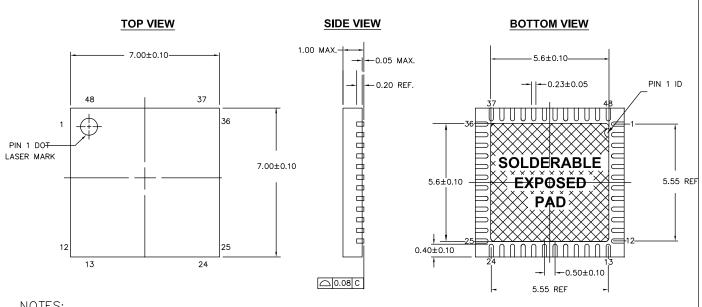

Figure 13-2. 48-pin QFN Package Outline

#### NOTES:

- 1.₩ HATCH AREA IS SOLDERABLE EXPOSED METAL.

- 2. REFERENCE JEDEC#: MO-220

- 3. PACKAGE WEIGHT: REFER TO PMDD SPEC.

- 4. ALL DIMENSIONS ARE IN MM [MIN/MAX]

- 5. PACKAGE CODE

| PART # | DESCRIPTION |

|--------|-------------|

| LT48D  | LEAD FREE   |

001-45616 \*E

| Revision | ECN     | Submission Date                                                                    | Orig. of<br>Change                                                                                                                                   | Description of Change                                                                                    |

|----------|---------|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| *D       | 2903576 | 04/01/10                                                                           | MKEA                                                                                                                                                 | Updated Vb pin in PCB Schematic                                                                          |

|          |         |                                                                                    |                                                                                                                                                      | Updated Tstartup parameter in AC Specifications table                                                    |

|          |         |                                                                                    |                                                                                                                                                      | Added Load regulation and Line regulation parameters to Inductive Boost                                  |

|          |         |                                                                                    |                                                                                                                                                      | Regulator DC Specifications table                                                                        |

|          |         |                                                                                    |                                                                                                                                                      | Updated I <sub>CC</sub> parameter in LCD Direct Drive DC Specs table                                     |

|          |         |                                                                                    |                                                                                                                                                      | In page 1, updated internal oscillator range under Precision programmable clocking a start from 2 AN II- |

|          |         |                                                                                    |                                                                                                                                                      | to start from 3 MHz Updated I <sub>OUT</sub> parameter in LCD Direct Drive DC Specs table                |

|          |         |                                                                                    |                                                                                                                                                      | Updated Table 6-2 and Table 6-3                                                                          |

|          |         |                                                                                    |                                                                                                                                                      | Removed DFB block in Figure 1-1.                                                                         |

|          |         |                                                                                    |                                                                                                                                                      | Added bullets on CapSense in page 1; added CapSense column in Section 12                                 |

|          |         |                                                                                    |                                                                                                                                                      | Removed some references to footnote [1]                                                                  |

|          |         |                                                                                    |                                                                                                                                                      | Changed INC_Rn cycles from 3 to 2 (Table 4-1)                                                            |

|          |         |                                                                                    |                                                                                                                                                      | Added footnote in PLL AC Specification table                                                             |

|          |         |                                                                                    |                                                                                                                                                      | Added PLL intermediate frequency row with footnote in PLL AC Specs table                                 |

|          |         |                                                                                    |                                                                                                                                                      | Added UDBs subsection under 11.6 Digital Peripherals                                                     |

|          |         |                                                                                    |                                                                                                                                                      | Updated Figure 2-6 (PCB Layout)                                                                          |

|          |         |                                                                                    |                                                                                                                                                      | Updated Pin Descriptions section and modified Figures 6-6, 6-8, 6-9                                      |

|          |         |                                                                                    |                                                                                                                                                      | Updated LVD in Tables 6-2 and 6-3; modified Low-power modes bullet in page                               |

|          |         |                                                                                    |                                                                                                                                                      | Added note to Figures 2-5 and 6-2; Updated Figure 6-2 to add capacitors for V <sub>D</sub>               |

|          |         |                                                                                    | and V <sub>DDD</sub> pins.                                                                                                                           |                                                                                                          |

|          |         |                                                                                    |                                                                                                                                                      | Updated boost converter section (6.2.2) Updated Tstartup values in Table 11-3.                           |

|          |         |                                                                                    | Removed IPOR rows from Table 11-67.                                                                                                                  |                                                                                                          |

|          |         |                                                                                    | Updated 6.3.1.1, Power Voltage Level Monitors.                                                                                                       |                                                                                                          |

|          |         |                                                                                    |                                                                                                                                                      | Updated section 5.2 and Table 11-2 to correct suggestion of execution from flas                          |

|          |         |                                                                                    |                                                                                                                                                      | Updated IMO max frequency in Figure 6-1, Table 11-77, and Table 11-78.                                   |

|          |         |                                                                                    |                                                                                                                                                      | Updated V <sub>REF</sub> specs in Table 11-21.                                                           |

|          |         |                                                                                    |                                                                                                                                                      | Updated IDAC uncompensated gain error in Table 11-25.                                                    |

|          |         |                                                                                    |                                                                                                                                                      | Updated Delay from Interrupt signal input to ISR code execution from ISR code                            |

|          |         |                                                                                    |                                                                                                                                                      | Table 11-57. Removed other line in table.                                                                |

|          |         |                                                                                    |                                                                                                                                                      | Added sentence to last paragraph of section 6.1.1.3.                                                     |

|          |         |                                                                                    |                                                                                                                                                      | Updated T <sub>RESP</sub> , high and low-power modes, in Table 11-24.                                    |

|          |         |                                                                                    |                                                                                                                                                      | Updated f_TCK values in Table 11-72 and f_SWDCK values in Table 11-73.                                   |

|          |         |                                                                                    | Updated SNR condition in Table 11-20.                                                                                                                |                                                                                                          |

|          |         |                                                                                    | Updated sleep wakeup time in Table 6-3 and Tsleep in Table 11-3. Added 1.71 V <= V <sub>DDD</sub> < 3.3 V, SWD over USBIO pins value to Table 11-73. |                                                                                                          |

|          |         |                                                                                    | Removed mention of hibernate reset (HRES) from page 1 features, Table 6-3,                                                                           |                                                                                                          |

|          |         |                                                                                    | Section 6.2.1.4, Section 6.3, and Section 6.3.1.1. Change PPOR/PRES to TBE                                                                           |                                                                                                          |

|          |         |                                                                                    | in Section 6.3.1.1, Section 6.4.1.6 (changed PPOR to reset), Table 11-3 (changed                                                                     |                                                                                                          |

|          |         |                                                                                    | PPOR to PRES), Table 11-67 (changed title, values TBD), and Table 11-68                                                                              |                                                                                                          |

|          |         |                                                                                    | (changed PPOR TR to PRES TR).                                                                                                                        |                                                                                                          |

|          |         |                                                                                    | Added sentence saying that LVD circuits can generate a reset to Section 6.3.1.                                                                       |                                                                                                          |

|          |         |                                                                                    | Changed I <sub>DD</sub> values on page 1, page 5, and Table 11-2.                                                                                    |                                                                                                          |

|          |         |                                                                                    | Changed resume time value in Section 6.2.1.3.                                                                                                        |                                                                                                          |

|          |         |                                                                                    | Changed ESD HBM value in Table 11-1.                                                                                                                 |                                                                                                          |

|          |         | Changed sample rate row in Table 11-20. Removed V <sub>DDA</sub> = 1.65 V rows and |                                                                                                                                                      |                                                                                                          |

|          |         |                                                                                    | changed BWag value in Table 11-22.                                                                                                                   |                                                                                                          |

|          |         |                                                                                    | Changed V <sub>IOFF</sub> values and changed CMRR value in Table 11-23. Changed INL max value in Table 11-27.                                        |                                                                                                          |

|          |         |                                                                                    | Added max value to the Quiescent current specs in Tables 11-29 and 11-31.                                                                            |                                                                                                          |

|          |         |                                                                                    |                                                                                                                                                      | Changed occurrences of "Block" to "Row" and deleted the "ECC not included"                               |