Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | 8051                                                                       |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 50MHz                                                                      |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART                 |

| Peripherals                | CapSense, DMA, LCD, POR, PWM, WDT                                          |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 64KB (64K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                               |

| Data Converters            | A/D 16x12b; D/A 2x8b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 48-BSSOP (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 48-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c3446pvi-102 |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

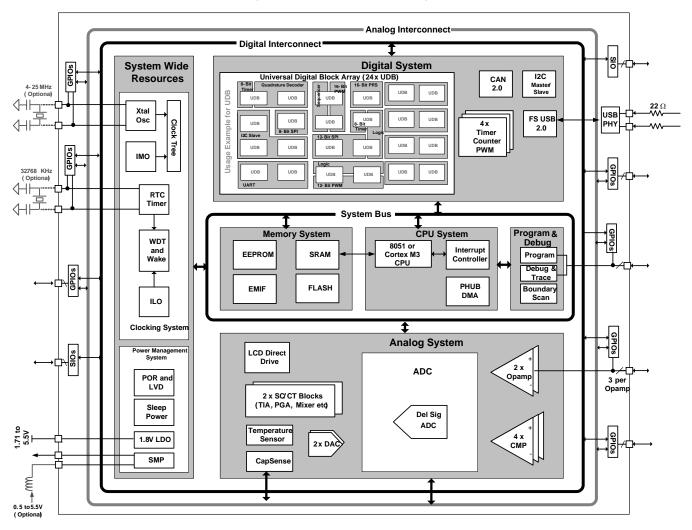

# 1. Architectural Overview

Introducing the CY8C34 family of ultra low-power, flash Programmable System-on-Chip (PSoC<sup>®</sup>) devices, part of a scalable 8-bit PSoC 3 and 32-bit PSoC 5 platform. The CY8C34 family provides configurable blocks of analog, digital, and interconnect circuitry around a CPU subsystem. The combination of a CPU with a flexible analog subsystem, digital subsystem, routing, and I/O enables a high level of integration in a wide variety of consumer, industrial, and medical applications.

Figure 1-1. Simplified Block Diagram

Figure 1-1 illustrates the major components of the CY8C34 family. They are:

- 8051 CPU subsystem

- Nonvolatile subsystem

- Programming, debug, and test subsystem

- Inputs and outputs

- Clocking

- Power

- Digital subsystem

## Analog subsystem

PSoC's digital subsystem provides half of its unique configurability. It connects a digital signal from any peripheral to any pin through the digital system interconnect (DSI). It also provides functional flexibility through an array of small, fast, lowpower UDBs. PSoC Creator provides a library of prebuilt and tested standard digital peripherals (UART, SPI, LIN, PRS, CRC, timer, counter, PWM, AND, OR, and so on) that are mapped to the UDB array. You can also easily create a digital circuit using boolean primitives by means of graphical design entry. Each UDB contains programmable array logic (PAL)/PLD functionality, together with a small state machine engine to support a wide variety of peripherals.

# 4.4 DMA and PHUB

The PHUB and the DMA controller are responsible for data transfer between the CPU and peripherals, and also data transfers between peripherals. The PHUB and DMA also control device configuration during boot. The PHUB consists of:

- A central hub that includes the DMA controller, arbiter, and router

- Multiple spokes that radiate outward from the hub to most peripherals

There are two PHUB masters: the CPU and the DMA controller. Both masters may initiate transactions on the bus. The DMA channels can handle peripheral communication without CPU intervention. The arbiter in the central hub determines which DMA channel is the highest priority if there are multiple requests.

## 4.4.1 PHUB Features

- CPU and DMA controller are both bus masters to the PHUB

- Eight Multi-layer AHB Bus parallel access paths (spokes) for peripheral access

- Simultaneous CPU and DMA access to peripherals located on different spokes

- Simultaneous DMA source and destination burst transactions on different spokes

- Supports 8, 16, 24, and 32-bit addressing and data

# Table 4-6. PHUB Spokes and Peripherals

| PHUB Spokes | Peripherals                                                                                         |

|-------------|-----------------------------------------------------------------------------------------------------|

| 0           | SRAM                                                                                                |

| 1           | IOs, PICU, EMIF                                                                                     |

| 2           | PHUB local configuration, Power manager,<br>Clocks, IC, SWV, EEPROM, Flash<br>programming interface |

| 3           | Analog interface and trim, Decimator                                                                |

| 4           | USB, CAN, I <sup>2</sup> C, Timers, Counters, and PWMs                                              |

| 5           | Reserved                                                                                            |

| 6           | UDBs group 1                                                                                        |

| 7           | UDBs group 2                                                                                        |

## 4.4.2 DMA Features

- Twenty-four DMA channels

- Each channel has one or more Transaction Descriptors (TDs) to configure channel behavior. Up to 128 total TDs can be defined

- TDs can be dynamically updated

- Eight levels of priority per channel

- Any digitally routable signal, the CPU, or another DMA channel, can trigger a transaction

- Each channel can generate up to two interrupts per transfer

- Transactions can be stalled or canceled

- Supports transaction size of infinite or 1 to 64 KB

- TDs may be nested and/or chained for complex transactions

## 4.4.3 Priority Levels

The CPU always has higher priority than the DMA controller when their accesses require the same bus resources. Due to the system architecture, the CPU can never starve the DMA. DMA channels of higher priority (lower priority number) may interrupt current DMA transfers. In the case of an interrupt, the current transfer is allowed to complete its current transaction. To ensure latency limits when multiple DMA accesses are requested simultaneously, a fairness algorithm guarantees an interleaved minimum percentage of bus bandwidth for priority levels 2 through 7. Priority levels 0 and 1 do not take part in the fairness algorithm and may use 100 percent of the bus bandwidth. If a tie occurs on two DMA requests of the same priority level, a simple round robin method is used to evenly share the allocated bandwidth. The round robin allocation can be disabled for each DMA channel, allowing it to always be at the head of the line. Priority levels 2 to 7 are guaranteed the minimum bus bandwidth shown in Table 4-7 after the CPU and DMA priority levels 0 and 1 have satisfied their requirements.

## Table 4-7. Priority Levels

| Priority Level | % Bus Bandwidth |

|----------------|-----------------|

| 0              | 100.0           |

| 1              | 100.0           |

| 2              | 50.0            |

| 3              | 25.0            |

| 4              | 12.5            |

| 5              | 6.2             |

| 6              | 3.1             |

| 7              | 1.5             |

When the fairness algorithm is disabled, DMA access is granted based solely on the priority level; no bus bandwidth guarantees are made.

## 4.4.4 Transaction Modes Supported

The flexible configuration of each DMA channel and the ability to chain multiple channels allow the creation of both simple and complex use cases. General use cases include, but are not limited to:

- Multiple I/O interrupt vectors

- Software can send interrupts

- Software can clear pending interrupts

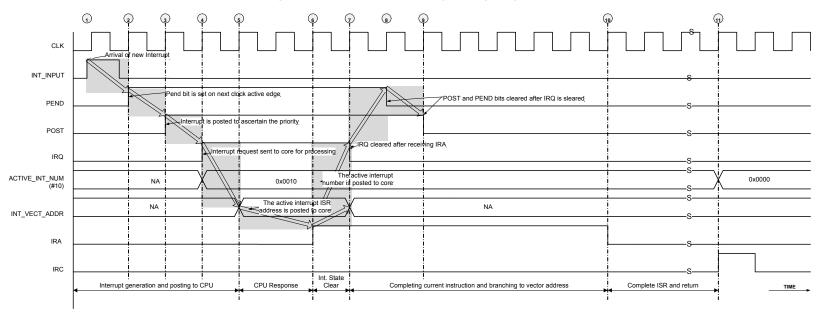

When an interrupt is pending, the current instruction is completed and the program counter is pushed onto the stack. Code execution then jumps to the program address provided by the vector. After the ISR is completed, a RETI instruction is executed and returns execution to the instruction following the previously interrupted instruction. To do this the RETI instruction pops the program counter from the stack.

If the same priority level is assigned to two or more interrupts, the interrupt with the lower vector number is executed first. Each interrupt vector may choose from three interrupt sources: Fixed Function, DMA, and UDB. The fixed function interrupts are

direct connections to the most common interrupt sources and provide the lowest resource cost connection. The DMA interrupt sources provide direct connections to the two DMA interrupt sources provided per DMA channel. The third interrupt source for vectors is from the UDB digital routing array. This allows any digital signal available to the UDB array to be used as an interrupt source. Fixed function interrupts and all interrupt sources may be routed to any interrupt vector using the UDB interrupt source connections.

Figure 4-2 represents typical flow of events when an interrupt triggered. Figure 4-3 on page 20 shows the interrupt structure and priority polling.

## Figure 4-2. Interrupt Processing Timing Diagram

## Notes

- 1: Interrupt triggered asynchronous to the clock

- 2: The PEND bit is set on next active clock edge to indicate the interrupt arrival

- 3: POST bit is set following the PEND bit

- 4: Interrupt request and the interrupt number sent to CPU core after evaluation priority (Takes 3 clocks)

- 5: ISR address is posted to CPU core for branching

# 5.7 Memory Map

The CY8C34 8051 memory map is very similar to the MCS-51 memory map.

## 5.7.1 Code Space

The CY8C34 8051 code space is 64 KB. Only main flash exists in this space. See the "Flash Program Memory" section on page 22.

## 5.7.2 Internal Data Space

The CY8C34 8051 internal data space is 384 bytes, compressed within a 256-byte space. This space consists of 256 bytes of RAM (in addition to the SRAM mentioned in Static RAM on page 22) and a 128-byte space for Special Function Registers (SFRs). See Figure 5-2. The lowest 32 bytes are used for 4 banks of registers R0-R7. The next 16 bytes are bit-addressable.

# Figure 5-2. 8051 Internal Data Space

| 0x00 | 4 Denka F                                                                          |                                                                            |  |  |  |  |  |  |

|------|------------------------------------------------------------------------------------|----------------------------------------------------------------------------|--|--|--|--|--|--|

| 0x1F | 4 Bariks, P                                                                        | 0-R7 Each                                                                  |  |  |  |  |  |  |

| 0x20 | Dit Addros                                                                         | sable Area                                                                 |  |  |  |  |  |  |

| 0x2F | Dit-Addres                                                                         | Sadie Alea                                                                 |  |  |  |  |  |  |

| 0x30 |                                                                                    |                                                                            |  |  |  |  |  |  |

|      |                                                                                    | Lower Core RAM Shared with Stack Space<br>(direct and indirect addressing) |  |  |  |  |  |  |

| 0x7F |                                                                                    | oot addrooonig,                                                            |  |  |  |  |  |  |

| 0x80 |                                                                                    |                                                                            |  |  |  |  |  |  |

|      | Upper Core RAM Shared                                                              | SFR<br>On a sint Function Desinters                                        |  |  |  |  |  |  |

|      | with Stack SpaceSpecial Function Registers(indirect addressing)(direct addressing) |                                                                            |  |  |  |  |  |  |

| 0xFF | (indirect addressing)                                                              | (uncor addressing)                                                         |  |  |  |  |  |  |

In addition to the register or bit address modes used with the lower 48 bytes, the lower 128 bytes can be accessed with direct or indirect addressing. With direct addressing mode, the upper 128 bytes map to the SFRs. With indirect addressing mode, the upper 128 bytes map to RAM. Stack operations use indirect addressing; the 8051 stack space is 256 bytes. See the "Addressing Modes" section on page 12

## 5.7.3 SFRs

The Special Function Register (SFR) space provides access to frequently accessed registers. The memory map for the SFR memory space is shown in Table 5-4.

| Address | 0/8        | 1/9        | 2/A         | 3/B  | 4/C  | 5/D  | 6/E | 7/F |

|---------|------------|------------|-------------|------|------|------|-----|-----|

| 0×F8    | SFRPRT15DR | SFRPRT15PS | SFRPRT15SEL |      |      |      |     |     |

| 0×F0    | В          |            | SFRPRT12SEL |      |      |      |     |     |

| 0×E8    | SFRPRT12DR | SFRPRT12PS | MXAX        |      |      |      |     |     |

| 0×E0    | ACC        |            |             |      |      |      |     |     |

| 0×D8    | SFRPRT6DR  | SFRPRT6PS  | SFRPRT6SEL  |      |      |      |     |     |

| 0×D0    | PSW        |            |             |      |      |      |     |     |

| 0×C8    | SFRPRT5DR  | SFRPRT5PS  | SFRPRT5SEL  |      |      |      |     |     |

| 0×C0    | SFRPRT4DR  | SFRPRT4PS  | SFRPRT4SEL  |      |      |      |     |     |

| 0×B8    |            |            |             |      |      |      |     |     |

| 0×B0    | SFRPRT3DR  | SFRPRT3PS  | SFRPRT3SEL  |      |      |      |     |     |

| 0×A8    | IE         |            |             |      |      |      |     |     |

| 0×A0    | P2AX       |            | SFRPRT1SEL  |      |      |      |     |     |

| 0×98    | SFRPRT2DR  | SFRPRT2PS  | SFRPRT2SEL  |      |      |      |     |     |

| 0×90    | SFRPRT1DR  | SFRPRT1PS  |             | DPX0 |      | DPX1 |     |     |

| 0×88    |            | SFRPRT0PS  | SFRPRT0SEL  |      |      |      |     |     |

| 0×80    | SFRPRT0DR  | SP         | DPL0        | DPH0 | DPL1 | DPH1 | DPS |     |

## Table 5-4. SFR Map

can generate custom clocks derived from any of the seven clock sources for any purpose. Examples include baud rate generators, accurate PWM periods, and timer clocks, and many others. If more than eight digital clock dividers are required, the Universal Digital Blocks (UDBs) and fixed function Timer/Counter/PWMs can also generate clocks.

Four 16-bit clock dividers generate clocks for the analog system components that require clocking, such as ADC and mixers. The analog clock dividers include skew control to ensure that critical analog events do not occur simultaneously with digital switching events. This is done to reduce analog system noise. Each clock divider consists of an 8-input multiplexer, a 16-bit clock divider (divide by 2 and higher) that generates ~50 percent duty cycle clocks, master clock resynchronization logic, and deglitch logic. The outputs from each digital clock tree can be routed into the digital system interconnect and then brought back into the clock system as an input, allowing clock chaining of up to 32 bits.

## 6.1.4 USB Clock Domain

The USB clock domain is unique in that it operates largely asynchronously from the main clock network. The USB logic contains a synchronous bus interface to the chip, while running on an asynchronous clock to process USB data. The USB logic requires a 48 MHz frequency. This frequency can be generated from different sources, including DSI clock at 48 MHz or doubled value of 24 MHz from internal oscillator, DSI signal, or crystal oscillator.

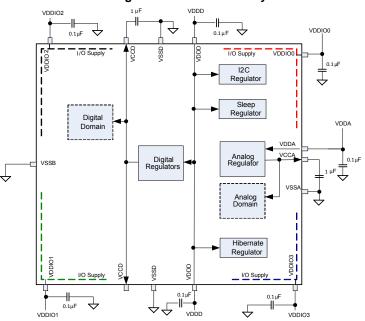

## 6.2 Power System

The power system consists of separate analog, digital, and I/O supply pins, labeled VDDA, VDDD, and VDDIOX, respectively. It also includes two internal 1.8 V regulators that provide the digital (VCCD) and analog (Vcca) supplies for the internal core logic. The output pins of the regulators (VCCD and VCCA) and the VDDIO pins must have capacitors connected as shown in Figure 6-4. The two VCCD pins must be shorted together, with as short a trace as possible, and connected to a 1  $\mu$ F ±10 percent X5R capacitor. The power system also contains a sleep regulator, an I<sup>2</sup>C regulator, and a hibernate regulator.

#### Figure 6-4. PSoC Power System

# Notes

- The two VCCD pins must be connected together with as short a trace as possible. A trace under the device is recommended, as shown in Figure 2-8 on page 11.

- It is good practice to check the datasheets for your bypass capacitors, specifically the working voltage and the DC bias specifications. With some capacitors, the actual capacitance can decrease considerably when the DC bias (VDDX or VCCX in Figure 6-4) is a significant percentage of the rated working voltage.

- You can power the device in internally regulated mode, where the voltage applied to the VDDx pins is as high as 5.5 V, and the internal regulators provide the core voltages. In this mode, do not apply power to the VCCx pins, and do not tie the VDDx pins to the VCCx pins.

- You can also power the device in externally regulated mode, that is, by directly powering the VCCD and VCCA pins. In this configuration, the VDDD pins should be shorted to the VCCD pins and the VDDA pin should be shorted to the VCCA pin. The allowed supply range in this configuration is 1.71 V to 1.89 V. After power up in this configuration, the internal regulators are on by default, and should be disabled to reduce power consumption.

# 6.4 I/O System and Routing

PSoC I/Os are extremely flexible. Every GPIO has analog and digital I/O capability. All I/Os have a large number of drive modes, which are set at POR. PSoC also provides up to four individual I/O voltage domains through the VDDIO pins.

There are two types of I/O pins on every device; those with USB provide a third type. Both General Purpose I/O (GPIO) and Special I/O (SIO) provide similar digital functionality. The primary differences are their analog capability and drive strength. Devices that include USB also provide two USBIO pins that support specific USB functionality as well as limited GPIO capability.

All I/O pins are available for use as digital inputs and outputs for both the CPU and digital peripherals. In addition, all I/O pins can generate an interrupt. The flexible and advanced capabilities of the PSoC I/O, combined with any signal to any pin routability, greatly simplify circuit design and board layout. All GPIO pins can be used for analog input, CapSense<sup>[13]</sup>, and LCD segment drive, while SIO pins are used for voltages in excess of VDDA and for programmable output voltages.

- Features supported by both GPIO and SIO:

- User programmable port reset state

- □ Separate I/O supplies and voltages for up to four groups of I/O

- Digital peripherals use DSI to connect the pins

- Input or output or both for CPU and DMA

- Eight drive modes

- Every pin can be an interrupt source configured as rising edge, falling edge or both edges. If required, level sensitive interrupts are supported through the DSI

- Dedicated port interrupt vector for each port

- Slew rate controlled digital output drive mode

- Access port control and configuration registers on either port basis or pin basis

- Separate port read (PS) and write (DR) data registers to avoid read modify write errors

- Special functionality on a pin by pin basis

- Additional features only provided on the GPIO pins:

- LCD segment drive on LCD equipped devices

- CapSense<sup>[13]</sup>

- Analog input and output capability

- Continuous 100 µA clamp current capability

- Standard drive strength down to 1.7 V

- Additional features only provided on SIO pins:

- B Higher drive strength than GPIO

- $\blacksquare$  Hot swap capability (5 V tolerance at any operating V\_{DD})

- Programmable and regulated high input and output drive levels down to 1.2 V

- D No analog input, CapSense, or LCD capability

- Dver voltage tolerance up to 5.5 V

- □ SIO can act as a general purpose analog comparator

- USBIO features:

- □ Full speed USB 2.0 compliant I/O

- Highest drive strength for general purpose use

- □ Input, output, or both for CPU and DMA

- □ Input, output, or both for digital peripherals

- Digital output (CMOS) drive mode

- Each pin can be an interrupt source configured as rising edge, falling edge, or both edges

<sup>13.</sup> GPIOs with opamp outputs are not recommended for use with CapSense

# 6.4.5 Pin Interrupts

All GPIO and SIO pins are able to generate interrupts to the system. All eight pins in each port interface to their own Port Interrupt Control Unit (PICU) and associated interrupt vector. Each pin of the port is independently configurable to detect rising edge, falling edge, both edge interrupts, or to not generate an interrupt.

Depending on the configured mode for each pin, each time an interrupt event occurs on a pin, its corresponding status bit of the interrupt status register is set to "1" and an interrupt request is sent to the interrupt controller. Each PICU has its own interrupt vector in the interrupt controller and the pin status register providing easy determination of the interrupt source down to the pin level.

Port pin interrupts remain active in all sleep modes allowing the PSoC device to wake from an externally generated interrupt.

While level sensitive interrupts are not directly supported; Universal Digital Blocks (UDB) provide this functionality to the system when needed.

## 6.4.6 Input Buffer Mode

GPIO and SIO input buffers can be configured at the port level for the default CMOS input thresholds or the optional LVTTL input thresholds. All input buffers incorporate Schmitt triggers for input hysteresis. Additionally, individual pin input buffers can be disabled in any drive mode.

## 6.4.7 I/O Power Supplies

Up to four I/O pin power supplies are provided depending on the device and package. Each I/O supply must be less than or equal to the voltage on the chip's analog (VDDA) pin. This feature allows users to provide different I/O voltage levels for different pins on the device. Refer to the specific device package pinout to determine VDDIO capability for a given port and pin.

The SIO port pins support an additional regulated high output capability, as described in Adjustable Output Level.

## 6.4.8 Analog Connections

These connections apply only to GPIO pins. All GPIO pins may be used as analog inputs or outputs. The analog voltage present on the pin must not exceed the VDDIO supply voltage to which the GPIO belongs. Each GPIO may connect to one of the analog global busses or to one of the analog mux buses to connect any pin to any internal analog resource such as ADC or comparators. In addition, select pins provide direct connections to specific analog features such as the high current DACs or uncommitted opamps.

## 6.4.9 CapSense

This section applies only to GPIO pins. All GPIO pins may be used to create CapSense buttons and sliders<sup>[15]</sup>. See the "CapSense" section on page 64 for more information.

## 6.4.10 LCD Segment Drive

This section applies only to GPIO pins. All GPIO pins may be used to generate Segment and Common drive signals for direct glass drive of LCD glass. See the "LCD Direct Drive" section on page 63 for details.

## 6.4.11 Adjustable Output Level

This section applies only to SIO pins. SIO port pins support the ability to provide a regulated high output level for interface to external signals that are lower in voltage than the SIO's respective VDDIO. SIO pins are individually configurable to output either the standard VDDIO level or the regulated output, which is based on an internally generated reference. Typically a voltage DAC (VDAC) is used to generate the reference (see Figure 6-13). The "DAC" section on page 64 has more details on VDAC use and reference routing to the SIO pins. Resistive pull-up and pull-down drive modes are not available with SIO in regulated output mode.

## 6.4.12 Adjustable Input Level

This section applies only to SIO pins. SIO pins by default support the standard CMOS and LVTTL input levels but also support a differential mode with programmable levels. SIO pins are grouped into pairs. Each pair shares a reference generator block which, is used to set the digital input buffer reference level for interface to external signals that differ in voltage from VDDIO. The reference sets the pins voltage threshold for a high logic level (see Figure 6-13). Available input thresholds are:

- 0.5 × VDDIO

- 0.4 × VDDIO

- 0.5 × VREF

- VREF

Typically a voltage DAC (VDAC) generates the V<sub>REF</sub> reference. "DAC" section on page 64 has more details on VDAC use and reference routing to the SIO pins.

The PSoC Creator tool offers a user friendly interface, which allows you to easily program the SC/CT blocks. Switch control and clock phase control configuration is done by PSoC Creator so users only need to determine the application use parameters such as gain, amplifier polarity,  $V_{\text{REF}}$  connection, and so on.

The same opamps and block interfaces are also connectable to an array of resistors which allows the construction of a variety of continuous time functions.

The opamp and resistor array is programmable to perform various analog functions including

- Naked operational amplifier Continuous mode

- Unity-gain buffer Continuous mode

- Programmable gain amplifier (PGA) Continuous mode

- Transimpedance amplifier (TIA) Continuous mode

- Up/down mixer Continuous mode

- Sample and hold mixer (NRZ S/H) Switched cap mode

- First order analog to digital modulator Switched cap mode

## 8.5.1 Naked Opamp

The Naked Opamp presents both inputs and the output for connection to internal or external signals. The opamp has a unity gain bandwidth greater than 6.0 MHz and output drive current up to 650  $\mu$ A. This is sufficient for buffering internal signals (such as DAC outputs) and driving external loads greater than 7.5 kohms.

## 8.5.2 Unity Gain

The Unity Gain buffer is a Naked Opamp with the output directly connected to the inverting input for a gain of 1.00. It has a -3 dB bandwidth greater than 6.0 MHz.

## 8.5.3 PGA

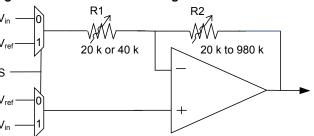

The PGA amplifies an external or internal signal. The PGA can be configured to operate in inverting mode or noninverting mode. The PGA function may be configured for both positive and negative gains as high as 50 and 49 respectively. The gain is adjusted by changing the values of R1 and R2 as illustrated in Figure 8-8. The schematic in Figure 8-8 shows the configuration and possible resistor settings for the PGA. The gain is switched from inverting and non inverting by changing the shared select value of the both the input muxes. The bandwidth for each gain case is listed in Table 8-3.

# Table 8-3. Bandwidth

| Gain | Bandwidth |

|------|-----------|

| 1    | 6.0 MHz   |

| 24   | 340 kHz   |

| 48   | 220 kHz   |

| 50   | 215 kHz   |

The PGA is used in applications where the input signal may not be large enough to achieve the desired resolution in the ADC, or dynamic range of another SC/CT block such as a mixer. The gain is adjustable at runtime, including changing the gain of the PGA prior to each ADC sample.

## 8.5.4 TIA

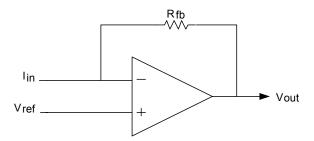

The Transimpedance Amplifier (TIA) converts an internal or external current to an output voltage. The TIA uses an internal feedback resistor in a continuous time configuration to convert input current to output voltage. For an input current I<sub>in</sub>, the output voltage is V<sub>REF</sub> - I<sub>in</sub> x R<sub>fb</sub>, where V<sub>REF</sub> is the value placed on the non inverting input. The feedback resistor Rfb is programmable between 20 K $\Omega$  and 1 M $\Omega$  through a configuration register. Table 8-4 shows the possible values of Rfb and associated configuration settings.

## Table 8-4. Feedback Resistor Settings

| Configuration Word | Nominal R <sub>fb</sub> (KΩ) |

|--------------------|------------------------------|

| 000b               | 20                           |

| 001b               | 30                           |

| 010b               | 40                           |

| 011b               | 60                           |

| 100b               | 120                          |

| 101b               | 250                          |

| 110b               | 500                          |

| 111b               | 1000                         |

## Figure 8-9. Continuous Time TIA Schematic

The TIA configuration is used for applications where an external sensor's output is current as a function of some type of stimulus such as temperature, light, magnetic flux etc. In a common application, the voltage DAC output can be connected to the  $V_{REF}$  TIA input to allow calibration of the external sensor bias current by adjusting the voltage DAC output voltage.

# 8.6 LCD Direct Drive

The PSoC Liquid Crystal Display (LCD) driver system is a highly configurable peripheral designed to allow PSoC to directly drive a broad range of LCD glass. All voltages are generated on chip, eliminating the need for external components. With a high multiplex ratio of up to 1/16, the CY8C34 family LCD driver system can drive a maximum of 736 segments. The PSoC LCD driver module was also designed with the conservative power budget of portable devices in mind, enabling different LCD drive modes and power down modes to conserve power.

PSoC Creator provides an LCD segment drive component. The component wizard provides easy and flexible configuration of LCD resources. You can specify pins for segments and commons along with other options. The software configures the device to meet the required specifications. This is possible because of the programmability inherent to PSoC devices.

Key features of the PSoC LCD segment system are:

- LCD panel direct driving

- Type A (standard) and Type B (low-power) waveform support

- Wide operating voltage range support (2 V to 5 V) for LCD panels

- Static, 1/2, 1/3, 1/4, 1/5 bias voltage levels

- Internal bias voltage generation through internal resistor ladder

- Up to 62 total common and segment outputs

- Up to 1/16 multiplex for a maximum of 16 backplane/common outputs

- Up to 62 front plane/segment outputs for direct drive

- Drives up to 736 total segments (16 backplane × 46 front plane)

- Up to 64 levels of software controlled contrast

- Ability to move display data from memory buffer to LCD driver through DMA (without CPU intervention)

- Adjustable LCD refresh rate from 10 Hz to 150 Hz

- Ability to invert LCD display for negative image

- Three LCD driver drive modes, allowing power optimization

# 8.6.1 LCD Segment Pin Driver

Each GPIO pin contains an LCD driver circuit. The LCD driver buffers the appropriate output of the LCD DAC to directly drive the glass of the LCD. A register setting determines whether the pin is a common or segment. The pin's LCD driver then selects one of the six bias voltages to drive the I/O pin, as appropriate for the display data.

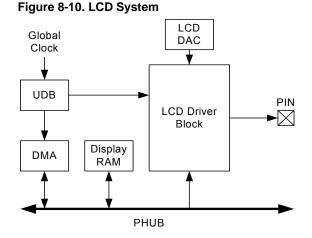

## 8.6.2 Display Data Flow

The LCD segment driver system reads display data and generates the proper output voltages to the LCD glass to produce the desired image. Display data resides in a memory buffer in the system SRAM. Each time you need to change the common and segment driver voltages, the next set of pixel data moves from the memory buffer into the Port Data Registers via DMA.

## 8.6.3 UDB and LCD Segment Control

A UDB is configured to generate the global LCD control signals and clocking. This set of signals is routed to each LCD pin driver through a set of dedicated LCD global routing channels. In addition to generating the global LCD control signals, the UDB also produces a DMA request to initiate the transfer of the next frame of LCD data.

## 8.6.4 LCD DAC

The LCD DAC generates the contrast control and bias voltage for the LCD system. The LCD DAC produces up to five LCD drive voltages plus ground, based on the selected bias ratio. The bias voltages are driven out to GPIO pins on a dedicated LCD bias bus, as required.

# **11.2 Device Level Specifications**

Specifications are valid for -40  $^{\circ}C \le T_A \le 85 ^{\circ}C$  and  $T_J \le 100 ^{\circ}C$ , except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted.

11.2.1 Device Level Specifications

# Table 11-2. DC Specifications

| Parameter                                                          | Description                                                              | Conditions                                                     |                        | Min  | <b>Typ</b> <sup>[25]</sup> | Max                                    | Units |

|--------------------------------------------------------------------|--------------------------------------------------------------------------|----------------------------------------------------------------|------------------------|------|----------------------------|----------------------------------------|-------|

| V <sub>DDA</sub>                                                   | Analog supply voltage and input to analog core regulator                 | Analog core regulat                                            | or enabled             | 1.8  | -                          | 5.5                                    | V     |

| V <sub>DDA</sub>                                                   | Analog supply voltage, analog regulator bypassed                         | Analog core regulat                                            | or disabled            | 1.71 | 1.8                        | 1.89                                   | V     |

| V <sub>DDD</sub>                                                   | Digital supply voltage relative to V <sub>SSD</sub>                      | Digital core regulate                                          | or enabled             | 1.8  | -                          | V <sub>DDA</sub> <sup>[21]</sup>       | V     |

| • 000                                                              |                                                                          |                                                                |                        | -    | -                          | V <sub>DDA</sub> + 0.1 <sup>[27]</sup> | v     |

| V <sub>DDD</sub>                                                   | Digital supply voltage, digital regulator bypassed                       | Digital core regulate                                          | 1.71                   | 1.8  | 1.89                       | V                                      |       |

| V <sub>DDI0</sub> [22]                                             | I/O supply voltage relative to V <sub>SSIO</sub>                         |                                                                |                        | 1.71 | -                          | V <sub>DDA</sub> <sup>[21]</sup>       | V     |

|                                                                    |                                                                          |                                                                |                        | _    | -                          | V <sub>DDA</sub> + 0.1 <sup>[27]</sup> | •     |

| V <sub>CCA</sub>                                                   | Direct analog core voltage input (Analog regulator bypass)               | Analog core regulat                                            | or disabled            | 1.71 | 1.8                        | 1.89                                   | V     |

| V <sub>CCD</sub>                                                   | Direct digital core voltage input (Digital regulator bypass)             | Digital core regulate                                          | 1.71                   | 1.8  | 1.89                       | V                                      |       |

|                                                                    | Active Mode                                                              |                                                                |                        |      |                            |                                        |       |

| Active Mode Only IMO and CPU cloc executing simple loop fr buffer. | Only IMO and CPU clock enabled. CPU                                      | $V_{DDX} = 2.7 V - 5.5 V;$<br>$F_{CPU} = 6 \text{ MHz}^{[26]}$ | T = -40 °C             | -    | 1.2                        | 2.9                                    |       |

|                                                                    | executing simple loop from instruction                                   |                                                                | T = 25 °C              | -    | 1.2                        | 3.1                                    |       |

|                                                                    | buller.                                                                  |                                                                | T = 85 °C              | -    | 4.9                        | 7.7                                    | _     |

|                                                                    |                                                                          | V <sub>DDX</sub> = 2.7 V –                                     | T = -40 °C             | -    | 1.3                        | 2.9                                    |       |

|                                                                    |                                                                          | 5.5 V;<br>F <sub>CPU</sub> = 3 MHz <sup>[26]</sup>             | T = 25 °C              | -    | 1.6                        | 3.2                                    |       |

|                                                                    |                                                                          |                                                                | T = 85 °C              | _    | 4.8                        | 7.5                                    |       |

|                                                                    |                                                                          | V <sub>DDX</sub> = 2.7 V –<br>5.5 V;                           | T = -40 °C             | _    | 2.1                        | 3.7                                    |       |

| I <sub>DD</sub> <sup>[23, 24]</sup>                                |                                                                          | F <sub>CPU</sub> = 6 MHz                                       | T = 25 °C<br>T = 85 °C | -    | 2.3                        | 3.9                                    |       |

| DD [, ]                                                            |                                                                          | V <sub>DDX</sub> = 2.7 V –                                     | T = -40 °C             |      | 5.6<br>3.5                 | 8.5<br>5.2                             | mA    |

|                                                                    | IMO enabled, bus clock and CPU clock enabled. CPU executing program from | 5.5 V;                                                         | T = 25 °C              |      | 3.8                        | 5.5                                    |       |

|                                                                    | flash.                                                                   | F <sub>CPU</sub> = 12 MHz <sup>[26]</sup>                      | T = 85 °C              | _    | 7.1                        | 9.8                                    |       |

|                                                                    |                                                                          | V <sub>DDX</sub> = 2.7 V –                                     | T = -40 °C             | _    | 6.3                        | 8.1                                    |       |

|                                                                    |                                                                          | 5.5 V;                                                         | T = 25 °C              | _    | 6.6                        | 8.3                                    | -     |

|                                                                    |                                                                          | F <sub>CPU</sub> = 24 MHz <sup>[26]</sup>                      | T = 85 °C              | _    | 10                         | 13                                     |       |

|                                                                    |                                                                          | V <sub>DDX</sub> = 2.7 V –                                     | T = -40 °C             | _    | 11.5                       | 13.5                                   |       |

|                                                                    |                                                                          | 5.5 V;                                                         | T = 25 °C              | _    | 12                         | 14                                     |       |

|                                                                    |                                                                          | F <sub>CPU</sub> = 48 MHz <sup>[26]</sup>                      | T = 85 °C              | _    | 15.5                       | 18.5                                   |       |

Notes

21. The power supplies can be brought up in any sequence however once stable V<sub>DDA</sub> must be greater than or equal to all other supplies.

22. The V<sub>DDIO</sub> supply voltage must be greater than the maximum voltage on the associated GPIO pins. Maximum voltage on GPIO pin ≤ V<sub>DDIO</sub> ≤ V<sub>DDA</sub>.

23. Total current for all power domains: digital (I<sub>DDD</sub>), analog (I<sub>DDA</sub>), and I/Os (I<sub>DDIO0,1,2,3</sub>). Boost not included. All I/Os floating.

24. The current consumption of additional peripherals that are implemented only in programmed logic blocks can be found in their respective datasheets, available in PSoC Creator, the integrated design environment. To estimate total current, find the CPU current at the frequency of interest and add peripheral currents for your next integrated design environment. particular system from the device datasheet and component datasheets. 25.  $V_{DDX} = 3.3 V$ .

26. Based on device characterization (Not Production tested).

27. Guaranteed by design, not production tested.

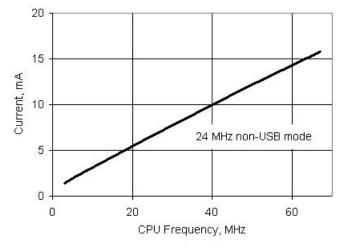

Figure 11-1. Active Mode Current vs  $F_{CPU}$ ,  $V_{DD}$  = 3.3 V, Temperature = 25 °C

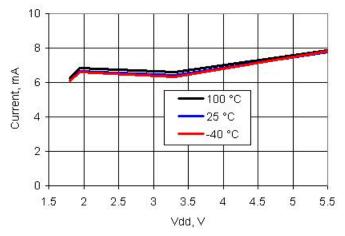

Figure 11-3. Active Mode Current vs V<sub>DD</sub> and Temperature, F<sub>CPU</sub> = 24 MHz

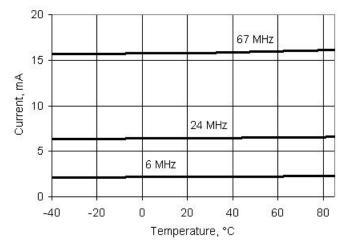

Figure 11-2. Active Mode Current vs Temperature and F<sub>CPU</sub>,  $V_{DD} = 3.3 V$

#### Notes

28. If V<sub>CCD</sub> and V<sub>CCA</sub> are externally regulated, the voltage difference between V<sub>CCD</sub> and V<sub>CCA</sub> must be less than 50 mV.

29. Sleep timer generates periodic interrupts to wake up the CPU. This specification applies only to those times that the CPU is off.

30. Externally regulated mode.

- 31. Based on device characterization (not production tested).

- 32. Based on device characterization (not production tested). USBIO pins tied to ground (VSSD).

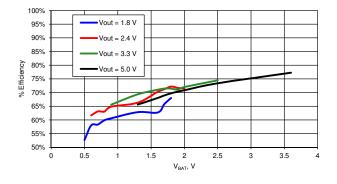

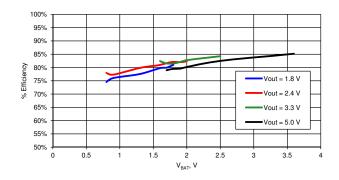

# Figure 11-11. Efficiency vs V<sub>BAT</sub>, $L_{BOOST}$ = 4.7 $\mu$ H <sup>[38]</sup>

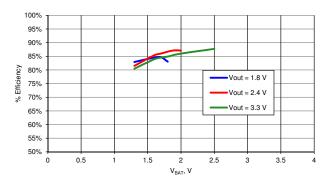

Figure 11-13. Efficiency vs  $V_{BAT}$ ,  $L_{BOOST}$  = 22  $\mu$ H <sup>[38]</sup>

Figure 11-12. Efficiency vs  $V_{BAT}$ ,  $L_{BOOST}$  = 10  $\mu$ H <sup>[38]</sup>

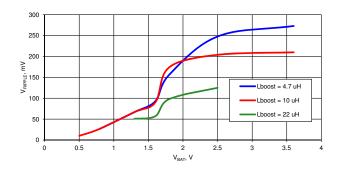

Figure 11-14. V<sub>RIPPLE</sub> vs V<sub>BAT</sub> <sup>[38]</sup>

#### Note

38. Typical example. Actual values may vary depending on external component selection, PCB layout, and other design parameters.

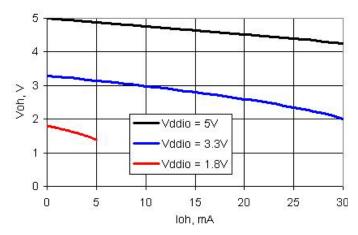

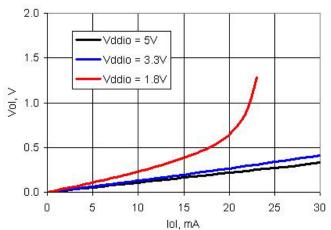

Figure 11-17. SIO Output High Voltage and Current, Unregulated Mode

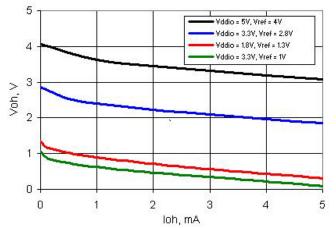

Figure 11-19. SIO Output High Voltage and Current, Regulated Mode

Table 11-12. SIO AC Specifications

| Parameter | Description                                            | Conditions                               | Min | Тур | Max | Units |

|-----------|--------------------------------------------------------|------------------------------------------|-----|-----|-----|-------|

| TriseF    | Rise time in Fast Strong Mode (90/10%) <sup>[44]</sup> | Cload = 25 pF, V <sub>DDIO</sub> = 3.3 V | -   | -   | 12  | ns    |

| TfallF    | Fall time in Fast Strong Mode (90/10%) <sup>[44]</sup> | Cload = 25 pF, V <sub>DDIO</sub> = 3.3 V | -   | -   | 12  | ns    |

| TriseS    | Rise time in Slow Strong Mode (90/10%) <sup>[44]</sup> | Cload = 25 pF, V <sub>DDIO</sub> = 3.0 V | -   | -   | 75  | ns    |

| TfallS    | Fall time in Slow Strong Mode (90/10%) <sup>[44]</sup> | Cload = 25 pF, V <sub>DDIO</sub> = 3.0 V | _   | _   | 60  | ns    |

# Table 11-12. SIO AC Specifications (continued)

| Parameter         | Description                                                                                        | Conditions                               | Min | Тур | Max | Units |

|-------------------|----------------------------------------------------------------------------------------------------|------------------------------------------|-----|-----|-----|-------|

|                   | SIO output operating frequency                                                                     |                                          |     |     |     |       |

|                   | 2.7 V < V <sub>DDIO</sub> < 5.5 V, Unregulated<br>output (GPIO) mode, fast strong<br>drive mode    | 90/10% V <sub>DDIO</sub> into 25 pF      | _   | -   | 33  | MHz   |

|                   | 1.71 V < V <sub>DDIO</sub> < 2.7 V, Unregu-<br>lated output (GPIO) mode, fast<br>strong drive mode | 90/10% V <sub>DDIO</sub> into 25 pF      | _   | -   | 16  | MHz   |

| Enioquit          | 3.3 V < V <sub>DDIO</sub> < 5.5 V, Unregulated<br>output (GPIO) mode, slow strong<br>drive mode    | 90/10% V <sub>DDIO</sub> into 25 pF      | _   | -   | 5   | MHz   |

| FSIOOUL           | 1.71 V < V <sub>DDIO</sub> < 3.3 V, Unregu-<br>lated output (GPIO) mode, slow<br>strong drive mode | 90/10% V <sub>DDIO</sub> into 25 pF      | -   | -   | 4   | MHz   |

|                   | 2.7 V < V <sub>DDIO</sub> < 5.5 V, Regulated output mode, fast strong drive mode                   | Output continuously switching into 25 pF | -   | -   | 20  | MHz   |

|                   | 1.71 V < V <sub>DDIO</sub> < 2.7 V, Regulated output mode, fast strong drive mode                  | Output continuously switching into 25 pF | -   | -   | 10  | MHz   |

|                   | 1.71 V < V <sub>DDIO</sub> < 5.5 V, Regulated<br>output mode, slow strong drive<br>mode            | Output continuously switching into 25 pF | -   | -   | 2.5 | MHz   |

| Fsioout<br>Fsioin | SIO input operating frequency                                                                      | •                                        | •   | · · |     |       |

|                   | 1.71 V <u>≤</u> V <sub>DDIO</sub> <u>≤</u> 5.5 V                                                   | 90/10% V <sub>DDIO</sub>                 | -   | -   | 33  | MHz   |

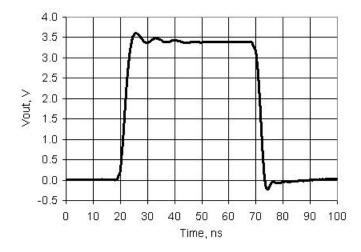

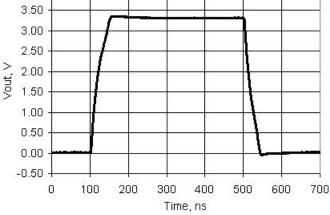

# Figure 11-20. SIO Output Rise and Fall Times, Fast Strong Mode, $V_{DDIO}$ = 3.3 V, 25 pF Load

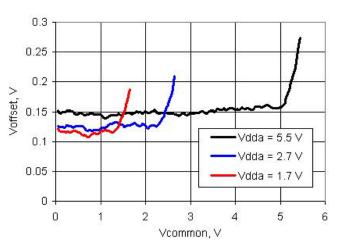

Figure 11-27. Opamp Voffset vs Vcommon and V<sub>DDA</sub>, 25 °C

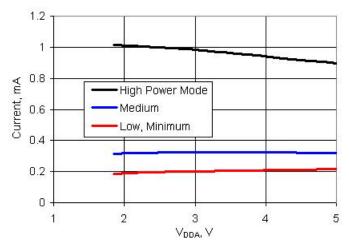

Figure 11-29. Opamp Operating Current vs  $V_{\mbox{\scriptsize DDA}}$  and Power Mode

Table 11-20. Opamp AC Specifications

| Parameter      | Description            | Conditions                                               | Min | Тур | Max | Units     |

|----------------|------------------------|----------------------------------------------------------|-----|-----|-----|-----------|

| GBW            | Gain-bandwidth product | Power mode = minimum, 15 pF load                         | 1   | -   | -   | MHz       |

|                |                        | Power mode = low, 15 pF load                             | 2   | -   | -   | MHz       |

|                |                        | Power mode = medium, 200 pF load                         | 1   | -   | -   | MHz       |

|                |                        | Power mode = high, 200 pF load                           | 3   | -   | -   | MHz       |

| SR             | Slew rate, 20% - 80%   | Power mode = low, 15 pF load                             | 1.1 | -   | -   | V/µs      |

|                |                        | Power mode = medium, 200 pF load                         | 0.9 | -   | -   | V/µs      |

|                |                        | Power mode = high, 200 pF load                           | 3   | -   | -   | V/µs      |

| e <sub>n</sub> | Input noise density    | Power mode = high, V <sub>DDA</sub> = 5 V,<br>at 100 kHz | _   | 45  | -   | nV/sqrtHz |

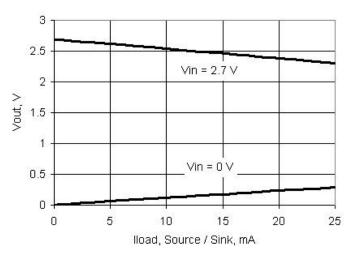

Figure 11-28. Opamp Output Voltage vs Load Current and Temperature, High Power Mode, 25 °C,  $V_{DDA}$  = 2.7 V

# 11.5.3 Voltage Reference

# Table 11-24. Voltage Reference Specifications

See also ADC external reference specifications in Section 11.5.2.

| Parameter        | Description                 | Conditions              | Min   | Тур   | Max   | Units |

|------------------|-----------------------------|-------------------------|-------|-------|-------|-------|

| V <sub>REF</sub> | Precision reference voltage | Initial trimming, 25 °C | 1.014 | 1.024 | 1.034 | V     |

|                  |                             |                         | (–1%) |       | (+1%) |       |

## 11.5.4 Analog Globals

# Table 11-25. Analog Globals Specifications

| Parameter | Description                                                                        | Conditions             | Min | Тур  | Max  | Units |

|-----------|------------------------------------------------------------------------------------|------------------------|-----|------|------|-------|

| Rppag     | Resistance pin-to-pin through P2[4],<br>AGL0, DSM INP, AGL1, P2[5] <sup>[52]</sup> | V <sub>DDA</sub> = 3 V | _   | 1472 | 2200 | Ω     |

| Rppmuxbus | Resistance pin-to-pin through P2[3], amuxbusL, P2[4] <sup>[52]</sup>               | V <sub>DDA</sub> = 3 V | _   | 706  | 1100 | Ω     |

# 11.5.5 Comparator

# Table 11-26. Comparator DC Specifications

| Parameter         | Description                                       | Conditions                                          | Min              | Тур | Max                        | Units |

|-------------------|---------------------------------------------------|-----------------------------------------------------|------------------|-----|----------------------------|-------|

|                   | Input offset voltage in fast mode                 | Factory trim, $V_{DDA}$ > 2.7 V, $V_{IN} \ge 0.5 V$ | -                |     | 10                         | mV    |

|                   | Input offset voltage in slow mode                 | Factory trim, Vin $\ge 0.5 \text{ V}$               | -                |     | 9                          | mV    |

| V <sub>OS</sub>   | Input offset voltage in fast mode <sup>[53]</sup> | Custom trim                                         | -                | -   | 4                          | mV    |

|                   | Input offset voltage in slow mode <sup>[53]</sup> | Custom trim                                         | -                | _   | 4                          | mV    |

|                   | Input offset voltage in ultra<br>low-power mode   | V <sub>DDA</sub> ≤ 4.6 V                            | -                | ±12 | -                          | mV    |

| V <sub>HYST</sub> | Hysteresis                                        | Hysteresis enable mode                              | -                | 10  | 32                         | mV    |

| V <sub>ICM</sub>  | Input common mode voltage                         | High current / fast mode                            | V <sub>SSA</sub> | -   | V <sub>DDA</sub>           | V     |

|                   |                                                   | Low current / slow mode                             | V <sub>SSA</sub> | -   | V <sub>DDA</sub>           | V     |

|                   |                                                   | Ultra low power mode<br>V <sub>DDA</sub> ≤ 4.6 V    | V <sub>SSA</sub> | -   | V <sub>DDA</sub> –<br>1.15 |       |

| CMRR              | Common mode rejection ratio                       |                                                     | -                | 50  | _                          | dB    |

| I <sub>CMP</sub>  | High current mode/fast mode <sup>[54]</sup>       |                                                     | -                | _   | 400                        | μA    |

|                   | Low current mode/slow mode <sup>[54]</sup>        |                                                     | -                | -   | 100                        | μA    |

|                   | Ultra low-power mode <sup>[54]</sup>              | V <sub>DDA</sub> ≤ 4.6 V                            | -                | 6   | _                          | μA    |

## Table 11-27. Comparator AC Specifications

| Parameter         | Description                                      | Conditions                                                        | Min | Тур | Max | Units |

|-------------------|--------------------------------------------------|-------------------------------------------------------------------|-----|-----|-----|-------|

| T <sub>RESP</sub> | Response time, high current mode <sup>[54]</sup> | 50 mV overdrive, measured<br>pin-to-pin                           | -   | 75  | 110 | ns    |

|                   | Response time, low current mode <sup>[54]</sup>  | 50 mV overdrive, measured pin-to-pin                              | -   | 155 | 200 | ns    |

|                   |                                                  | 50 mV overdrive, measured<br>pin-to-pin, V <sub>DDA</sub> ≤ 4.6 V | -   | 55  | _   | μs    |

#### Notes

53. The recommended procedure for using a custom trim value for the on-chip comparators can be found in the TRM.

54. Based on device characterization (Not production tested).

<sup>52.</sup> The resistance of the analog global and analog mux bus is high if V<sub>DDA</sub> ≤ 2.7 V, and the chip is in either sleep or hibernate mode. Use of analog global and analog mux bus under these conditions is not recommended.

# 11.5.6 Current Digital-to-analog Converter (IDAC)

All specifications are based on use of the low-resistance IDAC output pins (see Pin Descriptions on page 11 for details). See the IDAC component data sheet in PSoC Creator for full electrical specifications and APIs.

Unless otherwise specified, all charts and graphs show typical values.

# Table 11-28. IDAC DC Specifications

| Parameter        | Description                          | Conditions                                                                                                                          | Min | Тур    | Max  | Units  |

|------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----|--------|------|--------|

|                  | Resolution                           |                                                                                                                                     | _   | -      | 8    | bits   |

| I <sub>OUT</sub> | Output current at code = 255         | $\begin{array}{l} \mbox{Range = 2.04 mA, code = 255,} \\ \mbox{V}_{\mbox{DDA}} \geq 2.7 \mbox{ V, Rload = 600 } \Omega \end{array}$ | _   | 2.04   | -    | mA     |

|                  |                                      | Range = 2.04 mA, high speed mode, code = 255, $V_{DDA} \le 2.7$ V, Rload = 300 $\Omega$                                             | -   | 2.04   | -    | mA     |

|                  |                                      | Range = 255 $\mu$ A, code = 255, Rload<br>= 600 $\Omega$                                                                            | _   | 255    | _    | μA     |

|                  |                                      | Range = 31.875 $\mu$ A, code = 255,<br>Rload = 600 $\Omega$                                                                         | -   | 31.875 | _    | μA     |

|                  | Monotonicity                         |                                                                                                                                     | _   | -      | Yes  |        |

| Ezs              | Zero scale error                     |                                                                                                                                     | _   | 0      | ±1   | LSB    |

| Eg               | Gain error                           | Range = 2.04 mA, 25 °C                                                                                                              | _   | -      | ±2.5 | %      |

|                  |                                      | Range = 255 µA, 25 ° C                                                                                                              | _   | -      | ±2.5 | %      |

|                  |                                      | Range = 31.875 µA, 25 ° C                                                                                                           | _   | -      | ±3.5 | %      |

| TC_Eg            | Temperature coefficient of gain      | Range = 2.04 mA                                                                                                                     | _   | -      | 0.04 | % / °C |

|                  | error                                | Range = 255 µA                                                                                                                      | _   | -      | 0.04 | % / °C |

|                  |                                      | Range = 31.875 µA                                                                                                                   | _   | -      | 0.05 | % / °C |

| INL              | Integral nonlinearity                | Sink mode, range = 255 $\mu$ A, Codes<br>8 – 255, Rload = 2.4 k $\Omega$ , Cload =<br>15 pF                                         | _   | ±0.9   | ±1   | LSB    |

|                  |                                      | Source mode, range = 255 $\mu$ A,<br>Codes 8 – 255, Rload = 2.4 k $\Omega$ ,<br>Cload = 15 pF                                       | -   | ±1.2   | ±1.6 | LSB    |

| DNL              | Differential nonlinearity            | Sink mode, range = 255 $\mu$ A, Rload<br>= 2.4 k $\Omega$ , Cload = 15 pF                                                           | -   | ±0.3   | ±1   | LSB    |

|                  |                                      | Source mode, range = 255 $\mu$ A,<br>Rload = 2.4 k $\Omega$ , Cload = 15 pF                                                         | _   | ±0.3   | ±1   | LSB    |

| Vcompliance      | Dropout voltage, source or sink mode | Voltage headroom at max current, $R_{LOAD}$ to $V_{DDA}$ or $R_{LOAD}$ to $V_{SSA},$ $V_{DIFF}$ from $V_{DDA}$                      | 1   | -      | -    | V      |

# 11.5.8 Mixer

The mixer is created using a SC/CT analog block; see the Mixer component data sheet in PSoC Creator for full electrical specifications and APIs.

# Table 11-32. Mixer DC Specifications

| Parameter       | Description          | Conditions | Min | Тур | Max | Units |

|-----------------|----------------------|------------|-----|-----|-----|-------|

| V <sub>OS</sub> | Input offset voltage |            | -   | -   | 15  | mV    |

|                 | Quiescent current    |            | -   | 0.9 | 2   | mA    |

| G               | Gain                 |            | -   | 0   | -   | dB    |

## Table 11-33. Mixer AC Specifications

| Parameter       | Description                | Conditions      | Min | Тур | Max | Units |

|-----------------|----------------------------|-----------------|-----|-----|-----|-------|

| f <sub>LO</sub> | Local oscillator frequency | Down mixer mode | -   | -   | 4   | MHz   |

| f <sub>in</sub> | Input signal frequency     | Down mixer mode | -   | -   | 14  | MHz   |

| f <sub>LO</sub> | Local oscillator frequency | Up mixer mode   | -   | -   | 1   | MHz   |

| f <sub>in</sub> | Input signal frequency     | Up mixer mode   | -   | -   | 1   | MHz   |

| SR              | Slew rate                  |                 | 3   | _   | -   | V/µs  |

## 11.5.9 Transimpedance Amplifier

The TIA is created using a SC/CT analog block; see the TIA component data sheet in PSoC Creator for full electrical specifications and APIs.

## Table 11-34. Transimpedance Amplifier (TIA) DC Specifications

| Parameter         | Description                           | Conditions           | Min | Тур | Max | Units |

|-------------------|---------------------------------------|----------------------|-----|-----|-----|-------|

| V <sub>IOFF</sub> | Input offset voltage                  |                      | -   | -   | 10  | mV    |

| Rconv             | Conversion resistance <sup>[56]</sup> | R = 20K; 40 pF load  | -25 | -   | +35 | %     |

|                   |                                       | R = 30K; 40 pF load  | -25 | -   | +35 | %     |

|                   |                                       | R = 40K; 40 pF load  | -25 | -   | +35 | %     |

|                   |                                       | R = 80K; 40 pF load  | -25 | -   | +35 | %     |

|                   |                                       | R = 120K; 40 pF load | -25 | -   | +35 | %     |

|                   |                                       | R = 250K; 40 pF load | -25 | -   | +35 | %     |

|                   |                                       | R= 500K; 40 pF load  | -25 | -   | +35 | %     |

|                   |                                       | R = 1M; 40 pF load   | -25 | -   | +35 | %     |

|                   | Quiescent current                     |                      | -   | 1.1 | 2   | mA    |

## Table 11-35. Transimpedance Amplifier (TIA) AC Specifications

| Parameter | Description             | Conditions            | Min  | Тур | Max | Units |

|-----------|-------------------------|-----------------------|------|-----|-----|-------|

| BW        | Input bandwidth (-3 dB) | R = 20K; –40 pF load  | 1500 | -   | -   | kHz   |

|           |                         |                       |      |     |     |       |

|           |                         | R = 120K; –40 pF load | 240  | -   | -   | kHz   |

|           |                         | R = 1M; –40 pF load   | 25   | -   | -   | kHz   |

Note

<sup>56.</sup> Conversion resistance values are not calibrated. Calibrated values and details about calibration are provided in PSoC Creator component data sheets. External precision resistors can also be used.

# **11.6 Digital Peripherals**

Specifications are valid for –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C and T<sub>J</sub>  $\leq$  100 °C, except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted.

# 11.6.1 Timer

The following specifications apply to the Timer/Counter/PWM peripheral in timer mode. Timers can also be implemented in UDBs; for more information, see the Timer component data sheet in PSoC Creator.

## Table 11-41. Timer DC Specifications

| Parameter | Description               | Conditions                                    | Min | Тур | Max | Units |

|-----------|---------------------------|-----------------------------------------------|-----|-----|-----|-------|

|           | Block current consumption | 16-bit timer, at listed input clock frequency | -   | _   | -   | μA    |

|           | 3 MHz                     |                                               | -   | 15  | -   | μA    |

|           | 12 MHz                    |                                               | -   | 60  | -   | μA    |

|           | 50 MHz                    |                                               | -   | 260 | -   | μA    |

## Table 11-42. Timer AC Specifications

| Parameter | Description                    | Conditions | Min | Тур | Max   | Units |

|-----------|--------------------------------|------------|-----|-----|-------|-------|

|           | Operating frequency            |            | DC  | -   | 50.01 | MHz   |

|           | Capture pulse width (Internal) |            | 21  | -   | -     | ns    |

|           | Capture pulse width (external) |            | 42  | -   | -     | ns    |

|           | Timer resolution               |            | 21  | -   | -     | ns    |

|           | Enable pulse width             |            | 21  | -   | -     | ns    |

|           | Enable pulse width (external)  |            | 42  | -   | -     | ns    |

|           | Reset pulse width              |            | 21  | -   | -     | ns    |

|           | Reset pulse width (external)   |            | 42  | -   | -     | ns    |

## 11.6.2 Counter

The following specifications apply to the Timer/Counter/PWM peripheral, in counter mode. Counters can also be implemented in UDBs; for more information, see the Counter component data sheet in PSoC Creator.

# Table 11-43. Counter DC Specifications

| Parameter | Description | Conditions                                         | Min | Тур | Max | Units |

|-----------|-------------|----------------------------------------------------|-----|-----|-----|-------|

|           | •           | 16–bit counter, at listed input clock<br>frequency | -   | -   | -   | μA    |

|           | 3 MHz       |                                                    | -   | 15  | -   | μA    |

|           | 12 MHz      |                                                    | -   | 60  | -   | μA    |

|           | 50 MHz      |                                                    | -   | 260 | -   | μA    |

## Table 11-44. Counter AC Specifications

| Parameter | Description                   | Conditions | Min | Тур | Max   | Units |

|-----------|-------------------------------|------------|-----|-----|-------|-------|

|           | Operating frequency           |            | DC  | -   | 50.01 | MHz   |

|           | Capture pulse                 |            | 21  | -   | -     | ns    |

|           | Resolution                    |            | 21  | -   | -     | ns    |

|           | Pulse width                   |            | 21  | -   | -     | ns    |

|           | Pulse width (external)        |            | 42  |     |       | ns    |

|           | Enable pulse width            |            | 21  | -   | -     | ns    |

|           | Enable pulse width (external) |            | 42  | -   | -     | ns    |

|           | Reset pulse width             |            | 21  | -   | -     | ns    |

|           | Reset pulse width (external)  |            | 42  | -   | -     | ns    |

# 11.7.2 EEPROM

# Table 11-55. EEPROM DC Specifications

| Parameter | Description               | Conditions | Min  | Тур | Max | Units |

|-----------|---------------------------|------------|------|-----|-----|-------|

|           | Erase and program voltage |            | 1.71 | -   | 5.5 | V     |

# Table 11-56. EEPROM AC Specifications

| Parameter          | Description                                                                 | Conditions                                                                  | Min | Тур | Max | Units |

|--------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----|-----|-----|-------|

| T <sub>WRITE</sub> | Single row erase/write cycle time                                           |                                                                             | _   | 10  | 20  | ms    |

|                    | EEPROM data retention time, retention period measured from last erase cycle | Average ambient temp, T <sub>A</sub> ≤ 25 °C,<br>1M erase/program cycles    | 20  | -   | -   | years |

|                    |                                                                             | Average ambient temp, T <sub>A</sub> ≤ 55 °C,<br>100 K erase/program cycles | 20  | -   | -   |       |

|                    |                                                                             | Average ambient temp.<br>$T_A \le 85$ °C, 10 K erase/program cycles         | 10  | -   | -   |       |

# 11.7.3 Nonvolatile Latches (NVL))

# Table 11-57. NVL DC Specifications

| Parameter | Description               | Conditions           | Min  | Тур | Max | Units |

|-----------|---------------------------|----------------------|------|-----|-----|-------|

|           | Erase and program voltage | V <sub>DDD</sub> pin | 1.71 | _   | 5.5 | V     |

## Table 11-58. NVL AC Specifications

| Parameter | Description             | Conditions                                   | Min | Тур | Max | Units                       |

|-----------|-------------------------|----------------------------------------------|-----|-----|-----|-----------------------------|

|           | NVL endurance           | Programmed at 25 °C                          | 1K  | -   | _   | program/<br>erase<br>cycles |

|           |                         | Programmed at 0 °C to 70 °C                  | 100 | -   | -   | program/<br>erase<br>cycles |

|           | NVL data retention time | Average ambient temp. T <sub>A</sub> ≤ 55 °C | 20  | -   | -   | years                       |

|           |                         | Average ambient temp. T <sub>A</sub> ≤ 85 °C | 10  | -   | _   | years                       |

## 11.7.4 SRAM

# Table 11-59. SRAM DC Specifications

| Parameter         | Description            | Conditions | Min | Тур | Max | Units |

|-------------------|------------------------|------------|-----|-----|-----|-------|

| V <sub>SRAM</sub> | SRAM retention voltage |            | 1.2 | -   | -   | V     |

# Table 11-60. SRAM AC Specifications

| Parameter         | Description              | Conditions | Min | Тур | Max   | Units |

|-------------------|--------------------------|------------|-----|-----|-------|-------|

| F <sub>SRAM</sub> | SRAM operating frequency |            | DC  | _   | 50.01 | MHz   |