Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                    |

| Core Processor             | 8051                                                                        |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 50MHz                                                                       |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART                  |

| Peripherals                | CapSense, DMA, LCD, POR, PWM, WDT                                           |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 64KB (64K x 8)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 2K x 8                                                                      |

| RAM Size                   | 8K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                                |

| Data Converters            | A/D 16x12b; D/A 2x8b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 48-BSSOP (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 48-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c3446pvi-102t |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Contents**

| 1. | Architectural Overview                                                                                                                                                                                  | 4                                                  |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 2. | Pinouts                                                                                                                                                                                                 | 6                                                  |

| 3. | Pin Descriptions                                                                                                                                                                                        | 11                                                 |

|    | 4.1 8051 CPU                                                                                                                                                                                            | 12<br>12<br>12<br>13<br>17                         |

| 5. | Memory                                                                                                                                                                                                  | 22                                                 |

|    | 5.1 Static RAM 5.2 Flash Program Memory 5.3 Flash Security 5.4 EEPROM 5.5 Nonvolatile Latches (NVLs) 5.6 External Memory Interface 5.7 Memory Map                                                       | 22<br>22<br>22<br>22<br>23<br>24                   |

| 6. | System Integration                                                                                                                                                                                      |                                                    |

|    | 6.1 Clocking System                                                                                                                                                                                     | 27<br>30<br>34                                     |

| 7. | Digital Subsystem                                                                                                                                                                                       |                                                    |

|    | 7.1 Example Peripherals 7.2 Universal Digital Block 7.3 UDB Array Description 7.4 DSI Routing Interface Description 7.5 CAN 7.6 USB 7.7 Timers, Counters, and PWMs 7.8 I <sup>2</sup> C                 | 43<br>45<br>48<br>49<br>50<br>52<br>53             |

| 0  |                                                                                                                                                                                                         |                                                    |

| 8. | Analog Subsystem  8.1 Analog Routing  8.2 Delta-sigma ADC  8.3 Comparators  8.4 Opamps  8.5 Programmable SC/CT Blocks  8.6 LCD Direct Drive  8.7 CapSense  8.8 Temp Sensor  8.9 DAC  8.10 Up/Down Mixer | 57<br>59<br>60<br>61<br>61<br>63<br>64<br>64<br>64 |

|    | 8.11 Sample and Hold                                                                                                                                                                                    |                                                    |

| 9. | Programming, Debug Interfaces, Resources   |      |

|----|--------------------------------------------|------|

|    | 9.1 JTAG Interface                         | . 66 |

|    | 9.2 Serial Wire Debug Interface            |      |

|    | 9.3 Debug Features                         |      |

|    | 9.4 Trace Features                         |      |

|    | 9.5 Single Wire Viewer Interface           |      |

|    | 9.6 Programming Features                   |      |

|    | 9.7 Device Security                        |      |

| 10 | . Development Support                      |      |

|    | 10.1 Documentation                         |      |

|    | 10.2 Online                                |      |

|    | 10.3 Tools                                 |      |

| 11 | . Electrical Specifications                | . 70 |

|    | 11.1 Absolute Maximum Ratings              |      |

|    | 11.2 Device Level Specifications           |      |

|    | 11.3 Power Regulators                      |      |

|    | 11.4 Inputs and Outputs                    |      |

|    | 11.5 Analog Peripherals                    |      |

|    | 11.6 Digital Peripherals                   |      |

|    | 11.7 Memory                                |      |

|    | 11.8 PSoC System Resources                 |      |

|    | 11.9 Clocking                              |      |

| 12 | . Ordering Information                     | 121  |

|    | 12.1 Part Numbering Conventions            | 122  |

| 13 | . Packaging                                | 123  |

| 14 | . Acronyms                                 | 126  |

| 15 | . Reference Documents                      | 127  |

| 16 | . Document Conventions                     | 128  |

|    | 16.1 Units of Measure                      |      |

| 17 | 7. Revision History                        | 129  |

| 18 | S. Sales, Solutions, and Legal Information | 137  |

|    | Worldwide Sales and Design Support         | 137  |

|    | Products                                   |      |

|    | PSoC® Solutions                            |      |

|    | Cypress Developer Community                | 137  |

|    | Technical Support                          | 137  |

In addition to the flexibility of the UDB array, PSoC also provides configurable digital blocks targeted at specific functions. For the CY8C34 family these blocks can include four 16-bit timer, counter, and PWM blocks; I<sup>2</sup>C slave, master, and multi-master; Full-Speed USB; and Full CAN 2.0b.

For more details on the peripherals see the "Example Peripherals" section on page 43 of this data sheet. For information on UDBs, DSI, and other digital blocks, see the "Digital Subsystem" section on page 43 of this data sheet.

PSoC's analog subsystem is the second half of its unique configurability. All analog performance is based on a highly accurate absolute voltage reference with less than 1-percent error over temperature and voltage. The configurable analog subsystem includes:

- Analog muxes

- Comparators

- Voltage references

- Analog-to-digital converter (ADC)

- Digital-to-analog converters (DACs)

All GPIO pins can route analog signals into and out of the device using the internal analog bus. This allows the device to interface up to 62 discrete analog signals. The heart of the analog subsystem is a fast, accurate, configurable delta-sigma ADC with these features:

- Less than 100 µV offset

- A gain error of 0.2 percent

- INL less than ±1 LSB

- DNL less than ±1 LSB

- SINAD better than 66 dB

This converter addresses a wide variety of precision analog applications, including some of the most demanding sensors.

Two high-speed voltage or current DACs support 8-bit output signals at update rate of 8 Msps in current DAC (IDAC) and 1 Msps in voltage DAC (VDAC). They can be routed out of any GPIO pin. You can create higher resolution voltage PWM DAC outputs using the UDB array. This can be used to create a pulse width modulated (PWM) DAC of up to 10 bits, at up to 48 kHz. The digital DACs in each UDB support PWM, PRS, or delta-sigma algorithms with programmable widths.

In addition to the ADC and DACs, the analog subsystem provides multiple:

- Uncommitted opamps

- Configurable switched capacitor/continuous time (SC/CT) blocks. These support:

- Transimpedance amplifiers

- □ Programmable gain amplifiers

- Mixers

Other similar analog components

See the "Analog Subsystem" section on page 56 of this data sheet for more details.

PSoC's 8051 CPU subsystem is built around a single cycle pipelined 8051 8-bit processor running at up to 50 MHz. The CPU subsystem includes a programmable nested vector interrupt controller, DMA controller, and RAM. PSoC's nested vector interrupt controller provides low latency by allowing the CPU to vector directly to the first address of the interrupt service routine, bypassing the jump instruction required by other architectures. The DMA controller enables peripherals to exchange data without CPU involvement. This allows the CPU to run slower (saving power) or use those CPU cycles to improve the performance of firmware algorithms. The single cycle 8051 CPU runs ten times faster than a standard 8051 processor. The processor speed itself is configurable, allowing you to tune active power consumption for specific applications.

PSoC's nonvolatile subsystem consists of flash, byte-writeable EEPROM, and nonvolatile configuration options. It provides up to 64 KB of on-chip flash. The CPU can reprogram individual blocks of flash, enabling bootloaders. You can enable an error correcting code (ECC) for high reliability applications. A powerful and flexible protection model secures the user's sensitive information, allowing selective memory block locking for read and write protection. Up to 2 KB of byte-writeable EEPROM is available on-chip to store application data. Additionally, selected configuration options such as boot speed and pin drive mode are stored in nonvolatile memory. This allows settings to activate immediately after power-on reset (POR).

The three types of PSoC I/O are extremely flexible. All I/Os have many drive modes that are set at POR. PSoC also provides up to four I/O voltage domains through the VDDIO pins. Every GPIO has analog I/O, LCD drive  $^{[3]}$ , CapSense  $^{[4]}$ , flexible interrupt generation, slew rate control, and digital I/O capability. The SIOs on PSoC allow VOH to be set independently of VDDIO when used as outputs. When SIOs are in input mode they are high impedance. This is true even when the device is not powered or when the pin voltage goes above the supply voltage. This makes the SIO ideally suited for use on an I<sup>2</sup>C bus where the PSoC may not be powered when other devices on the bus are. The SIO pins also have high current sink capability for applications such as LED drives. The programmable input threshold feature of the SIO can be used to make the SIO function as a general purpose analog comparator. For devices with Full-Speed USB the USB physical interface is also provided (USBIO). When not using USB these pins may also be used for limited digital functionality and device programming. All of the features of the PSoC I/Os are covered in detail in the "I/O System and Routing" section on page 36 of this data sheet.

The PSoC device incorporates flexible internal clock generators, designed for high stability and factory trimmed for high accuracy. The Internal Main Oscillator (IMO) is the clock base for the system, and has 2-percent accuracy at 3 MHz. The IMO can be configured to run from 3 MHz up to 24 MHz. Multiple clock derivatives can be generated from the main clock frequency to meet application needs.

#### Notes

- 3. This feature on select devices only. See Ordering Information on page 121 for details.

- 4. GPIOs with opamp outputs are not recommended for use with CapSense.

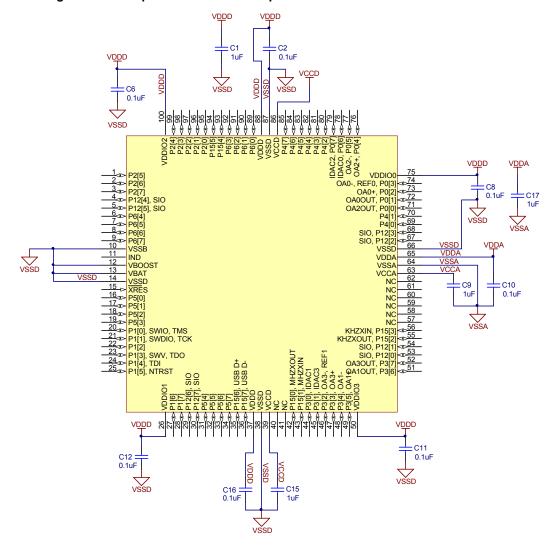

Figure 2-7 and Figure 2-8 on page 11 show an example schematic and an example PCB layout, for the 100-pin TQFP part, for optimal analog performance on a two-layer board.

- The two pins labeled VDDD must be connected together.

- The two pins labeled VCCD must be connected together, with capacitance added, as shown in Figure 2-7 and Power System on page 30. The trace between the two VCCD pins should be as short as possible.

- The two pins labeled VSSD must be connected together.

For information on circuit board layout issues for mixed signals, refer to the application note AN57821 - Mixed Signal Circuit Board Layout Considerations for PSoC® 3 and PSoC 5.

Figure 2-7. Example Schematic for 100-pin TQFP Part With Power Connections

**Note** The two VCCD pins must be connected together with as short a trace as possible. A trace under the device is recommended, as shown in Figure 2-8 on page 11.

For more information on pad layout, refer to http://www.cypress.com/cad-resources/psoc-3-cad-libraries.

#### 4.3 Instruction Set

The 8051 instruction set is highly optimized for 8-bit handling and Boolean operations. The types of instructions supported include:

- Arithmetic instructions

- Logical instructions

- Data transfer instructions

- Boolean instructions

- Program branching instructions

#### Table 4-1. Arithmetic Instructions

#### 4.3.1 Instruction Set Summary

#### 4.3.1.1 Arithmetic Instructions

Arithmetic instructions support the direct, indirect, register, immediate constant, and register-specific instructions.

Arithmetic modes are used for addition, subtraction, multiplication, division, increment, and decrement operations.

Table 4-1 lists the different arithmetic instructions.

| Mnemonic      | Description                                          | Bytes | Cycles |

|---------------|------------------------------------------------------|-------|--------|

| ADD A,Rn      | Add register to accumulator                          | 1     | 1      |

| ADD A,Direct  | Add direct byte to accumulator                       | 2     | 2      |

| ADD A,@Ri     | Add indirect RAM to accumulator                      | 1     | 2      |

| ADD A,#data   | Add immediate data to accumulator                    | 2     | 2      |

| ADDC A,Rn     | Add register to accumulator with carry               | 1     | 1      |

| ADDC A,Direct | Add direct byte to accumulator with carry            | 2     | 2      |

| ADDC A,@Ri    | Add indirect RAM to accumulator with carry           | 1     | 2      |

| ADDC A,#data  | Add immediate data to accumulator with carry         | 2     | 2      |

| SUBB A,Rn     | Subtract register from accumulator with borrow       | 1     | 1      |

| SUBB A,Direct | Subtract direct byte from accumulator with borrow    | 2     | 2      |

| SUBB A,@Ri    | Subtract indirect RAM from accumulator with borrow   | 1     | 2      |

| SUBB A,#data  | Subtract immediate data from accumulator with borrow | 2     | 2      |

| INC A         | Increment accumulator                                | 1     | 1      |

| INC Rn        | Increment register                                   | 1     | 2      |

| INC Direct    | Increment direct byte                                | 2     | 3      |

| INC @Ri       | Increment indirect RAM                               | 1     | 3      |

| DEC A         | Decrement accumulator                                | 1     | 1      |

| DEC Rn        | Decrement register                                   | 1     | 2      |

| DEC Direct    | Decrement direct byte                                | 2     | 3      |

| DEC @Ri       | Decrement indirect RAM                               | 1     | 3      |

| INC DPTR      | Increment data pointer                               | 1     | 1      |

| MUL           | Multiply accumulator and B                           | 1     | 2      |

| DIV           | Divide accumulator by B                              | 1     | 6      |

| DAA           | Decimal adjust accumulator                           | 1     | 3      |

Document Number: 001-53304 Rev. \*Y Page 13 of 137

#### 5. Memory

#### 5.1 Static RAM

CY8C34 Static RAM (SRAM) is used for temporary data storage. Up to 8 KB of SRAM is provided and can be accessed by the 8051 or the DMA controller. See Memory Map on page 25. Simultaneous access of SRAM by the 8051 and the DMA controller is possible if different 4-KB blocks are accessed.

#### 5.2 Flash Program Memory

Flash memory in PSoC devices provides nonvolatile storage for user firmware, user configuration data, bulk data storage, and optional ECC data. The main flash memory area contains up to 64 KB of user program space.

Up to an additional 8 KB of flash space is available for Error Correcting Codes (ECC). If ECC is not used this space can store device configuration data and bulk user data. User code may not be run out of the ECC flash memory section. ECC can correct one bit error and detect two bit errors per 8 bytes of firmware memory; an interrupt can be generated when an error is detected.

The CPU reads instructions located in flash through a cache controller. This improves instruction execution rate and reduces system power consumption by requiring less frequent flash access. The cache has 8 lines at 64 bytes per line for a total of 512 bytes. It is fully associative, automatically controls flash power, and can be enabled or disabled. If ECC is enabled, the cache controller also performs error checking and correction, and interrupt generation.

Flash programming is performed through a special interface and preempts code execution out of flash. The flash programming interface performs flash erasing, programming and setting code protection levels. Flash in-system serial programming (ISSP), typically used for production programming, is possible through both the SWD and JTAG interfaces. In-system programming, typically used for bootloaders, is also possible using serial interfaces such as I<sup>2</sup>C, USB, UART, and SPI, or any communications protocol.

#### 5.3 Flash Security

All PSoC devices include a flexible flash-protection model that prevents access and visibility to on-chip flash memory. This prevents duplication or reverse engineering of proprietary code. Flash memory is organized in blocks, where each block contains 256 bytes of program or data and 32 bytes of ECC or configuration data. A total of up to 256 blocks is provided on 64-KB flash devices.

The device offers the ability to assign one of four protection levels to each row of flash. Table 5-1 lists the protection modes available. Flash protection levels can only be changed by performing a complete flash erase. The Full Protection and Field Upgrade settings disable external access (through a debugging tool such as PSoC Creator, for example). If your application requires code update through a boot loader, then use the Field Upgrade setting. Use the Unprotected setting only when no security is needed in your application. The PSoC device also offers an advanced security feature called Device Security which permanently disables all test, programming, and debug ports, protecting your application from external access (see the

"Device Security" section on page 68). For more information about how to take full advantage of the security features in PSoC, see the PSoC 3 TRM.

Table 5-1. Flash Protection

| Protection<br>Setting | Allowed                                              | Not Allowed                              |

|-----------------------|------------------------------------------------------|------------------------------------------|

| Unprotected           | External read and write<br>+ internal read and write | -                                        |

| Factory<br>Upgrade    | External write + internal read and write             | External read                            |

| Field Upgrade         | Internal read and write                              | External read and write                  |

| Full Protection       | Internal read                                        | External read and write + internal write |

#### **Disclaimer**

Note the following details of the flash code protection features on Cypress devices.

Cypress products meet the specifications contained in their particular Cypress data sheets. Cypress believes that its family of products is one of the most secure families of its kind on the market today, regardless of how they are used. There may be methods, unknown to Cypress, that can breach the code protection features. Any of these methods, to our knowledge, would be dishonest and possibly illegal. Neither Cypress nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Cypress is willing to work with the customer who is concerned about the integrity of their code. Code protection is constantly evolving. We at Cypress are committed to continuously improving the code protection features of our products.

#### 5.4 EEPROM

PSoC EEPROM memory is a byte-addressable nonvolatile memory. The CY8C34 has up to 2 KB of EEPROM memory to store user data. Reads from EEPROM are random access at the byte level. Reads are done directly; writes are done by sending write commands to an EEPROM programming interface. CPU code execution can continue from flash during EEPROM writes. EEPROM is erasable and writeable at the row level. The EEPROM is divided into 128 rows of 16 bytes each. The factory default values of all EEPROM bytes are 0.

Because the EEPROM is mapped to the 8051 xdata space, the CPU cannot execute out of EEPROM. There is no ECC hardware associated with EEPROM. If ECC is required it must be handled in firmware.

It can take as much as 20 milliseconds to write to EEPROM or flash. During this time the device should not be reset, or unexpected changes may be made to portions of EEPROM or flash. Reset sources (see *Section 6.3.1*) include XRES pin, software reset, and watchdog; care should be taken to make sure that these are not inadvertently activated. In addition, the low voltage detect circuits should be configured to generate an interrupt instead of a reset.

#### 7.2.2 Datapath Module

The datapath contains an 8-bit single cycle ALU, with associated compare and condition generation logic. This datapath block is optimized to implement embedded functions, such as timers, counters, integrators, PWMs, PRS, CRC, shifters and dead band generators and many others.

PHUB System Bus R/W Access to All Registers F1 FIFOs Dynamic Configuration RAM Conditions: 2 Compares, 2 Zero Detect, 2 Ones Detect Overflow Detect Datapath Control Output Input F0 8 Word X 16 Bit Muxes Muxes A0 Input from Output to Programmable Α1 . Programmable Routing Routing 6 D0 D1 D1 Data Registers D0 To/From To/From Chaining Previous Next Datapath Datapath Α1 Accumulator A0 Parallel Input/Output (To/From Programmable Routing) PO -ALU Shift Mask

Figure 7-4. Datapath Top Level

#### 7.2.2.1 Working Registers

The datapath contains six primary working registers, which are accessed by CPU firmware or DMA during normal operation.

Table 7-1. Working Datapath Registers

| Name      | Function       | Description                                                                                                                                                                                               |

|-----------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0 and A1 | Accumulators   | These are sources and sinks for the ALU and also sources for the compares.                                                                                                                                |

| D0 and D1 | Data Registers | These are sources for the ALU and sources for the compares.                                                                                                                                               |

| F0 and F1 | FIFOs          | These are the primary interface to the system bus. They can be a data source for the data registers and accumulators or they can capture data from the accumulators or ALU. Each FIFO is four bytes deep. |

#### 7.2.2.2 Dynamic Configuration RAM

Dynamic configuration is the ability to change the datapath function and internal configuration on a cycle-by-cycle basis, under sequencer control. This is implemented using the 8-word × 16-bit configuration RAM, which stores eight unique 16-bit wide configurations. The address input to this RAM controls the sequence, and can be routed from any block connected to the UDB routing matrix, most typically PLD logic, I/O pins, or from the outputs of this or other datapath blocks.

#### ALU

The ALU performs eight general purpose functions. They are:

- Increment

- Decrement

- Add

- Subtract

- Logical AND

Document Number: 001-53304 Rev. \*Y Page 46 of 137

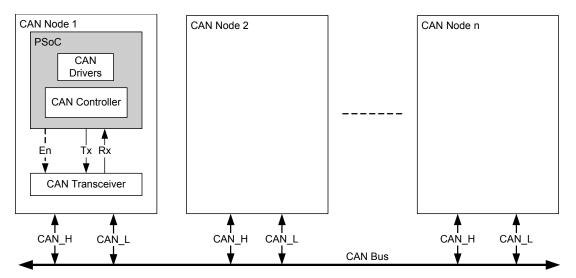

Figure 7-14. CAN Bus System Implementation

#### 7.5.1 CAN Features

- CAN2.0A/B protocol implementation ISO 11898 compliant

- Standard and extended frames with up to 8 bytes of data per frame

- Message filter capabilities

- Remote Transmission Request (RTR) support

- □ Programmable bit rate up to 1 Mbps

- Listen Only mode

- SW readable error counter and indicator

- Sleep mode: Wake the device from sleep with activity on the Rx pin

- Supports two or three wire interface to external transceiver (Tx, Rx, and Enable). The three-wire interface is compatible with the Philips PHY; the PHY is not included on-chip. The three wires can be routed to any I/O

- Enhanced interrupt controller

- □ CAN receive and transmit buffers status

- □ CAN controller error status including BusOff

- Receive path

- □ 16 receive buffers each with its own message filter

- □ Enhanced hardware message filter implementation that covers the ID, IDE and RTR

- DeviceNet addressing support

- Multiple receive buffers linkable to build a larger receive message array

- □ Automatic transmission request (RTR) response handler

- □ Lost received message notification

- Transmit path

- □ Eight transmit buffers

- □ Programmable transmit priority

- Round robin

- · Fixed priority

- Message transmissions abort capability

#### 7.5.2 Software Tools Support

CAN Controller configuration integrated into PSoC Creator:

- CAN Configuration walkthrough with bit timing analyzer

- Receive filter setup

#### 8.7 CapSense

The CapSense system provides a versatile and efficient means for measuring capacitance in applications such as touch sense buttons, sliders, proximity detection, etc. The CapSense system uses a configuration of system resources, including a few hardware functions primarily targeted for CapSense. Specific resource usage is detailed in the CapSense component in PSoC Creator

A capacitive sensing method using a delta-sigma modulator (CSD) is used. It provides capacitance sensing using a switched capacitor technique with a delta-sigma modulator to convert the sensing current to a digital code.

#### 8.8 Temp Sensor

Die temperature is used to establish programming parameters for writing flash. Die temperature is measured using a dedicated sensor based on a forward biased transistor. The temperature sensor has its own auxiliary ADC.

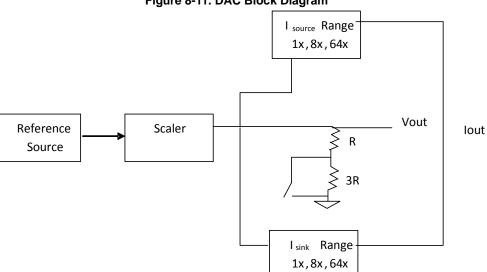

#### 8.9 DAC

The CY8C34 parts contain two Digital to Analog Convertors (DACs). Each DAC is 8-bit and can be configured for either voltage or current output. The DACs support CapSense, power supply regulation, and waveform generation. Each DAC has the following features:

- Adjustable voltage or current output in 255 steps

- Programmable step size (range selection)

- Eight bits of calibration to correct ± 25 percent of gain error

- Source and sink option for current output

- High and low speed / power modes

- 8 Msps conversion rate for current output

- 1 Msps conversion rate for voltage output

- Monotonic in nature

- Data and strobe inputs can be provided by the CPU or DMA, or routed directly from the DSI

- Dedicated low-resistance output pin for high-current mode

Figure 8-11. DAC Block Diagram

#### 8.9.1 Current DAC

The current DAC (IDAC) can be configured for the ranges 0 to 31.875  $\mu$ A, 0 to 255  $\mu$ A, and 0 to 2.04 mA. The IDAC can be configured to source or sink current.

#### 8.9.2 Voltage DAC

For the voltage DAC (VDAC), the current DAC output is routed through resistors. The two ranges available for the VDAC are 0 to 1.02 V and 0 to 4.08 V. In voltage mode any load connected to the output of a DAC should be purely capacitive (the output of the VDAC is not buffered).

#### 8.10 Up/Down Mixer

In continuous time mode, the SC/CT block components are used to build an up or down mixer. Any mixing application contains an input signal frequency and a local oscillator frequency. The polarity of the clock, Fclk, switches the amplifier between inverting or noninverting gain. The output is the product of the input and the switching function from the local oscillator, with frequency components at the local oscillator plus and minus the signal frequency (Fclk + Fin and Fclk – Fin) and reduced-level frequency components at odd integer multiples of the local oscillator frequency. The local oscillator frequency is provided by the selected clock source for the mixer.

Continuous time up and down mixing works for applications with input signals and local oscillator frequencies up to 1 MHz.

**Table 11-2. DC Specifications** (continued)

| Parameter | Description                                                     | Conditions                                                   |            | Min | <b>Typ</b> <sup>[25]</sup> | Max  | Units |

|-----------|-----------------------------------------------------------------|--------------------------------------------------------------|------------|-----|----------------------------|------|-------|

|           | Sleep Mode <sup>[28]</sup>                                      |                                                              |            |     |                            |      |       |

|           | CPU = OFF                                                       | V <sub>DD</sub> = V <sub>DDIO</sub> =                        | T = -40 °C | _   | 1.1                        | 2.3  | μA    |

|           | RTC = ON (= ECO32K ON, in low-power                             | 4.5 V - 5.5 V                                                | T = 25 °C  | -   | 1.1                        | 2.2  |       |

|           | mode)<br>  Sleep timer = ON (= ILO ON at 1 kHz) <sup>[29]</sup> |                                                              | T = 85 °C  | _   | 15                         | 30   |       |

|           | WDT = OFF                                                       | V <sub>DD</sub> = V <sub>DDIO</sub> =                        | T = -40 °C | -   | 1                          | 2.2  |       |

|           | I2C Wake = OFF                                                  | 2.7 V – 3.6 V                                                | T = 25 °C  | _   | 1                          | 2.1  |       |

|           | Comparator = OFF<br>POR = ON                                    |                                                              | T = 85 °C  | _   | 12                         | 28   |       |

|           | Boost = OFF                                                     | $V_{DD} = V_{DDIO} =$                                        | T = 25 °C  | -   | 2.2                        | 4.2  |       |

|           | SIO pins in single ended input, unregulated output mode         | 1.71 V – 1.95 V <sup>[30]</sup>                              |            |     |                            |      |       |

|           | Comparator = ON                                                 | $V_{DD} = V_{DDIO} = 2.7 \text{ V} - 3.6 \text{ V}^{[31]}$   | T = 25 °C  | -   | 2.2                        | 2.7  |       |

|           | CPU = OFF<br>RTC = OFF                                          | $2.7 \text{ V} - 3.6 \text{ V}^{[31]}$                       |            |     |                            |      |       |

|           | Sleep timer = OFF                                               |                                                              |            |     |                            |      |       |

|           | WDT = OFF                                                       |                                                              |            |     |                            |      |       |

|           | I2C Wake = OFF<br>POR = ON                                      |                                                              |            |     |                            |      |       |

|           | Boost = OFF                                                     |                                                              |            |     |                            |      |       |

|           | SIO pins in single ended input, unregu-                         |                                                              |            |     |                            |      |       |

|           | lated output mode                                               |                                                              |            |     |                            |      |       |

|           | I2C Wake = ON<br>CPU = OFF                                      | $V_{DD} = V_{DDIO} = 2.7 \text{ V} - 3.6 \text{ V}^{[31]}$   | T = 25 °C  | -   | 2.2                        | 2.8  |       |

|           | RTC = OFF                                                       |                                                              |            |     |                            |      |       |

|           | Sleep timer = OFF                                               |                                                              |            |     |                            |      |       |

|           | WDT = OFF                                                       |                                                              |            |     |                            |      |       |

|           | Comparator = OFF<br>POR = ON                                    |                                                              |            |     |                            |      |       |

|           | Boost = OFF                                                     |                                                              |            |     |                            |      |       |

|           | SIO pins in single ended input, unregu-                         |                                                              |            |     |                            |      |       |

|           | lated output mode                                               |                                                              |            |     |                            |      |       |

|           | Hibernate Mode <sup>[28]</sup>                                  |                                                              | 1          |     | _                          |      |       |

|           | Hibernate mode current All regulators and oscillators off       | V <sub>DD</sub> = V <sub>DDIO</sub> =<br>4.5 V - 5.5 V       | T = -40 °C | ı   | 0.2                        | 1.5  | μA    |

|           | SRAM retention                                                  | 4.5 V - 5.5 V                                                | T = 25 °C  | ı   | 0.5                        | 1.5  |       |

|           | GPIO interrupts are active                                      |                                                              | T = 85 °C  | -   | 4.1                        | 5.3  |       |

|           | Boost = OFF<br>SIO pins in single ended input, unregu-          | V <sub>DD</sub> = V <sub>DDIO</sub> =<br>2.7 V – 3.6 V       | T = -40 °C | ı   | 0.2                        | 1.5  |       |

|           | lated output                                                    | 2.7 V - 3.6 V                                                | T = 25 °C  | ı   | 0.2                        | 1.5  |       |

|           | mode                                                            |                                                              | T = 85 °C  | -   | 3.2                        | 4.2  |       |

|           |                                                                 | $V_{DD} = V_{DDIO} = 1.71 \text{ V} - 1.95 \text{ V}^{[30]}$ | T = -40 °C | _   | 0.2                        | 1.5  |       |

|           |                                                                 | 1.71 V – 1.95 V <sup>[30]</sup>                              | T = 25 °C  | _   | 0.3                        | 1.5  |       |

|           |                                                                 |                                                              | T = 85 °C  | _   | 3.3                        | 4.3  |       |

| DDAR      | Analog current consumption while device                         | $V_{DDA} \le 3.6 \text{ V}$                                  |            | _   | 0.3                        | 0.6  | mA    |

|           | is reset <sup>[32]</sup>                                        | V <sub>DDA</sub> > 3.6 V                                     |            | _   | 1.4                        | 3.3  | mA    |

| DDDR      | Digital current consumption while device is                     | II.                                                          |            | _   | 1.1                        | 3.1  | mA    |

|           | reset <sup>[32]</sup>                                           | V <sub>DDD</sub> > 3.6 V                                     |            | _   | 0.7                        | 3.1  | mA    |

|           |                                                                 | - DDD - 3.0 v                                                |            |     | 5.7                        | J. 1 | 111/3 |

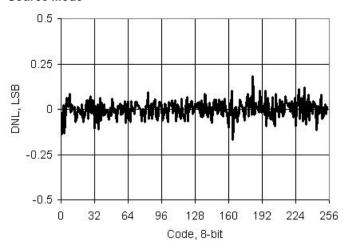

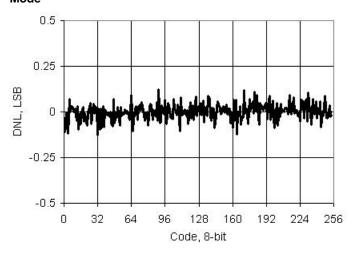

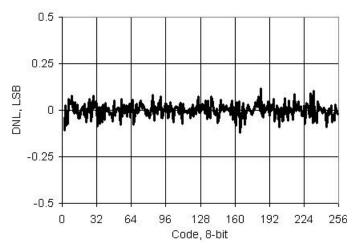

Figure 11-36. IDAC DNL vs Input Code, Range = 255  $\mu$ A, Source Mode

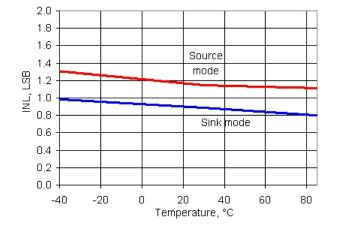

Figure 11-38. IDAC INL vs Temperature, Range = 255  $\mu$ A, High speed mode

Figure 11-37. IDAC DNL vs Input Code, Range = 255  $\mu$ A, Sink Mode

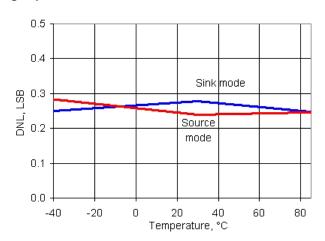

Figure 11-39. IDAC DNL vs Temperature, Range = 255  $\mu$ A, High speed mode

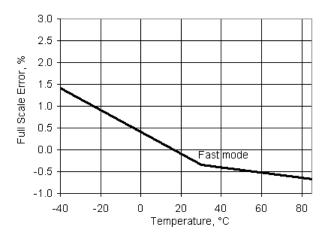

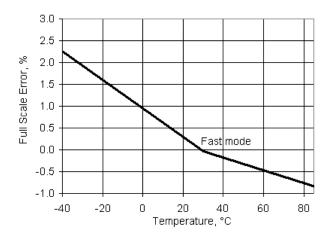

Figure 11-40. IDAC Full Scale Error vs Temperature, Range = 255  $\mu$ A, Source Mode

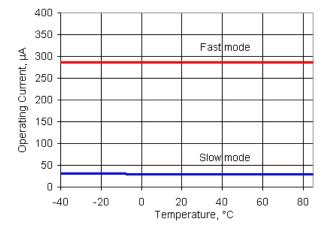

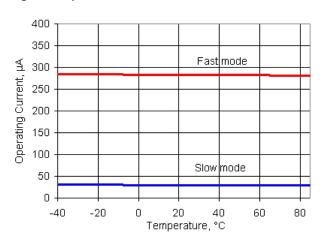

Figure 11-42. IDAC Operating Current vs Temperature, Range =  $255 \mu A$ , Code = 0, Source Mode

Figure 11-41. IDAC Full Scale Error vs Temperature, Range = 255  $\mu$ A, Sink Mode

Figure 11-43. IDAC Operating Current vs Temperature, Range = 255 µA, Code = 0, Sink Mode

Table 11-29. IDAC AC Specifications

| Parameter           | Description              | Conditions                                                                                             | Min | Тур | Max | Units     |

|---------------------|--------------------------|--------------------------------------------------------------------------------------------------------|-----|-----|-----|-----------|

| F <sub>DAC</sub>    | Update rate              |                                                                                                        | _   | _   | 8   | Msps      |

| T <sub>SETTLE</sub> | Settling time to 0.5 LSB | Range = 31.875 $\mu$ A or 255 $\mu$ A, full scale transition, High speed mode, 600 $\Omega$ 15-pF load | -   | _   | 125 | ns        |

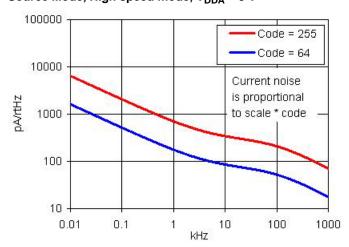

|                     | Current noise            | Range = 255 $\mu$ A, source mode,<br>High speed mode, V <sub>DDA</sub> = 5 V,<br>10 kHz                | -   | 340 | _   | pA/sqrtHz |

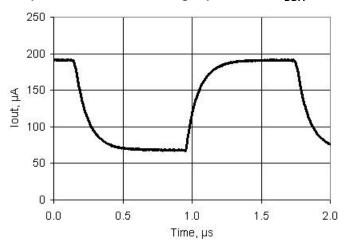

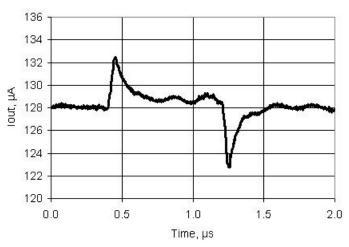

Figure 11-44. IDAC Step Response, Codes 0x40 - 0xC0, 255 µA Mode, Source Mode, High speed mode, V<sub>DDA</sub> = 5 V

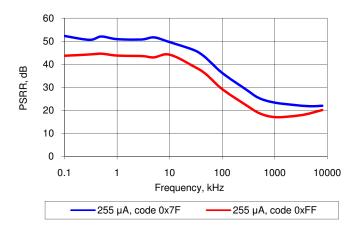

Figure 11-46. IDAC PSRR vs Frequency

Figure 11-45. IDAC Glitch Response, Codes 0x7F - 0x80, 255  $\mu A$  Mode, Source Mode, High speed mode,  $V_{DDA} = 5$  V

Figure 11-47. IDAC Current Noise, 255  $\mu$ A Mode, Source Mode, High speed mode, V<sub>DDA</sub> = 5 V

#### 11.5.7 Voltage Digital to Analog Converter (VDAC)

See the VDAC component datasheet in PSoC Creator for full electrical specifications and APIs.

Unless otherwise specified, all charts and graphs show typical values.

Table 11-30. VDAC DC Specifications

| Parameter        | Description                               | Conditions                        | Min | Тур  | Max  | Units     |

|------------------|-------------------------------------------|-----------------------------------|-----|------|------|-----------|

|                  | Resolution                                |                                   | _   | 8    | -    | bits      |

| INL1             | Integral nonlinearity                     | 1 V scale                         | _   | ±2.1 | ±2.5 | LSB       |

| INL4             | Integral nonlinearity <sup>[55]</sup>     | 4 V scale                         | _   | ±2.1 | ±2.5 | LSB       |

| DNL1             | Differential nonlinearity                 | 1 V scale                         | _   | ±0.3 | ±1   | LSB       |

| DNL4             | Differential nonlinearity <sup>[55]</sup> | 4 V scale                         | _   | ±0.3 | ±1   | LSB       |

| Rout             | Output resistance                         | 1 V scale                         | _   | 4    | _    | kΩ        |

|                  |                                           | 4 V scale                         | _   | 16   | _    | kΩ        |

| V <sub>OUT</sub> | Output voltage range, code = 255          | 1 V scale                         | _   | 1.02 | _    | V         |

|                  |                                           | 4 V scale, V <sub>DDA</sub> = 5 V | _   | 4.08 | -    | V         |

|                  | Monotonicity                              |                                   | _   | -    | Yes  | _         |

| V <sub>OS</sub>  | Zero scale error                          |                                   | _   | 0    | ±0.9 | LSB       |

| Eg               | Gain error                                | 1 V scale                         | _   | -    | ±2.5 | %         |

|                  |                                           | 4 V scale                         | _   | -    | ±2.5 | %         |

| TC_Eg            | Temperature coefficient, gain error       | 1 V scale                         | _   | -    | 0.03 | %FSR / °C |

|                  |                                           | 4 V scale                         | _   | _    | 0.03 | %FSR / °C |

| I <sub>DD</sub>  | Operating current                         | Low speed mode                    | _   | _    | 100  | μA        |

|                  |                                           | High speed mode                   | _   | _    | 500  | μA        |

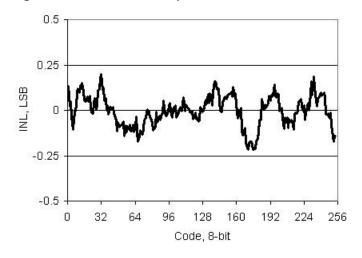

Figure 11-48. VDAC INL vs Input Code, 1 V Mode

Figure 11-49. VDAC DNL vs Input Code, 1 V Mode

#### Note

55. Based on device characterization (Not production tested).

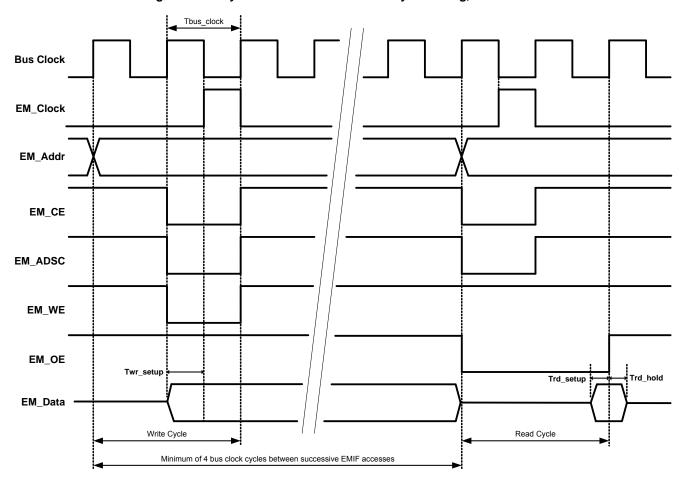

Figure 11-65. Synchronous Write and Read Cycle Timing, No Wait States

Table 11-62. Synchronous Write and Read Timing Specifications<sup>[63]</sup>

| Parameter  | Description                                                 | Conditions | Min             | Тур | Max | Units |

|------------|-------------------------------------------------------------|------------|-----------------|-----|-----|-------|

| Fbus_clock | Bus clock frequency <sup>[64]</sup>                         |            | _               | _   | 33  | MHz   |

| Tbus_clock | Bus clock period <sup>[65]</sup>                            |            | 30.3            | _   | _   | ns    |

| Twr_Setup  | Time from EM_data valid to rising edge of EM_Clock          |            | Tbus_clock - 10 | _   | _   | ns    |

| Trd_setup  | Time that EM_data must be valid before rising edge of EM_OE |            | 5               | -   | _   | ns    |

| Trd_hold   | Time that EM_data must be valid after rising edge of EM_OE  |            | 5               | _   | -   | ns    |

#### Notes

<sup>63.</sup> Based on device characterization (Not production tested).

64. EMIF signal timings are limited by GPIO frequency limitations. See "GPIO" section on page 79.

65. EMIF output signals are generally synchronized to bus clock, so EMIF signal timings are dependent on bus clock frequency.

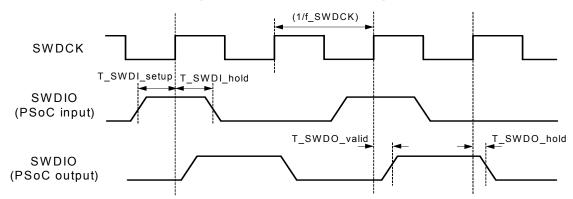

#### 11.8.5 SWD Interface

#### Figure 11-69. SWD Interface Timing

Table 11-71. SWD Interface AC Specifications<sup>[71]</sup>

| Parameter    | Description                         | Conditions                                                                      | Min | Тур | Max                 | Units |

|--------------|-------------------------------------|---------------------------------------------------------------------------------|-----|-----|---------------------|-------|

| f_SWDCK      | SWDCLK frequency                    | $3.3 \text{ V} \leq \text{V}_{DDD} \leq 5 \text{ V}$                            | _   | _   | 14 <sup>[72]</sup>  | MHz   |

|              |                                     | 1.71 V ≤ V <sub>DDD</sub> < 3.3 V                                               | -   | _   | 7 <sup>[72]</sup>   | MHz   |

|              |                                     | $1.71 \text{ V} \le \text{V}_{\text{DDD}} < 3.3 \text{ V},$ SWD over USBIO pins | _   | _   | 5.5 <sup>[72]</sup> | MHz   |

| T_SWDI_setup | SWDIO input setup before SWDCK high | T = 1/f_SWDCK max                                                               | T/4 | _   | -                   | _     |

| T_SWDI_hold  | SWDIO input hold after SWDCK high   | T = 1/f_SWDCK max                                                               | T/4 | _   | -                   | _     |

| T_SWDO_valid | SWDCK high to SWDIO output          | T = 1/f_SWDCK max                                                               | _   | _   | 2T/5                | _     |

#### 11.8.6 SWV Interface

#### Table 11-72. SWV Interface AC Specifications<sup>[71]</sup>

| Parameter | Description           | Conditions | Min | Тур | Max | Units |

|-----------|-----------------------|------------|-----|-----|-----|-------|

|           | SWV mode SWV bit rate |            | _   | _   | 33  | Mbit  |

#### Notes

<sup>71.</sup> Based on device characterization (Not production tested).

<sup>72.</sup> ff\_SWDCK must also be no more than 1/3 CPU clock frequency.

#### 11.9.5 External Clock Reference

### Table 11-81. External Clock Reference AC Specifications<sup>[76]</sup>

| Parameter | Description              | Conditions                         | Min | Тур | Max | Units |

|-----------|--------------------------|------------------------------------|-----|-----|-----|-------|

|           | External frequency range |                                    | 0   | _   | 33  | MHz   |

|           | Input duty cycle range   | Measured at V <sub>DDIO</sub> /2   | 30  | 50  | 70  | %     |

|           | Input edge rate          | V <sub>IL</sub> to V <sub>IH</sub> | 0.5 | _   | _   | V/ns  |

#### 11.9.6 Phase-Locked Loop

#### Table 11-82. PLL DC Specifications

| Parameter       | Description           | Conditions               | Min | Тур | Max | Units |

|-----------------|-----------------------|--------------------------|-----|-----|-----|-------|

| I <sub>DD</sub> | PLL operating current | In = 3 MHz, Out = 24 MHz | _   | 200 | _   | μΑ    |

#### Table 11-83. PLL AC Specifications

| Parameter   | Description                                | Conditions          | Min | Тур | Max | Units |

|-------------|--------------------------------------------|---------------------|-----|-----|-----|-------|

| Fpllin      | PLL input frequency <sup>[77]</sup>        |                     | 1   | _   | 48  | MHz   |

|             | PLL intermediate frequency <sup>[78]</sup> | Output of prescaler | 1   | _   | 3   | MHz   |

| Fpllout     | PLL output frequency <sup>[77]</sup>       |                     | 24  | _   | 50  | MHz   |

|             | Lock time at startup                       |                     | _   | _   | 250 | μs    |

| Jperiod-rms | Jitter (rms) <sup>[76]</sup>               |                     | _   | 1   | 250 | ps    |

Document Number: 001-53304 Rev. \*Y Page 120 of 137

<sup>76.</sup> Based on device characterization (Not production tested).

77. This specification is guaranteed by testing the PLL across the specified range using the IMO as the source for the PLL.

78. PLL input divider, Q, must be set so that the input frequency is divided down to the intermediate frequency range. Value for Q ranges from 1 to 16.

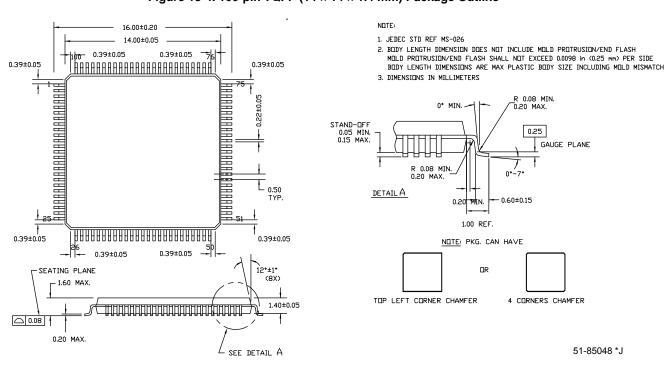

### 13. Packaging

**Table 13-1. Package Characteristics**

| Parameter      | Description                            | Conditions | Min | Тур   | Max | Units   |

|----------------|----------------------------------------|------------|-----|-------|-----|---------|

| T <sub>A</sub> | Operating ambient temperature          |            | -40 | 25.00 | 85  | °C      |

| TJ             | Operating junction temperature         |            | -40 | _     | 100 | °C      |

| $T_{JA}$       | Package θ <sub>JA</sub> (48-pin SSOP)  |            | -   | 49    | _   | °C/Watt |

| $T_{JA}$       | Package θ <sub>JA</sub> (48-pin QFN)   |            | -   | 14    | _   | °C/Watt |

| $T_JA$         | Package θ <sub>JA</sub> (68-pin QFN)   |            | -   | 15    | _   | °C/Watt |

| $T_{JA}$       | Package θ <sub>JA</sub> (100-pin TQFP) |            | -   | 34    | _   | °C/Watt |

| $T_{JC}$       | Package θ <sub>JC</sub> (48-pin SSOP)  |            | -   | 24    | -   | °C/Watt |

| $T_{JC}$       | Package θ <sub>JC</sub> (48-pin QFN)   |            | -   | 15    | _   | °C/Watt |

| $T_{JC}$       | Package θ <sub>JC</sub> (68-pin QFN)   |            | -   | 13    | _   | °C/Watt |

| $T_JC$         | Package θ <sub>JC</sub> (100-pin TQFP) |            | -   | 10    | _   | °C/Watt |

Table 13-2. Solder Reflow Peak Temperature

| Package      | Maximum Peak<br>Temperature | Maximum Time at Peak<br>Temperature |

|--------------|-----------------------------|-------------------------------------|

| 48-pin SSOP  | 260 °C                      | 30 seconds                          |

| 48-pin QFN   | 260 °C                      | 30 seconds                          |

| 68-pin QFN   | 260 °C                      | 30 seconds                          |

| 100-pin TQFP | 260 °C                      | 30 seconds                          |

Table 13-3. Package Moisture Sensitivity Level (MSL), IPC/JEDEC J-STD-2

| Package      | MSL   |

|--------------|-------|

| 48-pin SSOP  | MSL 3 |

| 48-pin QFN   | MSL 3 |

| 68-pin QFN   | MSL 3 |

| 100-pin TQFP | MSL 3 |

Document Number: 001-53304 Rev. \*Y Page 123 of 137

5.70±0.10

TOP VIEW SIDE VIEW BOTTOM VIEW 8.00±0.10 52 68 PIN 1 DOT 0.40±0.05 n n n n n 0.20±0.05 17 35 0.05 MAX 1.00 MAX -0.40+0.10

Figure 13-3. 68-pin QFN 8 × 8 with 0.4 mm Pitch Package Outline (Sawn Version)

#### NOTES:

- 1. MATCH AREA IS SOLDERABLE EXPOSED METAL.

- 2. REFERENCE JEDEC#: MO-220

- 3. PACKAGE WEIGHT: 17  $\pm$  2mg

- 4. ALL DIMENSIONS ARE IN MILLIMETERS

001-09618 \*E

Figure 13-4. 100-pin TQFP (14 × 14 × 1.4 mm) Package Outline

0.08

| Revision | ECN     | Submission<br>Date | Orig. of<br>Change | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------|---------|--------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| *J       | 3179219 | 02/22/2011         | MKEA               | Updated conditions for flash data retention time. Updated 100-pin TQFP package spec. Updated EEPROM AC specifications.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| *K       | 3200146 | 03/28/2011         | MKEA               | Removed Preliminary status from the data sheet. Updated JTAG ID Deleted Cin_G1, ADC input capacitance from Delta-Sigma ADC DC spec table Updated JTAG Interface AC Specifications and SWD Interface Specifications tables Updated USBIO DC specs Added 0.01 to max speed Updated Features on page 1 Added Section 5.5, Nonvolatile Latches Updated Flash AC specs Added CAN DC specs Updated Flash AC specs Updated delta-sigma graphs, noise histogram figures and RMS Noise spec tables Add reference to application note AN58304 in section 8.1 Updated 100-pin TQFP package spec Added oscillator, I/O, VDAC, regulator graphs Updated JTAG/SWD timing diagrams Updated GPIO and SIO AC specs Updated POR with Brown Out AC spec table Updated IDAC graphs Added DMA timing diagram, interrupt timing and interrupt vector, I2C timing diagrams Updated opamp graphs and PGA graphs Added full chip performance graphs Changed MHzECO range. Added "Solder Reflow Peak Temperature" table. |

| *L       | 3259185 | 05/17/2011         | MKEA               | Added JTAG and SWD interface connection diagrams Updated $T_{JA}$ and $T_{JC}$ values in Table 13-1 Changed typ and max values for the TCVos parameter in Opamp DC specifications table. Updated Clocking subsystem diagram. Changed VSSD to VSSB in the PSoC Power System diagram Updated Ordering information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

Document Number: 001-53304 Rev. \*Y

| Revision | ECN     | Submission<br>Date | Orig. of<br>Change | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------|---------|--------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| *P       | 3732521 | 09/03/2012         | MKEA               | Replaced I <sub>DDDR</sub> and I <sub>DDAR</sub> specs in Table 11-2, "DC Specifications," on page 71 that were dropped out in *N revision.  Updated Table 11-32, "Mixer DC Specifications," on page 102, V <sub>OS</sub> Max value from 10 to 15.  Updated Table 11-21, "12-bit Delta-sigma ADC DC Specifications," on page 91, I <sub>DD 12</sub> Max value from 1.4 to 1.95 mA  Replaced PSoC® 3 Programming AN62391 with TRM in footnote #59 and Section Table 9., "Programming, Debug Interfaces, Resources," on page 65  Removed Figure 11-8 (Efficiency vs Vout)  Removed 62-MHz sub-row in Table 11-2, "DC Specifications," on page 71  Updated Table 11-19, "Opamp DC Specifications," on page 88, I <sub>DD</sub> Quiescent current row values from 200 and 270 to 250 and 400 respectively.  Updated conditions for Storage Temperature in Table 11-1, "Absolute Maximum |

|          |         |                    |                    | Ratings DC Specifications[18]," on page 70 Updated conditions and min values for NVL data retention time in Table 11-58, "NVL AC Specifications," on page 109. Updated Table 11-75, "ILO DC Specifications," on page 118. Removed following pruned parts from "Ordering Information" section on page 121. CY8C3444AXI-116 CY8C34446XI-1089 CY8C3446AXI-105 CY8C3446PVI-091 CY8C3446PVI-102 Updated PSoC 3 boost circuit value throughout the document. Updated package diagram 51-85061 to *F revision.                                                                                                                                                                                                                                                                                                                                                                             |

| *Q       | 3922905 | 03/06/2013         | MKEA               | Updated I <sub>DD_XX</sub> parameters under Table 11-21, "12-bit Delta-sigma ADC DC Specifications," on page 91. Updated I <sup>2</sup> C section and updated GPIO and SIO DC specification tables.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| *R       | 4064707 | 07/18/2013         | MKEA               | Added USB test ID in Features. Updated schematic in Section 2. Added paragraph for device reset warning in Section 5.4. Added NVL bit for DEBUG_EN in Section 5.5. Updated UDB PLD array diagram in Section 7.2.1. Changed Tstartup specs in Section 11.2.1. Changed GPIO rise and fall time specs in Section 11.4. Added Opamp IIB spec in Section 11.5.1. Added IMO spec condition: pre-assembly in Section 11.9.1. Added Appendix for CSP package (preliminary)                                                                                                                                                                                                                                                                                                                                                                                                                  |

| *S       | 4118845 | 09/10/2013         | MKEA               | Removed T <sub>STG</sub> spec and added note clarifying the maximum storage temperature range in Table 11-1. Updated Vos spec conditions and TCVos in Table 11-21. Updated 100-TQFP package diagram.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| *T       | 4188568 | 11/14/2013         | MKEA               | Updated delta-sigma Vos spec conditions. Added SIO Comparator specifications.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| *U       | 4385782 | 05/21/2014         | MKEA               | Updated General Description and Features. Added More Information and PSoC Creator sections. Updated 100-pin TQFP package diagram.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |