Welcome to E-XFL.COM

### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Details

| Product Status          | Active                                                            |

|-------------------------|-------------------------------------------------------------------|

| Туре                    | Sigma                                                             |

| Interface               | I <sup>2</sup> C, SPI                                             |

| Clock Rate              | 294.912MHz                                                        |

| Non-Volatile Memory     | ROM (32kB)                                                        |

| On-Chip RAM             | 64kB                                                              |

| Voltage - I/O           | 3.30V                                                             |

| Voltage - Core          | 1.20V                                                             |

| Operating Temperature   | -40°C ~ 105°C (TA)                                                |

| Mounting Type           | Surface Mount                                                     |

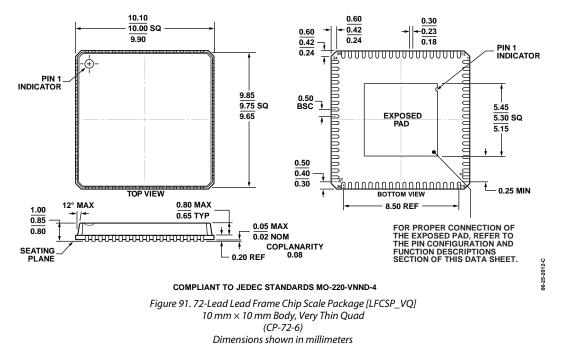

| Package / Case          | 72-VFQFN Exposed Pad, CSP                                         |

| Supplier Device Package | 72-LFCSP-VQ (10x10)                                               |

| Purchase URL            | https://www.e-xfl.com/product-detail/analog-devices/adau1451wbcpz |

|                         |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **GENERAL DESCRIPTION**

The ADAU1452/ADAU1451/ADAU1450 are automotive qualified audio processors that far exceed the digital signal processing capabilities of earlier SigmaDSP<sup>\*</sup> devices. The restructured hardware architecture is optimized for efficient audio processing. The audio processing algorithms are realized in sample-by-sample and block-by-block paradigms that can both be executed simultaneously in a signal processing flow created using the graphical programming tool, SigmaStudio<sup>™</sup>. The restructured digital signal processor (DSP) core architecture enables some types of audio processing algorithms to be executed using significantly fewer instructions than were required on previous SigmaDSP generations, leading to vastly improved code efficiency.

The 1.2 V, 32-bit DSP core can run at frequencies of up to 294.912 MHz and execute up to 6144 instructions per sample at the standard sample rate of 48 kHz. However, in addition to industry standard rates, a wide range of sample rates are available. The integer PLL and flexible clock generator hardware can generate up to 15 audio sample rates simultaneously. These clock generators, along with the on board asynchronous sample rate converters (ASRCs) and a flexible hardware audio routing matrix, make the ADAU1452/ADAU1451/ADAU1450 ideal audio hubs that greatly simplify the design of complex multirate audio systems.

The ADAU1452/ADAU1451/ADAU1450 interface with a wide range of ADCs, DACs, digital audio devices, amplifiers, and control circuitry, due to their highly configurable serial ports, S/PDIF interfaces (on the ADAU1452 and ADAU1451), and multipurpose input/output pins. They can also directly interface with PDM output MEMS microphones, thanks to integrated decimation filters specifically designed for that purpose. Independent slave and master I<sup>2</sup>C/SPI control ports allow the ADAU1452/ADAU1451/ADAU1450 not only to be programmed and configured by an external master device, but also to act as masters that can program and configure external slave devices directly. This flexibility, combined with self boot functionality, enables the design of standalone systems that do not require any external input to operate.

The power efficient DSP core executes full programs while consuming only a few hundred milliwatts (mW) of power and can run at a maximum program load while consuming less than a watt, even in worst case temperatures exceeding 100°C. This relatively low power consumption and small footprint make the ADAU1452/ADAU1451/ADAU1450 ideal replacements for large, general-purpose DSPs that consume more power at the same processing load.

### DIFFERENCES BETWEEN THE ADAU1452, ADAU1451, AND ADAU1450

The three variants of this device are differentiated by memory, DSP core frequency, availability of S/PDIF interfaces, and ASRC configuration. A detailed summary of the differences is listed in Table 1.

Because the ADAU1450 does not contain an S/PDIF receiver or transmitter, the SPDIFIN and SPDIFOUT pins are nonfunctional. Also, the settings of any registers related to the S/PDIF input or output in the ADAU1450 do not have any effect on the operation of the device.

Likewise, because the ADAU1450 does not contain ASRCs, the settings of any registers related to the ASRCs in the ADAU1450 do not have any effect on the operation of the device.

| 1 4010 10 1 10 4 |                         |                            |                       |                            |                                             |  |  |

|------------------|-------------------------|----------------------------|-----------------------|----------------------------|---------------------------------------------|--|--|

| Device<br>Number | Data Memory<br>(kWords) | Program Memory<br>(kWords) | DSP Core<br>Frequency | S/PDIF Input and<br>Output | ASRC Configuration                          |  |  |

| ADAU1452         | 40                      | 8                          | 294.912 MHz           | Available                  | 16 channels (8 rates × 2 channels per rate) |  |  |

| ADAU1451         | 16                      | 8                          | 294.912 MHz           | Available                  | 16 channels (8 rates × 2 channels per rate) |  |  |

| ADAU1450         | 8                       | 8                          | 147.456 MHz           | Not available              | No ASRCs included                           |  |  |

### Table 1. Product Selection Table

### **PDM** Inputs

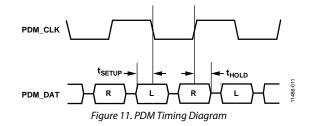

$T_A = -40^{\circ}C$  to  $+105^{\circ}C$ , DVDD  $= 1.2 V \pm 5\%$ , IOVDD = 1.8 V - 10% to 3.3 V + 10%. PDM data is latched on both edges of the clock (see Figure 11).

### Table 16.

| Parameter           | t <sub>MIN</sub> | t <sub>MAX</sub> | Unit | Description     |

|---------------------|------------------|------------------|------|-----------------|

| Timing Requirements |                  |                  |      |                 |

| <b>t</b> setup      | 10               |                  | ns   | Data setup time |

| thold               | 5                |                  | ns   | Data hold time  |

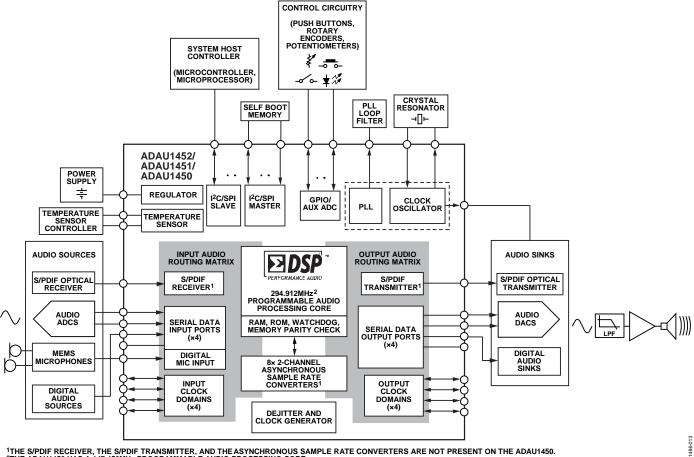

# THEORY OF OPERATION SYSTEM BLOCK DIAGRAM

<sup>1</sup>THE S/PDIF RECEIVER, THE S/PDIF TRANSMITTER, AND THE ASYNCHRONOUS SAMPLE RATE CONVERTERS ARE NOT PRESENT ON THE ADAU1450. <sup>2</sup>THE ADAU1450 HAS A 147.456MHz PROGRAMMABLE AUDIO PROCESSING CORE.

Figure 13. System Block Diagram with Example Connections to External Components

### **OVERVIEW**

The ADAU1452/ADAU1451/ADAU1450 are enhanced audio processors with 48 channels of input and output. They include options for the hardware routing of audio signals between the various inputs, outputs, SigmaDSP core, and integrated sample rate converters. The SigmaDSP core features full 32-bit processing (that is, 64-bit processing in double precision mode) with an 80-bit arithmetic logic unit (ALU). By using a quadruple multiply accumulator (MAC) data path, the ADAU1452/ADAU1451 can execute more than 1.2 billion MAC operations per second, which allows for processing power that far exceeds the predecessors in the SigmaDSP family of products. The powerful DSP core can process over 3000 double precision biquad filters or 24,000 FIR filter taps per sample at the standard 48 kHz audio sampling rate. The ADAU1450 features half the processing power of the ADAU1452/ADAU1451. Other features, including synchronous parameter loading for ensuring filter stability and 100% code efficiency with the SigmaStudio tools, reduce complexity in audio system development. The SigmaStudio library of audio processing algorithms allows system designers to compensate for real-world

limitations of speakers, amplifiers, and listening environments, through speaker equalization, multiband compression, limiting, and third party branded algorithms.

The input audio routing matrix and output audio routing matrix allow the user to multiplex inputs from multiple sources that are running at various sample rates to or from the SigmaDSP core, and then to pass them on to the desired hardware outputs. This drastically reduces the complexity of signal routing and clocking issues in the audio system. The audio subsystem includes up to eight stereo asynchronous sample rate converters (ASRCs), depending on the device model; Sony/Philips Digital Interconnect Format (S/PDIF) input and output (available on the ADAU1452/ ADAU1451); and serial (I<sup>2</sup>S) and time division multiplexing (TDM) I/Os. Any of these inputs can be routed to the SigmaDSP core or to any of the ASRCs (except on the ADAU1450, which does not have ASRCs). Similarly, the output signals can be taken from the SigmaDSP core, any of the ASRC outputs, the serial inputs, the PDM microphones, or the S/PDIF receiver. This routing scheme, which can be modified at any time using control registers, allows for maximum system flexibility without requiring hardware design changes.

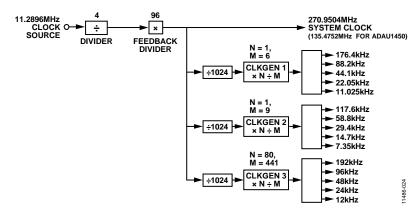

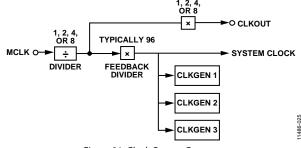

Figure 20. PLL and Audio Clock Generators with Default Settings and Resulting Clock Frequencies Labeled, XTALIN/MCLK = 11.2896 MHz

Figure 20 shows an example where the master clock input has a frequency of 11.2896 MHz, and the default settings are used for the PLL predivider, feedback divider, and Clock Generator 1 and Clock Generator 2. The resulting system clock is

11.2896 MHz ÷ 4 × 96 = 270.9504 MHz

The base output of Clock Generator 1 is

270.9504 MHz  $\div$  1024  $\times$  1  $\div$  6 = 44.1 kHz

The base output of Clock Generator 2 is

270.9504 MHz  $\div$  1024  $\times$  1  $\div$  9 = 29.4 kHz

In this example, Clock Generator 3 is configured with N = 80 and M = 441; therefore, the resulting base output of Clock Generator 3 is

270.9504 MHz ÷ 1024 × 80 ÷ 441 = 48 kHz

### **Master Clock Output**

The master clock output pin (CLKOUT) is useful in cases where a master clock must be fed to other ICs in the system, such as audio codecs. The master clock output frequency is determined by the setting of the MCLK\_OUT register (Address 0xF005). Four frequencies are possible: 1×, 2×, 4×, or 8× the frequency of the predivider output.

- The predivider output × 1 generates a 3.072 MHz output for a nominal system clock of 294.912 MHz.

- The predivider output × 2 generates a 6.144 MHz output for a nominal system clock of 294.912 MHz.

- The predivider output × 4 generates a 12.288 MHz output for a nominal system clock of 294.912 MHz.

- The predivider output × 8 generates a 24.576 MHz output for a nominal system clock of 294.912 MHz.

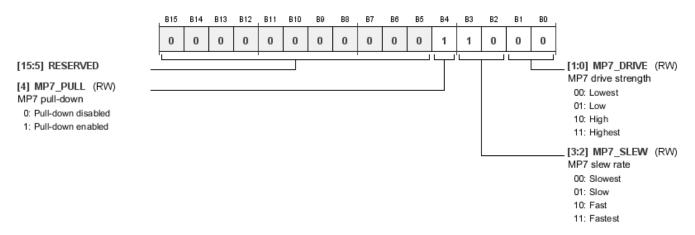

Figure 21. Clock Output Generator

The CLKOUT pin can drive more than one external slave IC if the drive strength is sufficient to drive the traces and external receiver circuitry. The ability to drive external ICs varies greatly, depending on the application and the characteristics of the PCB and the slave ICs. The drive strength and slew rate of the CLKOUT pin is configurable in the CLKOUT\_PIN register (Address 0xF7A3); thus, its performance can be tuned to match the specific application. The CLKOUT pin is not designed to drive long cables or other high impedance transmission lines. Use the CLKOUT pin only to drive signals to other integrated circuits on the same PCB. When changing the settings for the predivider, disable and then reenable the PLL using Register 0xF003 (PLL\_ENABLE), allowing the frequency of the CLKOUT signal to update.

### **Dejitter Circuitry**

To account for jitter between ICs in the system and to handle interfacing safely between internal and external clocks, de-jitter circuits are included to guarantee that jitter related clocking errors are avoided. The dejitter circuitry is automated and does not require interaction or control from the user.

### **Auxiliary Output Mode**

The received data on the S/PDIF receiver can be converted to a TDM8 stream, bypass the SigmaDSP core, and be output directly on a serial data output pin. This mode of operation is called auxiliary output mode. Configure this mode using Register 0xF608 (SPDIF\_AUX\_EN). The TDM8 output from the S/PDIF receiver regroups the recovered data in a TDM-like format, as shown in Table 52.

The S/PDIF receiver, when operating in auxiliary output mode, also recovers the embedded BCLK\_OUTx and LRCLK\_OUTx signals in the S/PDIF stream and outputs them on the corresponding BCLK\_OUTx and LRCLK\_OUTx pins in master mode when Register 0xF608 (SPDIF\_AUX\_EN), Bits[3:0] (TDMOUT), are configured to enable auxiliary output mode. The selected BCLK\_OUTx signal has a frequency of 256× the recovered sample rate, and the LRCLK\_OUTx signal is a 50-50 duty cycle square wave that has the same frequency as the audio sample rate (see Table 130).

# ADAU1452/ADAU1451/ADAU1450

#### TDM8 Channel **Description of Data Format** 0 8 zero bits followed by 24 audio bits, recovered from the left audio channel of the S/PDIF stream 28 zero bits followed by the left parity bit, left 1 validity bit, left user data, and left channel status 30 zero bits followed by the compression type bit 2 (0b0 = AC3, 0b1 = DTS) and the audio type bit (0 = PCM, 1 = compressed)3 No data 4 8 zero bits followed by 24 audio bits, recovered m

Table 52. S/PDIF Auxiliary Output Mode, TDM8 Data Format

|   | from the right audio channel of the S/PDIF stream                                                            |

|---|--------------------------------------------------------------------------------------------------------------|

| 5 | 28 zero bits followed by the right parity bit, right validity bit, right user data, and right channel status |

| 6 | No data                                                                                                      |

| 7 | 31 zero bits followed by the block start signal                                                              |

### S/PDIF Interface Registers

An overview of the registers related to the S/PDIF interface is shown in Table 53. For a more detailed description, refer to the S/PDIF Interface Registers section.

| Address          | Register                              | Description                                      |

|------------------|---------------------------------------|--------------------------------------------------|

| 0xF600           | SPDIF_LOCK_DET                        | S/PDIF receiver lock bit detection               |

| 0xF601           | SPDIF_RX_CTRL                         | S/PDIF receiver control                          |

| 0xF602           | SPDIF_RX_DECODE                       | Decoded signals from the S/PDIF receiver         |

| 0xF603           | SPDIF_RX_COMPRMODE                    | Compression mode from the S/PDIF receiver        |

| 0xF604           | SPDIF_RESTART                         | Automatically resume S/PDIF receiver audio input |

| 0xF605           | SPDIF_LOSS_OF_LOCK                    | S/PDIF receiver loss of lock detection           |

| 0xF608           | SPDIF_AUX_EN                          | S/PDIF receiver auxiliary outputs enable         |

| 0xF60F           | SPDIF_RX_AUXBIT_READY                 | S/PDIF receiver auxiliary bits ready flag        |

| 0xF610 to 0xF61B | SPDIF_RX_CS_LEFT_x                    | S/PDIF receiver channel status bits (left)       |

| 0xF620 to 0xF62B | SPDIF_RX_CS_RIGHT_x                   | S/PDIF receiver channel status bits (right)      |

| 0xF630 to 0xF63B | SPDIF_RX_UD_LEFT_x                    | S/PDIF receiver user data bits (left)            |

| 0xF640 to 0xF64B | SPDIF_RX_UD_RIGHT_x                   | S/PDIF receiver user data bits (right)           |

| 0xF650 to 0xF65B | SPDIF_RX_VB_LEFT_x                    | S/PDIF receiver validity bits (left)             |

| 0xF660 to 0xF66B | SPDIF_RX_VB_RIGHT_x                   | S/PDIF receiver validity bits (right)            |

| 0xF670 to 0xF67B | SPDIF_RX_PB_LEFT_x                    | S/PDIF receiver parity bits (left)               |

| 0xF680 to 0xF68B | SPDIF_RX_PB_RIGHT_x                   | S/PDIF receiver parity bits (right)              |

| 0xF690           | SPDIF_TX_EN                           | S/PDIF transmitter enable                        |

| 0xF691           | SPDIF_TX_CTRL                         | S/PDIF transmitter control                       |

| 0xF69F           | SPDIF_TX_AUXBIT_SOURCE                | S/PDIF transmitter auxiliary bits source select  |

| 0xF6A0 to 0xF6AB | SPDIF_TX_CS_LEFT_x                    | S/PDIF transmitter channel status bits (left)    |

| 0xF6B0 to 0xF6BB | SPDIF_TX_CS_RIGHT_x                   | S/PDIF transmitter channel status bits (right)   |

| 0xF6C0 to 0xF6CB | SPDIF_TX_UD_LEFT_x                    | S/PDIF transmitter user data bits (left)         |

| 0xF6D0 to 0xF6DB | SPDIF_TX_UD_RIGHT_x                   | S/PDIF transmitter user data bits (right)        |

| 0xF6E0 to 0xF6EB | SPDIF_TX_VB_LEFT_x                    | S/PDIF transmitter validity bits (left)          |

| 0xF6F0 to 0xF6FB | SPDIF_TX_VB_RIGHT_x                   | S/PDIF transmitter validity bits (right)         |

| 0xF700 to 0xF70B | SPDIF_TX_PB_LEFT_x                    | S/PDIF transmitter parity bits (left)            |

| 0xF710 to 0xF71B | SPDIF_TX_PB_RIGHT_x                   | S/PDIF transmitter parity bits (right)           |

|                  | · · · · · · · · · · · · · · · · · · · |                                                  |

## Table 53. S/PDIF Interface Registers

| Address | Register Name        | Description                               | Reset  | RW |

|---------|----------------------|-------------------------------------------|--------|----|

| 0xF6C9  | SPDIF_TX_UD_LEFT_9   | S/PDIF transmitter user data bits (left)  | 0x0000 | RW |

| 0xF6CA  | SPDIF_TX_UD_LEFT_10  | S/PDIF transmitter user data bits (left)) | 0x0000 | RW |

| 0xF6CB  | SPDIF_TX_UD_LEFT_11  | S/PDIF transmitter user data bits (left)  | 0x0000 | RW |

| 0xF6D0  | SPDIF_TX_UD_RIGHT_0  | S/PDIF transmitter user data bits (right) | 0x0000 | RW |

| 0xF6D1  | SPDIF_TX_UD_RIGHT_1  | S/PDIF transmitter user data bits (right) | 0x0000 | RW |

| 0xF6D2  | SPDIF_TX_UD_RIGHT_2  | S/PDIF transmitter user data bits (right) | 0x0000 | RW |

| 0xF6D3  | SPDIF_TX_UD_RIGHT_3  | S/PDIF transmitter user data bits (right) | 0x0000 | RW |

| 0xF6D4  | SPDIF_TX_UD_RIGHT_4  | S/PDIF transmitter user data bits (right) | 0x0000 | RW |

| 0xF6D5  | SPDIF_TX_UD_RIGHT_5  | S/PDIF transmitter user data bits (right) | 0x0000 | RW |

| 0xF6D6  | SPDIF_TX_UD_RIGHT_6  | S/PDIF transmitter user data bits (right) | 0x0000 | RW |

| 0xF6D7  | SPDIF_TX_UD_RIGHT_7  | S/PDIF transmitter user data bits (right) | 0x0000 | RW |

| 0xF6D8  | SPDIF_TX_UD_RIGHT_8  | S/PDIF transmitter user data bits (right) | 0x0000 | RW |

| 0xF6D9  | SPDIF_TX_UD_RIGHT_9  | S/PDIF transmitter user data bits (right) | 0x0000 | RW |

| 0xF6DA  | SPDIF_TX_UD_RIGHT_10 | S/PDIF transmitter user data bits (right) | 0x0000 | RW |

| 0xF6DB  | SPDIF_TX_UD_RIGHT_11 | S/PDIF transmitter user data bits (right) | 0x0000 | RW |

| 0xF6E0  | SPDIF_TX_VB_LEFT_0   | S/PDIF transmitter validity bits (left)   | 0x0000 | RW |

| 0xF6E1  | SPDIF_TX_VB_LEFT_1   | S/PDIF transmitter validity bits (left)   | 0x0000 | RW |

| 0xF6E2  | SPDIF_TX_VB_LEFT_2   | S/PDIF transmitter validity bits (left)   | 0x0000 | RW |

| 0xF6E3  | SPDIF_TX_VB_LEFT_3   | S/PDIF transmitter validity bits (left)   | 0x0000 | RW |

| 0xF6E4  | SPDIF_TX_VB_LEFT_4   | S/PDIF transmitter validity bits (left)   | 0x0000 | RW |

| 0xF6E5  | SPDIF_TX_VB_LEFT_5   | S/PDIF transmitter validity bits (left)   | 0x0000 | RW |

| 0xF6E6  | SPDIF_TX_VB_LEFT_6   | S/PDIF transmitter validity bits (left)   | 0x0000 | RW |

| 0xF6E7  | SPDIF_TX_VB_LEFT_7   | S/PDIF transmitter validity bits (left)   | 0x0000 | RW |

| 0xF6E8  | SPDIF_TX_VB_LEFT_8   | S/PDIF transmitter validity bits (left)   | 0x0000 | RW |

| 0xF6E9  | SPDIF_TX_VB_LEFT_9   | S/PDIF transmitter validity bits (left)   | 0x0000 | RW |

| 0xF6EA  | SPDIF_TX_VB_LEFT_10  | S/PDIF transmitter validity bits (left)   | 0x0000 | RW |

| 0xF6EB  | SPDIF_TX_VB_LEFT_11  | S/PDIF transmitter validity bits (left)   | 0x0000 | RW |

| 0xF6F0  | SPDIF_TX_VB_RIGHT_0  | S/PDIF transmitter validity bits (right)  | 0x0000 | RW |

| 0xF6F1  | SPDIF_TX_VB_RIGHT_1  | S/PDIF transmitter validity bits (right)  | 0x0000 | RW |

| 0xF6F2  | SPDIF_TX_VB_RIGHT_2  | S/PDIF transmitter validity bits (right)  | 0x0000 | RW |

| 0xF6F3  | SPDIF_TX_VB_RIGHT_3  | S/PDIF transmitter validity bits (right)  | 0x0000 | RW |

| 0xF6F4  | SPDIF_TX_VB_RIGHT_4  | S/PDIF transmitter validity bits (right)  | 0x0000 | RW |

| 0xF6F5  | SPDIF_TX_VB_RIGHT_5  | S/PDIF transmitter validity bits (right)  | 0x0000 | RW |

| 0xF6F6  | SPDIF_TX_VB_RIGHT_6  | S/PDIF transmitter validity bits (right)  | 0x0000 | RW |

| 0xF6F7  | SPDIF_TX_VB_RIGHT_7  | S/PDIF transmitter validity bits (right)  | 0x0000 | RW |

| 0xF6F8  | SPDIF_TX_VB_RIGHT_8  | S/PDIF transmitter validity bits (right)  | 0x0000 | RW |

| 0xF6F9  | SPDIF_TX_VB_RIGHT_9  | S/PDIF transmitter validity bits (right)  | 0x0000 | RW |

| 0xF6FA  | SPDIF_TX_VB_RIGHT_10 | S/PDIF transmitter validity bits (right)  | 0x0000 | RW |

| 0xF6FB  | SPDIF_TX_VB_RIGHT_11 | S/PDIF transmitter validity bits (right)  | 0x0000 | RW |

| 0xF700  | SPDIF_TX_PB_LEFT_0   | S/PDIF transmitter parity bits (left)     | 0x0000 | RW |

| 0xF701  | SPDIF_TX_PB_LEFT_1   | S/PDIF transmitter parity bits (left)     | 0x0000 | RW |

| 0xF702  | SPDIF_TX_PB_LEFT_2   | S/PDIF transmitter parity bits (left)     | 0x0000 | RW |

| 0xF703  | SPDIF_TX_PB_LEFT_3   | S/PDIF transmitter parity bits (left)     | 0x0000 | RW |

| 0xF704  | SPDIF_TX_PB_LEFT_4   | S/PDIF transmitter parity bits (left)     | 0x0000 | RW |

| 0xF705  | SPDIF_TX_PB_LEFT_5   | S/PDIF transmitter parity bits (left)     | 0x0000 | RW |

| 0xF706  | SPDIF_TX_PB_LEFT_6   | S/PDIF transmitter parity bits (left)     | 0x0000 | RW |

| 0xF707  | SPDIF_TX_PB_LEFT_7   | S/PDIF transmitter parity bits (left)     | 0x0000 | RW |

| 0xF708  | SPDIF_TX_PB_LEFT_8   | S/PDIF transmitter parity bits (left)     | 0x0000 | RW |

| 0xF709  | SPDIF_TX_PB_LEFT_9   | S/PDIF transmitter parity bits (left)     | 0x0000 | RW |

| 0xF70A  | SPDIF_TX_PB_LEFT_10  | S/PDIF transmitter parity bits (left)     | 0x0000 | RW |

| 0xF70B  | SPDIF_TX_PB_LEFT_11  | S/PDIF transmitter parity bits (left)     | 0x0000 | RW |

| 0xF710  | SPDIF_TX_PB_RIGHT_0  | S/PDIF transmitter parity bits (right)    | 0x0000 | RW |

| 0xF711  | SPDIF_TX_PB_RIGHT_1  | S/PDIF transmitter parity bits (right)    | 0x0000 | RW |

|         |                      |                                           |        |    |

# **CONTROL REGISTER DETAILS**

## PLL CONFIGURATION REGISTERS

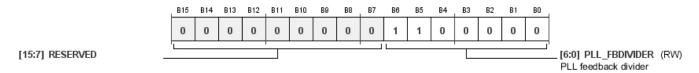

### PLL Feedback Divider Register

### Address: 0xF000, Reset: 0x0060, Name: PLL\_CTRL0

This register is the value of the feedback divider in the PLL. This value effectively multiplies the frequency of the input clock to the PLL, creating the output system clock, which clocks the DSP core and other digital circuit blocks. The format of the value stored in this register is binary integer in 7.0 format. For example, the default feedback divider value of 96 is stored as 0x60. The value written to this register does not take effect until Register 0xF003 (PLL\_ENABLE), Bit 0 (PLL\_ENABLE) changes state from 0b0 to 0b1.

### Table 65. Bit Descriptions for PLL\_CTRL0

| Bits   | Bit Name      | Settings | Description                                                                                                                                                                                                                                                                                                                                                                                                               | Reset | Access |

|--------|---------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------|

| [15:7] | RESERVED      |          |                                                                                                                                                                                                                                                                                                                                                                                                                           | 0x0   | RW     |

| [6:0]  | PLL_FBDIVIDER |          | PLL feedback divider. This is the value of the feedback divider in the PLL, which<br>effectively multiplies the frequency of the input clock to the PLL, creating the<br>output system clock, which clocks the DSP core and other digital circuit<br>blocks. The format of the value stored in this register is binary integer in 7.0<br>format. For example, the default feedback divider value of 96 is stored as 0x60. | 0x60  | RW     |

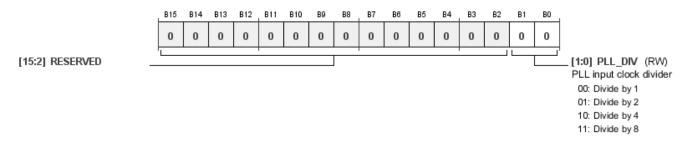

### PLL Prescale Divider Register

### Address: 0xF001, Reset: 0x0000, Name: PLL\_CTRL1

This register sets the input prescale divider for the PLL. The value written to this register does not take effect until Register 0xF003 (PLL\_ENABLE), Bit 0 (PLL\_ENABLE) changes state from 0b0 to 0b1.

### Table 66. Bit Descriptions for PLL\_CTRL1

| Bits   | Bit Name | Settings | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Reset | Access |

|--------|----------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------|

| [15:2] | RESERVED |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0x0   | RW     |

| [1:0]  | PLL_DIV  | 00       | PLL input clock divider. This prescale clock divider creates the PLL input clock from the externally input master clock. The nominal frequency of the PLL input is 3.072 MHz. Therefore, if the input master clock frequency is 3.072 MHz, set the prescale clock divider to divide by 1. If the input clock is 12.288 MHz, set the prescale clock divider to divide by 4. The goal is to make the input to the PLL as close to 3.072 MHz as possible. Divide by 1 | 0x0   | RW     |

|        |          | 01       | Divide by 2                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |        |

|        |          | 10       | Divide by 4                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |        |

|        |          | 11       | Divide by 8                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |        |

# **Data Sheet**

# ADAU1452/ADAU1451/ADAU1450

| Bits  | Bit Name     | Settings | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Reset | Access |

|-------|--------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------|

| 4     | CLK_GEN3_SRC |          | Reference source for Clock Generator 3. This bit selects the reference of Clock Generator 3. If set to use an external reference clock, Bits[3:0] define the source pin. Otherwise, the PLL output is used as the reference clock. When an external reference clock is used for Clock Generator 3, the resulting base output frequency of Clock Generator 3 is the frequency of the input reference clock multiplied by the Clock Generator 3 numerator, divided by 1024. For example: if Bit 4 (CLK_GEN3_SRC) = 0b1 (an external reference clock is used); Bits[3:0] (FREF_PIN) = 0b1110 (the input signal of the S/PDIF receiver is used as the reference source); the sample rate of the S/PDIF input signal = 48 kHz; and the numerator of Clock Generator 3 is 48 kHz × 2048/1024 = 96 kHz. | 0x0   | RW     |

|       |              | 0        | Reference signal provided by PLL output; multiply the frequency of that signal by M and divide it by N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |        |

|       |              | 1        | Reference signal provided by the signal input to the hardware pin defined<br>by Bits[3:0] (FREF_PIN); multiply the frequency of that signal by N (and<br>then divide by 1024) to get the resulting sample rate; M is ignored                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |        |

| [3:0] | FREF_PIN     |          | Input reference for Clock Generator 3. If Clock Generator 3 is set up to lock to an external reference clock (Bit 4 (CLK_GEN3_SRC) = 0b1), these bits allow the user to specify which pin is receiving the reference clock. The signal input to the corresponding pin should be a 50% duty cycle square wave clock representing the reference sample rate.                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0xE   | RW     |

|       |              | 0000     | Input reference source is SS_M/MP0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |        |

|       |              | 0001     | Input reference source is MOSI_M/MP1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |        |

|       |              | 0010     | Input reference source is SCL_M/SCLK_M/MP2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |        |

|       |              | 0011     | Input reference source is SDA_M/MISO_M/MP3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |        |

|       |              | 0100     | Input reference source is LRCLK_OUT0/MP4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |        |

|       |              | 0101     | Input reference source is LRCLK_OUT1/MP5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |        |

|       |              | 0110     | Input reference source is MP6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       |        |

|       |              | 0111     | Input reference source is MP7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       |        |

|       |              | 1000     | Input reference source is LRCLK_OUT2/MP8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |        |

|       |              | 1001     | Input reference source is LRCLK_OUT3/MP9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |        |

|       |              | 1010     | Input reference source is LRCLK_IN0/MP10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |        |

|       |              | 1011     | Input reference source is LRCLK_IN1/MP11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |        |

|       |              | 1100     | Input reference source is LRCLK_IN2/MP12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |        |

|       |              | 1101     | Input reference source is LRCLK_IN3/MP13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |        |

|       |              | 1110     | Input reference source is S/PDIF receiver (recovered frame clock)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |        |

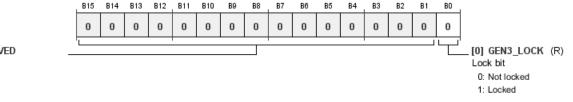

### Lock Bit for Clock Generator 3 Input Reference Register

### Address: 0xF027, Reset: 0x0000, Name: CLK\_GEN3\_LOCK

This register monitors whether or not Clock Generator 3 has locked to its reference clock source, regardless of whether it is coming from the PLL output or from an external reference signal, which is configured in Register 0xF026, Bit 4 (CLK\_GEN3\_SRC).

[15:1] RESERVED

### Table 79. Bit Descriptions for CLK\_GEN3\_LOCK

| Bits   | Bit Name  | Settings | Description | Reset | Access |

|--------|-----------|----------|-------------|-------|--------|

| [15:1] | RESERVED  |          |             | 0x0   | RW     |

| 0      | GEN3_LOCK |          | Lock bit.   | 0x0   | R      |

|        |           | 0        | Not locked  |       |        |

|        |           | 1        | Locked      |       |        |

| Bits | Bit Name      | Settings       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Reset | Access |

|------|---------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------|

| 10   | CLK_GEN1_PWR  |                | Clock Generator 1 power enable. When this bit is disabled, Clock Generator 1<br>is disabled and ceases to output audio clocks. Any LRCLK_OUTx, LRCLK_INx<br>or BCLK_OUTx, BCLK_INx pins that are configured to output clocks<br>generated by Clock Generator 1 output a logic low signal while Clock<br>Generator 1 is disabled. Any functional block in hardware, including the DSP<br>core, that is configured to be clocked by Clock Generator 1 ceases to function<br>when this bit is disabled. | 0x0   | RW     |

|      |               | 0              | Power disabled<br>Power enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |        |

| 9    | ASRCBANK1_PWR |                | ASRC 4, ASRC 5, ASRC 6, ASRC 7 power enable. When this bit is disabled, ASRC Channel 8 to Channel 15 are disabled, and their output data streams cease.                                                                                                                                                                                                                                                                                                                                              | 0x0   | RW     |

|      |               | 0              | Power disabled<br>Power enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |        |

| 8    | ASRCBANK0_PWR | 1              | ASRC 0, ASRC 1, ASRC 2, ASRC 3 power enable. When this bit is disabled, ASRC Channel 0 to Channel 7 are disabled, and their output data streams cease.                                                                                                                                                                                                                                                                                                                                               | 0x0   | RW     |

|      |               | 0              | Power disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |        |

|      |               | 1              | Power enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |        |

| 7    | SOUT3_PWR     |                | SDATA_OUT3 power enable. When this bit is disabled, the SDATA_OUT3 pin and associated serial port circuitry are also disabled. LRCLK_OUT3 and BCLK_OUT3 are not affected.                                                                                                                                                                                                                                                                                                                            | 0x0   | RW     |

|      | 0             | Power disabled |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |        |

|      |               | 1              | Power enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |        |

| 6    | 6 SOUT2_PWR   |                | SDATA_OUT2 power enable. When this bit is disabled, the SDATA_OUT2 pin and associated serial port circuitry is disabled. LRCLK_OUT2 and BCLK_OUT2 are not affected.                                                                                                                                                                                                                                                                                                                                  | 0x0   | RW     |

|      |               | 0              | Power disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |        |

|      |               | 1              | Power enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |        |

| 5    | 5 SOUT1_PWR   |                | SDATA_OUT1 power enable. When this bit is disabled, the SDATA_OUT1 pin and associated serial port circuitry are also disabled. LRCLK_OUT1 and BCLK_OUT1 are not affected.                                                                                                                                                                                                                                                                                                                            | 0x0   | RW     |

|      |               | 0              | Power disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |        |

|      |               | 1              | Power enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |        |

| 4    | SOUT0_PWR     |                | SDATA_OUT0 power enable. When this bit is disabled, the SDATA_OUT0 pin and associated serial port circuitry are disabled. LRCLK_OUT0 and BCLK_OUT0 are not affected.                                                                                                                                                                                                                                                                                                                                 | 0x0   | RW     |

|      |               | 0              | Power disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |        |

|      |               | 1              | Power enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |        |

| 3    | SIN3_PWR      |                | SDATA_IN3 power enable. When this bit is disabled, the SDATA_IN3 pin and associated serial port circuitry are disabled. LRCLK_IN3 and BCLK_IN3 are not affected.                                                                                                                                                                                                                                                                                                                                     | 0x0   | RW     |

|      |               | 0              | Power disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |        |

|      |               | 1              | Power enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |        |

| 2    | SIN2_PWR      |                | SDATA_IN2 power enable. When this bit is disabled, the SDATA_IN2 pin and associated serial port circuitry are disabled. LRCLK_IN2 and BCLK_IN2 are not affected.                                                                                                                                                                                                                                                                                                                                     | 0x0   | RW     |

|      |               | 0              | Power disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |        |

|      |               | 1              | Power enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |        |

| 1    | SIN1_PWR      |                | SDATA_IN1 power enable. When this bit is disabled, the SDATA_IN1 pin and associated serial port circuitry are disabled. The LRCLK_IN1 and BCLK_IN1 pins are not affected.                                                                                                                                                                                                                                                                                                                            | 0x0   | RW     |

|      |               | 0              | Power disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |        |

|      | -             | 1              | Power enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |        |

| 0    | SIN0_PWR      |                | SDATA_IN0 power enable. When this bit is disabled, the SDATA_IN0 pin<br>and associated serial port circuitry are disabled. The LRCLK_IN0 and<br>BCLK_IN0 pins are not affected.                                                                                                                                                                                                                                                                                                                      | 0x0   | RW     |

|      |               | 0              | Power disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |        |

|      |               | 1              | Power enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |        |

### SERIAL PORT CONFIGURATION REGISTERS

### Serial Port Control 0 Register

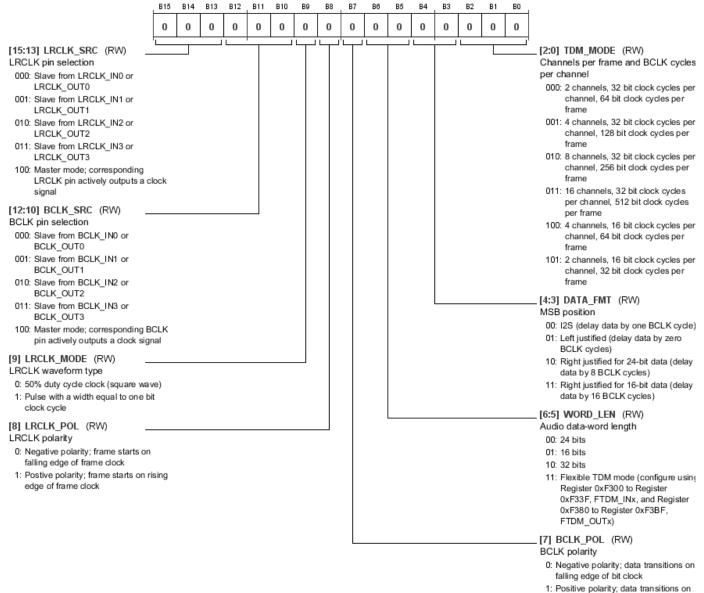

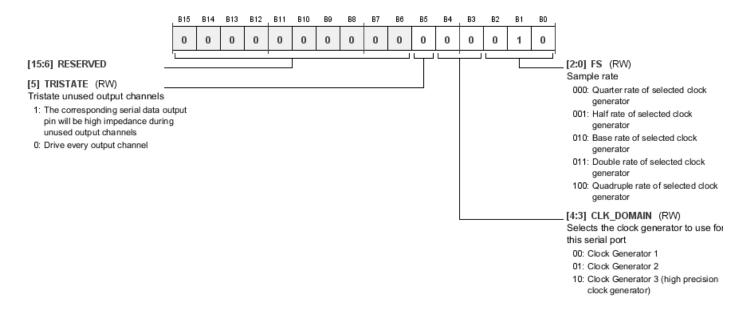

### Address: 0xF200 to 0xF21C (Increments of 0x4), Reset: 0x0000, Name: SERIAL\_BYTE\_x\_0

These eight registers configure several settings for the corresponding serial input and serial output ports. Channel count, MSB position, data-word length, clock polarity, clock sources, and clock type are configured using these registers. On the input side, Register 0xF200 (SERIAL\_BYTE\_0\_0) corresponds to SDATA\_IN0; Register 0xF204 (SERIAL\_BYTE\_1\_0) corresponds to SDATA\_IN1; Register 0xF208 (SERIAL\_BYTE\_2\_0) corresponds to SDATA\_IN2; and Register 0xF20C (SERIAL\_BYTE\_3\_0) corresponds to SDATA\_IN3. On the output side, Register 0xF210 (SERIAL\_BYTE\_4\_0) corresponds to SDATA\_OUT0; Register 0xF214 (SERIAL\_BYTE\_5\_0) corresponds to SDATA\_OUT1; Register 0xF218 (SERIAL\_BYTE\_6\_0) corresponds to SDATA\_OUT2; and Register 0xF21C (SERIAL\_BYTE\_7\_0) corresponds to SDATA\_OUT3.

Positive polarity; data transitions or rising edge of bit clock

### Table 86. Bit Descriptions for SERIAL\_BYTE\_x\_0

| Bits    | Bit Name   | Settings                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Reset | Access |

|---------|------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------|

| [15:13] | LRCLK_SRC  | 000<br>001<br>010<br>011<br>100 | LRCLK pin selection. These bits configure whether the corresponding<br>serial port is a frame clock master or slave. When configured as a master,<br>the corresponding LRCLK pin (LRCLK_INx for SDATA_IN pins and<br>LRCLK_OUTx for SDATA_OUT pins) with the same number as the serial<br>port (for example, LRCLK_OUT0 for SDATA_OUT0) actively drives out a<br>clock signal. When configured as a slave, the serial port can receive its<br>clock signal from any of the four corresponding LRCLK pins (LRCLK_INx<br>pins for SDATA_INx pins or LRCLK_OUTx pins for SDATA_OUTx pins).<br>Slave from LRCLK_IN0 or LRCLK_OUT0<br>Slave from LRCLK_IN1 or LRCLK_OUT1<br>Slave from LRCLK_IN2 or LRCLK_OUT2<br>Slave from LRCLK_IN3 or LRCLK_OUT3<br>Master mode; corresponding LRCLK pin actively outputs a clock signal                                       | 0x0   | RW     |

| [12:10] | BCLK_SRC   | 000<br>001<br>010<br>011<br>100 | BCLK pin selection. These bits configure whether the corresponding serial<br>port is a bit clock master or slave. When configured as a master, the<br>corresponding BCLK pin (BCLK_INx for SDATA_INx pins and BCLK_OUTx<br>for SDATA_OUTx pins) with the same number as the serial port (for example,<br>BCLK_OUT0 for SDATA_OUT0) actively drives out a clock signal. When<br>configured as a slave, the serial port can receive its clock signal from any<br>of the four corresponding BCLK pins (BCLK_INx pins for SDATA_INx pins or<br>BCLK_OUTx pins for SDATA_OUTx pins).<br>Slave from BCLK_IN0 or BCLK_OUT0<br>Slave from BCLK_IN1 or BCLK_OUT1<br>Slave from BCLK_IN2 or BCLK_OUT2<br>Slave from BCLK_IN3 or BCLK_OUT3<br>Master mode; corresponding BCLK pin actively outputs a clock signal                                                        | 0x0   | RW     |

| 9       | LRCLK_MODE | 0                               | LRCLK waveform type. The frame clock can be a 50/50 duty cycle square<br>wave or a short pulse.<br>50% duty cycle clock (square wave)<br>Pulse with a width equal to one bit clock cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0x0   | RW     |

| 8       | LRCLK_POL  | 0                               | LRCLK polarity. This bit sets the frame clock polarity on the corresponding serial port. Negative polarity means that the frame starts on the falling edge of the frame clock. This conforms to the I <sup>2</sup> S standard audio format. Negative polarity; frame starts on falling edge of frame clock Positive polarity; frame starts on rising edge of frame clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0x0   | RW     |

| 7       | BCLK_POL   | 0                               | BCLK polarity. This bit sets the bit clock polarity on the corresponding<br>serial port. Negative polarity means that the data signal transitions on the<br>falling edge of the bit clock. This conforms to the l <sup>2</sup> S standard audio format.<br>Negative polarity; data transitions on falling edge of bit clock<br>Positive polarity; data transitions on rising edge of bit clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0x0   | RW     |

| [6:5]   | WORD_LEN   | 00<br>01<br>10<br>11            | Audio data-word length. These bits set the word length of the audio data<br>channels on the corresponding serial port. For serial input ports, if the<br>input data has more words than the length as configured by these bits,<br>the extra data bits are ignored. For output serial ports, if the word length,<br>as configured by these bits, is shorter than the data length coming from<br>the data source (the DSP, ASRCs, S/PDIF receiver, PDM inputs, or serial<br>inputs), the extra data bits are truncated and output as 0s. If Bits[6:5]<br>(WORD_LEN) are set to 0b10 for 32-bit mode, the corresponding 32-bit<br>input or output cells are required in SigmaStudio.<br>24 bits<br>16 bits<br>32 bits<br>Flexible TDM mode (configure using Register 0xF300 to Register 0xF33F,<br>FTDM_INx, and Register 0xF380 to Register 0xF3BF, FTDM_OUTx) | 0x0   | RW     |

| Bits  | Bit Name                                                          | Settings                                                         | Description                                                                                                                                                                          | Reset | Access |  |

|-------|-------------------------------------------------------------------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------|--|

| [4:3] | DATA_FMT                                                          |                                                                  | MSB position. These bits set the positioning of the data in the frame on                                                                                                             | 0x0   | RW     |  |

|       |                                                                   |                                                                  | the corresponding serial port.                                                                                                                                                       |       |        |  |

|       |                                                                   | 00                                                               | I <sup>2</sup> S (delay data by one BCLK cycle)                                                                                                                                      |       |        |  |

|       |                                                                   | 01                                                               | 01 Left justified (delay data by zero BCLK cycles)                                                                                                                                   |       |        |  |

|       |                                                                   | 10 Right justified for 24-bit data (delay data by 8 BCLK cycles) |                                                                                                                                                                                      |       |        |  |

|       | 11 Right justified for 16-bit data (delay data by 16 BCLK cycles) |                                                                  |                                                                                                                                                                                      |       |        |  |

| [2:0] | [2:0] TDM_MODE Ch                                                 |                                                                  | Channels per frame and BCLK cycles per channel. These bits set the number<br>of channels per frame and the number of bit clock cycles per frame on the<br>corresponding serial port. | 0x0   | RW     |  |

|       |                                                                   | 000                                                              | 2 channels, 32 bit clock cycles per channel, 64 bit clock cycles per frame                                                                                                           |       |        |  |