Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 5                                                                        |

| Program Memory Size        | 1.75KB (1K x 14)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 64 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 4x10b; D/A 1x5b                                                      |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 8-VDFN Exposed Pad                                                       |

| Supplier Device Package    | 8-DFN (3x3)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f752-i-mf |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 1: PIC12F752/HV752 FEATURE SUMMARY

| Device     | Flash Program<br>Memory (User)<br>(words) | Self Read/Write<br>Flash Memory | SRAM (bytes) | s0/I | 10-bit A/D (ch) | Comparators | Timers<br>8/16-bit | ССР | Complementary<br>Output Generator<br>(COG) | Shunt Regulator | ХГР |

|------------|-------------------------------------------|---------------------------------|--------------|------|-----------------|-------------|--------------------|-----|--------------------------------------------|-----------------|-----|

| PIC12F752  | 1024                                      | Y                               | 64           | 6    | 4               | 2           | 3/1                | 1   | Y                                          | Ν               | Y   |

| PIC12HV752 | 1024                                      | Y                               | 64           | 6    | 4               | 2           | 3/1                | 1   | Y                                          | Y               | Y   |

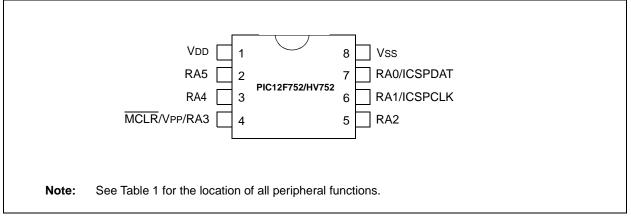

## FIGURE 1: 8-PIN PDIP, SOIC, DFN

#### 2.3 Global SFRs

#### 2.3.1 STATUS REGISTER

The STATUS register, shown in Register 2-1, contains:

- The Arithmetic Status of the ALU

- The Reset Status

- The Bank Select Bits for Data Memory (RAM)

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not

writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS, will clear the upper three bits and set the Z bit. This leaves the STATUS register as `000u u1uu' (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any Status bits. For other instructions not affecting any Status bits, see Section 16.0 "Instruction Set Summary".

|       | • • • • • • |       |     |     |       |                   |                  |

|-------|-------------|-------|-----|-----|-------|-------------------|------------------|

| R/W-0 | R/W-0       | R/W-0 | R-1 | R-1 | R/W-x | R/W-x             | R/W-x            |

| IRP   | RP1         | RP0   | TO  | PD  | Z     | DC <sup>(1)</sup> | C <sup>(1)</sup> |

| bit 7 |             |       |     |     |       |                   | bit 0            |

| Legend:      |                                                                                         |                                                                                                           |                                      |                                                              |

|--------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--------------------------------------|--------------------------------------------------------------|

| R = Readab   | le bit                                                                                  | W = Writable bit                                                                                          | U = Unimplemented bit, r             | ead as '0'                                                   |

| -n = Value a | t POR                                                                                   | '1' = Bit is set                                                                                          | '0' = Bit is cleared                 | x = Bit is unknown                                           |

| bit 7        | <b>IRP:</b> Register<br>1 = Bank 2, 3<br>0 = Bank 0, 1                                  | ,                                                                                                         | ndirect addressing)                  |                                                              |

| bit 6        | <b>RP1:</b> Registe<br>00 = Bank 0 (<br>01 = Bank 1 (<br>10 = Bank 2 (<br>11 = Bank 3 ( | 80h-FFh)<br>100h-17Fh)                                                                                    | direct addressing)                   |                                                              |

| bit 5        | <b>RP0:</b> Registe<br>1 = Bank 1 (8<br>0 = Bank 0 (0                                   | ,                                                                                                         | lirect addressing)                   |                                                              |

| bit 4        | •                                                                                       | bit<br>er-up, CLRWDT instruction c<br>ne-out occurred                                                     | r SLEEP instruction                  |                                                              |

| bit 3        |                                                                                         | own bit<br>er-up or by the CLRWDT ins<br>ion of the SLEEP instruction                                     |                                      |                                                              |

| bit 2        | <b>Z:</b> Zero bit<br>1 = The resul                                                     | t of an arithmetic or logic op<br>t of an arithmetic or logic op                                          | peration is zero                     |                                                              |

| bit 1        | 1 = A carry-or                                                                          | ry/Borrow bit <sup>(2)</sup> (ADDWF, ADI<br>ut from the 4th low-order bit<br>put from the 4th low-order b | of the result occurred               | , For $\overline{\text{Borrow}}$ , the polarity is reversed. |

| bit 0        | 1 = A carry-ou                                                                          | ow bit <sup>(2)</sup> (ADDWF, ADDLW, st<br>the Most Significant<br>but from the Most Significar           |                                      |                                                              |

|              | The C and DC bits of instructions for exa                                               |                                                                                                           | git Borrow out bit, respectively, in | subtraction. See the SUBLW and SUBW                          |

2: For Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high-order or low-order bit of the source register.

## 4.3 System Clock Output

The CLKOUT pin is available for general purpose I/O or system clock output. The CLKOUTEN bit of the Configuration Word controls the function of the CLKOUT pin.

When the CLKOUTEN bit is cleared, the CLKOUT pin is driven by the selected internal oscillator frequency divided by 4. The corresponding I/O pin always reads '0' in this configuration.

The CLKOUT signal may be used to provide a clock for external circuitry, synchronization, calibration, test or other application requirements.

When the  $\overline{\text{CLKOUTEN}}$  bit is set, the system clock out function is disabled and the CLKOUT pin is available for general purpose I/O.

## 4.4 Oscillator Delay upon Wake-Up, Power-Up, and Base Frequency Change

In applications where the OSCTUNE register is used to shift the HFINTOSC frequency, the application should not expect the frequency to stabilize immediately. In this case, the frequency may shift gradually toward the new value. The time for this frequency shift is less than eight cycles of the base frequency.

A short delay is invoked upon power-up and when waking from sleep to allow the memory bias circuitry to stabilize. Table 4-1 shows examples where the oscillator delay is invoked.

## TABLE 4-1: OSCILLATOR DELAY EXAMPLES

| Switch From | Switch To | Frequency       | Oscillator Delay                          |

|-------------|-----------|-----------------|-------------------------------------------|

| Sleep/POR   | INTOSC    | 31 kHz to 8 MHz | 10 $\mu$ s internal delay to allow memory |

| Sleep/POR   | EC        | DC – 20 MHz     | bias to stabilize.                        |

|                                         |     | -                  |                                                       |                                    |         | -       |         |  |

|-----------------------------------------|-----|--------------------|-------------------------------------------------------|------------------------------------|---------|---------|---------|--|

| U-0                                     | U-0 | R/W-0/0            | R/W-0/0                                               | R/W-0/0                            | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |

| —                                       | _   | IOCAP5             | IOCAP4                                                | IOCAP3                             | IOCAP2  | IOCAP1  | IOCAP0  |  |

| bit 7                                   |     |                    |                                                       |                                    |         |         | bit C   |  |

|                                         |     |                    |                                                       |                                    |         |         |         |  |

| Legend:                                 |     |                    |                                                       |                                    |         |         |         |  |

| R = Readable bit W = Writable bit       |     |                    | t                                                     | U = Unimplemented bit, read as '0' |         |         |         |  |

| u = Bit is unchanged x = Bit is unknown |     |                    | -n/n = Value at POR and BOR/Value at all other Resets |                                    |         |         |         |  |

| '1' = Bit is set                        |     | '0' = Bit is clear | ed                                                    |                                    |         |         |         |  |

|                                         |     |                    |                                                       |                                    |         |         |         |  |

#### REGISTER 5-8: IOCAP: INTERRUPT-ON-CHANGE POSITIVE EDGE REGISTER

bit 7-6 Unimplemented: Read as '0'

bit 5-0

IOCAP<5:0>: Interrupt-on-Change Positive Edge Enable bits

1 = Interrupt-on-Change enabled on the pin for a positive going edge. Associated Status bit and interrupt flag will be set upon detecting an edge.

0 = Interrupt-on-Change disabled for the associated pin.

#### REGISTER 5-9: IOCAN: INTERRUPT-ON-CHANGE NEGATIVE EDGE REGISTER

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   | IOCAN5  | IOCAN4  | IOCAN3  | IOCAN2  | IOCAN1  | IOCAN0  |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 Unimplemented: Read as '0'

bit 5-0

bit 5-0

IOCAN<5:0>: Interrupt-on-Change Negative Edge Enable bits

- 1 = Interrupt-on-Change enabled on the pin for a negative going edge. Associated Status bit and interrupt flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin.

#### REGISTER 5-10: IOCAF: INTERRUPT-ON-CHANGE FLAG REGISTER

| U-0   | U-0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 |

|-------|-----|------------|------------|------------|------------|------------|------------|

| —     | —   | IOCAF5     | IOCAF4     | IOCAF3     | IOCAF2     | IOCAF1     | IOCAF0     |

| bit 7 |     |            |            |            |            |            | bit 0      |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS - Bit is set in hardware                           |

bit 7-6 Unimplemented: Read as '0'

IOCAF<5:0>: Interrupt-on-Change Flag bits

1 = An enabled change was detected on the associated pin.

- Set when IOCAPx = 1 and a rising edge was detected on RBx, or when IOCANx = 1 and a falling edge was detected on RAx.

- 0 = No change was detected, or the user cleared the detected change.

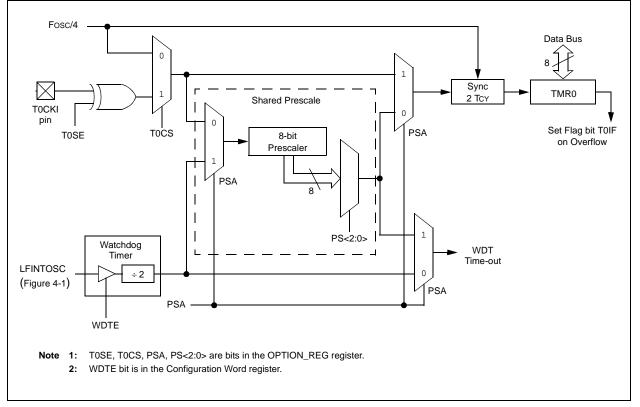

## 6.0 TIMER0 MODULE

The Timer0 module is an 8-bit timer/counter with the following features:

- 8-Bit Timer/Counter Register (TMR0)

- 8-Bit Prescaler (shared with Watchdog Timer)

- Programmable Internal or External Clock Source

- Programmable External Clock Edge Selection

- Interrupt-on-Overflow

Figure 6-1 is a block diagram of the Timer0 module.

## 6.1 Timer0 Operation

When used as a timer, the Timer0 module can be used as either an 8-bit timer or an 8-bit counter.

#### 6.1.1 8-BIT TIMER MODE

When used as a timer, the Timer0 module will increment every instruction cycle (without prescaler). Timer mode is selected by clearing the T0CS bit of the OPTION register to '0'.

When TMR0 is written, the increment is inhibited for two instruction cycles immediately following the write.

Note: The value written to the TMR0 register can be adjusted, in order to account for the two instruction-cycle delay when TMR0 is written.

#### 6.1.2 8-BIT COUNTER MODE

When used as a counter, the Timer0 module will increment on every rising or falling edge of the T0CKI pin. The incrementing edge is determined by the T0SE bit of the OPTION\_REG register. Counter mode is selected by setting the T0CS bit of the OPTION register to '1'.

## FIGURE 6-1: TIMER0 WITH SHARED PRESCALE BLOCK DIAGRAM

#### 10.3.2 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP1 module for standard PWM operation:

- 1. Disable the CCP1 pin output driver by setting the associated TRIS bit

- 2. Load the PR2 register with the PWM period value

- 3. Configure the CCP1 module for the PWM mode by loading the CCP1CON register with the appropriate values

- Load the CCPR1L register and the DC1B<1:0> bits of the CCP1CON register, with the PWM duty cycle value

- 5. Configure and start Timer2:

- Clear the TMR2IF interrupt flag bit of the PIR1 register (see Note below)

- Configure the T2CKPS bits of the T2CON register with the Timer prescale value

- Enable the Timer by setting the TMR2ON bit of the T2CON register

- 6. Enable PWM output pin:

- Wait until the Timer overflows and the TMR2IF bit of the PIR1 register is set. See Note below

- Enable the CCP1 pin output driver by clearing the associated TRIS bit

- **Note:** In order to send a complete duty cycle and period on the first PWM output, the above steps must be included in the setup sequence. If it is not critical to start with a complete PWM signal on the first output, then step 6 may be ignored.

#### 10.3.3 PWM PERIOD

The PWM period is specified by the PR2 register of Timer2. The PWM period can be calculated using the formula of Equation 10-1.

#### EQUATION 10-1: PWM PERIOD

$PWM Period = [(PR2) + 1] \bullet 4 \bullet Tosc \bullet$ (TMR2 Prescale Value)

Note 1: Tosc = 1/Fosc

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCP1 pin is set (exception: If the PWM duty cycle = 0%, the pin will not be set)

- The PWM duty cycle is latched from CCPR1L into CCPR1H

Note: The Timer postscaler (see Section 8.1 "Timer2 Operation") is not used in the determination of the PWM frequency.

## 10.3.4 PWM DUTY CYCLE

The PWM duty cycle is specified by writing a 10-bit value to multiple registers: CCPR1L register and DC1B<1:0> bits of the CCP1CON register. The CCPR1L contains the eight MSbs and the DC1B<1:0> bits of the CCP1CON register contain the two LSbs. CCPR1L and DC1B<1:0> bits of the CCP1CON register contain the two LSbs. CCPR1L and DC1B<1:0> bits of the CCP1CON register can be written to at any time. The duty cycle value is not latched into CCPR1H until after the period completes (i.e. a match between PR2 and TMR2 registers occurs). While using the PWM, the CCPR1H register is read-only.

Equation 10-2 is used to calculate the PWM pulse width.

Equation 10-3 is used to calculate the PWM duty cycle ratio.

#### EQUATION 10-2: PULSE WIDTH

$$Pulse Width = (CCPR1L:CCP1CON < 5:4>) \bullet$$

TOSC • (TMR2 Prescale Value)

## EQUATION 10-3: DUTY CYCLE RATIO

$Duty Cycle Ratio = \frac{(CCPRxL:CCPxCON < 5:4>)}{4(PRx + 1)}$

The CCPR1H register and a 2-bit internal latch are used to double buffer the PWM duty cycle. This double buffering is essential for glitchless PWM operation.

The 8-bit timer TMR2 register is concatenated with either the 2-bit internal system clock (FOSC), or two bits of the prescaler, to create the 10-bit time base. The system clock is used if the Timer2 prescaler is set to 1:1.

When the 10-bit time base matches the CCPR1H and 2-bit latch, then the CCP1 pin is cleared (see Figure 10-4).

#### 11.8 Auto-Shutdown Control

Auto-shutdown is a method to immediately override the COG output levels with specific overrides that allow for safe shutdown of the circuit.

The shutdown state can be either cleared automatically or held until cleared by software.

#### 11.8.1 SHUTDOWN

The shutdown state can be entered by either of the following two mechanisms:

- Software generated

- External Input

#### 11.8.1.1 Software Generated Shutdown

Setting the GxASDE bit of the COGxASD register will force the COG into the shutdown state.

When auto-restart is disabled, the shutdown state will persist as long as the GxASDE bit is set.

When auto-restart is enabled, the GxASDE bit will clear automatically and resume operation on the next rising event. See Figure 11-5.

#### 11.8.1.2 External Shutdown Source

External shutdown inputs provide the fastest way to safely suspend COG operation in the event of a fault condition. When any of the selected shutdown inputs goes true, the output drive latches are reset and the COG outputs will immediately go to the selected override levels without software delay.

Any combination of four input sources can be selected to cause a shutdown condition. The four sources include:

- HLTimer1 output

- C2OUT (low true)

- C1OUT (low true)

- COG1FLT pin (low true)

Shutdown inputs are selected independently with bits <3:0> of the COGxASD register (Register 11-3).

| Note: | Shutdo                                    | own inputs | are leve | l sen | sitive, not |  |  |  |

|-------|-------------------------------------------|------------|----------|-------|-------------|--|--|--|

|       | edge sensitive. The shutdown state cannot |            |          |       |             |  |  |  |

|       | be cleared as long as the shutdown input  |            |          |       |             |  |  |  |

|       | level                                     | persists,  | except   | by    | disabling   |  |  |  |

|       | auto-s                                    | hutdown,   |          | -     | -           |  |  |  |

#### 11.8.2 PIN OVERRIDE LEVELS

The levels driven to the output pins, while the shutdown input is true, are controlled by the GxASDL0 and GxASDL1 bits of the COGxASD register (Register 11-3). GxASDL0 controls the GxOUT0 override level and GxASDL1 controls the GxOUT1 override level. The control bit logic level corresponds to the output logic drive level while in the shutdown state.

Note: The polarity control does not apply to the override level.

#### 11.8.3 AUTO-SHUTDOWN RESTART

After an auto-shutdown event has occurred, there are two ways to have the module resume operation:

- Software controlled

- Auto-restart

The restart method is selected with the GxARSEN bit of the COGxASD register. Waveforms of a software controlled automatic restart are shown in Figure 11-5.

#### 11.8.3.1 Software Controlled Restart

When the GxARSEN bit of the COGxASD register is cleared, the COG must be restarted after an auto-shutdown event by software.

The COG will resume operation on the first rising event after the GxASDE bit is cleared. Clearing the shutdown state requires all selected shutdown inputs to be false, otherwise, the GxASDE bit will remain set.

#### 11.8.3.2 Auto-Restart

When the GxARSEN bit of the COGxASD register is set, then the COG will restart from the auto-shutdown state automatically.

The GxASDE bit will clear automatically and the COG will resume operation on the first rising event after all selected shutdown inputs go false.

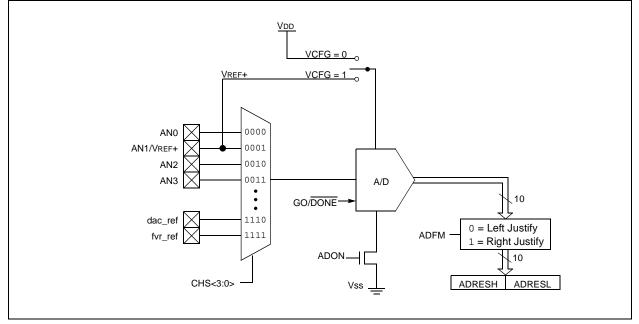

# 12.0 ANALOG-TO-DIGITAL CONVERTER (ADC) MODULE

The Analog-to-Digital Converter (ADC) allows conversion of an analog input signal to a 10-bit binary representation of that signal. This device uses analog inputs, which are multiplexed into a single sample and hold circuit. The output of the sample and hold is connected to the input of the converter. The converter generates a 10-bit binary result via successive approximation and stores the conversion result into the ADC result registers (ADRESL and ADRESH).

The ADC voltage reference is software selectable to either VDD or a voltage applied to the external reference pins.

The ADC can generate an interrupt upon completion of a conversion. This interrupt can be used to wake-up the device from Sleep.

Figure 12-1 shows the block diagram of the ADC.

| Note: | The ADRESL and ADRESH registers are |

|-------|-------------------------------------|

|       | read-only.                          |

## FIGURE 12-1: ADC BLOCK DIAGRAM

# 12.3 ADC Control Registers

## REGISTER 12-1: ADCON0: A/D CONTROL REGISTER 0

| R/W-0        | R/W-0                                                | R/W-0                                                                                                       | R/W-0                          | R/W-0            | R/W-0           | R/W-0                               | R/W-0 |

|--------------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|--------------------------------|------------------|-----------------|-------------------------------------|-------|

| ADFM         | VCFG                                                 |                                                                                                             | CHS                            | S<3:0>           |                 | GO/DONE                             | ADON  |

| bit 7        |                                                      |                                                                                                             |                                |                  |                 |                                     | bit ( |

|              |                                                      |                                                                                                             |                                |                  |                 |                                     |       |

| Legend:      |                                                      |                                                                                                             |                                |                  |                 |                                     |       |

| R = Readab   | le bit                                               | W = Writable                                                                                                | bit                            | U = Unimpler     | nented bit, rea | ad as '0'                           |       |

| -n = Value a | It POR                                               | '1' = Bit is set                                                                                            |                                | '0' = Bit is cle | ared            | x = Bit is unknown                  |       |

| bit 7        | <b>ADFM:</b> A/D<br>1 = Right ju<br>0 = Left just    |                                                                                                             | ult Format Se                  | elect bit        |                 |                                     |       |

| bit 6        | <b>VCFG:</b> Volta<br>1 = VREF pir<br>0 = VDD        | age Reference b<br>n                                                                                        | it                             |                  |                 |                                     |       |

| bit 5-2      | 0000 = Cha<br>0001 = Cha<br>0010 = Cha<br>0011 = Cha | Analog Channel<br>annel 00 (AN0)<br>annel 01 (AN1)<br>annel 02 (AN2)<br>annel 03 (AN3)<br>served. Do not us |                                |                  |                 |                                     |       |

|              | 1110 <b>= Dig</b> i                                  | erved. Do not us<br>tal-to-Analog Co<br>ed Voltage Refere                                                   | nverter (DAC                   | output)          |                 |                                     |       |

| bit 1        | 1 = A/D con<br>This bit                              | A/D Conversion<br>version cycle in<br>is automatically oversion complete                                    | progress. Set<br>cleared by ha | rdware when th   |                 | version cycle.<br>sion has complete | ed.   |

| bit 0        | 1 = ADC is                                           | C Enable bit<br>enabled<br>disabled and cor                                                                 | isumes no op                   | erating current  |                 |                                     |       |

# PIC12F752/HV752

## REGISTER 12-2: ADCON1: A/D CONTROL REGISTER 1

| U-0   | R/W-0/0 | R/W-0/0   | R/W-0/0 | U-0 | U-0 | U-0 | U-0   |

|-------|---------|-----------|---------|-----|-----|-----|-------|

| —     |         | ADCS<2:0> |         | —   | —   |     | —     |

| bit 7 |         |           |         |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7   | Unimplemented: Read as '0'                                                  |

|---------|-----------------------------------------------------------------------------|

| bit 6-4 | ADCS<2:0>: A/D Conversion Clock Select bits                                 |

|         | 000 = Fosc/2                                                                |

|         | 001 = Fosc/8                                                                |

|         | 010 = Fosc/32                                                               |

|         | 011 = FRC (clock supplied from an internal oscillator with a divisor of 16) |

|         | 100 = Fosc/4                                                                |

|         | 101 = Fosc/16                                                               |

|         | 110 = Fosc/64                                                               |

| bit 3-0 | Unimplemented: Read as '0'                                                  |

| Name                  | Bit 7                         | Bit 6                        | Bit 5     | Bit 4  | Bit 3                 | Bit 2    | Bit 1   | Bit 0  | Register on<br>Page |

|-----------------------|-------------------------------|------------------------------|-----------|--------|-----------------------|----------|---------|--------|---------------------|

| ADCON0                | ADFM                          | VCFG                         |           | CHS    | <3:0>                 |          | GO/DONE | ADON   | 94                  |

| ADCON1                | —                             |                              | ADCS<2:0> |        | —                     | —        | -       | —      | 94                  |

| ANSELA                | _                             |                              | ANSA5     | ANSA4  | _                     | ANSA2    | ANSA1   | ANSA0  | 41                  |

| ADRESH <sup>(2)</sup> | A/D Result Register High Byte |                              |           |        | 96*                   |          |         |        |                     |

| ADRESL <sup>(2)</sup> | A/D Result F                  | A/D Result Register Low Byte |           |        |                       | 94*      |         |        |                     |

| PORTA                 | _                             |                              | RA5       | RA4    | RA3                   | RA2      | RA1     | RA0    | 40                  |

| INTCON                | GIE                           | PEIE                         | TOIE      | INTE   | IOCIE                 | T0IF     | INTF    | IOCIF  | 15                  |

| PIE1                  | TMR1GIE                       | ADIE                         |           |        | _                     | HLTMR1IE | TMR2IE  | TMR1IE | 16                  |

| PIR1                  | TMR1GIF                       | ADIF                         | _         | _      | _                     | HLTMR1IF | TMR2IF  | TMR1IF | 18                  |

| TRISA                 | _                             |                              | TRISA5    | TRISA4 | TRISA3 <sup>(1)</sup> | TRISA2   | TRISA1  | TRISA0 | 40                  |

TABLE 12-2: SUMMARY OF ASSOCIATED ADC REGISTERS

**Legend:** x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for ADC module.

\* Page provides register information.

Note 1: TRISA3 always reads '1'.

2: Read-only register.

## **15.2 Comparator Control**

Each comparator has two control registers: CMxCON0 and CMxCON1.

The CMxCON0 registers (see Register 15-1) contain Control and Status bits for the following:

- Enable

- Output selection

- Output pin enable

- Output polarity

- · Speed/Power selection

- Hysteresis enable

- Output synchronization

The CMxCON1 registers (see Register 15-2) contain Control bits for the following:

- Interrupt edge polarity (rising and/or falling)

- Positive input channel selection

- Negative input channel selection

#### 15.2.1 COMPARATOR ENABLE

Setting the CxON bit of the CMxCON0 register enables the comparator for operation. Clearing the CxON bit disables the comparator resulting in minimum current consumption.

#### 15.2.2 COMPARATOR OUTPUT SELECTION

The output of the comparator can be monitored by reading either the CxOUT bit of the CMxCON0 register or the MCxOUT bit of the CMOUT register. In order to make the output available for an external connection, the following conditions must be true:

- CxOE bit of the CMxCON0 register must be set

- · Corresponding TRIS bit must be cleared

- CxON bit of the CMxCON0 register must be set

| Note 1: | The CxOE bit of the CMxCON0 register   |

|---------|----------------------------------------|

|         | overrides the PORT data latch. Setting |

|         | the CxON bit of the CMxCON0 register   |

|         | has no impact on the port override.    |

2: The internal output of the comparator is latched with each instruction cycle. Unless otherwise specified, external outputs are not latched.

#### 15.2.3 COMPARATOR OUTPUT POLARITY

Inverting the output of the comparator is functionally equivalent to swapping the comparator inputs. The polarity of the comparator output can be inverted by setting the CxPOL bit of the CMxCON0 register. Clearing the CxPOL bit results in a non-inverted output.

Table 15-1 shows the output state versus input conditions, including polarity control.

#### TABLE 15-1: COMPARATOR OUTPUT STATE VS. INPUT CONDITIONS

| Input Condition | CxPOL | CxOUT |

|-----------------|-------|-------|

| CxVN > CxVP     | 0     | 0     |

| CxVN < CxVP     | 0     | 1     |

| CxVN > CxVP     | 1     | 1     |

| CxVN < CxVP     | 1     | 0     |

## 15.2.4 COMPARATOR SPEED/POWER SELECTION

The trade-off between speed or power can be optimized during program execution with the CxSP control bit. The default state for this bit is '1' which selects the normal speed mode. Device power consumption can be optimized at the cost of slower comparator propagation delay by clearing the CxSP bit to '0'.

#### 15.3 Comparator Hysteresis

A selectable amount of separation voltage can be added to the input pins of each comparator to provide a hysteresis function to the overall operation. Hysteresis is enabled by setting the CxHYS bit of the CMxCON0 register.

See **Section 20.0 "Electrical Specifications**" for more information.

## 15.4 Timer1 Gate Operation

The output resulting from a comparator operation can be used as a source for gate control of Timer1. See **Section 7.5 "Timer1 Gate"** for more information. This feature is useful for timing the duration or interval of an analog event.

It is recommended that the comparator output be synchronized to Timer1. This ensures that Timer1 does not increment while a change in the comparator is occurring.

# PIC12F752/HV752

| MOVF             | Move f                                                                                                                                                                                                                                                                                     |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] MOVF f,d                                                                                                                                                                                                                                                                           |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                                |

| Operation:       | (f) $\rightarrow$ (dest)                                                                                                                                                                                                                                                                   |

| Status Affected: | Z                                                                                                                                                                                                                                                                                          |

| Description:     | The contents of register 'f' is<br>moved to a destination dependent<br>upon the status of 'd'. If $d = 0$ ,<br>destination is W register. If $d = 1$ ,<br>the destination is file register 'f'<br>itself. $d = 1$ is useful to test a file<br>register since Status flag Z is<br>affected. |

| Words:           | 1                                                                                                                                                                                                                                                                                          |

| Cycles:          | 1                                                                                                                                                                                                                                                                                          |

| Example:         | MOVF FSR, 0                                                                                                                                                                                                                                                                                |

|                  | After Instruction<br>W = value in FSR<br>register<br>Z = 1                                                                                                                                                                                                                                 |

| MOVWF            | Move W to f                                                                                       |

|------------------|---------------------------------------------------------------------------------------------------|

| Syntax:          | [label] MOVWF f                                                                                   |

| Operands:        | $0 \leq f \leq 127$                                                                               |

| Operation:       | $(W) \rightarrow (f)$                                                                             |

| Status Affected: | None                                                                                              |

| Description:     | Move data from W register to register 'f'.                                                        |

| Words:           | 1                                                                                                 |

| Cycles:          | 1                                                                                                 |

| Example:         | MOVW OPTION<br>F                                                                                  |

|                  | Before Instruction<br>OPTION = 0xFF<br>W = 0x4F<br>After Instruction<br>OPTION = 0x4F<br>W = 0x4F |

| MOVLW            | Move literal to W                                                                         |

|------------------|-------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                  |

| Operands:        | $0 \leq k \leq 255$                                                                       |

| Operation:       | $k \rightarrow (W)$                                                                       |

| Status Affected: | None                                                                                      |

| Description:     | The 8-bit literal 'k' is loaded into W register. The "don't cares" will assemble as '0's. |

| Words:           | 1                                                                                         |

| Cycles:          | 1                                                                                         |

| Example:         | MOVLW 0x5A                                                                                |

|                  | After Instruction<br>W = 0x5A                                                             |

| NOP              | No Operation  |

|------------------|---------------|

| Syntax:          | [ label ] NOP |

| Operands:        | None          |

| Operation:       | No operation  |

| Status Affected: | None          |

| Description:     | No operation  |

| Words:           | 1             |

| Cycles:          | 1             |

| Example:         | NOP           |

#### 19.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

## 19.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

## 19.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

## 19.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a full-speed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

#### 19.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

# 20.0 ELECTRICAL SPECIFICATIONS

# Absolute Maximum Ratings<sup>(†)</sup>

| Ambient ter  | nperature under bias                                                                                                                                                         |                      |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Storage terr | nperature                                                                                                                                                                    | 65°C to +150°C       |

| Voltage on   | pins with respect to Vss                                                                                                                                                     |                      |

|              | on VDD pin                                                                                                                                                                   |                      |

|              | PIC12HV752                                                                                                                                                                   | -0.3V to +6.5V       |

|              | PIC12F752                                                                                                                                                                    | -0.3V to +6.5V       |

| (            | on MCLR                                                                                                                                                                      | 0.3V to +13.5V       |

| (            | on all other pins                                                                                                                                                            | 0.3V to (VDD + 0.3V) |

| Maximum c    | urrent                                                                                                                                                                       |                      |

| (            | on Vss pin <sup>(1)</sup>                                                                                                                                                    |                      |

|              | $-40^{\circ}C \leq TA \leq +85^{\circ}C \;$                                                                                                                                  | 95 mA                |

|              | $-40^{\circ}C \leq T_{A} \leq +125^{\circ}C \;$                                                                                                                              | 95 mA                |

| (            | on VDD pin <sup>(1)</sup>                                                                                                                                                    |                      |

|              | $-40^{\circ}C \leq TA \leq +85^{\circ}C \;$                                                                                                                                  | 95 mA                |

|              | $-40^{\circ}C \leq TA \leq +125^{\circ}C \;$                                                                                                                                 | 95 mA                |

| (            | on RA1, RA4, RA5                                                                                                                                                             | 25 mA                |

| (            | on RA0, RA2                                                                                                                                                                  | 50 mA                |

| Clamp curre  | ent, Ik (VPIN < 0 or VPIN >VDD)                                                                                                                                              | ± 20 mA              |

| li           | Maximum current rating requires even load distribution across I/O pins. Maxin<br>imited by the device package power dissipation characteristics. See Table 20<br>imitations. | <b>3</b> 1           |

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure above maximum rating conditions for extended periods may affect device reliability.

| PIC12F752     |                 | Standard Operating Conditions (unless otherwise stated)<br>Sleep mode |                        |       |       |       |            |                                               |  |

|---------------|-----------------|-----------------------------------------------------------------------|------------------------|-------|-------|-------|------------|-----------------------------------------------|--|

| PIC12H        | V752            |                                                                       |                        |       |       |       |            |                                               |  |

| Param. Device |                 |                                                                       | <b>T</b> 4             | Max.  | Max.  | Unite | Conditions |                                               |  |

| No.           | Characteristics | Min.                                                                  | Тур.†                  | 85°C  | 125°C | Units | Vdd        | Note                                          |  |

|               | Power-down Bas  | e Curre                                                               | nt (IPD) <sup>(2</sup> | 2, 3) |       |       |            |                                               |  |

| D025          |                 | _                                                                     | 0.2                    | 3.0   | 6.5   | μA    | 3.0        | A/D Current <sup>(1)</sup> , no conversion in |  |

|               |                 |                                                                       | 0.36                   | 3.5   | 10    | μA    | 5.0        | progress                                      |  |

| D025          |                 |                                                                       | 210                    | 280   | 280   | μA    | 3.0        |                                               |  |

|               |                 |                                                                       | 260                    | 350   | 350   | μA    | 4.5        |                                               |  |

| D026          |                 |                                                                       | 20.0                   | 30    | 30    | μA    | 2.0        | DAC Current <sup>(1)</sup>                    |  |

|               |                 |                                                                       | 30.0                   | 40    | 40    | μA    | 3.0        |                                               |  |

|               |                 | _                                                                     | 50.0                   | 70    | 70    | μA    | 5.0        |                                               |  |

| D026          |                 | _                                                                     | 160                    | 238   | 238   | μA    | 2.0        |                                               |  |

|               |                 | _                                                                     | 250                    | 322   | 322   | μA    | 3.0        |                                               |  |

|               |                 | _                                                                     | 310                    | 448   | 448   | μA    | 4.5        |                                               |  |

| D027          |                 | _                                                                     | 295.0                  | 436   | 485   | μA    | 2.0        | FVR Current <sup>(1)</sup> , FVRBUFEN = 1,    |  |

|               |                 | _                                                                     | 300                    | 450   | 500   | μA    | 3.0        | REFOUT buffer enabled                         |  |

|               |                 | _                                                                     | 325                    | 475   | 515   | μA    | 5.0        |                                               |  |

| D027          |                 | _                                                                     | 395.0                  | 605   | 605   | μA    | 2.0        |                                               |  |

|               |                 | _                                                                     | 470                    | 710   | 710   | μA    | 3.0        |                                               |  |

|               |                 | —                                                                     | 505                    | 765   | 765   | μA    | 4.5        |                                               |  |

| D028          |                 | —                                                                     | 5.5                    | 10    | 16    | μA    | 2.0        | T1OSC Current,                                |  |

|               |                 | —                                                                     | 7.0                    | 12    | 18    | μA    | 3.0        | TMR1CS <1:0> = 11                             |  |

|               |                 |                                                                       | 8.5                    | 14    | 22    | μA    | 5.0        |                                               |  |

| D028          |                 | _                                                                     | 140.0                  | 205   | 205   | μA    | 2.0        |                                               |  |

|               |                 | —                                                                     | 220.0                  | 290   | 290   | μA    | 3.0        |                                               |  |

|               |                 | —                                                                     | 270.0                  | 360   | 360   | μA    | 4.5        |                                               |  |

## TABLE 20-3: POWER-DOWN CURRENTS (IPD) (CONTINUED)<sup>(1,2)</sup>

\* These parameters are characterized but not tested.

† Data in "Typ." column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The peripheral △ current can be determined by subtracting the base IPD current from this limit. Max values should be used when calculating total current consumption.

2: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to Vss.

3: Shunt regulator is always on and always draws operating current.

# PIC12F752/HV752

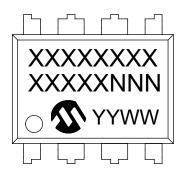

# 22.0 PACKAGING INFORMATION

## 22.1 Package Marking Information

8-Lead PDIP (300 mil)

8-Lead SOIC (3.90 mm)

Example

| Legend: | XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>*                                                                                                                                                           | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC <sup>®</sup> designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator ( (C3))<br>can be found on the outer packaging for this package. |  |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|         | In the event the full Microchip part number cannot be marked on one line, it will carried over to the next line, thus limiting the number of available characters customer-specific information. |                                                                                                                                                                                                                                                                                                                                                                                              |  |

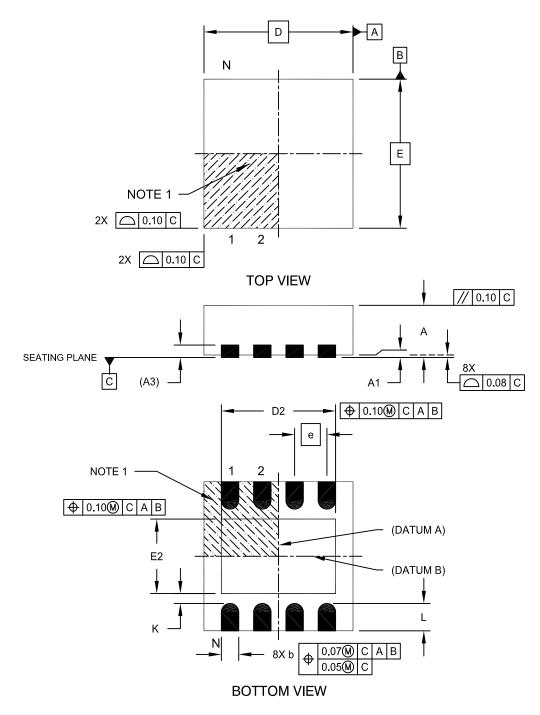

#### 8-Lead Plastic Dual Flat, No Lead Package (MF) - 3x3x0.9mm Body [DFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing No. C04-062C Sheet 1 of 2

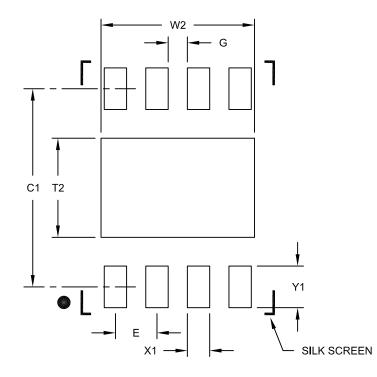

#### 8-Lead Plastic Dual Flat, No Lead Package (MF) - 3x3x0.9mm Body [DFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## RECOMMENDED LAND PATTERN

|                            | MILLIMETERS |          |      |      |

|----------------------------|-------------|----------|------|------|

| Dimensio                   | MIN         | NOM      | MAX  |      |

| Contact Pitch E            |             | 0.65 BSC |      |      |

| Optional Center Pad Width  | W2          |          |      | 2.40 |

| Optional Center Pad Length | T2          |          |      | 1.55 |

| Contact Pad Spacing        | C1          |          | 3.10 |      |

| Contact Pad Width (X8)     | X1          |          |      | 0.35 |

| Contact Pad Length (X8)    | Y1          |          |      | 0.65 |

| Distance Between Pads      | G           | 0.30     |      |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2062B