# E·XFL

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                                |

|---------------------------------|-------------------------------------------------------------------------|

| Core Processor                  | PowerPC e300c4s                                                         |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                          |

| Speed                           | 667MHz                                                                  |

| Co-Processors/DSP               | Security; SEC 3.0                                                       |

| RAM Controllers                 | DDR, DDR2                                                               |

| Graphics Acceleration           | No                                                                      |

| Display & Interface Controllers | · ·                                                                     |

| Ethernet                        | 10/100/1000Mbps (2)                                                     |

| SATA                            | SATA 3Gbps (4)                                                          |

| USB                             | USB 2.0 + PHY (1)                                                       |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                        |

| Operating Temperature           | -40°C ~ 125°C (TA)                                                      |

| Security Features               | Cryptography, Random Number Generator                                   |

| Package / Case                  | 689-BBGA Exposed Pad                                                    |

| Supplier Device Package         | 689-TEPBGA II (31x31)                                                   |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/kmpc8379ecvralg |

|                                 |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.10 Serial ATA (SATA) Controllers

The serial ATA (SATA) controllers have the following features:

- Supports Serial ATA Rev 2.5 Specification

- Spread spectrum clocking on receive

- Asynchronous notification

- Hot Plug including asynchronous signal recovery

- Link power management

- Native command queuing

- Staggered spin-up and port multiplier support

- Port multiplier support

- SATA 1.5 and 3.0 Gb/s operation

- Interrupt driven

- Power management support

- Error handling and diagnostic features

- Far end/near end loopback

- Failed CRC error reporting

- Increased ALIGN insertion rates

- Scrambling and CONT override

# 1.11 Enhanced Secured Digital Host Controller (eSDHC)

The enhanced SD host controller (eSDHC) has the following features:

- Conforms to SD Host Controller Standard Specification, Rev 2.0 with Test Event register support.

- Compatible with the MMC System Specification, Rev 4.0

- Compatible with the *SD Memory Card Specification, Rev 2.0*, and supports High Capacity SD memory cards

- Compatible with the SDIO Card Specification Rev, 1.2

- Designed to work with SD Memory, miniSD Memory, SDIO, miniSDIO, SD Combo, MMC, MMC*plus*, MMC 4x, and RS-MMC cards

- SD bus clock frequency up to 50 MHz

- Supports 1-/4-bit SD and SDIO modes, 1-/4-bit MMC modes

- Supports internal DMA capabilities

# 2 Electrical Characteristics

This section provides the AC and DC electrical specifications and thermal characteristics for the chip. The device is currently targeted to these specifications. Some of these specifications are independent of the I/O cell, but are included for a more complete reference. These are not purely I/O buffer design specifications.

| Core Frequency<br>(MHz) | CSB/DDR Frequency<br>(MHz) | Sleep Power<br>at T <sub>j</sub> = 65°C (W) $^2$ | Typical Application<br>at $T_j = 65^{\circ}C$ (W) <sup>2</sup> | Typical Application at $T_j = 125^{\circ}C$ (W) <sup>3</sup> | Max Application at $T_j = 125$ °C (W) <sup>4</sup> |

|-------------------------|----------------------------|--------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------------------|----------------------------------------------------|

| 450                     | 300                        | 1.45                                             | 2.0                                                            | 3.2                                                          | 3.8                                                |

| 450                     | 225                        | 1.45                                             | 1.9                                                            | 3.1                                                          | 3.7                                                |

| 500                     | 333                        | 1.45                                             | 2.0                                                            | 3.3                                                          | 3.9                                                |

| 500                     | 250                        | 1.45                                             | 1.9                                                            | 3.2                                                          | 3.8                                                |

| 532                     | 355                        | 1.45                                             | 2.0                                                            | 3.3                                                          | 4.0                                                |

| 533                     | 266                        | 1.45                                             | 2.0                                                            | 3.2                                                          | 3.9                                                |

| 600                     | 400                        | 1.45                                             | 2.1                                                            | 3.4                                                          | 4.1                                                |

| 600                     | 300                        | 1.45                                             | 2.0                                                            | 3.3                                                          | 4.0                                                |

| 667                     | 333                        | 1.45                                             | 2.1                                                            | 3.3                                                          | 4.1                                                |

| 667                     | 266                        | 1.45                                             | 2.0                                                            | 3.3                                                          | 3.9                                                |

| 800                     | 400                        | 1.45                                             | 2.5                                                            | 3.8                                                          | 4.3                                                |

### Table 5. Power Dissipation <sup>1</sup> (continued)

### Notes:

1. The values do not include I/O supply power ( $OV_{DD}$ ,  $LV_{DD}$ ,  $GV_{DD}$ ) or  $AV_{DD}$ . For I/O power values, see Table 6. 2. Typical power is based on a voltage of  $V_{DD}$  = 1.0 V for core frequencies  $\leq$  667 MHz or  $V_{DD}$  = 1.05 V for core frequencies of 800 MHz, and running a Dhrystone benchmark application.

3. Typical power is based on a voltage of  $V_{DD}$  = 1.0 V for core frequencies  $\leq$  667 MHz or  $V_{DD}$  = 1.05 V for core frequencies of 800 MHz, and running a Dhrystone benchmark application.

4. Maximum power is based on a voltage of  $V_{DD}$  = 1.0 V for core frequencies  $\leq$  667 MHz or  $V_{DD}$  = 1.05 V for core frequencies of 800 MHz, worst case process, and running an artificial smoke test.

# 4.2 AC Electrical Characteristics

The primary clock source for the device can be one of two inputs, CLKIN or PCI\_CLK, depending on whether the device is configured in PCI host or PCI agent mode. This table provides the clock input (CLKIN/PCI\_CLK) AC timing specifications for the device.

| Parameter                        | Symbol                               | Min | Typical | Max    | Unit | Note |

|----------------------------------|--------------------------------------|-----|---------|--------|------|------|

| CLKIN/PCI_CLK frequency          | fclkin                               | 25  | —       | 66.666 | MHz  | 1, 6 |

| CLKIN/PCI_CLK cycle time         | t <sub>CLKIN</sub>                   | 15  | —       | 40     | ns   | -    |

| CLKIN/PCI_CLK rise and fall time | t <sub>KH</sub> , t <sub>KL</sub>    | 0.6 | 1.0     | 2.3    | ns   | 2    |

| CLKIN/PCI_CLK duty cycle         | t <sub>KHK</sub> /t <sub>CLKIN</sub> | 40  | —       | 60     | %    | 3    |

| CLKIN/PCI_CLK jitter             | —                                    | —   | —       | ± 150  | ps   | 4, 5 |

### Table 8. CLKIN AC Timing Specifications

### Notes:

- 1. **Caution:** The system, core and security block must not exceed their respective maximum or minimum operating frequencies.

- 2. Rise and fall times for CLKIN/PCI\_CLK are measured at 0.4 V and 2.7 V.

- 3. Timing is guaranteed by design and characterization.

- 4. This represents the total input jitter-short term and long term-and is guaranteed by design.

- 5. The CLKIN/PCI\_CLK driver's closed loop jitter bandwidth should be < 500 kHz at -20 dB. The bandwidth must be set low to allow cascade-connected PLL-based devices to track CLKIN drivers with the specified jitter.

- 6. Spread spectrum is allowed up to 1% down-spread on CLKIN/PCI\_CLK up to 60 KHz.

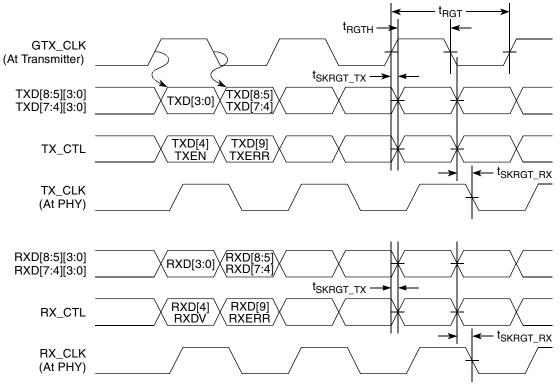

# 4.3 eTSEC Gigabit Reference Clock Timing

This table provides the eTSEC gigabit reference clocks (EC\_GTX\_CLK125) AC timing specifications.

### Table 9. EC\_GTX\_CLK125 AC Timing Specifications

At recommended operating conditions with LV\_{DD} = 2.5  $\pm$  0.125 mV/ 3.3 V  $\pm$  165 mV

| Parameter/Condition                                                                                                                                        | Symbol                                 | Min | Typical | Max         | Unit | Note |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-----|---------|-------------|------|------|

| EC_GTX_CLK125 frequency                                                                                                                                    | t <sub>G125</sub>                      | _   | 125     | _           | MHz  | —    |

| EC_GTX_CLK125 cycle time                                                                                                                                   | t <sub>G125</sub>                      | _   | 8       | _           | ns   | —    |

| EC_GTX_CLK rise and fall time $\label{eq:VDD} \begin{array}{l} \text{EC}_{\text{DD}} = 2.5 \text{ V} \\ \text{LV}_{\text{DD}} = 3.3 \text{ V} \end{array}$ | t <sub>G125R</sub> /t <sub>G125F</sub> | _   |         | 0.75<br>1.0 | ns   | 1    |

| EC_GTX_CLK125 duty cycle<br>1000Base-T for RGMII, RTBI                                                                                                     | t <sub>G125H</sub> /t <sub>G125</sub>  | 47  | _       | 53          | %    | 2    |

| EC_GTX_CLK125 jitter                                                                                                                                       | _                                      | _   | _       | ±150        | ps   | 2    |

Notes:

- 1. Rise and fall times for EC\_GTX\_CLK125 are measured from 0.5 and 2.0 V for  $LV_{DD}$  = 2.5 V and from 0.6 and 2.7 V for  $LV_{DD}$  = 3.3 V.

- EC\_GTX\_CLK125 is used to generate the GTX clock for the eTSEC transmitter with 2% degradation. The EC\_GTX\_CLK125 duty cycle can be loosened from 47%/53% as long as the PHY device can tolerate the duty cycle generated by the eTSEC GTX\_CLK. See Section 8.2.2, "RGMII and RTBI AC Timing Specifications," for the duty cycle for 10Base-T and 100Base-T reference clock.

### Table 13. DDR2 SDRAM DC Electrical Characteristics for GV<sub>DD</sub>(typ) = 1.8 V (continued)

| Parameter                                | Symbol          | Min  | Мах | Unit | Note |

|------------------------------------------|-----------------|------|-----|------|------|

| Output low current ( $V_{OUT} = 0.3 V$ ) | I <sub>OL</sub> | 13.4 |     | mA   | —    |

Notes:

1.  $GV_{DD}$  is expected to be within 50 mV of the DRAM  $GV_{DD}$  at all times.

- MV<sub>REF</sub> is expected to be equal to 0.5 × GV<sub>DD</sub>, and to track GV<sub>DD</sub> DC variations as measured at the receiver. Peak-to-peak noise on MV<sub>REF</sub> may not exceed ±2% of the DC value.

- V<sub>TT</sub> is not applied directly to the device. It is the supply to which far end signal termination is made and is expected to be equal to MV<sub>REF</sub>. This rail should track variations in the DC level of MV<sub>REF</sub>.

- 4. Output leakage is measured with all outputs disabled, 0 V  $\leq$  V<sub>OUT</sub>  $\leq$  GV<sub>DD</sub>.

- 5. See AN3665, "MPC837xE Design Checklist," for proper DDR termination.

Table 14 provides the DDR2 capacitance when  $GV_{DD}(typ) = 1.8$  V.

| Parameter                                    | Symbol           | Min | Мах | Unit | Note |

|----------------------------------------------|------------------|-----|-----|------|------|

| Input/output capacitance: DQ, DQS, DQS       | C <sub>IO</sub>  | 6   | 8   | pF   | 1    |

| Delta input/output capacitance: DQ, DQS, DQS | C <sub>DIO</sub> | _   | 0.5 | pF   | 1    |

#### Note:

1. This parameter is sampled.  $GV_{DD} = 1.8 \text{ V} \pm 0.090 \text{ V}$ , f = 1 MHz,  $T_A = 25^{\circ}C$ ,  $V_{OUT} = GV_{DD}/2$ ,  $V_{OUT}$  (peak-to-peak) = 0.2 V.

This table provides the recommended operating conditions for the DDR SDRAM component(s) when  $GV_{DD}(typ) = 2.5 \text{ V}.$

| Table 15 | . DDR SDRAM I | OC Electrical Characte | ristics for GV <sub>DD</sub> (typ) = 2.5 V |

|----------|---------------|------------------------|--------------------------------------------|

|----------|---------------|------------------------|--------------------------------------------|

| Parameter                                      | Symbol            | Min                      | Мах                      | Unit | Note |

|------------------------------------------------|-------------------|--------------------------|--------------------------|------|------|

| I/O supply voltage                             | GV <sub>DD</sub>  | 2.375                    | 2.625                    | V    | 1    |

| I/O reference voltage                          | MV <sub>REF</sub> | $0.49 	imes GV_{DD}$     | $0.51 	imes GV_{DD}$     | V    | 2, 5 |

| I/O termination voltage                        | V <sub>TT</sub>   | MV <sub>REF</sub> - 0.04 | MV <sub>REF</sub> + 0.04 | V    | 3    |

| Input high voltage                             | V <sub>IH</sub>   | MV <sub>REF</sub> + 0.18 | GV <sub>DD</sub> + 0.3   | V    | _    |

| Input low voltage                              | V <sub>IL</sub>   | -0.3                     | MV <sub>REF</sub> – 0.18 | V    | _    |

| Output leakage current                         | I <sub>OZ</sub>   | -50                      | 50                       | μA   | 4    |

| Output high current (V <sub>OUT</sub> = 1.9 V) | I <sub>ОН</sub>   | -15.2                    | —                        | mA   | —    |

| Output low current (V <sub>OUT</sub> = 0.38 V) | I <sub>OL</sub>   | 15.2                     | —                        | mA   | —    |

Notes:

1.  $GV_{DD}$  is expected to be within 50 mV of the DRAM  $GV_{DD}$  at all times.

- MV<sub>REF</sub> is expected to be equal to 0.5 × GV<sub>DD</sub>, and to track GV<sub>DD</sub> DC variations as measured at the receiver. Peak-to-peak noise on MV<sub>REF</sub> may not exceed ±2% of the DC value.

- V<sub>TT</sub> is not applied directly to the device. It is the supply to which far end signal termination is made and is expected to be equal to MV<sub>REF</sub>. This rail should track variations in the DC level of MV<sub>REF</sub>.

- 4. Output leakage is measured with all outputs disabled,  $0 V \le V_{OUT} \le GV_{DD}$ .

- 5. See AN3665, "MPC837xE Design Checklist," for proper DDR termination.

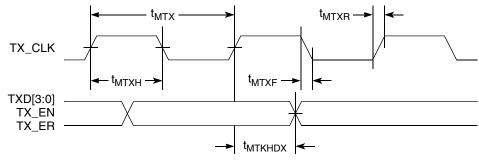

### Table 26. MII Transmit AC Timing Specifications (continued)

At recommended operating conditions with  $LV_{DD}$  of 3.3 V  $\pm$  5%.

| Parameter                        | Symbol <sup>1</sup> | Min | Typical | Max | Unit |

|----------------------------------|---------------------|-----|---------|-----|------|

| TX_CLK data clock rise (20%-80%) | t <sub>MTXR</sub>   | 1.0 | _       | 4.0 | ns   |

| TX_CLK data clock fall (80%-20%) | t <sub>MTXF</sub>   | 1.0 |         | 4.0 | ns   |

#### Note:

1. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MTKHDX</sub> symbolizes MII transmit timing (MT) for the time t<sub>MTX</sub> clock reference (K) going high (H) until data outputs (D) are invalid (X). Note that, in general, the clock reference symbol representation is based on two to three letters representing the clock of a particular functional. For example, the subscript of t<sub>MTX</sub> represents the MII(M) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

This figure shows the MII transmit AC timing diagram.

Figure 7. MII Transmit AC Timing Diagram

### 8.2.1.2 MII Receive AC Timing Specifications

This table provides the MII receive AC timing specifications.

### Table 27. MII Receive AC Timing Specifications

At recommended operating conditions with  $LV_{DD}$  of 3.3 V ± 5%.

| Parameter                                   | Symbol <sup>1</sup>                 | Min  | Typical | Мах | Unit |

|---------------------------------------------|-------------------------------------|------|---------|-----|------|

| Input low voltage                           | V <sub>IL</sub>                     | —    | —       | 0.7 | V    |

| Input high voltage                          | V <sub>IH</sub>                     | 1.9  | _       | —   | V    |

| RX_CLK clock period 10 Mbps                 | t <sub>MRX</sub>                    | —    | 400     | —   | ns   |

| RX_CLK clock period 100 Mbps                | t <sub>MRX</sub>                    | —    | 40      | —   | ns   |

| RX_CLK duty cycle                           | t <sub>MRXH</sub> /t <sub>MRX</sub> | 35   | _       | 65  | %    |

| RXD[3:0], RX_DV, RX_ER setup time to RX_CLK | t <sub>MRDVKH</sub>                 | 10.0 | —       | —   | ns   |

| RXD[3:0], RX_DV, RX_ER hold time to RX_CLK  | t <sub>MRDXKH</sub>                 | 10.0 |         | —   | ns   |

This figure shows the RGMII and RTBI AC timing and multiplexing diagrams.

Figure 11. RGMII and RTBI AC Timing and Multiplexing Diagrams

### 8.2.3 RMII AC Timing Specifications

This section describes the RMII transmit and receive AC timing specifications.

### 8.2.3.1 RMII Transmit AC Timing Specifications

This table shows the RMII transmit AC timing specifications.

### Table 29. RMII Transmit AC Timing Specifications

At recommended operating conditions with LV\_DD of 3.3 V  $\pm$  5%.

| Parameter                   | Symbol <sup>1</sup> | Min  | Typical | Мах  | Unit |

|-----------------------------|---------------------|------|---------|------|------|

| REF_CLK clock period        | t <sub>RMT</sub>    | 15.0 | 20.0    | 25.0 | ns   |

| REF_CLK duty cycle          | t <sub>RMTH</sub>   | 35   | 50      | 65   | %    |

| REF_CLK peak-to-peak jitter | t <sub>RMTJ</sub>   | —    | —       | 250  | ps   |

| Rise time REF_CLK (20%-80%) | t <sub>RMTR</sub>   | 1.0  | —       | 2.0  | ns   |

This figures show the local bus signals.

Figure 20. Local Bus Signals, Non-special Signals Only (PLL Enable Mode)

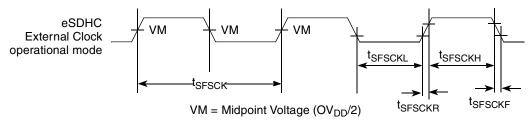

### Table 42. eSDHC AC Timing Specifications for Full-Speed Mode (continued)

At recommended operating conditions  $\text{OV}_{\text{DD}}$  = 3.3 V  $\pm$  165 mV.

| Parameter                                                   | Symbol <sup>1</sup>      | Min | Max | Unit | Note |

|-------------------------------------------------------------|--------------------------|-----|-----|------|------|

| Input hold times: SD_CMD, SD_DAT <i>x</i> , SD_CD to SD_CLK | t <sub>SFSIXKH</sub>     | 0   | —   | ns   | 2    |

| SD_CLK delay within device                                  | t <sub>INT_CLK_DLY</sub> | 1.5 | —   | ns   | 4    |

| Output valid: SD_CLK to SD_CMD, SD_DAT <i>x</i> valid       | t <sub>SFSKHOV</sub>     | —   | 4   | ns   | 2    |

| Output hold: SD_CLK to SD_CMD, SD_DAT <i>x</i> valid        | t <sub>SFSKHOX</sub>     | 0   | —   | —    | _    |

| SD card input setup                                         | t <sub>ISU</sub>         | 5   | —   | ns   | 3    |

| SD card input hold                                          | t <sub>IH</sub>          | 5   | —   | ns   | 3    |

| SD card output valid                                        | t <sub>ODLY</sub>        | —   | 14  | ns   | 3    |

| SD card output hold                                         | t <sub>ОН</sub>          | 0   | —   | ns   | 3    |

#### Notes:

1. The symbols used for timing specifications herein follow the pattern of t<sub>(first three letters of functional block)(signal)(state)</sub> (reference)(state) for inputs and t<sub>(first three letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>SFSIXKH</sub> symbolizes eSDHC full mode speed device timing (SFS) input (I) to go invalid (X) with respect to the clock reference (K) going to high (H). Also t<sub>SFSKHOV</sub> symbolizes eSDHC full speed timing (SFS) for the clock reference (K) to go high (H), with respect to the output (O) going valid (V) or data output valid time. Note that, in general, the clock reference symbol representation is based on five letters representing the clock of a particular functional. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

- 2. Measured at capacitive load of 40 pF.

- 3. For reference only, according to the SD card specifications.

- 4. Average, for reference only.

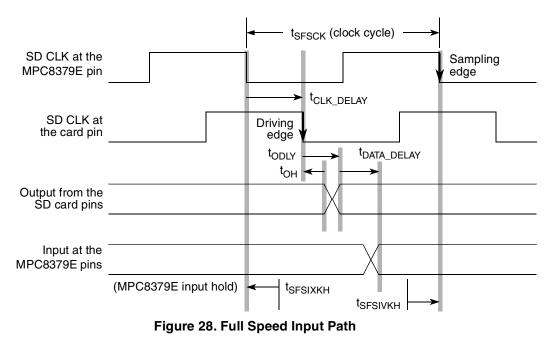

This figure provides the eSDHC clock input timing diagram.

Figure 26. eSDHC Clock Input Timing Diagram

### *t<sub>CLK\_DELAY</sub>* + *t<sub>IH</sub>* - *t<sub>SFSKHOX</sub>* < *t<sub>SFSCKL</sub>* + *t<sub>DATA\_DELAY</sub>*

This means that clock can be delayed versus data up to 15 ns (external delay line) in ideal case of  $t_{SFSCLKL} = 20$  ns:

$t_{CLK\_DELAY} + 5 - 0 < 20 + t_{DATA\_DELAY}$  $t_{CLK\_DELAY} < 15 + t_{DATA\_DELAY}$

### 11.2.1.3 Full-Speed Write Combined Formula

The following equation is the combined formula to calculate the allowed skew range between the SD\_CLK and SD\_DAT/CMD signals on the PCB.

```

t_{CLK\_DELAY} + t_{IH} - t_{SFSKHOX} < t_{SFSCKL} + t_{DATA\_DELAY} < t_{SFSCK} + t_{CLK\_DELAY} - t_{ISU} - t_{SFSKHOV} Eqn. 6

```

### 11.2.2 Full-Speed Input Path (Read)

This figure provides the data and command input timing diagram.

### 11.2.2.1 Full-Speed Read Meeting Setup (Maximum Delay)

The following equations show how to calculate the allowed combined propagation delay range of the SD\_CLK and SD\_DAT/CMD signals on the PCB.

$$t_{CLK\_DELAY} + t_{DATA\_DELAY} + t_{ODLY} + t_{SFSIVKH} < t_{SFSCK} Eqn. 7$$

$$t_{CLK\_DELAY} + t_{DATA\_DELAY} < t_{SFSCK} - t_{ODLY} - t_{SFSIVKH} - t_{INT\_CLK\_DLY} Eqn. 8$$

Eqn. 5

### 11.2.2.2 Full-Speed Read Meeting Hold (Minimum Delay)

There is no minimum delay constraint due to the full clock cycle between the driving and sampling of data.

### t<sub>CLK\_DELAY</sub> + t<sub>OH</sub> + t<sub>DATA\_DELAY</sub> > t<sub>SFSIXKH</sub>

Eqn. 9

This means that Data + Clock delay must be greater than -2 ns. This is always fulfilled.

# 11.3 eSDHC AC Timing Specifications (High-Speed Mode)

This table provides the eSDHC AC timing specifications for high-speed mode as defined in Figure 30 and Figure 31.

### Table 43. eSDHC AC Timing Specifications for High-Speed Mode

At recommended operating conditions  $\text{OV}_{\text{DD}}$  = 3.3 V  $\pm$  165 mV.

| Parameter                                           | Symbol <sup>1</sup>                         | Min | Мах | Unit | Note |

|-----------------------------------------------------|---------------------------------------------|-----|-----|------|------|

| SD_CLK clock frequency—high speed mode              | f <sub>sнscк</sub>                          | 0   | 50  | MHz  | —    |

| SD_CLK clock cycle                                  | t <sub>sнscк</sub>                          | 20  | _   | ns   | _    |

| SD_CLK clock frequency—identification mode          | f <sub>SIDCK</sub>                          | 0   | 400 | KHz  | —    |

| SD_CLK clock low time                               | <sup>t</sup> sнsck∟                         | 7   | —   | ns   | 2    |

| SD_CLK clock high time                              | t <sub>sнscкн</sub>                         | 7   | —   | ns   | 2    |

| SD_CLK clock rise and fall times                    | t <sub>SHSCKR/</sub><br>t <sub>SHSCKF</sub> | _   | 3   | ns   | 2    |

| Input setup times: SD_CMD, SD_DATx, SD_CD to SD_CLK | <sup>t</sup> shsivkh                        | 5   | —   | ns   | 2    |

| Input hold times: SD_CMD, SD_DATx, SD_CD to SD_CLK  | t <sub>SHSIXKH</sub>                        | 0   | —   | ns   | 2    |

| Output delay time: SD_CLK to SD_CMD, SD_DATx valid  | t <sub>SHSKHOV</sub>                        |     | 4   | ns   | 2    |

| Output Hold time: SD_CLK to SD_CMD, SD_DATx invalid | t <sub>SHSKHOX</sub>                        | 0   | —   | ns   | 2    |

| SD_CLK delay within device                          | t <sub>INT_CLK_DLY</sub>                    | 1.5 | —   | ns   | 4    |

| SD Card Input Setup                                 | t <sub>ISU</sub>                            | 6   | —   | ns   | 3    |

| SD Card Input Hold                                  | t <sub>IH</sub>                             | 2   | —   | ns   | 3    |

| SD Card Output Valid                                | t <sub>ODLY</sub>                           | _   | 14  | ns   | 3    |

| SD Card Output Hold                                 | t <sub>OH</sub>                             | 2.5 | —   | ns   | 3    |

Notes:

1. The symbols used for timing specifications herein follow the pattern of t<sub>(first three letters of functional block)(signal)(state)</sub> (reference)(state) for inputs and t<sub>(first three letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>SFSIXKH</sub> symbolizes eSDHC full mode speed device timing (SFS) input (I) to go invalid (X) with respect to the clock reference (K) going to high (H). Also t<sub>SFSKHOV</sub> symbolizes eSDHC full speed timing (SFS) for the clock reference (K) to go high (H), with respect to the output (O) going valid (V) or data output valid time. Note that, in general, the clock reference symbol representation is based on five letters representing the clock of a particular functional. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

2. Measured at capacitive load of 40 pF.

3. For reference only, according to the SD card specifications.

4. Average, for reference only.

### Table 49. PCI AC Timing Specifications at 66 MHz (continued)

PCI\_SYNC\_IN clock input levels are with next levels: VIL =  $0.1 \times OV_{DD}$ , VIH =  $0.7 \times OV_{DD}$ .

| Parameter            | Symbol <sup>1</sup> | Min  | Мах | Unit | Note    |

|----------------------|---------------------|------|-----|------|---------|

| Input hold from cock | t <sub>PCIXKH</sub> | 0.25 | —   | ns   | 2, 4, 6 |

| Output clock skew    | t <sub>РСКОЅК</sub> | —    | 0.5 | ns   | 5       |

#### Notes:

Note that the symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state)</sub> (reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>PCIVKH</sub> symbolizes PCI timing (PC) with respect to the time the input signals (I) reach the valid state (V) relative to the PCI\_SYNC\_IN clock, t<sub>SYS</sub>, reference (K) going to the high (H) state or setup time. Also, t<sub>PCRHFV</sub> symbolizes PCI timing (PC) with respect to the time hard reset (R) went high (H) relative to the frame signal (F) going to the valid (V) state.

2. See the timing measurement conditions in the PCI 2.3 Local Bus Specifications.

- 3. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 4. Input timings are measured at the pin.

- 5. PCI specifications allows 1 ns skew for 66 MHz but includes the total allowed skew, board, connectors, etc.

- 6. Value does not comply with the PCI 2.3 Local Bus Specifications.

### This table shows the PCI AC timing specifications at 33 MHz.

#### Table 50. PCI AC Timing Specifications at 33 MHz

PCI\_SYNC\_IN clock input levels are with next levels: VIL =  $0.1 \times OV_{DD}$ ,  $V_{IH} = 0.7 \times OV_{DD}$ .

| Parameter                      | Symbol <sup>1</sup> | Min  | Мах | Unit | Note    |

|--------------------------------|---------------------|------|-----|------|---------|

| Clock to output valid          | <sup>t</sup> PCKHOV | _    | 11  | ns   | 2       |

| Output hold from clock         | t <sub>PCKHOX</sub> | 2    | -   | ns   | 2       |

| Clock to output high impedance | t <sub>PCKHOZ</sub> | _    | 14  | ns   | 2, 3    |

| Input setup to clock           | t <sub>PCIVKH</sub> | 3.0  | -   | ns   | 2, 4    |

| Input hold from clock          | t <sub>PCIXKH</sub> | 0.25 | -   | ns   | 2, 4, 6 |

| Output clock skew              | t <sub>PCKOSK</sub> |      | 0.5 | ns   | 5       |

Notes:

- Note that the symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state)</sub> (reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>PCIVKH</sub> symbolizes PCI timing (PC) with respect to the time the input signals (I) reach the valid state (V) relative to the PCI\_SYNC\_IN clock, t<sub>SYS</sub>, reference (K) going to the high (H) state or setup time. Also, t<sub>PCRHFV</sub> symbolizes PCI timing (PC) with respect to the time hard reset (R) went high (H) relative to the frame signal (F) going to the valid (V) state.

- 2. See the timing measurement conditions in the PCI 2.3 Local Bus Specifications.

- 3. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 4. Input timings are measured at the pin.

- 5. PCI specifications allows 2 ns skew for 33 MHz but includes the total allowed skew, board, connectors, etc.

- 6. Value does not comply with the PCI 2.3 Local Bus Specifications.

# 15.2.1 Gen1i/1.5G Transmitter Specifications

This table provides the DC differential transmitter output DC characteristics for the SATA interface at Gen1i or 1.5 Gbits/s transmission.

| Table 52. Gen1i/1.5G Transmitter (Tx) DC Specifications |  |

|---------------------------------------------------------|--|

|---------------------------------------------------------|--|

| Parameter                      | Symbol                     | Min | Typical | Max | Units             | Note |

|--------------------------------|----------------------------|-----|---------|-----|-------------------|------|

| Tx differential output voltage | V <sub>SATA_TXDIFF</sub>   | 400 | 500     | 600 | mV <sub>p-p</sub> | 1    |

| Tx differential pair impedance | Z <sub>SATA_TXDIFFIM</sub> | 85  | 100     | 115 | Ω                 | —    |

Note:

1. Terminated by 50  $\Omega$  load.

This table provides the differential transmitter output AC characteristics for the SATA interface at Gen1i or 1.5 Gbits/s transmission.

Table 53. Gen1i/1.5G Transmitter AC Specifications

| Parameter                                 | Symbol                      | Min      | Typical | Max      | Units             | Note |

|-------------------------------------------|-----------------------------|----------|---------|----------|-------------------|------|

| Channel speed                             | t <sub>CH_SPEED</sub>       | —        | 1.5     | _        | Gbps              | —    |

| Unit interval                             | T <sub>UI</sub>             | 666.4333 | 666.667 | 670.2333 | ps                | —    |

| Total jitter, data-data<br>5 UI           | U <sub>SATA_TXTJ5UI</sub>   | —        | —       | 0.355    | UI <sub>p-p</sub> | 1    |

| Total jitter, data-data<br>250 UI         | U <sub>SATA_TXTJ250UI</sub> | _        | _       | 0.47     | UI <sub>p-p</sub> | 1    |

| Deterministic jitter, data-data<br>5 UI   | U <sub>SATA_TXDJ5UI</sub>   | _        | _       | 0.175    | UI <sub>p-p</sub> | 1    |

| Deterministic jitter, data-data<br>250 UI | U <sub>SATA_TXDJ250UI</sub> | —        | —       | 0.22     | UI <sub>p-p</sub> | 1    |

Note:

1. Measured at Tx output pins peak to peak phase variation, random data pattern.

## 15.2.2 Gen2i/3G Transmitter Specifications

This table provides the differential transmitter output DC characteristics for the SATA interface at Gen2i or 3.0 Gbits/s transmission.

Table 54. Gen 2i/3G Transmitter DC Specifications

| Parameter                      | Symbol                     | Min | Typical | Мах | Units             | Note |

|--------------------------------|----------------------------|-----|---------|-----|-------------------|------|

| Tx differential output voltage | V <sub>SATA_TXDIFF</sub>   | 400 | 550     | 700 | mV <sub>p-p</sub> | 1    |

| Tx differential pair impedance | Z <sub>SATA_TXDIFFIM</sub> | 85  | 100     | 115 | Ω                 | —    |

Note:

1. Terminated by 50  $\Omega$  load.

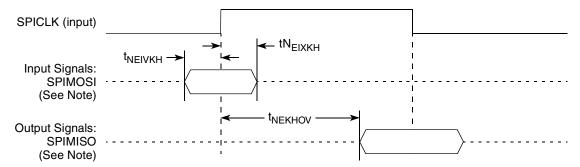

This figure shows the SPI timing in slave mode (external clock).

Note: The clock edge is selectable on SPI.

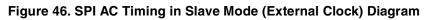

This figure shows the SPI timing in master mode (internal clock).

Note: The clock edge is selectable on SPI.

Figure 47. SPI AC Timing in Master Mode (Internal Clock) Diagram

# 20 High-Speed Serial Interfaces (HSSI)

This chip features two serializer/deserializer (SerDes) interfaces to be used for high-speed serial interconnect applications. See Table 1 for the interfaces supported.

This section describes the common portion of SerDes DC electrical specifications, which is the DC requirement for SerDes reference clocks. The SerDes data lane's transmitter and receiver reference circuits are also shown.

# 20.1 Signal Terms Definition

The SerDes utilizes differential signaling to transfer data across the serial link. This section defines terms used in the description and specification of differential signals.

Figure 48 shows how the signals are defined. For illustration purpose, only one SerDes lane is used for description. The figure shows waveform for either a transmitter output (SD*n*\_TX and  $\overline{SDn}_T\overline{X}$ ) or a receiver input (SD*n*\_RX and  $\overline{SDn}_R\overline{X}$ ). Each signal swings between A volts and B volts where A > B.

### NOTE

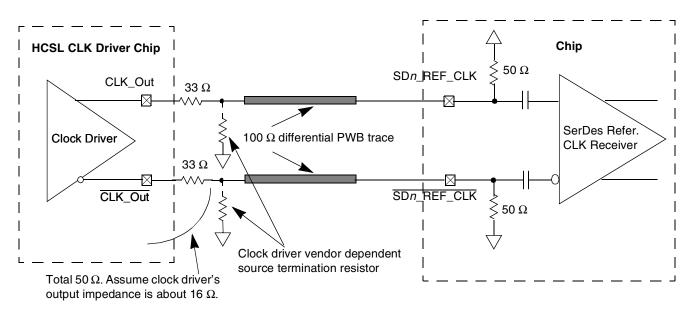

Figure 53 to Figure 56 below are for conceptual reference only. Due to the fact that clock driver chip's internal structure, output impedance, and termination requirements are different between various clock driver chip manufacturers, it is very possible that the clock circuit reference designs provided by the clock driver chip vendor are different from what is shown below. They might also vary from one vendor to the other. Therefore, Freescale Semiconductor can neither provide the optimal clock driver reference circuits, nor guarantee the correctness of the following clock driver connection reference circuits. The system designer is recommended to contact the selected clock driver chip vendor for the optimal reference circuits with the device SerDes reference clock receiver requirement provided in this document.

This figure shows the SerDes reference clock connection reference circuits for HCSL type clock driver. It assumes that the DC levels of the clock driver chip is compatible with device SerDes reference clock input's DC requirement.

Figure 53. DC-Coupled Differential Connection with HCSL Clock Driver (Reference Only)

This figure shows the SerDes reference clock connection reference circuits for LVDS type clock driver. Since LVDS clock driver's common-mode voltage is higher than the device SerDes reference clock input's allowed range (100 to 400 mV), AC-coupled connection scheme must be used. It assumes the LVDS

occurs in the 1–15 MHz range. The source impedance of the clock driver should be 50  $\Omega$  to match the transmission line and reduce reflections which are a source of noise to the system.

This table describes some AC parameters common to SATAprotocols

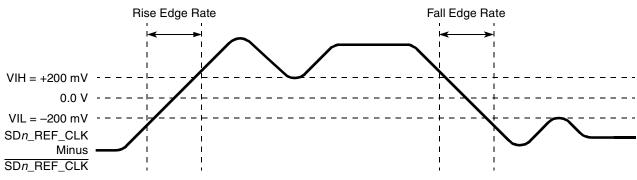

### Table 68. SerDes Reference Clock Common AC Parameters

At recommended operating conditions with  $XV_{DD\_SRDS}$  or  $XV_{DD\_SRDS} = 1.0 V \pm 5\%$ .

| Parameter                                                                                    | Symbol             | Min | Max  | Unit | Note |

|----------------------------------------------------------------------------------------------|--------------------|-----|------|------|------|

| Rising Edge Rate                                                                             | Rise Edge Rate     | 1.0 | 4.0  | V/ns | 2, 3 |

| Falling Edge Rate                                                                            | Fall Edge Rate     | 1.0 | 4.0  | V/ns | 2, 3 |

| Differential Input High Voltage                                                              | V <sub>IH</sub>    | 200 | _    | mV   | 2    |

| Differential Input Low Voltage                                                               | V <sub>IL</sub>    | _   | -200 | mV   | 2    |

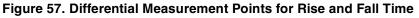

| Rising edge rate (SD <i>n</i> _REF_CLK) to falling edge rate (SD <i>n</i> _REF_CLK) matching | Rise-Fall Matching | _   | 20   | %    | 1, 4 |

### Notes:

- 1. Measurement taken from single ended waveform.

- 2. Measurement taken from differential waveform.

- Measured from -200 mV to +200 mV on the differential waveform (derived from SDn\_REF\_CLK minus SDn\_REF\_CLK). The signal must be monotonic through the measurement region for rise and fall time. The 400 mV measurement window is centered on the differential zero crossing. See Figure 57.

- 4. Matching applies to rising edge rate for SDn\_REF\_CLK and falling edge rate for SDn\_REF\_CLK. It is measured using a 200 mV window centered on the median cross point where SDn\_REF\_CLK rising meets SDn\_REF\_CLK falling. The median cross point is used to calculate the voltage thresholds the oscilloscope is to use for the edge rate calculations. The Rise Edge Rate of SDn\_REF\_CLK should be compared to the Fall Edge Rate of SDn\_REF\_CLK, the maximum allowed difference should not exceed 20% of the slowest edge rate. See Figure 58.

Figure 58. Single-Ended Measurement Points for Rise and Fall Time Matching

| Signal | Package Pin Number | Pin Type | Power Supply | Note |

|--------|--------------------|----------|--------------|------|

| MBA2   | M3                 | 0        | GVDD         | _    |

| MCAS_B | W5                 | 0        | GVDD         |      |

| MCK_B0 | H1                 | 0        | GVDD         |      |

| MCK_B1 | К1                 | 0        | GVDD         |      |

| MCK_B2 | V1                 | 0        | GVDD         |      |

| MCK_B3 | W2                 | 0        | GVDD         |      |

| MCK_B4 | AA1                | 0        | GVDD         |      |

| MCK_B5 | AB2                | 0        | GVDD         |      |

| MCK0   | J1                 | 0        | GVDD         |      |

| MCK1   | L1                 | 0        | GVDD         |      |

| MCK2   | V2                 | 0        | GVDD         |      |

| МСКЗ   | W1                 | 0        | GVDD         |      |

| MCK4   | Y1                 | 0        | GVDD         |      |

| MCK5   | AB1                | 0        | GVDD         |      |

| MCKE0  | M4                 | 0        | GVDD         | 3    |

| MCKE1  | R5                 | 0        | GVDD         | 3    |

| MCS_B0 | W3                 | 0        | GVDD         |      |

| MCS_B1 | P3                 | 0        | GVDD         |      |

| MCS_B2 | T4                 | 0        | GVDD         |      |

| MCS_B3 | R4                 | 0        | GVDD         |      |

| MDIC0  | AH8                | I/O      | GVDD         | 9    |

| MDIC1  | AJ8                | I/O      | GVDD         | 9    |

| MDM0   | B6                 | 0        | GVDD         | _    |

| MDM1   | B2                 | 0        | GVDD         |      |

| MDM2   | E2                 | 0        | GVDD         |      |

| MDM3   | E1                 | 0        | GVDD         | _    |

| MDM4   | Y6                 | 0        | GVDD         | _    |

| MDM5   | AC6                | 0        | GVDD         | _    |

| MDM6   | AE6                | 0        | GVDD         | _    |

| MDM7   | AJ4                | 0        | GVDD         | _    |

| MDM8   | L6                 | 0        | GVDD         | _    |

| MDQ0   | A8                 | I/O      | GVDD         | 11   |

| MDQ1   | A6                 | I/O      | GVDD         | 11   |

### Table 69. TePBGA II Pinout Listing (continued)

| Signal           | Package Pin Number                 | Pin Type                                | Power Supply | Note |

|------------------|------------------------------------|-----------------------------------------|--------------|------|

| L1_XCOREVSS      | AG14, AG15, AG16, AH16, AG18, AG20 | SerDes Core<br>GND                      | _            | _    |

| L1_XPADVDD       | AE16, AF16, AD18, AE19, AF19       | SerDes I/O<br>Power (1.0 or<br>1.05 V)  |              | _    |

| L1_XPADVSS       | AF14, AE17, AF20                   | SerDes I/O<br>GND                       | _            |      |

|                  | SerDes2 Interface                  |                                         |              |      |

| L2_SD_IMP_CAL_RX | C19                                | I                                       | L2_XPADVDD   |      |

| L2_SD_IMP_CAL_TX | C15                                | I                                       | L2_XPADVDD   |      |

| L2_SD_REF_CLK    | B17                                | I                                       | L2_XPADVDD   |      |

| L2_SD_REF_CLK_B  | A17                                | I                                       | L2_XPADVDD   | _    |

| L2_SD_RXA_N      | A19                                | I                                       | L2_XPADVDD   | _    |

| L2_SD_RXA_P      | B19                                | I                                       | L2_XPADVDD   | _    |

| L2_SD_RXE_N      | A15                                | I                                       | L2_XPADVDD   |      |

| L2_SD_RXE_P      | B15                                | I                                       | L2_XPADVDD   |      |

| L2_SD_TXA_N      | D18                                | 0                                       | L2_XPADVDD   |      |

| L2_SD_TXA_P      | E18                                | 0                                       | L2_XPADVDD   |      |

| L2_SD_TXE_N      | D15                                | 0                                       | L2_XPADVDD   |      |

| L2_SD_TXE_P      | E15                                | 0                                       | L2_XPADVDD   |      |

| L2_SDAVDD_0      | A16                                | SerDes PLL<br>Power<br>(1.0 or 1.05 V)  |              | _    |

| L2_SDAVSS_0      | C17                                | SerDes PLL<br>GND                       | _            |      |

| L2_XCOREVDD      | A14, B14, D17, B18, B20            | SerDes Core<br>Power<br>(1.0 or 1.05 V) |              | _    |

| L2_XCOREVSS      | C14, C16, A18, C18, A20, C20       | SerDes Core<br>GND                      | —            | _    |

| L2_XPADVDD       | D14, E16, F18, D19, E19            | SerDes I/O<br>Power (1.0 or<br>1.05 V)  |              | _    |

| L2_XPADVSS       | D16, E17, D20                      | SerDes I/O<br>GND                       | —            | _    |

|                  | SPI Interface                      |                                         |              |      |

| SPICLK/SD_CLK    | AH9                                | I/O                                     | OVDD         | _    |

### Table 69. TePBGA II Pinout Listing (continued)

|                                        |      |                                                    | Input                          | (MHz) <sup>2</sup> |       |  |

|----------------------------------------|------|----------------------------------------------------|--------------------------------|--------------------|-------|--|

| CFG_CLKIN_DIV<br>at reset <sup>1</sup> | SPMF | <i>csb_clk</i> :<br>Input Clock Ratio <sup>1</sup> | 25                             | 33.33              | 66.67 |  |

|                                        |      |                                                    | <i>csb_clk</i> Frequency (MHz) |                    |       |  |

| Low                                    | 0111 | 7 : 1                                              | 175                            | 233                |       |  |

| Low                                    | 1000 | 8 : 1                                              | 200                            | 267                |       |  |

| Low                                    | 1001 | 9 : 1                                              | 225                            | 300                |       |  |

| Low                                    | 1010 | 10 : 1                                             | 250                            | 333                |       |  |

| Low                                    | 1011 | 11 : 1                                             | 275                            | 367                |       |  |

| Low                                    | 1100 | 12 : 1                                             | 300                            | 400                |       |  |

| Low                                    | 1101 | 13 : 1                                             | 325                            |                    |       |  |

| Low                                    | 1110 | 14 : 1                                             | 350                            |                    |       |  |

| Low                                    | 1111 | 15 : 1                                             | 375                            |                    |       |  |

Table 75. CSB Frequency Options for Agent Mode (continued)

Notes:

1. CFG\_CLKIN\_DIV doubles csb\_clk if set high.

2. CLKIN is the input clock in host mode; PCI\_CLK is the input clock in agent mode.

# 22.2 Core PLL Configuration

RCWLR[COREPLL] selects the ratio between the internal coherent system bus clock (*csb\_clk*) and the e300 core clock (*core\_clk*). Table 76 shows the encodings for RCWLR[COREPLL]. COREPLL values that are not listed in Table 76 should be considered as reserved.

### NOTE

Core VCO frequency = core frequency  $\times$  VCO divider VCO divider has to be set properly so that the core VCO frequency is in the range of 800–1600 MHz.

| RCWLR[COREPLL] |      |   |                                                                | VCO Divider <sup>1</sup>                                          |

|----------------|------|---|----------------------------------------------------------------|-------------------------------------------------------------------|

| 0–1            | 2–5  | 6 | <i>core_clk</i> : <i>csb_clk</i> Ratio                         | VCO Divider                                                       |

| nn             | 0000 | 0 | PLL bypassed<br>(PLL off, <i>csb_clk</i> clocks core directly) | PLL bypassed<br>(PLL off, <i>csb_clk</i> clocks core<br>directly) |

| 11             | nnnn | n | n/a                                                            | n/a                                                               |

| 00             | 0001 | 0 | 1:1                                                            | 2                                                                 |

| 01             | 0001 | 0 | 1:1                                                            | 4                                                                 |

| 10             | 0001 | 0 | 1:1                                                            | 8                                                                 |

| 00             | 0001 | 1 | 1.5:1                                                          | 2                                                                 |

Table 76. e300 Core PLL Configuration

This table shows the heat sink thermal resistance for TePBGA II package with heat sinks, simulated in a standard JEDEC environment, per JESD 51-6.

|                                                |                    | Thermal Resistance |  |

|------------------------------------------------|--------------------|--------------------|--|

| Heat Sink Assuming Thermal Grease              | Air Flow           | (°/W)              |  |

| AAVID 30 $\times$ 30 $\times$ 9.4 mm Pin Fin   | Natural Convection | 13.1               |  |

|                                                | 0.5 m/s            | 10.6               |  |

|                                                | 1 m/s              | 9.3                |  |

|                                                | 2 m/s              | 8.2                |  |

|                                                | 4 m/s              | 7.5                |  |

| AAVID 31 $	imes$ 35 $	imes$ 23 mm Pin Fin      | Natural Convection | 11.1               |  |

|                                                | 0.5 m/s            | 8.5                |  |

|                                                | 1 m/s              | 7.7                |  |

|                                                | 2 m/s              | 7.2                |  |

|                                                | 4 m/s              | 6.8                |  |

| AAVID 43× 41× 16.5mm Pin Fin                   | Natural Convection | 11.3               |  |

|                                                | 0.5 m/s            | 9.0                |  |

|                                                | 1 m/s              | 7.8                |  |

|                                                | 2 m/s              | 7.0                |  |

|                                                | 4 m/s              | 6.5                |  |

| Wakefield, 53 $	imes$ 53 $	imes$ 25 mm Pin Fin | Natural Convection | 9.7                |  |

|                                                | 0.5 m/s            | 7.7                |  |

|                                                | 1 m/s              | 6.8                |  |

|                                                | 2 m/s              | 6.4                |  |

|                                                | 4 m/s              | 6.1                |  |

Heat sink vendors include the following:

Aavid Thermalloy www.aavidthermalloy.com

Alpha Novatech www.alphanovatech.com

International Electronic Research Corporation (IERC) www.ctscorp.com

Millennium Electronics (MEI) www.mei-thermal.com

| Revision | Date    | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2        | 10/2009 | <ul> <li>In Table 3, "Recommended Operating Conditions," added "Operating temperature range" values.</li> <li>In Table 5, "Power Dissipation <sup>1</sup>," corrected maximal application for 800/400 MHz to 4.3 W.</li> <li>In Table 5, "Power Dissipation <sup>1</sup>," added a column for "Typical Application at T<sub>j</sub> = 65°C (W)".</li> <li>In Table 5, "Power Dissipation <sup>1</sup>," added a column for "Sleep Power at T<sub>j</sub> = 65°C (W)".</li> <li>In Table 11, removed overbar from CFG_CLKIN_DIV.</li> <li>In Table 17, "Current Draw Characteristics for MV<sub>REF</sub>," updated I<sub>MVREF</sub> maximum value for both DDR1 and DDR2 to 600 and 400 μA, respectively. Also, updated Note 1 and added Note 2.</li> <li>In Table 20, "DDR1 and DDR2 SDRAM Input AC Timing Specifications," column headings renamed to "Min" and "Max". Footnote 2 updated to state "T is the MCK clock period".</li> <li>In Table 20, "DDR1 and DDR2 SDRAM Input AC Timing Specifications," and Table 21, "DDR1 and DDR2 SDRAM Output AC Timing Specifications," and Table 21, "DDR1 and DDR2 SDRAM Input AC Timing Specifications," and Table 21, "DDR1 and DDR2 SDRAM Output AC Timing Specifications," updated t<sub>RMTDX</sub> to 2.0 ns.</li> <li>In Table 57, Gen 1i/1.5G Transmitter AC Specifications," and Table 59, Gen 2i/3G Transmitter AC Specifications," corrected titles from "Transmitter" to "Receiver".</li> <li>In Table 69, "TePBGA II Pinout Listing," removed pin THERM0; it is now Reserved. Also added 1.05 V to VDD pin.</li> <li>In Table 76, "e300 Core PLL Configuration," added 3.5:1 and 4:1 core_clk: csb_clk ratio options.</li> <li>In Table 76, "e300 Core PLL Configuration," added 3.5:1 and 4:1 core_clk: csb_clk ratio options.</li> <li>In Table 76, "e300 Core PLL Configuration," corrected t<sub>NIKHOX</sub> and t<sub>NEKHOV</sub> respectively.</li> </ul> |

| 1        | 02/2009 | <ul> <li>In Table 3, "Recommended Operating Conditions," added two new rows for 800 MHz, and created two rows for SerDes. In addition, changed 666 to 667 MHz.</li> <li>In Table 5, "Power Dissipation <sup>1</sup>," added Notes 4 and 5. In addition, changed 666 to 667 MHz.</li> <li>In Table 13, "DDR2 SDRAM DC Electrical Characteristics for GV<sub>DD</sub>(typ) = 1.8 V," Table 21, "DDR1 and DDR2 SDRAM Output AC Timing Specifications," and Table 69, "TePBGA II Pinout Listing," added footnote to references to MVREF, MDQ, and MDQS, referencing AN3665, <i>MPC837xE Design Checklist</i>.</li> <li>In Table 21, updated t<sub>DDKHCX</sub> minimum value for 333 MHz to 2.40.</li> <li>In Table 69, "TePBGA II Pinout Listing," added footnote to USBDR_STP_SUSPEND and modified footnote 10 and added footnote 15.</li> <li>In Table 71, "Operating Frequencies for TePBGA II," changed 667 to 800 MHz for <i>core_clk</i>.</li> <li>In Table 77, "Example Clock Frequency Combinations," added 800 MHz cells for e300 core.</li> <li>Updated part numbering information in AF column in Table 81, "Part Numbering Nomenclature." In addition, modified extended temperature information in notes 1 and 4.</li> <li>In Table 82, "Available Parts (Core/DDR Data Rate)," added new row for 800/400 MHz.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 0        | 12/2008 | Initial public release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |