### NXP USA Inc. - MSC8256TVT1000B Datasheet

Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

#### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Details

| Product Status          | Obsolete                                                                       |

|-------------------------|--------------------------------------------------------------------------------|

| Туре                    | SC3850 Six Core                                                                |

| Interface               | Ethernet, I <sup>2</sup> C, PCI, RGMII, Serial RapidIO, SGMII, SPI, UART/USART |

| Clock Rate              | 1GHz                                                                           |

| Non-Volatile Memory     | ROM (96kB)                                                                     |

| On-Chip RAM             | 576kB                                                                          |

| Voltage - I/O           | 2.50V                                                                          |

| Voltage - Core          | 1.00V                                                                          |

| Operating Temperature   | -40°C ~ 105°C (TJ)                                                             |

| Mounting Type           | Surface Mount                                                                  |

| Package / Case          | 783-BBGA, FCBGA                                                                |

| Supplier Device Package | 783-FCPBGA (29x29)                                                             |

| Purchase URL            | https://www.e-xfl.com/product-detail/nxp-semiconductors/msc8256tvt1000b        |

|                         |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

**Pin Assignment**

# 1 Pin Assignment

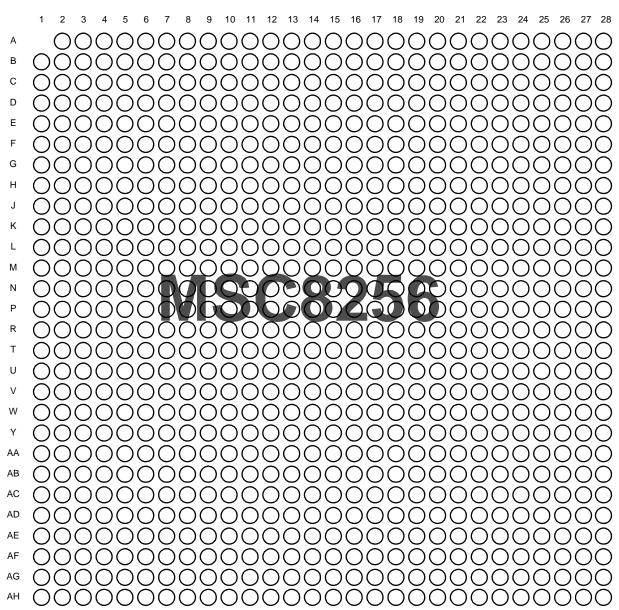

This section includes diagrams of the MSC8256 package ball grid array layouts and tables showing how the pinouts are allocated for the package.

# 1.1 FC-PBGA Ball Layout Diagram

The top view of the FC-PBGA package is shown in Figure 3 with the ball location index numbers.

### Top View

Figure 3. MSC8256 FC-PBGA Package, Top View

# 1.2 Signal List By Ball Location

Table 1 presents the signal list sorted by ball number. When designing a board, make sure that the power rail for each signal is appropriately considered. The specified power rail must be tied to the voltage level specified in this document if any of the related signal functions are used (active)

**Note:** The information in Table 1 and Table 2 distinguishes among three concepts. First, the power pins are the balls of the device package used to supply specific power levels for different device subsystems (as opposed to signals). Second, the power rails are the electrical lines on the board that transfer power from the voltage regulators to the device. They are indicated here as the reference power rails for signal lines; therefore, the actual power inputs are listed as N/A with regard to the power rails. Third, symbols used in these tables are the names for the voltage levels (absolute, recommended, and so on) and not the power supplies themselves.

| Ball Number | Signal Name <sup>1,2</sup> | Pin Type <sup>10</sup> | Power Rail<br>Name |

|-------------|----------------------------|------------------------|--------------------|

| A2          | M2DQS3                     | I/O                    | GVDD2              |

| A3          | M2DQS3                     | I/O                    | GVDD2              |

| A4          | M2ECC0                     | I/O                    | GVDD2              |

| A5          | M2DQS8                     | I/O                    | GVDD2              |

| A6          | M2DQS8                     | I/O                    | GVDD2              |

| A7          | M2A5                       | 0                      | GVDD2              |

| A8          | M2CK1                      | 0                      | GVDD2              |

| A9          | M2CK1                      | 0                      | GVDD2              |

| A10         | M2CS0                      | 0                      | GVDD2              |

| A11         | M2BA0                      | 0                      | GVDD2              |

| A12         | M2CAS                      | 0                      | GVDD2              |

| A13         | M2DQ34                     | I/O                    | GVDD2              |

| A14         | M2DQS4                     | I/O                    | GVDD2              |

| A15         | M2DQS4                     | I/O                    | GVDD2              |

| A16         | M2DQ50                     | I/O                    | GVDD2              |

| A17         | M2DQS6                     | I/O                    | GVDD2              |

| A18         | M2DQS6                     | I/O                    | GVDD2              |

| A19         | M2DQ48                     | I/O                    | GVDD2              |

| A20         | M2DQ49                     | I/O                    | GVDD2              |

| A21         | VSS                        | Ground                 | N/A                |

| A22         | Reserved                   | NC                     | _                  |

| A23         | SXPVDD1                    | Power                  | N/A                |

| A24         | SXPVSS1                    | Ground                 | N/A                |

| A25         | Reserved                   | NC                     | _                  |

| A26         | Reserved                   | NC                     | _                  |

| A27         | SXCVDD1                    | Power                  | N/A                |

| A28         | SXCVSS1                    | Ground                 | N/A                |

| B1          | M2DQ24                     | I/O                    | GVDD2              |

| B2          | GVDD2                      | Power                  | N/A                |

| B3          | M2DQ25                     | I/O                    | GVDD2              |

| B4          | VSS                        | Ground                 | N/A                |

| B5          | GVDD2                      | Power                  | N/A                |

| B6          | M2ECC1                     | I/O                    | GVDD2              |

| B7          | VSS                        | Ground                 | N/A                |

| B8          | GVDD2                      | Power                  | N/A                |

### Table 1. Signal List by Ball Number

| Ball Number | Signal Name <sup>1,2</sup>   | Pin Type <sup>10</sup> | Power Rail<br>Name |

|-------------|------------------------------|------------------------|--------------------|

| G7          | M2CKE0                       | 0                      | GVDD2              |

| G8          | M2A11                        | 0                      | GVDD2              |

| G9          | M2A7                         | 0                      | GVDD2              |

| G10         | M2CK2                        | 0                      | GVDD2              |

| G11         | M2APAR_OUT                   | 0                      | GVDD2              |

| G12         | M2ODT1                       | 0                      | GVDD2              |

| G13         | M2APAR_IN                    | I                      | GVDD2              |

| G14         | M2DQ43                       | I/O                    | GVDD2              |

| G15         | M2DM5                        | 0                      | GVDD2              |

| G16         | M2DQ44                       | I/O                    | GVDD2              |

| G17         | M2DQ40                       | I/O                    | GVDD2              |

| G18         | M2DQ59                       | I/O                    | GVDD2              |

| G19         | M2DM7                        | 0                      | GVDD2              |

| G20         | M2DQ60                       | I/O                    | GVDD2              |

| G21         | Reserved                     | NC                     | _                  |

| G22         | Reserved                     | NC                     | _                  |

| G23         | SXPVSS1                      | Ground                 | N/A                |

| G24         | SXPVDD1                      | Power                  | N/A                |

| G25         | SR1_IMP_CAL_TX               | I                      | SXCVDD1            |

| G26         | SXCVSS1                      | Ground                 | N/A                |

| G27         | Reserved                     | NC                     | _                  |

| G28         | Reserved                     | NC                     |                    |

| H1          | GVDD2                        | Power                  | N/A                |

| H2          | VSS                          | Ground                 | N/A                |

| H3          | M2DQ18                       | I/O                    | GVDD2              |

| H4          | GVDD2                        | Power                  | N/A                |

| H5          | VSS                          | Ground                 | N/A                |

| H6          | M2DQ20                       | I/O                    | GVDD2              |

| H7          | GVDD2                        | Power                  | N/A                |

| H8          | VSS                          | Ground                 | N/A                |

| H9          | M2A15                        | 0                      | GVDD2              |

| H10         | M2CK2                        | 0                      | GVDD2              |

| H11         | M2MDIC0                      | I/O                    | GVDD2              |

| H12         | M2VREF                       |                        | GVDD2              |

| H13         | M2MDIC1                      | I/O                    | GVDD2              |

| H14         | M2DQ46                       | I/O                    | GVDD2              |

| H15         | M2DQ47                       | I/O                    | GVDD2              |

| H16         | M2DQ45                       | I/O                    | GVDD2              |

| H17         | M2DQ41                       | I/O                    | GVDD2              |

| H18         | M2DQ62                       | I/O                    | GVDD2              |

| H19         | M2DQ63                       | I/O                    | GVDD2              |

| H20         | M2DQ61                       | I/O                    | GVDD2              |

| H21         | Reserved                     | NC                     | _                  |

| H22         | Reserved                     | NC                     |                    |

| H23         | SR1_TXD3/SG2_TX <sup>4</sup> | 0                      | SXPVDD1            |

| H24         | SR1_TXD3/SG2_TX <sup>4</sup> | 0                      | SXPVDD1            |

| Ball Number | Signal Name <sup>1,2</sup>   | Pin Type <sup>10</sup> | Power Rail<br>Name |

|-------------|------------------------------|------------------------|--------------------|

| H25         | SXCVSS1                      | Ground                 | N/A                |

| H26         | SXCVDD1                      | Power                  | N/A                |

| H27         | SR1_RXD3/SG2_RX <sup>4</sup> | I                      | SXCVDD1            |

| H28         | SR1_RXD3/SG2_RX <sup>4</sup> | I                      | SXCVDD1            |

| J1          | M2DQS1                       | I/O                    | GVDD2              |

| J2          | M2DQS1                       | I/O                    | GVDD2              |

| J3          | M2DQ10                       | I/O                    | GVDD2              |

| J4          | M2DQ11                       | I/O                    | GVDD2              |

| J5          | M2DQ14                       | I/O                    | GVDD2              |

| J6          | M2DQ23                       | I/O                    | GVDD2              |

| J7          | M2ODT0                       | 0                      | GVDD2              |

| J8          | M2A12                        | 0                      | GVDD2              |

| J9          | M2A14                        | 0                      | GVDD2              |

| J10         | VSS                          | Ground                 | N/A                |

| J11         | GVDD2                        | Power                  | N/A                |

| J12         | VSS                          | Ground                 | N/A                |

| J13         | GVDD2                        | Power                  | N/A                |

| J14         | VSS                          | Ground                 | N/A                |

| J15         | GVDD2                        | Power                  | N/A                |

| J16         | VSS                          | Ground                 | N/A                |

| J17         | GVDD2                        | Power                  | N/A                |

| J18         | VSS                          | Ground                 | N/A                |

| J19         | GVDD2                        | Power                  | N/A                |

| J20         | Reserved                     | NC                     | _                  |

| J21         | Reserved                     | NC                     | _                  |

| J22         | Reserved                     | NC                     | _                  |

| J23         | SXPVDD1                      | Power                  | N/A                |

| J24         | SXPVSS1                      | Ground                 | N/A                |

| J25         | SXCVDD1                      | Power                  | N/A                |

| J26         | SXCVSS1                      | Ground                 | N/A                |

| J27         | SXCVDD1                      | Power                  | N/A                |

| J28         | SXCVSS1                      | Ground                 | N/A                |

| K1          | VSS                          | Ground                 | N/A                |

| K2          | GVDD2                        | Power                  | N/A                |

| K3          | M2DM1                        | 0                      | GVDD2              |

| K4          | VSS                          | Ground                 | N/A                |

| K5          | GVDD2                        | Power                  | N/A                |

| K6          | M2DQ0                        | I/O                    | GVDD2              |

| K7          | VSS                          | Ground                 | N/A                |

| K8          | GVDD2                        | Power                  | N/A                |

| K9          | M2DQ5                        | I/O                    | GVDD2              |

| K10         | VSS                          | Ground                 | N/A                |

| K11         | VDD                          | Power                  | N/A                |

| K12         | VSS                          | Ground                 | N/A                |

| K13         | VDD                          | Power                  | N/A                |

| K14         | VSS                          | Ground                 | N/A                |

| Ball Number | Signal Name <sup>1,2</sup>    | Pin Type <sup>10</sup> | Power Rail<br>Name |

|-------------|-------------------------------|------------------------|--------------------|

| U3          | GVDD1                         | Power                  | N/A                |

| U4          | M1DQ15                        | I/O                    | GVDD1              |

| U5          | M1DQ1                         | I/O                    | GVDD1              |

| U6          | VSS                           | Ground                 | N/A                |

| U7          | GVDD1                         | Power                  | N/A                |

| U8          | M1DQ7                         | I/O                    | GVDD1              |

| U9          | M1DQ6                         | I/O                    | GVDD1              |

| U10         | VDD                           | Power                  | N/A                |

| U11         | VSS                           | Ground                 | N/A                |

| U12         | M3VDD                         | Power                  | N/A                |

| U13         | VSS                           | Ground                 | N/A                |

| U14         | VDD                           | Power                  | N/A                |

| U15         | VSS                           | Ground                 | N/A                |

| U16         | VDD                           | Power                  | N/A                |

| U17         | VSS                           | Ground                 | N/A                |

| U18         | VDD                           | Power                  | N/A                |

| U19         | VSS                           | Ground                 | N/A                |

| U20         | VSS                           | Ground                 | N/A                |

| U21         | VSS                           | Ground                 | N/A                |

| U22         | VSS                           | Non-user               | N/A                |

| U23         | SR2_TXD0/PE_TXD0 <sup>4</sup> | 0                      | SXPVDD2            |

| U24         | SR2_TXD0/PE_TXD0 <sup>4</sup> | 0                      | SXPVDD2            |

| U25         | SXCVDD2                       | Power                  | N/A                |

| U26         | SXCVSS2                       | Ground                 | N/A                |

| U27         | SR2_RXD0/PE_RXD0 <sup>4</sup> | I                      | SXCVDD2            |

| U28         | SR2_RXD0/PE_RXD0 <sup>4</sup> | I                      | SXCVDD2            |

| V1          | M1DQ9                         | I/O                    | GVDD1              |

| V2          | M1DQ12                        | I/O                    | GVDD1              |

| V3          | M1DQ13                        | I/O                    | GVDD1              |

| V4          | M1DQS0                        | I/O                    | GVDD1              |

| V5          | M1DQS0                        | I/O                    | GVDD1              |

| V6          | M1DM0                         | 0                      | GVDD1              |

| V7          | M1DQ3                         | I/O                    | GVDD1              |

| V8          | M1DQ2                         | I/O                    | GVDD1              |

| V9          | M1DQ4                         | I/O                    | GVDD1              |

| V10         | VSS                           | Ground                 | N/A                |

| V11         | VDD                           | Power                  | N/A                |

| V12         | VSS                           | Ground                 | N/A                |

| V13         | VDD                           | Power                  | N/A                |

| V14         | VSS                           | Ground                 | N/A                |

| V15         | VDD                           | Power                  | N/A                |

| V16         | VSS                           | Ground                 | N/A                |

| V17         | VDD                           | Power                  | N/A                |

| V18         | VSS                           | Ground                 | N/A                |

| V19         | VDD                           | Power                  | N/A                |

| V20         | NVDD                          | Power                  | N/A                |

| Ball Number | Signal Name <sup>1,2</sup>            | Pin Type <sup>10</sup> | Power Rail<br>Name |

|-------------|---------------------------------------|------------------------|--------------------|

| Y11         | GVDD1                                 | Power                  | N/A                |

| Y12         | VSS                                   | Ground                 | N/A                |

| Y13         | GVDD1                                 | Power                  | N/A                |

| Y14         | VSS                                   | Ground                 | N/A                |

| Y15         | GVDD1                                 | Power                  | N/A                |

| Y16         | VSS                                   | Ground                 | N/A                |

| Y17         | GVDD1                                 | Power                  | N/A                |

| Y18         | VSS                                   | Ground                 | N/A                |

| Y19         | GVDD1                                 | Power                  | N/A                |

| Y20         | VSS                                   | Ground                 | N/A                |

| Y21         | NVDD                                  | Power                  | N/A                |

| Y22         | GPIO20/SPI_SL <sup>5,8</sup>          | I/O                    | NVDD               |

| Y23         | GPIO17/SPI_SCK <sup>5,8</sup>         | I/O                    | NVDD               |

| Y24         | GPIO14/DRQ0/IRQ14/RC14 <sup>5,8</sup> | I/O                    | NVDD               |

| Y25         | GPIO12/IRQ12/RC12 <sup>5,8</sup>      | I/O                    | NVDD               |

| Y26         | GPIO8/IRQ8/RC8 <sup>5,8</sup>         | I/O                    | NVDD               |

| Y27         | NVDD                                  | Power                  | N/A                |

| Y28         | VSS                                   | Ground                 | N/A                |

| AA1         | GVDD1                                 | Power                  | N/A                |

| AA2         | VSS                                   | Ground                 | N/A                |

| AA3         | M1DQ18                                | I/O                    | GVDD1              |

| AA4         | GVDD1                                 | Power                  | N/A                |

| AA5         | VSS                                   | Ground                 | N/A                |

| AA6         | M1DQ20                                | I/O                    | GVDD1              |

| AA7         | GVDD1                                 | Power                  | N/A                |

| AA8         | VSS                                   | Ground                 | N/A                |

| AA9         | M1A15                                 | 0                      | GVDD1              |

| AA10        | M1CK2                                 | 0                      | GVDD1              |

| AA11        | M1MDIC0                               | I/O                    | GVDD1              |

| AA12        | M1VREF                                | I                      | GVDD1              |

| AA13        | M1MDIC1                               | I/O                    | GVDD1              |

| AA14        | M1DQ46                                | I/O                    | GVDD1              |

| AA15        | M1DQ47                                | I/O                    | GVDD1              |

| AA16        | M1DQ45                                | I/O                    | GVDD1              |

| AA17        | M1DQ41                                | I/O                    | GVDD1              |

| AA18        | M1DQ62                                | I/O                    | GVDD1              |

| AA19        | M1DQ63                                | I/O                    | GVDD1              |

| AA20        | M1DQ61                                | I/O                    | GVDD1              |

| AA21        | VSS                                   | Ground                 | N/A                |

| AA22        | GPIO21 <sup>5,8</sup>                 | I/O                    | NVDD               |

| AA23        | GPIO18/SPI_MOSI <sup>5,8</sup>        | I/O                    | NVDD               |

| AA24        | GPIO16/RC16 <sup>5,8</sup>            | I/O                    | NVDD               |

| AA25        | GPIO4/DDN1/IRQ4/RC4 <sup>5,8</sup>    | I/O                    | NVDD               |

| AA26        | GPIO9/IRQ9/RC9 <sup>5,8</sup>         | I/O                    | NVDD               |

| AA27        | GPIO6/IRQ6/RC6 <sup>5,8</sup>         | I/O                    | NVDD               |

| AA28        | GPIO1/IRQ1/RC1 <sup>5,8</sup>         | I/O                    | NVDD               |

| Ball Number | Signal Name <sup>1,2</sup>          | Pin Type <sup>10</sup> | Power Rail<br>Name |

|-------------|-------------------------------------|------------------------|--------------------|

| AB1         | M1DQS2                              | I/O                    | GVDD1              |

| AB2         | M1DQS2                              | I/O                    | GVDD1              |

| AB3         | M1DQ19                              | I/O                    | GVDD1              |

| AB4         | M1DM2                               | 0                      | GVDD1              |

| AB5         | M1DQ21                              | I/O                    | GVDD1              |

| AB6         | M1DQ22                              | I/O                    | GVDD1              |

| AB7         | M1CKE0                              | 0                      | GVDD1              |

| AB8         | M1A11                               | 0                      | GVDD1              |

| AB9         | M1A7                                | 0                      | GVDD1              |

| AB10        | M1CK2                               | 0                      | GVDD1              |

| AB11        | M1APAR_OUT                          | 0                      | GVDD1              |

| AB12        | M1ODT1                              | 0                      | GVDD1              |

| AB13        | M1APAR_IN                           | 1                      | GVDD1              |

| AB14        | M1DQ43                              | I/O                    | GVDD1              |

| AB15        | M1DM5                               | 0                      | GVDD1              |

| AB16        | M1DQ44                              | I/O                    | GVDD1              |

| AB17        | M1DQ40                              | I/O                    | GVDD1              |

| AB18        | M1DQ59                              | I/O                    | GVDD1              |

| AB19        | M1DM7                               | 0                      | GVDD1              |

| AB20        | M1DQ60                              | I/O                    | GVDD1              |

| AB21        | VSS                                 | Ground                 | N/A                |

| AB22        | GPIO31/I2C_SDA <sup>5,8</sup>       | I/O                    | NVDD               |

| AB23        | GPIO27/TMR4/RCW_SRC0 <sup>5,8</sup> | I/O                    | NVDD               |

| AB24        | GPIO25/TMR2/RCW_SRC1 <sup>5,8</sup> | I/O                    | NVDD               |

| AB25        | GPIO24/TMR1/RCW_SRC2 <sup>5,8</sup> | I/O                    | NVDD               |

| AB26        | GPIO10/IRQ10/RC10 <sup>5,8</sup>    | I/O                    | NVDD               |

| AB27        | GPIO5/IRQ5/RC5 <sup>5,8</sup>       | I/O                    | NVDD               |

| AB28        | GPIO0/IRQ0/RC0 <sup>5,8</sup>       | I/O                    | NVDD               |

| AC1         | VSS                                 | Ground                 | N/A                |

| AC2         | GVDD1                               | Power                  | N/A                |

| AC3         | M1DQ16                              | I/O                    | GVDD1              |

| AC4         | VSS                                 | Ground                 | N/A                |

| AC5         | GVDD1                               | Power                  | N/A                |

| AC6         | M1DQ17                              | I/O                    | GVDD1              |

| AC7         | VSS                                 | Ground                 | N/A                |

| AC8         | GVDD1                               | Power                  | N/A                |

| AC9         | M1BA2                               | 0                      | GVDD1              |

| AC10        | VSS                                 | Ground                 | N/A                |

| AC11        | GVDD1                               | Power                  | N/A                |

| AC12        | M1A4                                | 0                      | GVDD1              |

| AC13        | VSS                                 | Ground                 | N/A                |

| AC14        | GVDD1                               | Power                  | N/A                |

| AC15        | M1DQ42                              | I/O                    | GVDD1              |

| AC16        | VSS                                 | Ground                 | N/A                |

| AC17        | GVDD1                               | Power                  | N/A                |

| AC18        | M1DQ58                              | I/O                    | GVDD1              |

| Ball Number | Signal Name <sup>1,2</sup>       | Pin Type <sup>10</sup> | Power Rail<br>Name |

|-------------|----------------------------------|------------------------|--------------------|

| AF27        | TDM2TDT/GE1_TX_CLK <sup>3</sup>  | I/O                    | NVDD               |

| AF28        | TDM3RSN/GE1_RD1 <sup>3</sup>     | I/O                    | NVDD               |

| AG1         | M1DQ24                           | I/O                    | GVDD1              |

| AG2         | GVDD1                            | Power                  | N/A                |

| AG3         | M1DQ25                           | I/O                    | GVDD1              |

| AG4         | VSS                              | Ground                 | N/A                |

| AG5         | GVDD1                            | Power                  | N/A                |

| AG6         | M1ECC1                           | I/O                    | GVDD1              |

| AG7         | VSS                              | Ground                 | N/A                |

| AG8         | GVDD1                            | Power                  | N/A                |

| AG9         | M1A13                            | 0                      | GVDD1              |

| AG10        | VSS                              | Ground                 | N/A                |

| AG11        | GVDD1                            | Power                  | N/A                |

| AG12        | M1CS1                            | 0                      | GVDD1              |

| AG13        | VSS                              | Ground                 | N/A                |

| AG14        | GVDD1                            | Power                  | N/A                |

| AG15        | M1DQ35                           | I/O                    | GVDD1              |

| AG16        | VSS                              | Ground                 | N/A                |

| AG17        | GVDD1                            | Power                  | N/A                |

| AG18        | M1DQ51                           | I/O                    | GVDD1              |

| AG19        | VSS                              | Ground                 | N/A                |

| AG20        | GVDD1                            | Power                  | N/A                |

| AG21        | NVDD                             | Power                  | N/A                |

| AG22        | TDM1TSN/GE2_TD1 <sup>3</sup>     | I/O                    | NVDD               |

| AG23        | TDM1RDT/GE2_TX_CLK <sup>3</sup>  | I/O                    | NVDD               |

| AG24        | TDM0TCK/GE2_GTX_CLK <sup>3</sup> | I/O                    | NVDD               |

| AG25        | TDM1TDT/GE2_TD0 <sup>3</sup>     | I/O                    | NVDD               |

| AG26        | VSS                              | Ground                 | N/A                |

| AG27        | NVDD                             | Power                  | N/A                |

| AG28        | TDM3RDT/GE1_RD0 <sup>3</sup>     | I/O                    | NVDD               |

| AH1         | Reserved.                        | NC                     | _                  |

| AH2         | M1DQS3                           | I/O                    | GVDD1              |

| AH3         | M1DQS3                           | I/O                    | GVDD1              |

| AH4         | M1ECC0                           | I/O                    | GVDD1              |

| AH5         | M1DQS8                           | I/O                    | GVDD1              |

| AH6         | M1DQS8                           | I/O                    | GVDD1              |

| AH7         | M1A5                             | 0                      | GVDD1              |

| AH8         | M1CK1                            | 0                      | GVDD1              |

| AH9         | M1CK1                            | 0                      | GVDD1              |

| AH10        | M1CS0                            | 0                      | GVDD1              |

| AH11        | M1BA0                            | 0                      | GVDD1              |

| AH12        | M1CAS                            | 0                      | GVDD1              |

| AH13        | M1DQ34                           | I/O                    | GVDD1              |

| AH14        | M1DQS4                           | I/O                    | GVDD1              |

| AH15        | M1DQS4                           | I/O                    | GVDD1              |

| AH16        | M1DQ50                           | I/O                    | GVDD1              |

| Ball Numbe                                    | er                                            | Signal Name <sup>1,2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Pin Type <sup>10</sup>                                          | Power Rail<br>Name                     |

|-----------------------------------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|----------------------------------------|

| AH17                                          |                                               | M1DQS6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | I/O                                                             | GVDD1                                  |

| AH18                                          |                                               | M1DQS6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | I/O                                                             | GVDD1                                  |

| AH19                                          |                                               | M1DQ48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | I/O                                                             | GVDD1                                  |

| AH20                                          |                                               | M1DQ49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | I/O                                                             | GVDD1                                  |

| AH21                                          |                                               | VSS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Ground                                                          | N/A                                    |

| AH22                                          |                                               | TDM0RCK/GE2_RD2 <sup>3</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | I/O                                                             | NVDD                                   |

| AH23                                          |                                               | TDM0RDT/GE2_RD3 <sup>3</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | I/O                                                             | NVDD                                   |

| AH24                                          |                                               | TDM0TSN/GE2_RD0 <sup>3</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | I/O                                                             | NVDD                                   |

| AH25                                          |                                               | TDM1RCK/GE2_RD1 <sup>3</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | I/O                                                             | NVDD                                   |

| AH26                                          |                                               | TDM3TDT/GE1_RD3 <sup>3</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | I/O                                                             | NVDD                                   |

| AH27                                          |                                               | TDM3TCK/GE1_RD2 <sup>3</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | I                                                               | NVDD                                   |

| AH28                                          |                                               | VSS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Ground                                                          | N/A                                    |

| Notes: 1.<br>2.<br>3.<br>4.<br>5.<br>6.<br>7. | for<br>Unc<br>Sig<br>Sel<br>Sel<br>Cha<br>Ope | served signals should be disconnected for compatibility with future revisions of the manufacturing and test purposes only. The assigned signal name is used to indica connected (Reserved), pulled down (VSS), or pulled up (VDD). nal function during power-on reset is determined by the RCW source type. ection of TDM versus RGMII functionality is determined by the RCW bit values. ection of RapidIO, SGMII, and PCI Express functionality is determined by the RCW bit values. Fapter in the <i>MSC8256 Reference Manual</i> . en-drain signal. | ate whether the signa<br>W bit values.<br>or configuration deta | al must be<br>ils, see the <i>GPIO</i> |

| 8.                                            | pro                                           | signals with GPIO functionality, the open-drain and internal 20 K $\Omega$ pull-up resisto gramming. See the GPIO chapter of the MSC8256 Reference Manual for configure                                                                                                                                                                                                                                                                                                                                                                                 | ration details.                                                 | , ,                                    |

| ~                                             | 0.1                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | · · · · · · · · · · · · · · · · · · ·                           | and a factor that                      |

Connect to power supply via external filter. See Section 3.2, *PLL Power Supply Design Considerations* for details.

Pin types are: Ground = all VSS connections; Power = all VDD connections; I = Input; O = Output; I/O = Input/Output; NC = not connected.

### 2.5.1.3 DDR2/DDR3 SDRAM Capacitance

Table 8 provides the DDR controller interface capacitance for DDR2 and DDR3 memory.

**Note:** At recommended operating conditions (see Table 3) with V<sub>DDDDR</sub> = 1.8 V for DDR2 memory or V<sub>DDDDR</sub> = 1.5 V for DDR3 memory.

| Parameter                                               | Symbol           | Min | Мах | Unit |  |

|---------------------------------------------------------|------------------|-----|-----|------|--|

| I/O capacitance: DQ, DQS, DQS                           | C <sub>IO</sub>  | 6   | 8   | pF   |  |

| Delta I/O capacitance: DQ, DQS, DQS                     | C <sub>DIO</sub> | —   | 0.5 | pF   |  |

| Note: Guaranteed by FAB process and micro-construction. |                  |     |     |      |  |

#### Table 8. DDR2/DDR3 SDRAM Capacitance

### 2.5.1.4 DDR Reference Current Draw

Table 9 lists the current draw characteristics for MV<sub>REF</sub>.

Note: Values when used at recommended operating conditions (see Table 3).

### Table 9. Current Draw Characteristics for MV<sub>REF</sub>

| Parameter / Condition                                               | Symbol              | Min | Max        | Unit     |

|---------------------------------------------------------------------|---------------------|-----|------------|----------|

| Current draw for MV <sub>REFn</sub><br>• DDR2 SDRAM<br>• DDR3 SDRAM | I <sub>MVREFn</sub> |     | 300<br>250 | μΑ<br>μΑ |

# 2.5.2 High-Speed Serial Interface (HSSI) DC Electrical Characteristics

The MSC8256 features an HSSI that includes two 4-channel SerDes ports used for high-speed serial interface applications (PCI Express, Serial RapidIO interfaces, and SGMII). This section and its subsections describe the common portion of the SerDes DC, including the DC requirements for the SerDes reference clocks and the SerDes data lane transmitter (Tx) and receiver (Rx) reference circuits. The data lane circuit specifications are specific for each supported interface, and they have individual subsections by protocol. The selection of individual data channel functionality is done via the Reset Configuration Word High Register (RCWHR) SerDes Protocol selection fields (S1P and S2P). Specific AC electrical characteristics are defined in Section 2.6.2, "HSSI AC Timing Specifications."

## 2.5.2.1 Signal Term Definitions

The SerDes interface uses differential signalling to transfer data across the serial link. This section defines terms used in the description and specification of differential signals. Figure 4 shows how the signals are defined. For illustration purposes only, one SerDes lane is used in the description. Figure 4 shows the waveform for either a transmitter output (SR[1–2]\_TX and

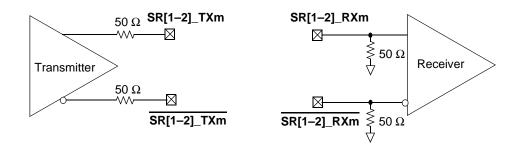

# 2.5.2.3 SerDes Transmitter and Receiver Reference Circuits

Figure 6 shows the reference circuits for SerDes data lane transmitter and receiver.

Note: The [1–2] indicates the specific SerDes Interface (1 or 2) and the m indicates the specific channel within that interface (0,1,2,3). Actual signals are assigned by the HRCW assignments at reset (see **Chapter 5**, *Reset* in the reference manual for details)

Figure 6. SerDes Transmitter and Receiver Reference Circuits

# 2.5.3 DC-Level Requirements for SerDes Interfaces

The following subsections define the DC-level requirements for the SerDes reference clocks, the PCI Express data lines, the Serial RapidIO data lines, and the SGMII data lines.

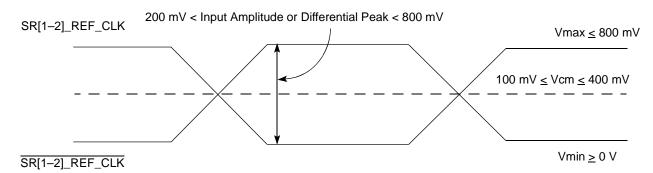

# 2.5.3.1 DC-Level Requirements for SerDes Reference Clocks

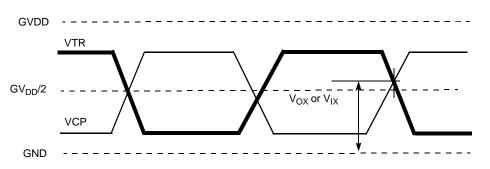

The DC-level requirement for the SerDes reference clock inputs is different depending on the signaling mode used to connect the clock driver chip and SerDes reference clock inputs, as described below:

- Differential Mode

- The input amplitude of the differential clock must be between 400 mV and 1600 mV differential peak-peak (or between 200 mV and 800 mV differential peak). In other words, each signal wire of the differential pair must have a single-ended swing of less than 800 mV and greater than 200 mV. This requirement is the same for both external DC-coupled or AC-coupled connection.

- For an external DC-coupled connection, the maximum average current requirements sets the requirement for average voltage (common mode voltage) as between 100 mV and 400 mV. Figure 7 shows the SerDes reference clock input requirement for DC-coupled connection scheme.

| Parameter                       | Symbol          | Min | Typical | Мах  | Units | Notes |

|---------------------------------|-----------------|-----|---------|------|-------|-------|

| Differential input voltage      | V <sub>IN</sub> | 200 | —       | 1600 | mVp-p | 1     |

| Notes: 1. Measured at receiver. |                 |     |         |      |       |       |

#### Table 14. Serial RapidIO Receiver DC Specifications

### 2.5.3.4 DC-Level Requirements for SGMII Configurations

**Note:** Specifications are valid at the recommended operating conditions listed in Table 3

Table 15 describes the SGMII SerDes transmitter AC-coupled DC electrical characteristics. Transmitter DC characteristics are measured at the transmitter outputs ( $SR[1-2]_TX[n]$  and  $\overline{SR[1-2]_TX}[n]$ ) as shown in Figure 10.

| Parameter                                                               | Symbol                                                | Min                                                                                                                                                                         | Тур                                    | Max                                     | Unit                     | Notes  |

|-------------------------------------------------------------------------|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-----------------------------------------|--------------------------|--------|

| Output high voltage                                                     | V <sub>OH</sub>                                       | _                                                                                                                                                                           | _                                      | $XV_{DD_SRDS-Typ}/2 +  V_{OD} _{max}/2$ | mV                       | 1      |

| Output low voltage                                                      | V <sub>OL</sub>                                       | $XV_{DD_SRDS-Typ}/2 -  V_{OD} _{max}/2$                                                                                                                                     | _                                      |                                         | mV                       | 1      |

| Output differential                                                     | V <sub>OD</sub>                                       | 323                                                                                                                                                                         | 500                                    | 725                                     | mV                       | 2,3,4  |

| voltage (XV <sub>DD-Typ</sub> at                                        |                                                       | 296                                                                                                                                                                         | 459                                    | 665                                     |                          | 2,3,5  |

| 1.0 V)                                                                  |                                                       | 269                                                                                                                                                                         | 417                                    | 604                                     |                          | 2,3,6  |

|                                                                         |                                                       | 243                                                                                                                                                                         | 376                                    | 545                                     |                          | 2,3,7  |

|                                                                         |                                                       | 215                                                                                                                                                                         | 333                                    | 483                                     |                          | 2,3,8  |

|                                                                         |                                                       | 189                                                                                                                                                                         | 292                                    | 424                                     |                          | 2,3,9  |

|                                                                         |                                                       | 162                                                                                                                                                                         | 250                                    | 362                                     |                          | 2,3,10 |

| Output impedance R <sub>O</sub> 40<br>(single-ended)                    |                                                       | 50                                                                                                                                                                          | 60                                     | Ω                                       | _                        |        |

| <ul> <li>2. The  V<sub>OE</sub> equalization</li> <li>The MS</li> </ul> | ) value shown<br>ion setting in t<br>B (bit 0) of the | DC-coupled SGMII. $XV_{DD\_SRDS2-Typ}$ =<br>in the table assumes full multitude b<br>he XMITEQ <b>AB</b> (for lanes A and B) o<br>e above bit field is set to zero (selecti | y setting s<br>r XMITEC<br>ng the full | EF (for lanes E and F) bit field of Co  | ntrol Regi<br>er up defa |        |

Table 15. SGMII DC Transmitter Electrical Characteristics

• The LSB (bit [1–3]) of the above bit field is set based on the equalization settings listed in notes 4 through 10.

3. The  $|V_{OD}|$  value shown in the Typ column is based on the condition of  $XV_{DD\_SRDS2-Typ} = 1.0$  V, no common mode offset variation ( $V_{OS} = 500$  mV), SerDes transmitter is terminated with 100- $\Omega$  differential load between

- 4. Equalization setting: 1.0x: 0000.

- 5. Equalization setting: 1.09x: 1000.

- 6. Equalization setting: 1.2x: 0100.

- 7. Equalization setting: 1.33x: 1100.

- 8. Equalization setting: 1.5x: 0010.

- 9. Equalization setting: 1.71x: 1010.

- 10. Equalization setting: 2.0x: 0110.

- 11.  $|V_{OD}| = |V_{SR[1-2] TXn} V_{\overline{SR[1-2] TXn}}|$ .  $|V_{OD}|$  is also referred to as output differential peak voltage.  $V_{TX-DIFFp-p} = 2^*|V_{OD}|$ .

# 2.5.4 **RGMII and Other Interface DC Electrical Characteristics**

Table 17 describes the DC electrical characteristics for the following interfaces:

- RGMII Ethernet

- SPI

- TDM

- GPIO

- UART

- TIMER

- EE

- I<sup>2</sup>C

- Interrupts (IRQn, NMI\_OUT, INT\_OUT)

- Clock and resets (CLKIN, PORESET, HRESET, SRESET)

- DMA External Request

- JTAG signals

### Table 17. 2.5 V I/O DC Electrical Characteristics

| Characteristic                                                                                                                                                                                                                                                                     | Symbol          | Min       | Max         | Unit | Notes |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------|-------------|------|-------|

| Input high voltage                                                                                                                                                                                                                                                                 | V <sub>IH</sub> | 1.7       | _           | V    | 1     |

| Input low voltage                                                                                                                                                                                                                                                                  | V <sub>IL</sub> | —         | 0.7         | V    | 1     |

| Input high current (V <sub>IN</sub> = V <sub>DDIO</sub> )                                                                                                                                                                                                                          | I <sub>IN</sub> | —         | 30          | μΑ   | 2     |

| Output high voltage ( $V_{DDIO} = min, I_{OH} = -1.0 mA$ )                                                                                                                                                                                                                         | V <sub>OH</sub> | 2.0       | VDDIO + 0.3 | V    | 1     |

| Output low voltage (V <sub>DDIO</sub> = min, I <sub>OL</sub> = 1.0 mA)                                                                                                                                                                                                             | V <sub>OL</sub> | GND – 0.3 | 0.40        | V    | 1     |

| <ol> <li>Notes: 1. The min V<sub>IL</sub> and max V<sub>IH</sub> values are based on the respective min and max V<sub>IN</sub> values listed in Table 3.</li> <li>2. The symbol V<sub>IN</sub> represents the input voltage of the supply. It is referenced in Table 3.</li> </ol> |                 |           |             |      |       |

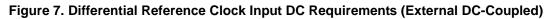

Figure 13 shows the DDR SDRAM output timing diagram.

Figure 13. DDR SDRAM Output Timing

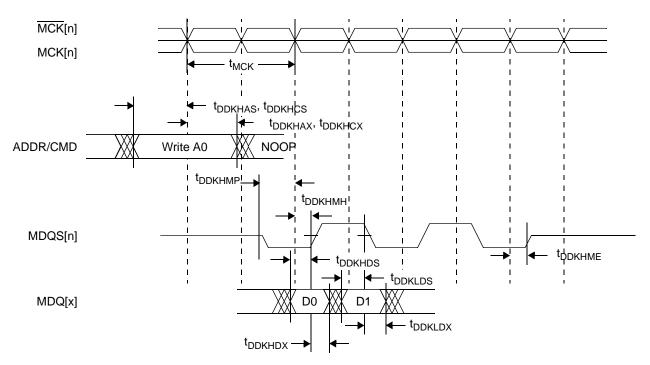

Figure 14 provides the AC test load for the DDR2 and DDR3 controller bus.

Figure 14. DDR2 and DDR3 Controller Bus AC Test Load

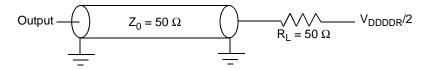

## 2.6.1.3 DDR2 and DDR3 SDRAM Differential Timing Specifications

This section describes the DC and AC differential timing specifications for the DDR2 and DDR3 SDRAM controller interface. Figure 15 shows the differential timing specification.

Figure 15. DDR2 and DDR3 SDRAM Differential Timing Specifications

Note: VTR specifies the true input signal (such as MCK or MDQS) and VCP is the complementary input signal (such as  $\overline{MCK}$  or  $\overline{MDQS}$ ).

# 2.6.5 Ethernet Timing

This section describes the AC electrical characteristics for the Ethernet interface.

There are programmable delay units (PDU) that should be programmed differently for each interface to meet timing. There is a general configuration register 4 (GCR4) used to configure the timing. For additional information, see the *MSC8256 Reference Manual*.

## 2.6.5.1 Management Interface Timing

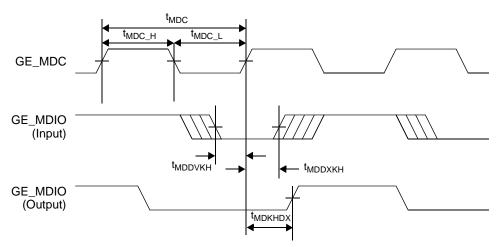

Table 33 lists the timer input Ethernet controller management interface timing specifications shown in Figure 24.

| Table 33. Ethernet Controller Management Interface Tir | nina |

|--------------------------------------------------------|------|

|--------------------------------------------------------|------|

| Characteristics                          | Symbol              | Min | Max | Unit |

|------------------------------------------|---------------------|-----|-----|------|

| GE_MDC frequency                         | f <sub>MDC</sub>    | _   | 2.5 | MHz  |

| GE_MDC period                            | t <sub>MDC</sub>    | 400 | —   | ns   |

| GE_MDC clock pulse width high            | t <sub>MDC_H</sub>  | 160 | _   | ns   |

| GE_MDC clock pulse width low             | t <sub>MDC_L</sub>  | 160 | _   | ns   |

| GE_MDC to GE_MDIO delay <sup>2</sup>     | t <sub>mdkhdx</sub> | 10  | 70  | ns   |

| GE_MDIO to GE_MDC rising edge setup time | t <sub>MDDVKH</sub> | 20  | _   | ns   |

| GE_MDC rising edge to GE_MDIO hold time  | t <sub>mddxkh</sub> | 0   | _   | ns   |

Program the GE\_MDC frequency (f<sub>MDC</sub>) to a maximum value of 2.5 MHz (400 ns period for t<sub>MDC</sub>). The value depends on the source clock and configuration of MIIMCFG[MCS] and UPSMR[MDCP]. For example, for a source clock of 400 MHz to achieve f<sub>MDC</sub> = 2.5 MHz, program MIIMCFG[MCS] = 0x4 and UPSMR[MDCP] = 0. See the *MSC8256 Reference Manual* for configuration details.

2. The value depends on the source clock. For example, for a source clock of 267 MHz, the delay is 70 ns. For a source clock of 333 MHz, the delay is 58 ns.

Figure 24. MII Management Interface Timing

# 3.1.2 Power-On Ramp Time

This section describes the AC electrical specification for the power-on ramp rate requirements for all voltage supplies (including GVDD/SXPVDD/SXCVDD/QVDD/GVDD/NVDD, all VDD supplies, MVREF, and all AVDD supplies). Controlling the power-on ramp time is required to avoid falsely triggering the ESD circuitry. Table 39 defines the power supply ramp time specification.

### Table 39. Power Supply Ramp Rate

|          |                      | Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Min           | Max        | Unit               |

|----------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------------|--------------------|

| Required | Required ramp rate.  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |               | 36000      | V/s                |

| Notes:   | 1.<br>2.<br>3.<br>4. | Ramp time is specified as a linear ramp from 10% to 90% of nominal voltage of the specific non-linear (for example, exponential), the maximum rate of change from 200 to 500 mV is th might falsely trigger the ESD circuitry.<br>Required over the full recommended operating temperature range (see Table 3).<br>All supplies must be at their stable values within 50 ms.<br>The GVDD pins can be held low on the application board at powerup. If GVDD is not held low voltage level that depends on the board-level impedance-to-ground. If the impedance is high | e most critic | al because | this range<br>to a |

# 3.1.3 Power Supply Guidelines

Use the following guidelines for power-up sequencing:

• Couple M3VDD with the VDD power rail using an extremely low impedance path.

theoretically, GVDD can rise up close to the VDD levels.

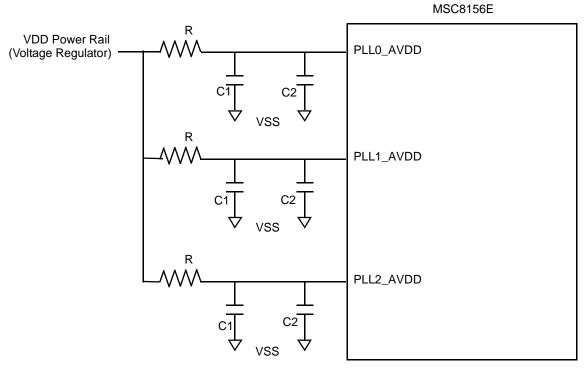

- Couple inputs PLL1\_AVDD, PLL2\_AVDD and PLL3\_AVDD with the VDD power rail using an RC filter (see Figure 37).

- There is no dependency in power-on/power-off sequence between the GVDD1, GVDD2, NVDD, and QVDD power rails.

- Couple inputs M1VREF and M2VREF with the GVDD1 and GVDD2 power rails, respectively. They should rise at the same time as or after their respective power rail.

- There is no dependency between RapidIO supplies: SXCVDD1, SXCVDD2, SXPVDD1 and SXPVDD2 and other MSC8256 supplies in the power-on/power-off sequence

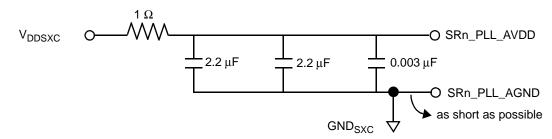

- Couple inputs SR1\_PLL\_AVDD and SR2\_PLL\_AVDD with SXCVDD1 and SXCVDD2 power rails, respectively, using an RC filter (see Figure 38).

External voltage applied to any input line must not exceed the I/O supply voltage related to this line by more than 0.6 V at any time, including during power-up. Some designs require pull-up voltages applied to selected input lines during power-up for configuration purposes. This is an acceptable exception to the rule during start-up. However, each such input can draw up to 80 mA per input pin per MSC8256 device in the system during power-up. An assertion of the inputs to the high voltage level before power-up should be with slew rate less than 4 V/ns.

The device power rails should rise in the following sequence:

1. VDD (and all coupled supplies)

# 3.2 PLL Power Supply Design Considerations

Each global PLL power supply must have an external RC filter for the PLLn\_AVDD input (see Figure 37) in which the following components are defined as listed:

- $R = 5 \Omega \pm 5\%$

- $C1 = 10 \ \mu\text{F} \pm 10\%$ , 0603, X5R, with ESL  $\leq 0.5 \ \text{nH}$ , low ESL Surface Mount Capacitor.

- $C2 = 1.0 \ \mu\text{F} \pm 10\%$ , 0402, X5R, with ESL  $\leq 0.5 \ \text{nH}$ , low ESL Surface Mount Capacitor.

Note: A higher capacitance value for C2 may be used to improve the filter as long as the other C2 parameters do not change.

All three PLLs can connect to a single supply voltage source (such as a voltage regulator) as long as the external RC filter is applied to each PLL separately. For optimal noise filtering, place the circuit as close as possible to its PLLn\_AVDD inputs.

#### Figure 37. PLL Supplies

Each SerDes PLL power supply must be filtered using a circuit similar to the one shown in Figure 38, to ensure stability of the internal clock. For maximum effectiveness, the filter circuit should be placed as closely as possible to the SRn\_PLL\_AVDD ball to ensure it filters out as much noise as possible. The ground connection should be near the SRn\_PLL\_AVDD ball. The 0.003  $\mu$ F capacitor is closest to the ball, followed by the two 2.2  $\mu$ F capacitors, and finally the 1  $\Omega$  resistor to the board supply plane. The capacitors are connected from SRn\_PLL\_AVDD to the ground plane. Use ceramic chip capacitors with the highest possible self-resonant frequency. All trances should be kept short, wide, and direct.

Figure 38. SerDes PLL Supplies

# 3.5 Connectivity Guidelines

**Note:** Although the package actually uses a ball grid array, the more conventional term pin is used to denote signal connections in this discussion.

First, select the pin multiplexing mode to allocate the required I/O signals. Then use the guidelines presented in the following subsections for board design and connections. The following conventions are used in describing the connectivity requirements:

- 1. GND indicates using a 10 k $\Omega$  pull-down resistor (recommended) or a direct connection to the ground plane. Direct connections to the ground plane may yield DC current up to 50 mA through the I/O supply that adds to overall power consumption.

- 2.  $V_{DD}$  indicates using a 10 k $\Omega$  pull-up resistor (recommended) or a direct connection to the appropriate power supply. Direct connections to the supply may yield DC current up to 50 mA through the I/O supply that adds to overall power consumption.

- 3. Mandatory use of a pull-up or pull-down resistor is clearly indicated as "pull-up/pull-down." For buses, each pin on the bus should have its own resistor.

- 4. NC indicates "not connected" and means do not connect anything to the pin.

- 5. The phrase "in use" indicates a typical pin connection for the required function.

- **Note:** Please see recommendations #1 and #2 as mandatory pull-down or pull-up connection for unused pins in case of subset interface connection.

# 3.5.1.2 DDR Interface Is Used With 32-Bit DDR Memory Only

Table 41 lists unused pin connection when using 32-bit DDR memory. The 32 most significant data lines are not used.

### Table 41. Connectivity of DDR Related Pins When Using 32-bit DDR Memory Only

| Signal Name | Pin Connection |

|-------------|----------------|

| MDQ[31-0]   | in use         |

| MDQ[63-32]  | NC             |

| MDQS[3-0]   | in use         |

| MDQS[7-4]   | NC             |

| MDQS[3-0]   | in use         |

| MDQS[7-4]   | NC             |

| MA[15-0]    | in use         |

| MCK[2-0]    | in use         |

| MCK[2-0]    | in use         |

| MCS[1-0]    | in use         |

| MDM[3-0]    | in use         |

| MDM[7-4]    | NC             |

| MBA[2-0]    | in use         |

| MCAS        | in use         |

| MCKE[1-0]   | in use         |

| MODT[1-0]   | in use         |

| MMDIC[1-0]  | in use         |

| MRAS        | in use         |

| MWE         | in use         |

| MVREF       | in use         |

| GVDD1/GVDD2 | in use         |

2. For MSC8256 Revision 1 silicon, these pins were connected to GND (or VDD). For newer revisions of the MSC8256, connecting these pins to GND increases device power consumption.

## 3.5.1.3 ECC Unused Pin Connections

When the error code correction mechanism is not used in any 32- or 64-bit DDR configuration, refer to Table 42 to determine the correct pin connections.

|                 | Signal Name | Pin connection |  |  |

|-----------------|-------------|----------------|--|--|

| MECC[7-0]       |             | NC             |  |  |

| MDM8            |             | NC             |  |  |

| MDQS8           |             | NC             |  |  |

| MDQS8           |             | NC             |  |  |

| Notes: 1.<br>2. |             |                |  |  |

|                    | Signal Name                                                                                                                                                                                                      | Pin Connection |  |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--|

| TDMnTCLK           |                                                                                                                                                                                                                  | GND            |  |

| TDMnT <b>x</b> DAT | Г                                                                                                                                                                                                                | GND            |  |

| TDM <b>n</b> TSYN  |                                                                                                                                                                                                                  | GND            |  |

| V <sub>DDIO</sub>  |                                                                                                                                                                                                                  | 2.5 V          |  |

|                    | <ol> <li>x = {0, 1, 2,3}</li> <li>In case of subset of TDM interface usage please make sure to disable unused TDM modules. See <i>TDM</i> chapter in the <i>MSC8256 Reference Manual</i> for details.</li> </ol> |                |  |

# 3.5.5 Miscellaneous Pins