## NXP USA Inc. - <u>MSC8256TVT800B Datasheet</u>

Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

#### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Details

| Product Status          | Obsolete                                                                       |

|-------------------------|--------------------------------------------------------------------------------|

| Туре                    | SC3850 Six Core                                                                |

| Interface               | Ethernet, I <sup>2</sup> C, PCI, RGMII, Serial RapidIO, SGMII, SPI, UART/USART |

| Clock Rate              | 800MHz                                                                         |

| Non-Volatile Memory     | ROM (96kB)                                                                     |

| On-Chip RAM             | 576kB                                                                          |

| Voltage - I/O           | 2.50V                                                                          |

| Voltage - Core          | 1.00V                                                                          |

| Operating Temperature   | -40°C ~ 105°C (TJ)                                                             |

| Mounting Type           | Surface Mount                                                                  |

| Package / Case          | 783-BBGA, FCBGA                                                                |

| Supplier Device Package | 783-FCPBGA (29x29)                                                             |

| Purchase URL            | https://www.e-xfl.com/product-detail/nxp-semiconductors/msc8256tvt800b         |

|                         |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Ball Number | Signal Name <sup>1,2</sup>   | Pin Type <sup>10</sup> | Power Rail<br>Name |

|-------------|------------------------------|------------------------|--------------------|

| E17         | M2DQ56                       | I/O                    | GVDD2              |

| E18         | M2DQ57                       | I/O                    | GVDD2              |

| E19         | M2DQS7                       | I/O                    | GVDD2              |

| E20         | Reserved                     | NC                     | —                  |

| E21         | Reserved                     | NC                     | —                  |

| E22         | Reserved                     | NC                     | —                  |

| E23         | SXPVDD1                      | Power                  | N/A                |

| E24         | SXPVSS1                      | Ground                 | N/A                |

| E25         | SR1_PLL_AGND <sup>9</sup>    | Ground                 | SXCVSS1            |

| E26         | SR1_PLL_AVDD <sup>9</sup>    | Power                  | SXCVDD1            |

| E27         | SXCVSS1                      | Ground                 | N/A                |

| E28         | SXCVDD1                      | Power                  | N/A                |

| F1          | VSS                          | Ground                 | N/A                |

| F2          | GVDD2                        | Power                  | N/A                |

| F3          | M2DQ16                       | I/O                    | GVDD2              |

| F4          | VSS                          | Ground                 | N/A                |

| F5          | GVDD2                        | Power                  | N/A                |

| F6          | M2DQ17                       | I/O                    | GVDD2              |

| F7          | VSS                          | Ground                 | N/A                |

| F8          | GVDD2                        | Power                  | N/A                |

| F9          | M2BA2                        | 0                      | GVDD2              |

| F10         | VSS                          | Ground                 | N/A                |

| F11         | GVDD2                        | Power                  | N/A                |

| F12         | M2A4                         | 0                      | GVDD2              |

| F13         | VSS                          | Ground                 | N/A                |

| F14         | GVDD2                        | Power                  | N/A                |

| F15         | M2DQ42                       | I/O                    | GVDD2              |

| F16         | VSS                          | Ground                 | N/A                |

| F17         | GVDD2                        | Power                  | N/A                |

| F18         | M2DQ58                       | I/O                    | GVDD2              |

| F19         | M2DQS7                       | I/O                    | GVDD2              |

| F20         | GVDD2                        | Power                  | N/A                |

| F21         | SXPVDD1                      | Power                  | N/A                |

| F22         | SXPVSS1                      | Ground                 | N/A                |

| F23         | SR1_TXD2/SG1_TX <sup>4</sup> | 0                      | SXPVDD1            |

| F24         | SR1_TXD2/SG1_TX <sup>4</sup> | 0                      | SXPVDD1            |

| F25         | SXCVDD1                      | Power                  | N/A                |

| F26         | SXCVSS1                      | Ground                 | N/A                |

| F27         | SR1_RXD2/SG1_RX <sup>4</sup> | I                      | SXCVDD1            |

| F28         | SR1_RXD2/SG1_RX <sup>4</sup> | I                      | SXCVDD1            |

| G1          | M2DQS2                       | I/O                    | GVDD2              |

| G2          | M2DQS2                       | I/O                    | GVDD2              |

| G3          | M2DQ19                       | I/O                    | GVDD2              |

| G4          | M2DM2                        | 0                      | GVDD2              |

| G5          | M2DQ21                       | I/O                    | GVDD2              |

| G6          | M2DQ22                       | I/O                    | GVDD2              |

| Ball Number | Signal Name <sup>1,2</sup>           | Pin Type <sup>10</sup> | Power Rail<br>Name |

|-------------|--------------------------------------|------------------------|--------------------|

| N23         | SR2_TXD2/PE_TXD2/SG1_TX <sup>4</sup> | 0                      | SXPVDD2            |

| N24         | SR2_TXD2/PE_TXD2/SG1_TX <sup>4</sup> | 0                      | SXPVDD2            |

| N25         | SXCVDD2                              | Power                  | N/A                |

| N26         | SXCVSS2                              | Ground                 | N/A                |

| N27         | SR2_RXD2/PE_RXD2/SG1_RX <sup>4</sup> | I                      | SXCVDD2            |

| N28         | SR2_RXD2/PE_RXD2/SG1_RX <sup>4</sup> | I                      | SXCVDD2            |

| P1          | CLKIN                                | I                      | QVDD               |

| P2          | EE0                                  | I                      | QVDD               |

| P3          | QVDD                                 | Power                  | N/A                |

| P4          | VSS                                  | Ground                 | N/A                |

| P5          | STOP_BS                              | 1                      | QVDD               |

| P6          | QVDD                                 | Power                  | N/A                |

| P7          | VSS                                  | Ground                 | N/A                |

| P8          | PLL0_AVDD <sup>9</sup>               | Power                  | VDD                |

| P9          | PLL2_AVDD <sup>9</sup>               | Power                  | VDD                |

| P10         | VSS                                  | Ground                 | N/A                |

| P11         | VDD                                  | Power                  | N/A                |

| P12         | VSS                                  | Ground                 | N/A                |

| P13         | VDD                                  | Power                  | N/A                |

| P14         | VSS                                  | Ground                 | N/A                |

| P15         | VSS                                  | Ground                 | N/A                |

| P16         | VSS                                  | Ground                 | N/A                |

| P17         | VSS                                  | Ground                 | N/A                |

| P18         | VSS                                  | Ground                 | N/A                |

| P19         | VDD                                  | Power                  | N/A                |

| P20         | Reserved                             | NC                     |                    |

| P21         | Reserved                             | NC                     |                    |

| P22         | Reserved                             | NC                     |                    |

| P23         | SXPVDD2                              | Power                  | N/A                |

| P24         | SXPVSS2                              | Ground                 | N/A                |

| P25         | SR2_PLL_AGND <sup>9</sup>            | Ground                 | SXCVSS2            |

| P26         | SR2_PLL_AVDD <sup>9</sup>            | Power                  | SXCVDD2            |

| P27         | SXCVSS2                              | Ground                 | N/A                |

| P28         | SXCVDD2                              | Power                  | N/A                |

| R1          | VSS                                  | Ground                 | N/A                |

| R2          | NMI                                  |                        | QVDD               |

| R3          | NMI_OUT <sup>6</sup>                 | 0                      | QVDD               |

| R4          | HRESET <sup>6,7</sup>                |                        | QVDD               |

| R5          | INT_OUT <sup>6</sup>                 | 0                      | QVDD               |

| R6          | EE1                                  | 0                      | QVDD               |

| R7          | VSS                                  | Ground                 | N/A                |

| R8          | PLL1_AVDD <sup>9</sup>               | Power                  | VDD                |

| R9          | VSS                                  | Ground                 | N/A                |

| R10         | VDD                                  | Power                  | N/A                |

| R10         | VSS                                  | Non-user               | N/A                |

| R12         | VDD                                  | Power                  | N/A<br>N/A         |

| Ball Number | Signal Name <sup>1,2</sup>         | Pin Type <sup>10</sup> | Power Rail<br>Name |

|-------------|------------------------------------|------------------------|--------------------|

| V21         | RCW_LSEL_3/RC20                    | I/O                    | NVDD               |

| V22         | RCW_LSEL_2/RC19                    | I/O                    | NVDD               |

| V23         | SXPVDD2                            | Power                  | N/A                |

| V24         | SXPVSS2                            | Ground                 | N/A                |

| V25         | RCW_LSEL_1/RC18                    | I/O                    | NVDD               |

| V26         | RC21                               | I                      | NVDD               |

| V27         | SXCVDD2                            | Power                  | N/A                |

| V28         | SXCVSS2                            | Ground                 | N/A                |

| W1          | VSS                                | Ground                 | N/A                |

| W2          | GVDD1                              | Power                  | N/A                |

| W3          | M1DM1                              | 0                      | GVDD1              |

| W4          | VSS                                | Ground                 | N/A                |

| W5          | GVDD1                              | Power                  | N/A                |

| W6          | M1DQ0                              | I/O                    | GVDD1              |

| W7          | VSS                                | Ground                 | N/A                |

| W8          | GVDD1                              | Power                  | N/A                |

| W9          | M1DQ5                              | I/O                    | GVDD1              |

| W10         | VDD                                | Power                  | N/A                |

| W11         | VSS                                | Ground                 | N/A                |

| W12         | VDD                                | Power                  | N/A                |

| W13         | VSS                                | Ground                 | N/A                |

| W14         | VDD                                | Power                  | N/A                |

| W15         | VSS                                | Ground                 | N/A                |

| W16         | VDD                                | Power                  | N/A                |

| W17         | VSS                                | Ground                 | N/A                |

| W18         | VDD                                | Power                  | N/A                |

| W19         | VSS                                | Ground                 | N/A                |

| W20         | VSS                                | Ground                 | N/A                |

| W21         | RCW_LSEL0/RC17                     | I/O                    | NVDD               |

| W22         | GPIO19/SPI_MISO <sup>5,8</sup>     | I/O                    | NVDD               |

| W23         | VSS                                | Ground                 | N/A                |

| W24         | NVDD                               | Power                  | N/A                |

| W25         | GPIO11/IRQ11/RC11 <sup>5,8</sup>   | I/O                    | NVDD               |

| W26         | GPIO3/DRQ1/IRQ3/RC3 <sup>5,8</sup> | I/O                    | NVDD               |

| W27         | GPIO7/IRQ7/RC7 <sup>5,8</sup>      | I/O                    | NVDD               |

| W28         | GPIO2/IRQ2/RC2 <sup>5,8</sup>      | I/O                    | NVDD               |

| Y1          | M1DQS1                             | I/O                    | GVDD1              |

| Y2          | M1DQS1                             | I/O                    | GVDD1              |

| Y3          | M1DQ10                             | I/O                    | GVDD1              |

| Y4          | M1DQ11                             | I/O                    | GVDD1              |

| Y5          | M1DQ14                             | I/O                    | GVDD1              |

| Y6          | M1DQ23                             | I/O                    | GVDD1              |

| Y7          | M1ODT0                             | 0                      | GVDD1              |

| Y8          | M1A12                              | 0                      | GVDD1              |

| Y9          | M1A14                              | 0                      | GVDD1              |

| Y10         | VSS                                | Ground                 | N/A                |

| Ball Number | Signal Name <sup>1,2</sup>          | Pin Type <sup>10</sup> | Power Rail<br>Name |  |

|-------------|-------------------------------------|------------------------|--------------------|--|

| AB1         | M1DQS2                              | I/O                    | GVDD1              |  |

| AB2         | M1DQS2                              | I/O                    | GVDD1              |  |

| AB3         | M1DQ19                              | I/O                    | GVDD1              |  |

| AB4         | M1DM2                               | 0                      | GVDD1              |  |

| AB5         | M1DQ21                              | I/O                    | GVDD1              |  |

| AB6         | M1DQ22                              | I/O                    | GVDD1              |  |

| AB7         | M1CKE0                              | 0                      | GVDD1              |  |

| AB8         | M1A11                               | 0                      | GVDD1              |  |

| AB9         | M1A7                                | 0                      | GVDD1              |  |

| AB10        | M1CK2                               | 0                      | GVDD1              |  |

| AB11        | M1APAR_OUT                          | 0                      | GVDD1              |  |

| AB12        | M1ODT1                              | 0                      | GVDD1              |  |

| AB13        | M1APAR_IN                           | 1                      | GVDD1              |  |

| AB14        | M1DQ43                              | I/O                    | GVDD1              |  |

| AB15        | M1DM5                               | 0                      | GVDD1              |  |

| AB16        | M1DQ44                              | I/O                    | GVDD1              |  |

| AB17        | M1DQ40                              | I/O                    | GVDD1              |  |

| AB18        | M1DQ59                              | I/O                    | GVDD1              |  |

| AB19        | M1DM7                               | 0                      | GVDD1              |  |

| AB20        | M1DQ60                              | I/O                    | GVDD1              |  |

| AB21        | VSS                                 | Ground                 | N/A                |  |

| AB22        | GPIO31/I2C_SDA <sup>5,8</sup>       | I/O                    | NVDD               |  |

| AB23        | GPIO27/TMR4/RCW_SRC0 <sup>5,8</sup> | I/O                    | NVDD               |  |

| AB24        | GPIO25/TMR2/RCW_SRC1 <sup>5,8</sup> | I/O                    | NVDD               |  |

| AB25        | GPIO24/TMR1/RCW_SRC2 <sup>5,8</sup> | I/O                    | NVDD               |  |

| AB26        | GPIO10/IRQ10/RC10 <sup>5,8</sup>    | I/O                    | NVDD               |  |

| AB27        | GPIO5/IRQ5/RC5 <sup>5,8</sup>       | I/O                    | NVDD               |  |

| AB28        | GPIO0/IRQ0/RC0 <sup>5,8</sup>       | I/O                    | NVDD               |  |

| AC1         | VSS                                 | Ground                 | N/A                |  |

| AC2         | GVDD1                               | Power                  | N/A                |  |

| AC3         | M1DQ16                              | I/O                    | GVDD1              |  |

| AC4         | VSS                                 | Ground                 | N/A                |  |

| AC5         | GVDD1                               | Power                  | N/A                |  |

| AC6         | M1DQ17                              | I/O                    | GVDD1              |  |

| AC7         | VSS                                 | Ground                 | N/A                |  |

| AC8         | GVDD1                               | Power                  | N/A                |  |

| AC9         | M1BA2                               | 0                      | GVDD1              |  |

| AC10        | VSS                                 | Ground                 | N/A                |  |

| AC11        | GVDD1                               | Power                  | N/A                |  |

| AC12        | M1A4                                | 0                      | GVDD1              |  |

| AC13        | VSS                                 | Ground                 | N/A                |  |

| AC14        | GVDD1                               | Power                  | N/A                |  |

| AC15        | M1DQ42                              | I/O                    | GVDD1              |  |

| AC16        | VSS                                 | Ground                 | N/A                |  |

| AC17        | GVDD1                               | Power                  | N/A                |  |

| AC18        | M1DQ58                              | I/O                    | GVDD1              |  |

| Ball Number | Signal Name <sup>1,2</sup>       | Pin Type <sup>10</sup> | Power Rail<br>Name |

|-------------|----------------------------------|------------------------|--------------------|

| AE9         | M1A8                             | 0                      | GVDD1              |

| AE10        | GVDD1                            | Power                  | N/A                |

| AE11        | VSS                              | Ground                 | N/A                |

| AE12        | M1A0                             | 0                      | GVDD1              |

| AE13        | GVDD1                            | Power                  | N/A                |

| AE14        | VSS                              | Ground                 | N/A                |

| AE15        | M1DQ39                           | I/O                    | GVDD1              |

| AE16        | GVDD1                            | Power                  | N/A                |

| AE17        | VSS                              | Ground                 | N/A                |

| AE18        | M1DQ54                           | I/O                    | GVDD1              |

| AE19        | GVDD1                            | Power                  | N/A                |

| AE20        | VSS                              | Ground                 | N/A                |

| AE21        | GPIO29/UART_TXD <sup>5,8</sup>   | I/O                    | NVDD               |

| AE22        | TDM1TCK/GE2_RX_CLK <sup>3</sup>  | I                      | NVDD               |

| AE23        | TDM1RSN/GE2_RX_CTL <sup>3</sup>  | I/O                    | NVDD               |

| AE24        | VSS                              | Ground                 | N/A                |

| AE25        | TDM3RCK/GE1_GTX_CLK <sup>3</sup> | I/O                    | NVDD               |

| AE26        | TDM3TSN/GE1_RX_CLK <sup>3</sup>  | I/O                    | NVDD               |

| AE27        | TDM2RSN/GE1_TD2 <sup>3</sup>     | I/O                    | NVDD               |

| AE28        | TDM2RDT/GE1_TD1 <sup>3</sup>     | I/O                    | NVDD               |

| AF1         | M1DQ28                           | I/O                    | GVDD1              |

| AF2         | M1DM3                            | 0                      | GVDD1              |

| AF3         | M1DQ26                           | I/O                    | GVDD1              |

| AF4         | M1ECC4                           | I/O                    | GVDD1              |

| AF5         | M1DM8                            | 0                      | GVDD1              |

| AF6         | M1ECC2                           | I/O                    | GVDD1              |

| AF7         | M1CKE1                           | 0                      | GVDD1              |

| AF8         | М1СКО                            | 0                      | GVDD1              |

| AF9         | М1СКО                            | 0                      | GVDD1              |

| AF10        | M1BA1                            | 0                      | GVDD1              |

| AF11        | M1A1                             | 0                      | GVDD1              |

| AF12        | M1WE                             | 0                      | GVDD1              |

| AF13        | M1DQ37                           | I/O                    | GVDD1              |

| AF14        | M1DM4                            | 0                      | GVDD1              |

| AF15        | M1DQ36                           | I/O                    | GVDD1              |

| AF16        | M1DQ32                           | I/O                    | GVDD1              |

| AF17        | M1DQ55                           | I/O                    | GVDD1              |

| AF18        | M1DM6                            | 0                      | GVDD1              |

| AF19        | M1DQ53                           | I/O                    | GVDD1              |

| AF20        | M1DQ52                           | I/O                    | GVDD1              |

| AF21        | GPIO28/UART_RXD <sup>5,8</sup>   | I/O                    | NVDD               |

| AF22        | TDM0RSN/GE2_TD2 <sup>3</sup>     | I/O                    | NVDD               |

| AF23        | TDM0TDT/GE2_TD3 <sup>3</sup>     | I/O                    | NVDD               |

| AF24        | <br>NVDD                         | Power                  | N/A                |

| AF25        | TDM2TSN/GE1_TX_CTL <sup>3</sup>  | I/O                    | NVDD               |

| AF26        | GE1_RX_CTL                       | 1                      | NVDD               |

| Ball Number | Signal Name <sup>1,2</sup>       | Pin Type <sup>10</sup> | Power Rail<br>Name |  |

|-------------|----------------------------------|------------------------|--------------------|--|

| AF27        | TDM2TDT/GE1_TX_CLK <sup>3</sup>  | I/O                    | NVDD               |  |

| AF28        | TDM3RSN/GE1_RD1 <sup>3</sup>     | I/O                    | NVDD               |  |

| AG1         | M1DQ24                           | I/O                    | GVDD1              |  |

| AG2         | GVDD1                            | Power                  | N/A                |  |

| AG3         | M1DQ25                           | I/O                    | GVDD1              |  |

| AG4         | VSS                              | Ground                 | N/A                |  |

| AG5         | GVDD1                            | Power                  | N/A                |  |

| AG6         | M1ECC1                           | I/O                    | GVDD1              |  |

| AG7         | VSS                              | Ground                 | N/A                |  |

| AG8         | GVDD1                            | Power                  | N/A                |  |

| AG9         | M1A13                            | 0                      | GVDD1              |  |

| AG10        | VSS                              | Ground                 | N/A                |  |

| AG11        | GVDD1                            | Power                  | N/A                |  |

| AG12        | M1CS1                            | 0                      | GVDD1              |  |

| AG13        | VSS                              | Ground                 | N/A                |  |

| AG14        | GVDD1                            | Power                  | N/A                |  |

| AG15        | M1DQ35                           | I/O                    | GVDD1              |  |

| AG16        | VSS                              | Ground                 | N/A                |  |

| AG17        | GVDD1                            | Power                  | N/A                |  |

| AG18        | M1DQ51                           | I/O                    | GVDD1              |  |

| AG19        | VSS                              | Ground                 | N/A                |  |

| AG20        | GVDD1                            | Power                  | N/A                |  |

| AG21        | NVDD                             | Power                  | N/A                |  |

| AG22        | TDM1TSN/GE2_TD1 <sup>3</sup>     | I/O                    | NVDD               |  |

| AG23        | TDM1RDT/GE2_TX_CLK <sup>3</sup>  | I/O                    | NVDD               |  |

| AG24        | TDM0TCK/GE2_GTX_CLK <sup>3</sup> | I/O                    | NVDD               |  |

| AG25        | TDM1TDT/GE2_TD0 <sup>3</sup>     | I/O                    | NVDD               |  |

| AG26        | VSS                              | Ground                 | N/A                |  |

| AG27        | NVDD                             | Power                  | N/A                |  |

| AG28        | TDM3RDT/GE1_RD0 <sup>3</sup>     | I/O                    | NVDD               |  |

| AH1         | Reserved.                        | NC                     | _                  |  |

| AH2         | M1DQS3                           | I/O                    | GVDD1              |  |

| AH3         | M1DQS3                           | I/O                    | GVDD1              |  |

| AH4         | M1ECC0                           | I/O                    | GVDD1              |  |

| AH5         | M1DQS8                           | I/O                    | GVDD1              |  |

| AH6         | M1DQS8                           | I/O                    | GVDD1              |  |

| AH7         | M1A5                             | 0                      | GVDD1              |  |

| AH8         | M1CK1                            | 0                      | GVDD1              |  |

| AH9         | M1CK1                            | 0                      | GVDD1              |  |

| AH10        | M1CS0                            | 0                      | GVDD1              |  |

| AH11        | M1BA0                            | 0                      | GVDD1              |  |

| AH12        | M1CAS                            | 0                      | GVDD1              |  |

| AH13        | M1DQ34                           | I/O                    | GVDD1              |  |

| AH14        | M1DQS4                           | I/O                    | GVDD1              |  |

| AH15        | M1DQS4                           | I/O                    | GVDD1              |  |

| AH16        | M1DQ50                           | I/O                    | GVDD1              |  |

#### **Electrical Characteristics** 2

This document contains detailed information on power considerations, DC/AC electrical characteristics, and AC timing specifications. For additional information, see the MSC8256 Reference Manual.

#### **Maximum Ratings** 2.1

In calculating timing requirements, adding a maximum value of one specification to a minimum value of another specification does not yield a reasonable sum. A maximum specification is calculated using a worst case variation of process parameter values in one direction. The minimum specification is calculated using the worst case for the same parameters in the opposite direction. Therefore, a "maximum" value for a specification never occurs in the same device with a "minimum" value for another specification; adding a maximum to a minimum represents a condition that can never exist.

Table 2 describes the maximum electrical ratings for the MSC8256.

| Rating                                                  | Power Rail Name     | Symbol                                                            | Value                                     | Unit        |

|---------------------------------------------------------|---------------------|-------------------------------------------------------------------|-------------------------------------------|-------------|

| Core supply voltage<br>• Cores 0–5                      | VDD                 | V <sub>DD</sub>                                                   | -0.3 to 1.1                               | V           |

| PLL supply voltage <sup>3</sup>                         |                     | V <sub>DDPLL0</sub><br>V <sub>DDPLL1</sub><br>V <sub>DDPLL2</sub> | -0.3 to 1.1<br>-0.3 to 1.1<br>-0.3 to 1.1 | V<br>V<br>V |

| M3 memory supply voltage                                | M3VDD               | V <sub>DDM3</sub>                                                 | -0.3 to 1.1                               | V           |

| DDR memory supply voltage<br>• DDR2 mode<br>• DDR3 mode | GVDD1, GVDD2        | V <sub>DDDDR</sub>                                                | -0.3 to 1.98<br>-0.3 to 1.65              | V<br>V      |

| DDR reference voltage                                   | MVREF               | MV <sub>REF</sub>                                                 | –0.3 to 0.51 $\times$ V_{DDDDR}           | V           |

| Input DDR voltage                                       |                     | VINDDR                                                            | –0.3 to V <sub>DDDDR</sub> + 0.3          | V           |

| I/O voltage excluding DDR and RapidIO lines             | NVDD, QVDD          | V <sub>DDIO</sub>                                                 | -0.3 to 2.625                             | V           |

| Input I/O voltage                                       |                     | V <sub>INIO</sub>                                                 | –0.3 to V <sub>DDIO</sub> + 0.3           | V           |

| RapidIO pad voltage                                     | SXPVDD1,<br>SXPVDD2 | V <sub>DDSXP</sub>                                                | -0.3 to 1.26                              | V           |

| Rapid I/O core voltage                                  | SXCVDD1,<br>SXCVDD2 | V <sub>DDSXC</sub>                                                | -0.3 to 1.21                              | V           |

| Rapid I/O PLL voltage <sup>3</sup>                      |                     | V <sub>DDRIOPLL</sub>                                             | -0.3 to 1.21                              | V           |

| Input RapidIO I/O voltage                               |                     | V <sub>INRIO</sub>                                                | -0.3 to V <sub>DDSXC</sub> + 0.3          | V           |

| Operating temperature                                   |                     | TJ                                                                | -40 to 105                                | °C          |

| Storage temperature range                               |                     | T <sub>STG</sub>                                                  | -55 to +150                               | °C          |

#### Table 2. Absolute Maximum Ratings

2. Absolute maximum ratings are stress ratings only, and functional operation at the maximum is not guaranteed. Stress beyond the listed limits may affect device reliability or cause permanent damage.

3. PLL supply voltage is specified at input of the filter and not at pin of the MSC8256 (see Figure 37 and Figure 38)

## 2.5.1.1 DDR2 (1.8 V) SDRAM DC Electrical Characteristics

Table 6 provides the recommended operating conditions for the DDR SDRAM controller when interfacing to DDR2 SDRAM.

Note: At recommended operating conditions (see Table 3) with  $V_{DDDDR} = 1.8$  V.

| Parameter/Condition                             | Symbol            | Min                       | Max                       | Unit | Notes   |

|-------------------------------------------------|-------------------|---------------------------|---------------------------|------|---------|

| I/O reference voltage                           | MV <sub>REF</sub> | $0.49 \times V_{DDDDR}$   | $0.51 \times V_{DDDDR}$   | V    | 2, 3, 4 |

| Input high voltage                              | V <sub>IH</sub>   | MV <sub>REF</sub> + 0.125 | V <sub>DDDDR</sub> + 0.3  | V    | 5       |

| Input low voltage                               | V <sub>IL</sub>   | -0.3                      | MV <sub>REF</sub> - 0.125 | V    | 5       |

| I/O leakage current                             | I <sub>OZ</sub>   | -50                       | 50                        | μΑ   | 6       |

| Output high current ( $V_{OUT}$ (VOH) = 1.37 V) | I <sub>ОН</sub>   | -13.4                     | —                         | mA   | 7       |

| Output low current ( $V_{OUT}$ (VOL) = 0.33 V)  | I <sub>OL</sub>   | 13.4                      | —                         | mA   | 7       |

### Table 6. DDR2 SDRAM Interface DC Electrical Characteristics

Notes: 1. V<sub>DDDDR</sub> is expected to be within 50 mV of the DRAM V<sub>DD</sub> supply voltage at all times. The DRAM and memory controller can use the same or different sources.

2.  $MV_{REF}$  is expected to be equal to  $0.5 \times V_{DDDDR}$ , and to track  $V_{DDDDR}$  DC variations as measured at the receiver. Peak-to-peak noise on  $MV_{REF}$  may not exceed ±2% of the DC value.

V<sub>TT</sub> is not applied directly to the device. It is the supply to which far end signal termination is made and is expected to be equal to MV<sub>REF</sub> with a minimum value of MV<sub>REF</sub> – 0.4 and a maximum value of MV<sub>REF</sub> + 0.04 V. V<sub>TT</sub> should track variations in the DC-level of MV<sub>REF</sub>.

- 4. The voltage regulator for  $MV_{REF}$  must be able to supply up to 300  $\mu$ A.

- 5. Input capacitance load for DQ, DQS, and DQS signals are available in the IBIS models.

- 6. Output leakage is measured with all outputs are disabled,  $0 V \le V_{OUT} \le V_{DDDDR}$ .

- 7. Refer to the IBIS model for the complete output IV curve characteristics.

## 2.5.1.2 DDR3 (1.5V) SDRAM DC Electrical Characteristics

Table 7 provides the recommended operating conditions for the DDR SDRAM controller when interfacing to DDR3 SDRAM.

Note: At recommended operating conditions (see Table 3) with  $V_{DDDDR} = 1.5$  V.

#### Table 7. DDR3 SDRAM Interface DC Electrical Characteristics

| Parameter/Condition   | Symbol            | Min                       | Мах                       | Unit | Notes |

|-----------------------|-------------------|---------------------------|---------------------------|------|-------|

| I/O reference voltage | MV <sub>REF</sub> | $0.49 \times V_{DDDDR}$   | $0.51 \times V_{DDDDR}$   | V    | 2,3,4 |

| Input high voltage    | V <sub>IH</sub>   | MV <sub>REF</sub> + 0.100 | V <sub>DDDDR</sub>        | V    | 5     |

| Input low voltage     | V <sub>IL</sub>   | GND                       | MV <sub>REF</sub> – 0.100 | V    | 5     |

| I/O leakage current   | I <sub>OZ</sub>   | -50                       | 50                        | μΑ   | 6     |

Notes: 1. V<sub>DDDDR</sub> is expected to be within 50 mV of the DRAM V<sub>DD</sub> at all times. The DRAM and memory controller can use the same or different sources.

2.  $MV_{REF}$  is expected to be equal to  $0.5 \times V_{DDDDR}$  and to track  $V_{DDDDR}$  DC variations as measured at the receiver. Peak-to-peak noise on  $MV_{REF}$  may not exceed ±1% of the DC value.

3. V<sub>TT</sub> is not applied directly to the device. It is the supply to which far end signal termination is made and is expected to be equal to MV<sub>REF</sub> with a minimum value of MV<sub>REF</sub> – 0.4 and a maximum value of MV<sub>REF</sub> + 0.04 V. V<sub>TT</sub> should track variations in the DC-level of MV<sub>REF</sub>.

- 4. The voltage regulator for  $MV_{REF}$  must be <u>able</u> to supply up to 250  $\mu$ A.

- 5. Input capacitance load for DQ, DQS, and DQS signals are available in the IBIS models.

- **6.** Output leakage is measured with all outputs are disabled,  $0 V \le V_{OUT} \le V_{DDDDR}$ .

## 2.5.1.3 DDR2/DDR3 SDRAM Capacitance

Table 8 provides the DDR controller interface capacitance for DDR2 and DDR3 memory.

**Note:** At recommended operating conditions (see Table 3) with V<sub>DDDDR</sub> = 1.8 V for DDR2 memory or V<sub>DDDDR</sub> = 1.5 V for DDR3 memory.

| Parameter                                               | Symbol           | Min | Мах | Unit |  |

|---------------------------------------------------------|------------------|-----|-----|------|--|

| I/O capacitance: DQ, DQS, DQS                           | C <sub>IO</sub>  | 6   | 8   | pF   |  |

| Delta I/O capacitance: DQ, DQS, DQS                     | C <sub>DIO</sub> | —   | 0.5 | pF   |  |

| Note: Guaranteed by FAB process and micro-construction. |                  |     |     |      |  |

#### Table 8. DDR2/DDR3 SDRAM Capacitance

## 2.5.1.4 DDR Reference Current Draw

Table 9 lists the current draw characteristics for MV<sub>REF</sub>.

Note: Values when used at recommended operating conditions (see Table 3).

#### Table 9. Current Draw Characteristics for MV<sub>REF</sub>

| Parameter / Condition                                               | Symbol              | Min | Max        | Unit     |

|---------------------------------------------------------------------|---------------------|-----|------------|----------|

| Current draw for MV <sub>REFn</sub><br>• DDR2 SDRAM<br>• DDR3 SDRAM | I <sub>MVREFn</sub> |     | 300<br>250 | μΑ<br>μΑ |

## 2.5.2 High-Speed Serial Interface (HSSI) DC Electrical Characteristics

The MSC8256 features an HSSI that includes two 4-channel SerDes ports used for high-speed serial interface applications (PCI Express, Serial RapidIO interfaces, and SGMII). This section and its subsections describe the common portion of the SerDes DC, including the DC requirements for the SerDes reference clocks and the SerDes data lane transmitter (Tx) and receiver (Rx) reference circuits. The data lane circuit specifications are specific for each supported interface, and they have individual subsections by protocol. The selection of individual data channel functionality is done via the Reset Configuration Word High Register (RCWHR) SerDes Protocol selection fields (S1P and S2P). Specific AC electrical characteristics are defined in Section 2.6.2, "HSSI AC Timing Specifications."

## 2.5.2.1 Signal Term Definitions

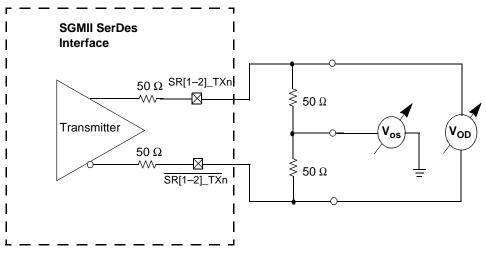

The SerDes interface uses differential signalling to transfer data across the serial link. This section defines terms used in the description and specification of differential signals. Figure 4 shows how the signals are defined. For illustration purposes only, one SerDes lane is used in the description. Figure 4 shows the waveform for either a transmitter output (SR[1–2]\_TX and

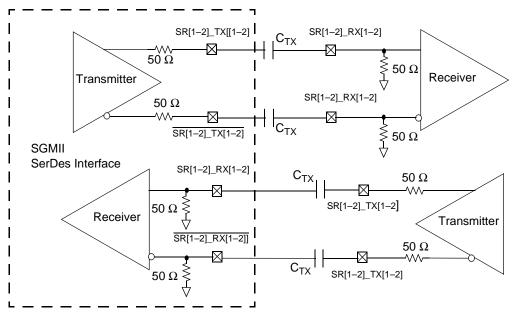

### Figure 10. SGMII Transmitter DC Measurement Circuit

Table 16 describes the SGMII SerDes receiver AC-coupled DC electrical characteristics.

|                                       | Parameter                                                                          | Symbol                  | Min | Тур | Max  | Unit | Notes |

|---------------------------------------|------------------------------------------------------------------------------------|-------------------------|-----|-----|------|------|-------|

| DC Input voltage range                |                                                                                    |                         | N/A |     |      |      | 1     |

| Input<br>differential                 | SRDSnCR4[EICE{12:10}] = 0b001 for SGMII1<br>SRDSnCR4[EICF{4:2}] = 0b001 for SGMII2 | V <sub>RX_DIFFp-p</sub> | 100 | _   | 1200 | mV   | 2, 4  |

| voltage                               | SRDSnCR4[EICE{12:10}] = 0b100 for SGMII1<br>SRDSnCR4[EICF{4:2}] = 0b100 for SGMII2 |                         | 175 |     |      |      |       |

| Loss of signal                        | SRDSnCR4[EICE{12:10}] = 0b001 for SGMII1<br>SRDSnCR4[EICF{4:2}] = 0b001 for SGMII2 | VLOS                    | 30  |     | 100  | mV   | 3, 4  |

| threshold                             | SRDSnCR4[EICE{12:10}] = 0b100 for SGMII1<br>SRDSnCR4[EICF{4:2}] = 0b100 for SGMII2 |                         | 65  | _   | 175  |      |       |

| Receiver differential input impedance |                                                                                    | Z <sub>RX_DIFF</sub>    | 80  | _   | 120  | W    | _     |

oupled

$V_{\mathsf{RX\_DIFFp}\text{-}p}$  is also referred to as peak-to-peak input differential voltage. 2.

The concept of this parameter is equivalent to the Electrical Idle Detect Threshold parameter in the PCI Express interface. 3. Refer to the PCI Express Differential Receiver (RX) Input Specifications section of the PCI Express Specification document. for details.

The values for SGMII1 and SGMII2 are selected in the SRDS control registers. 4.

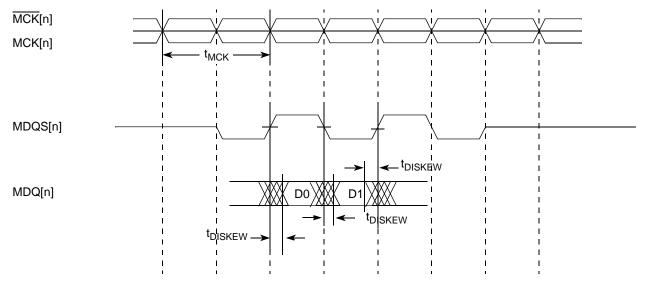

5. The supply voltage is 1.0 V. Figure 11 shows the DDR2 and DDR3 SDRAM interface input timing diagram.

Figure 11. DDR2 and DDR3 SDRAM Interface Input Timing Diagram

## 2.6.1.2 DDR SDRAM Output AC Timing Specifications

Table 21 provides the output AC timing specifications for the DDR SDRAM interface.

| Parameter                                                                                   | Symbol <sup>1</sup>                         | Min                          | Max                          | Unit     | Notes |

|---------------------------------------------------------------------------------------------|---------------------------------------------|------------------------------|------------------------------|----------|-------|

| MCK[n] cycle time                                                                           | t <sub>MCK</sub>                            | 2.5                          | 5                            | ns       | 2     |

| ADDR/CMD output setup with respect to MCK<br>• 800 MHz data rate<br>• 667 MHz data rate     | <sup>t</sup> DDKHAS                         | 0.917<br>1.10                |                              | ns<br>ns | 3     |

| ADDR/CMD output hold with respect to MCK<br>• 800 MHz data rate<br>• 667 MHz data rate      | <sup>t</sup> ddkhax                         | 0.767<br>1.02                |                              | ns<br>ns | 3     |

| MCSn output setup with respect to MCK<br>• 800 MHz data rate<br>• 667 MHz data rate         | <sup>t</sup> DDKHCS                         | 0.917<br>1.10                |                              | ns<br>ns | 3     |

| MCSn output hold with respect to MCK<br>• 800 MHz data rate<br>• 667 MHz data rate          | <sup>t</sup> DDKHCX                         | 0.767<br>1.02                |                              | ns<br>ns | 3     |

| MCK to MDQS Skew<br>• 800 MHz data rate<br>• 667 MHz data rate                              | t <sub>DDKHMH</sub>                         | -0.4<br>-0.6                 | 0.375<br>0.6                 | ns       | 4     |

| MDQ/MECC/MDM output setup with respect to MDQS <ul> <li>800 MHz</li> <li>667 MHz</li> </ul> | <sup>t</sup> DDKHDS,<br><sup>t</sup> DDKLDS | 300<br>375                   |                              | ps<br>ps | 5     |

| MDQ/MECC/MDM output hold with respect to MDQS<br>• 800 MHz<br>• 667 MHz                     | <sup>t</sup> DDKHDX,<br><sup>t</sup> DDKLDX | 300<br>375                   |                              | ps<br>ps | 5     |

| MDQS preamble                                                                               | t <sub>DDKHMP</sub>                         | $-0.9 	imes t_{MCK}$         |                              | ns       | —     |

| MDQS postamble                                                                              | t <sub>DDKHME</sub>                         | $-0.4 \times t_{\text{MCK}}$ | $-0.6 \times t_{\text{MCK}}$ | ns       | —     |

### Table 21. DDR SDRAM Output AC Timing Specifications

## 2.6.2.2 PCI Express AC Physical Layer Specifications

The AC requirements for PCI Express implementations have separate requirements for the Tx and Rx lines. The MSC8256 supports a 2.5 Gbps PCI Express interface defined by the *PCI Express Base Specification, Revision 1.0a.* The transmitter specifications are defined in Table 25 and the receiver specifications are defined in Table 26. The parameters are specified at the component pins. the AC timing specifications do not include REF\_CLK jitter.

Note: Specifications are valid at the recommended operating conditions listed in Table 3.

### Table 25. PCI Express (2.5 Gbps) Differential Transmitter (Tx) Output AC Specifications

| Parameter                                                                     | Symbol                                       | Min    | Typical | Max    | Units | Notes |

|-------------------------------------------------------------------------------|----------------------------------------------|--------|---------|--------|-------|-------|

| Unit interval                                                                 | UI                                           | 399.88 | 400.00  | 400.12 | ps    | 1     |

| Minimum Tx eye width                                                          | T <sub>TX-EYE</sub>                          | 0.70   | -       | —      | UI    | 2, 3  |

| Maximum time between the jitter median and maximum deviation from the median. | T <sub>TX-EYE-MEDIAN-</sub><br>to-MAX-JITTER | —      | —       | 0.15   | UI    | 3, 4  |

| AC coupling capacitor                                                         | C <sub>TX</sub>                              | 75     |         | 200    | nF    | 5     |

Notes: 1. Each UI is 400 ps ± 300 ppm. UI does not account for spread spectrum clock dictated variations. No test load is necessarily associated with this value.

2. The maximum transmitter jitter can be derived as  $T_{TX-MAX-JITTER} = 1 - T_{TX-EYE} = 0.3$  UI.

- 3. Specified at the measurement point into a timing and voltage compliance test load as shown in Figure 8 and measured over any 250 consecutive Tx UIs. A T<sub>TX-EYE</sub> = 0.70 UI provides for a total sum of deterministic and random jitter budget of T<sub>TX-JITTER-MAX</sub> = 0.30 UI for the transmitter collected over any 250 consecutive Tx UIs. The T<sub>TX-EYE-MEDIAN-to-MAX-JITTER</sub> median is less than half of the total Tx jitter budget collected over any 250 consecutive Tx UIs. It should be noted that the median is not the same as the mean. The jitter median describes the point in time where the number of jitter points on either side is approximately equal as opposed to the averaged time value. Jitter is defined as the measurement variation of the crossing points (V<sub>TX-DIFFp-p</sub> = 0 V) in relation to a recovered Tx UI. A recovered Tx UI is calculated over 3500 consecutive unit intervals of sample data.

- 4. Jitter is measured using all edges of the 250 consecutive UI in the center of the 3500 UI used for calculating the Tx UI.

- 5. All transmitters shall be AC-coupled. The AC coupling is required either within the media or within the transmitting component itself. The SerDes transmitter does not have built-in Tx capacitance. An external AC coupling capacitor is required.

### Table 26. PCI Express (2.5 Gbps) Differential Receiver (Rx) Input AC Specifications

| Parameter                                                                     | Symbol                                       | Min    | Typical | Мах    | Units | Notes   |

|-------------------------------------------------------------------------------|----------------------------------------------|--------|---------|--------|-------|---------|

| Unit Interval                                                                 | UI                                           | 399.88 | 400.00  | 400.12 | ps    | 1       |

| Minimum receiver eye width                                                    | T <sub>RX-EYE</sub>                          | 0.4    | —       | —      | UI    | 2, 3, 4 |

| Maximum time between the jitter median and maximum deviation from the median. | T <sub>RX-EYE-MEDIAN-to-MAX</sub><br>-JITTER | _      | _       | 0.3    | UI    | 3, 4, 5 |

Notes: 1. Each UI is 400 ps ± 300 ppm. UI does not account for spread spectrum clock dictated variations. No test load is necessarily associated with this value.

2. The maximum interconnect media and transmitter jitter that can be tolerated by the receiver can be derived as  $T_{RX-MAX-JITTER} = 1 - T_{RX-EYE} = 0.6$  UI.

3. Specified at the measurement point and measured over any 250 consecutive UIs. The test load in Figure 8 should be used as the Rx device when taking measurements. If the clocks to the Rx and Tx are not derived from the same reference clock, the Tx UI recovered from 3500 consecutive UI must be used as a reference for the eye diagram.

4. A T<sub>RX-EYE</sub> = 0.40 UI provides for a total sum of 0.60 UI deterministic and random jitter budget for the transmitter and interconnect collected any 250 consecutive UIs. The T<sub>RX-EYE-MEDIAN-to-MAX-JITTER</sub> specification ensures a jitter distribution in which the median and the maximum deviation from the median is less than half of the total. UI jitter budget collected over any 250 consecutive Tx UIs. It should be noted that the median is not the same as the mean. The jitter median describes the point in time where the number of jitter points on either side is approximately equal as opposed to the averaged time value. If the clocks to the Rx and Tx are not derived from the same reference clock, the Tx UI recovered from 3500 consecutive UI must be used as the reference for the eye diagram.

5. Jitter is defined as the measurement variation of the crossing points (V<sub>RX-DIFFp-p</sub> = 0 V) in relation to a recovered Tx UI. A recovered Tx UI is calculated over 3500 consecutive unit intervals of sample data. Jitter is measured using all edges of the 250 consecutive UI in the center of the 3500 UI used for calculating the Tx UI. It is recommended that the recovered Tx UI is calculated using all edges in the 3500 consecutive UI interval with a fit algorithm using a minimization merit function. Least squares and median deviation fits have worked well with experimental and simulated data.

#### 2.6.2.3 Serial RapidIO AC Timing Specifications

Note: Specifications are valid at the recommended operating conditions listed in Table 3.

Table 27 defines the transmitter AC specifications for the Serial RapidIO interface. The AC timing specifications do not include REF\_CLK jitter.

| Table 27. Serial RapidIO | Transmitter AC | Timing Specifications |

|--------------------------|----------------|-----------------------|

|--------------------------|----------------|-----------------------|

| Characteristic             | Symbol         | Min          | Typical | Мах          | Unit   |

|----------------------------|----------------|--------------|---------|--------------|--------|

| Deterministic Jitter       | J <sub>D</sub> | —            | —       | 0.17         | UI p-p |

| Total Jitter               | J <sub>T</sub> | —            | —       | 0.35         | UI p-p |

| Unit Interval: 1.25 GBaud  | UI             | 800 – 100ppm | 800     | 800 + 100ppm | ps     |

| Unit Interval: 2.5 GBaud   | UI             | 400 – 100ppm | 400     | 400 + 100ppm | ps     |

| Unit Interval: 3.125 GBaud | UI             | 320 – 100ppm | 320     | 320 + 100ppm | ps     |

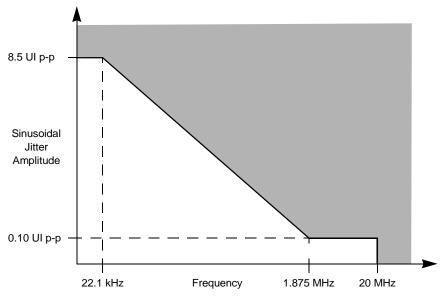

Table 28 defines the Receiver AC specifications for the Serial RapidIO interface. The AC timing specifications do not include **REF\_CLK** jitter.

### Table 28. Serial RapidIO Receiver AC Timing Specifications

| Characteristic                                        | Symbol          | Min          | Typical | Max               | Unit   | Notes |

|-------------------------------------------------------|-----------------|--------------|---------|-------------------|--------|-------|

| Deterministic Jitter Tolerance                        | J <sub>D</sub>  | 0.37         | _       | —                 | UI p-p | 1     |

| Combined Deterministic and Random Jitter<br>Tolerance | J <sub>DR</sub> | 0.55         | _       | _                 | UI p-p | 1     |

| Total Jitter Tolerance                                | J <sub>T</sub>  | 0.65         | _       | —                 | UI p-p | 1, 2  |

| Bit Error Rate                                        | BER             | —            | _       | 10 <sup>-12</sup> | _      | —     |

| Unit Interval: 1.25 GBaud                             | UI              | 800 – 100ppm | 800     | 800 + 100ppm      | ps     | _     |

| Unit Interval: 2.5 GBaud                              | UI              | 400 – 100ppm | 400     | 400 + 100ppm      | ps     | —     |

| Unit Interval: 3.125 GBaud                            | UI              | 320 – 100ppm | 320     | 320 + 100ppm      | ps     | —     |

Total jitter is composed of three components, deterministic jitter, random jitter, and single frequency sinusoidal jitter. The 2. sinusoidal jitter may have any amplitude and frequency in the unshaded region of Figure 18. The sinusoidal jitter component is included to ensure margin for low frequency jitter, wander, noise, crosstalk, and other variable system effects.

Figure 18. Single Frequency Sinusoidal Jitter Limits

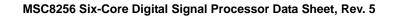

Figure 30 shows the boundary scan (JTAG) timing diagram.

Figure 30. Boundary Scan (JTAG) Timing

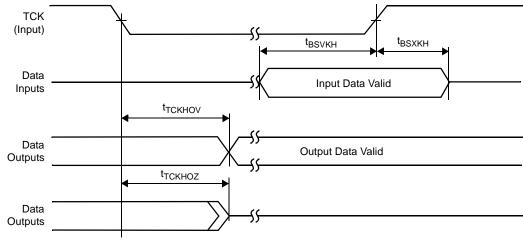

Figure 31. Test Access Port Timing

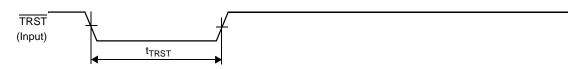

Figure 32 shows the  $\overline{\text{TRST}}$  timing diagram.

Figure 32. TRST Timing

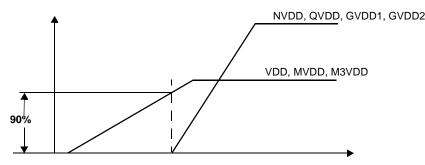

2. After the above rails rise to 90% of their nominal voltage, the following I/O power rails may rise in any sequence (see Figure 34): QVDD, NVDD, GVDD1, and GVDD2.

Figure 34. Supply Ramp-Up Sequence

- Notes: 1. If the M3 memory is not used, M3VDD can be tied to GND.

- 2. If the HSSI port1 is not used, SXCVDD1 and SXPVDD1 must be connected to the designated power supplies.

- 3. If the HSSI port2 is not used, SXCVDD2 and SXPVDD2 must be connected to the designated power supplies.

- 4. If the DDR port 1 interface is not used, it is recommended that GVDD1 be left unconnected.

- 5. If the DDR port 2 interface is not used, it is recommended that GVDD2 be left unconnected.

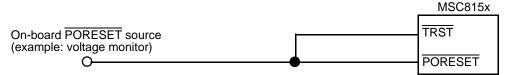

## 3.1.4 Reset Guidelines

When a debugger is not used, implement the connection scheme shown in Figure 35.

Figure 35. Reset Connection in Functional Application

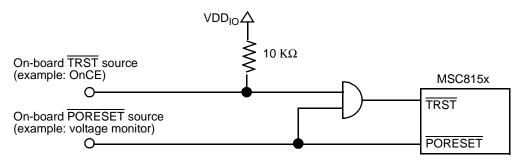

When a debugger is used, implement the connection scheme shown in Figure 36.

Figure 36. Reset Connection in Debugger Application

# 3.3 Clock and Timing Signal Board Layout Considerations

When laying out the system board, use the following guidelines:

- Keep clock and timing signal paths as short as possible and route with 50  $\Omega$  impedance.

- Use a serial termination resistor placed close to the clock buffer to minimize signal reflection. Use the following equation to compute the resistor value:

Rterm = Rim - Rbuf

where Rim = trace characteristic impedance

Rbuf = clock buffer internal impedance.

# 3.4 SGMII AC-Coupled Serial Link Connection Example

Figure 39 shows an example of a 4-wire AC-coupled serial link connection. For additional layout suggestions, see *AN3556 MSC815x High Speed Serial Interface Hardware Design Considerations*, available on the Freescale website or from your local sales office or representative.

Figure 39. 4-Wire AC-Coupled SGMII Serial Link Connection Example

# 3.5 Connectivity Guidelines

**Note:** Although the package actually uses a ball grid array, the more conventional term pin is used to denote signal connections in this discussion.

First, select the pin multiplexing mode to allocate the required I/O signals. Then use the guidelines presented in the following subsections for board design and connections. The following conventions are used in describing the connectivity requirements:

- 1. GND indicates using a 10 k $\Omega$  pull-down resistor (recommended) or a direct connection to the ground plane. Direct connections to the ground plane may yield DC current up to 50 mA through the I/O supply that adds to overall power consumption.

- 2.  $V_{DD}$  indicates using a 10 k $\Omega$  pull-up resistor (recommended) or a direct connection to the appropriate power supply. Direct connections to the supply may yield DC current up to 50 mA through the I/O supply that adds to overall power consumption.

- 3. Mandatory use of a pull-up or pull-down resistor is clearly indicated as "pull-up/pull-down." For buses, each pin on the bus should have its own resistor.

- 4. NC indicates "not connected" and means do not connect anything to the pin.

- 5. The phrase "in use" indicates a typical pin connection for the required function.

- **Note:** Please see recommendations #1 and #2 as mandatory pull-down or pull-up connection for unused pins in case of subset interface connection.

#### 3.5.1 **DDR Memory Related Pins**

This section discusses the various scenarios that can be used with either of the MSC8256 DDR ports.

The signal names in Table 40, Table 41 and Table 42 are generic names for a DDR SDRAM interface. For actual pin Note: names refer to Table 1.

#### 3.5.1.1 **DDR Interface Is Not Used**

| Signal Name              | Pin Connection |

|--------------------------|----------------|

| MDQ[0-63]                | NC             |

| MDQS[7-0]                | NC             |

| MDQS[7-0]                | NC             |

| MA[15–0]                 | NC             |

| MCK[0-2]                 | NC             |

| MCK[0-2]                 | NC             |

| MCS[1-0]                 | NC             |

| MDM[7-0]                 | NC             |

| MBA[2-0]                 | NC             |

| MCAS                     | NC             |

| MCKE[1-0]                | NC             |

| MODT[1-0]                | NC             |

| MMDIC[1-0]               | NC             |

| MRAS                     | NC             |

| MWE                      | NC             |

| MECC[7-0]                | NC             |

| MDM8                     | NC             |

| MDQS8                    | NC             |

| MDQS8                    | NC             |

| MAPAR_OUT                | NC             |

| MAPAR_IN                 | NC             |

| MVREF <sup>3</sup>       | NC             |

| GVDD1/GVDD2 <sup>3</sup> | NC             |

#### Table 40. Connectivity of DDR Related Pins When the DDR Interface Is Not Used

Clocks and General Configuration Registers chapters in the MSC8256 Reference Manual for details.

For MSC8256 Revision 1 silicon, these pins were connected to GND. For newer revisions of the MSC8256, connecting these 3. pins to GND increases device power consumption.

# 6 **Product Documentation**

Following is a general list of supporting documentation:

- *MSC8256 Technical Data Sheet* (MSC8256). Details the signals, AC/DC characteristics, clock signal characteristics, package and pinout, and electrical design considerations of the MSC8256 device.

- *MSC8256 Reference Manual* (MSC8256RM). Includes functional descriptions of the extended cores and all the internal subsystems including configuration and programming information.

- Application Notes. Cover various programming topics related to the StarCore DSP core and the MSC8256 device.

- *QUICC Engine Block Reference Manual with Protocol Interworking* (QEIWRM). Provides detailed information regarding the QUICC Engine technology including functional description, registers, and programming information.

- *SC3850 DSP Core Reference Manual*. Covers the SC3850 core architecture, control registers, clock registers, program control, and instruction set.

- *MSC8156SC3850 DSP Core Subsystem Reference Manual*. Covers core subsystem architecture, functionality, and registers.

# 7 Revision History

Table 50 provides a revision history for this data sheet.

| Rev. | Date     | Description                                                                                                                                                                      |

|------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | Apr 2010 | Initial public release.                                                                                                                                                          |

| 1    | Dec 2010 | <ul> <li>Updated Table 16.</li> <li>Updated Section 3.1.2, Power-On Ramp Time.</li> <li>Updated Section 4, Ordering Information.</li> </ul>                                      |

| 2    | Mar 2011 | <ul> <li>Updated Table 8.</li> <li>Updated Table 15.</li> <li>Updated Table 17.</li> <li>Updated Table 33.</li> <li>Updated Table 35.</li> <li>Updated Table 39.</li> </ul>      |

| 3    | May 2011 | <ul> <li>Updated Table 1. Changed the pin types for the following:</li> <li>F25 from ground to power.</li> <li>F26 from power to ground.</li> <li>T6 from power to O.</li> </ul> |

| 4    | Oct 2011 | • Updated Table 34 and Table 35 to reflect 1 Gbps and 100 Mbps data rate instead of 1 GHz and 100 MHz.                                                                           |

| 5    | Dec 2011 | • Added note 4 to Table 39.                                                                                                                                                      |

### Table 50. Document Revision History