# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0                  |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Active                                                                 |

| Core Processor             | S08                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 40MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                                     |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 22                                                                     |

| Program Memory Size        | 16KB (16K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 512 x 8                                                                |

| RAM Size                   | 1K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | A/D 16x10b                                                             |

| Oscillator Type            | External                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 28-TSSOP (0.173", 4.40mm Width)                                        |

| Supplier Device Package    | 28-TSSOP                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08el16ctlr |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Section Number

Title

### Page

| A.12.2 TPM/MTIM Module Timing             |  |

|-------------------------------------------|--|

| A.12.3 SPI                                |  |

| A.13 Flash and EEPROM Specifications      |  |

| A.14 EMC Performance                      |  |

| A.14.1 Radiated Emissions                 |  |

| A.14.2 Conducted Transient Susceptibility |  |

# Appendix B Ordering Information and Mechanical Drawings

| <b>B</b> .1 | Ordering Information          |  |

|-------------|-------------------------------|--|

|             | B.1.1 Device Numbering Scheme |  |

| B.2         | Mechanical Drawings           |  |

**Chapter 2 Pins and Connections**

# 2.2 Recommended System Connections

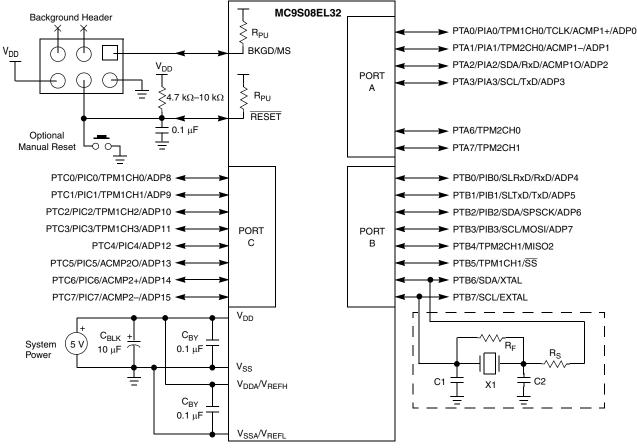

Figure 2-3 shows pin connections that are common to MC9S08EL32 Series and MC9S08SL16 Series application systems.

Figure 2-3. Basic System Connections

# 2.2.1 Power

$V_{DD}$  and  $V_{SS}$  are the primary power supply pins for the MCU. This voltage source supplies power to all I/O buffer circuitry and to an internal voltage regulator. The internal voltage regulator provides a regulated lower-voltage source to the CPU and other internal circuitry of the MCU.

Typically, application systems have two separate capacitors across the power pins. In this case, there should be a bulk electrolytic capacitor, such as a  $10-\mu$ F tantalum capacitor, to provide bulk charge storage for the overall system and a  $0.1-\mu$ F ceramic bypass capacitor located as near to the MCU power pins as practical to suppress high-frequency noise. Each pin must have a bypass capacitor for best noise suppression.

$V_{DDA}$  and  $V_{SSA}$  are the analog power supply pins for the MCU. This voltage source supplies power to the ADC module. A 0.1- $\mu$ F ceramic bypass capacitor should be located as near to the MCU power pins as practical to suppress high-frequency noise. The  $V_{REFH}$  and  $V_{REFL}$  pins are the voltage reference high and voltage reference low inputs, respectively, for the ADC module.

Chapter 2 Pins and Connections

# 4.4 RAM

The MC9S08EL32 Series and MC9S08SL16 Series includes static RAM. The locations in RAM below 0x0100 can be accessed using the more efficient direct addressing mode, and any single bit in this area can be accessed with the bit manipulation instructions (BCLR, BSET, BRCLR, and BRSET). Locating the most frequently accessed program variables in this area of RAM is preferred.

The RAM retains data when the MCU is in low-power wait, stop2, or stop3 mode. At power-on the contents of RAM are uninitialized. RAM data is unaffected by any reset provided that the supply voltage does not drop below the minimum value for RAM retention ( $V_{RAM}$ ).

For compatibility with M68HC05 MCUs, the HCS08 resets the stack pointer to 0x00FF. In the MC9S08EL32 Series and MC9S08SL16 Series, it is usually best to reinitialize the stack pointer to the top of the RAM so the direct page RAM can be used for frequently accessed RAM variables and bit-addressable program variables. Include the following 2-instruction sequence in your reset initialization routine (where RamLast is equated to the highest address of the RAM in the Freescale Semiconductor-provided equate file).

LDHX #RamLast+1 ;point one past RAM TXS ;SP<-(H:X-1)

When security is enabled, the RAM is considered a secure memory resource and is not accessible through BDM or through code executing from non-secure memory. See Section 4.5.9, "Security", for a detailed description of the security feature.

**Chapter 4 Memory**

### NOTE

The FCBEF flag will not set after launching the sector erase abort command. If an attempt is made to start a new command write sequence with a sector erase abort operation active, the FACCERR flag in the FSTAT register will be set. A new command write sequence may be started after clearing the ACCERR flag, if set.

### NOTE

The sector erase abort command should be used sparingly since a sector erase operation that is aborted counts as a complete program/erase cycle.

# 4.5.6 Access Errors

An access error occurs whenever the command execution protocol is violated.

Any of the following specific actions will cause the access error flag (FACCERR) in FSTAT to be set. FACCERR must be cleared by writing a 1 to FACCERR in FSTAT before any command can be processed.

- Writing to a FLASH address before the internal FLASH and EEPROM clock frequency has been set by writing to the FCDIV register.

- Writing to a FLASH address while FCBEF is not set. (A new command cannot be started until the command buffer is empty.)

- Writing a second time to a FLASH address before launching the previous command. (There is only one write to FLASH for every command.)

- Writing a second time to FCMD before launching the previous command. (There is only one write to FCMD for every command.)

- Writing to any FLASH control register other than FCMD after writing to a FLASH address.

- Writing any command code other than the six allowed codes (0x05, 0x20, 0x25, 0x40, 0x41, or 0x47) to FCMD.

- Writing any FLASH control register other than to write to FSTAT (to clear FCBEF and launch the command) after writing the command to FCMD.

- The MCU enters stop mode while a program or erase command is in progress. (The command is aborted.)

- Writing the byte program, burst program, sector erase or sector erase abort command code (0x20, 0x25, 0x40, or 0x47) with a background debug command while the MCU is secured. (The background debug controller can do blank check and mass erase commands only when the MCU is secure.)

- Writing 0 to FCBEF to cancel a partial command.

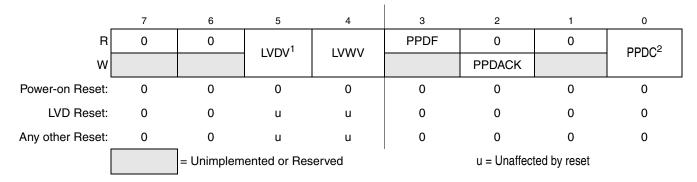

# 5.7.7 System Power Management Status and Control 2 Register (SPMSC2)

This register is used to report the status of the low voltage warning function, and to configure the stop mode behavior of the MCU.

<sup>1</sup> This bit can be written only one time after power-on reset. Additional writes are ignored.

<sup>2</sup> This bit can be written only one time after reset. Additional writes are ignored.

#### Figure 5-9. System Power Management Status and Control 2 Register (SPMSC2)

#### Table 5-10. SPMSC2 Register Field Descriptions

| Field       | Description                                                                                                                                                                                                               |  |  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 5<br>LVDV   | <b>Low-Voltage Detect Voltage Select</b> — This write-once bit selects the low voltage detect (LVD) trip point setting. It also selects the warning voltage range. See Table 5-11.                                        |  |  |

| 4<br>LVWV   | <b>Low-Voltage Warning Voltage Select</b> — This bit selects the low voltage warning (LVW) trip point voltage. See Table 5-11.                                                                                            |  |  |

| 3<br>PPDF   | <ul> <li>Partial Power Down Flag — This read-only status bit indicates that the MCU has recovered from stop2 mode.</li> <li>0 MCU has not recovered from stop2 mode.</li> <li>1 MCU recovered from stop2 mode.</li> </ul> |  |  |

| 2<br>PPDACK | Partial Power Down Acknowledge — Writing a 1 to PPDACK clears the PPDF bit                                                                                                                                                |  |  |

| 0<br>PPDC   | <ul> <li>Partial Power Down Control — This write-once bit controls whether stop2 or stop3 mode is selected.</li> <li>0 Stop3 mode enabled.</li> <li>1 Stop2, partial power down, mode enabled.</li> </ul>                 |  |  |

### Table 5-11. LVD and LVW trip point typical values<sup>1</sup>

| LVDV:LVWV | LVW Trip Point             | LVD Trip Point             |

|-----------|----------------------------|----------------------------|

| 0:0       | V <sub>LVW0</sub> = 2.74 V | V <sub>LVD0</sub> = 2.56 V |

| 0:1       | V <sub>LVW1</sub> = 2.92 V |                            |

| 1:0       | V <sub>LVW2</sub> = 4.3 V  | V <sub>LVD1</sub> = 4.0 V  |

| 1:1       | V <sub>LVW3</sub> = 4.6 V  |                            |

<sup>1</sup> See Electrical Characteristics appendix for minimum and maximum values.

#### MC9S08EL32 Series and MC9S08SL16 Series Data Sheet, Rev. 3

| Source<br>Form                                                                                                  | Operation                                                                                                                                                                                                                   | Address<br>Mode                                     | Object Code                                                                      | Cycles                          | Cyc-by-Cyc                                                         | Affect<br>on CCR      |         |

|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------|--------------------------------------------------------------------|-----------------------|---------|

| Form                                                                                                            | -                                                                                                                                                                                                                           | Ade                                                 |                                                                                  | ŝ                               | Details                                                            | <b>V</b> 1 1 <b>H</b> | INZC    |

| DIV                                                                                                             | Divide $A \leftarrow (H:A) \div (X); H \leftarrow Remainder$                                                                                                                                                                | INH                                                 | 52                                                                               | 6                               | fffffp                                                             | - 1 1 -               | ‡ ‡     |

| EOR #opr8i<br>EOR opr8a<br>EOR opr16a<br>EOR oprx16,X<br>EOR oprx8,X<br>EOR ,X<br>EOR oprx16,SP<br>EOR oprx8,SP | Exclusive OR Memory with Accumulator $A \leftarrow (A \oplus M)$                                                                                                                                                            | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | A8 ii<br>B8 dd<br>C8 hh 11<br>D8 ee ff<br>E8 ff<br>F8<br>9E D8 ee ff<br>9E E8 ff | 2<br>3<br>4<br>3<br>3<br>5<br>4 | pp<br>rpp<br>prpp<br>rpp<br>rfp<br>pprpp<br>prpp<br>prpp           | 011-                  | - ‡ ‡ - |

| INC opr8a<br>INCA<br>INCX<br>INC oprx8,X<br>INC ,X<br>INC oprx8,SP                                              | $\begin{array}{ll} \mbox{Increment} & M \leftarrow (M) + \$01 \\ & A \leftarrow (A) + \$01 \\ & X \leftarrow (X) + \$01 \\ & M \leftarrow (M) + \$01 \\ & M \leftarrow (M) + \$01 \\ & M \leftarrow (M) + \$01 \end{array}$ | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3C dd<br>4C<br>5C<br>6C ff<br>7C<br>9E 6C ff                                     | 5<br>1<br>5<br>4<br>6           | rfwpp<br>p<br>rfwpp<br>rfwp<br>prfwpp                              | ‡11-                  | - ‡ ‡ - |

| JMP opr8a<br>JMP opr16a<br>JMP oprx16,X<br>JMP oprx8,X<br>JMP ,X                                                | Jump<br>PC ← Jump Address                                                                                                                                                                                                   | DIR<br>EXT<br>IX2<br>IX1<br>IX                      | BC dd<br>CC hh ll<br>DC ee ff<br>EC ff<br>FC                                     | 3<br>4<br>4<br>3<br>3           | 900<br>900<br>900<br>900<br>900<br>900<br>900<br>900<br>900<br>900 | - 1 1 -               |         |

| JSR opr8a<br>JSR opr16a<br>JSR oprx16,X<br>JSR oprx8,X<br>JSR ,X                                                | Jump to Subroutine<br>$PC \leftarrow (PC) + n \ (n = 1, 2, or 3)$<br>Push (PCL); $SP \leftarrow (SP) - \$0001$<br>Push (PCH); $SP \leftarrow (SP) - \$0001$<br>$PC \leftarrow Unconditional Address$                        | DIR<br>EXT<br>IX2<br>IX1<br>IX                      | BD dd<br>CD hh ll<br>DD ee ff<br>ED ff<br>FD                                     | 56655                           | ssppp<br>ssppp<br>ssppp<br>ssppp                                   | - 1 1 -               |         |

| LDA #opr8i<br>LDA opr8a<br>LDA opr16a<br>LDA oprx16,X<br>LDA oprx8,X<br>LDA ,X<br>LDA oprx16,SP<br>LDA oprx8,SP | Load Accumulator from Memory $A \leftarrow (M)$                                                                                                                                                                             | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | A6 ii<br>B6 dd<br>C6 hh ll<br>D6 ee ff<br>E6 ff<br>F6<br>9E D6 ee ff<br>9E E6 ff | 2<br>3<br>4<br>3<br>3<br>5<br>4 | pp<br>rpp<br>prpp<br>prpp<br>rpp<br>rfp<br>pprpp<br>prpp           | 011-                  | - 1 1 - |

| LDHX #opr16i<br>LDHX opr8a<br>LDHX opr16a<br>LDHX ,X<br>LDHX oprx16,X<br>LDHX oprx8,X<br>LDHX oprx8,SP          | Load Index Register (H:X)<br>H:X ← (M:M + \$0001)                                                                                                                                                                           | IMM<br>DIR<br>EXT<br>IX<br>IX2<br>IX1<br>SP1        | 45 jj kk<br>55 dd<br>32 hh ll<br>9E AE<br>9E BE ee ff<br>9E CE ff<br>9E FE ff    | 3<br>4<br>5<br>5<br>6<br>5<br>5 | ppp<br>rrpp<br>prrpp<br>prrfp<br>pprrpp<br>prrpp<br>prrpp          | 011-                  | - 1 1 - |

| LDX #opr8i<br>LDX opr8a<br>LDX opr16a<br>LDX oprx16,X<br>LDX oprx8,X<br>LDX ,X<br>LDX oprx16,SP<br>LDX oprx8,SP | Load X (Index Register Low) from Memory $X \leftarrow (M)$                                                                                                                                                                  | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | AE ii<br>BE dd<br>CE hh ll<br>DE ee ff<br>EE ff<br>FE<br>9E DE ee ff<br>9E EE ff | 2<br>3<br>4<br>4<br>3<br>5<br>4 | pp<br>rpp<br>prpp<br>rpp<br>rfp<br>pprpp<br>prpp                   | 011-                  | - ‡ ‡ - |

| Table 7-2. Instruction | Set Summary | (Sheet 5 of 9) |

|------------------------|-------------|----------------|

|------------------------|-------------|----------------|

#### MC9S08EL32 Series and MC9S08SL16 Series Data Sheet, Rev. 3

### 8.4.1.5 FLL Bypassed External (FBE)

The FLL bypassed external (FBE) mode is entered when all the following conditions occur:

- CLKS bits are written to 10.

- IREFS bit is written to 0.

- BDM mode is active or LP bit is written to 0.

In FLL bypassed external mode, the ICSOUT clock is derived from the external reference clock. The FLL clock is controlled by the external reference clock, and the FLL loop will lock the FLL frequency to 1024 times the reference frequency, as selected by the RDIV bits, so that the ICSLCLK will be available for BDC communications, and the external reference clock is enabled.

### 8.4.1.6 FLL Bypassed External Low Power (FBELP)

The FLL bypassed external low power (FBELP) mode is entered when all the following conditions occur:

- CLKS bits are written to 10.

- IREFS bit is written to 0.

- BDM mode is not active and LP bit is written to 1.

In FLL bypassed external low power mode, the ICSOUT clock is derived from the external reference clock and the FLL is disabled. The ICSLCLK will be not be available for BDC communications. The external reference clock is enabled.

### 8.4.1.7 Stop

Stop mode is entered whenever the MCU enters a STOP state. In this mode, all ICS clock signals are static except in the following cases:

ICSIRCLK will be active in stop mode when all the following conditions occur:

- IRCLKEN bit is written to 1

- IREFSTEN bit is written to 1

ICSERCLK will be active in stop mode when all the following conditions occur:

- ERCLKEN bit is written to 1

- EREFSTEN bit is written to 1

### 8.4.2 Mode Switching

When switching between FLL engaged internal (FEI) and FLL engaged external (FEE) modes the IREFS bit can be changed at anytime, but the RDIV bits must be changed simultaneously so that the resulting frequency stays in the range of 31.25 kHz to 39.0625 kHz. After a change in the IREFS value the FLL will begin locking again after a few full cycles of the resulting divided reference frequency. The completion of the switch is shown by the IREFST bit.

### 9.1.3 Features

The ACMP has the following features:

- Full rail to rail supply operation.

- Selectable interrupt on rising edge, falling edge, or either rising or falling edges of comparator output.

- Option to compare to fixed internal bandgap reference voltage.

- Option to allow comparator output to be visible on a pin, ACMPxO.

- Can operate in stop3 mode

# 9.1.4 Modes of Operation

This section defines the ACMP operation in wait, stop and background debug modes.

### 9.1.4.1 ACMP in Wait Mode

The ACMP continues to run in wait mode if enabled before executing the WAIT instruction. Therefore, the ACMP can be used to bring the MCU out of wait mode if the ACMP interrupt, ACIE is enabled. For lowest possible current consumption, the ACMP should be disabled by software if not required as an interrupt source during wait mode.

### 9.1.4.2 ACMP in Stop Modes

### 9.1.4.2.1 Stop3 Mode Operation

The ACMP continues to operate in Stop3 mode if enabled and compare operation remains active. If ACOPE is enabled, comparator output operates as in the normal operating mode and comparator output is placed onto the external pin. The MCU is brought out of stop when a compare event occurs and ACIE is enabled; ACF flag sets accordingly.

If stop is exited with a reset, the ACMP will be put into its reset state.

### 9.1.4.2.2 Stop2 and Stop1 Mode Operation

During either Stop2 and Stop1 mode, the ACMP module will be fully powered down. Upon wake-up from Stop2 or Stop1 mode, the ACMP module will be in the reset state.

### 9.1.4.3 ACMP in Active Background Mode

When the microcontroller is in active background mode, the ACMP will continue to operate normally.

# Chapter 10 Analog-to-Digital Converter (S08ADCV1)

# 10.1 Introduction

The 10-bit analog-to-digital converter (ADC) is a successive approximation ADC designed for operation within an integrated microcontroller system-on-chip.

### NOTE

MC9S08EL32 Series and MC9S08SL16 Series devices operates at a higher voltage range (2.7 V to 5.5 V) and does not include stop1 mode.

The ADC channel assignments, alternate clock function, and hardware trigger function are configured as described below for the MC9S08EL32 Series and MC9S08SL16 Series family of devices.

# **10.1.1 Channel Assignments**

The ADC channel assignments for the MC9S08EL32 Series and MC9S08SL16 Series devices are shown in Table 10-1. Reserved channels convert to an unknown value.

| ADCH  | Channel | Input                              |  |

|-------|---------|------------------------------------|--|

| 00000 | AD0     | PTA0/PIA0/TPM1CH0/TCLK/ACMP1+/ADP0 |  |

| 00001 | AD1     | PTA1/PIA1/TPM2CH0/ACMP1-/ADP1      |  |

| 00010 | AD2     | PTA2/PIA2/SDA/RxD/ACMP1O/ADP2      |  |

| 00011 | AD3     | PTA3/PIA3/SCL/TxD/ADP3             |  |

| 00100 | AD4     | PTB0/PIB0/SLRxD/RxD/ADP4           |  |

| 00101 | AD5     | PTB1/PIB1/SLTxD/TxD/ADP5           |  |

| 00110 | AD6     | PTB2/PIB2/SDA/SPSCK/ADP6           |  |

| 00111 | AD7     | PTB3/PIB3/SCL/MOSI/ADP7            |  |

| 01000 | AD8     | PTC0/PIC0/TPM1CH0/ADP8             |  |

| 01001 | AD9     | PTC1/PIC1/TPM1CH1/ADP9             |  |

| 01010 | AD10    | PTC2/PIC2/TPM1CH2/ADP10            |  |

| 01011 | AD11    | PTC3/PIC3/TPM1CH3/ADP11            |  |

| 01100 | AD12    | PTC4/PIC4/ADP12                    |  |

| 01101 | AD13    | PTC5/PIC5/ACMP2O/ADP13             |  |

| 01110 | AD14    | PTC6/PIC6/ACMP2+/ADP14             |  |

| 01111 | AD15    | PTC7/PIC7/ACMP2-/ADP15             |  |

### Table 10-1. ADC Channel Assignment

| ADCH  | Channel           | Input                           |  |

|-------|-------------------|---------------------------------|--|

| 10000 | AD16              | V <sub>REFL</sub>               |  |

| 10001 | AD17              | V <sub>REFL</sub>               |  |

| 10010 | AD18              | V <sub>REFL</sub>               |  |

| 10011 | AD19              | V <sub>REFL</sub>               |  |

| 10100 | AD20              | V <sub>REFL</sub>               |  |

| 10101 | AD21              | V <sub>REFL</sub>               |  |

| 10110 | AD22              | V <sub>REFL</sub>               |  |

| 10111 | AD23              | V <sub>REFL</sub>               |  |

| 11000 | AD24              | Reserved                        |  |

| 11001 | AD25              | Reserved                        |  |

| 11010 | AD26              | Temperature Sensor <sup>1</sup> |  |

| 11011 | AD27              | Internal Bandgap <sup>2</sup>   |  |

| 11100 | V <sub>REFH</sub> | V <sub>REFH</sub>               |  |

| 11101 | V <sub>REFH</sub> | V <sub>REFH</sub>               |  |

| 11110 | V <sub>REFL</sub> | V <sub>REFL</sub>               |  |

| 11111 | Module Disabled   | None                            |  |

<sup>1</sup> For information, see Section 10.1.4, "Temperature Sensor".

<sup>2</sup> Requires BGBE =1 in SPMSC1 see Section 5.7.7, "System Power Management Status and Control 2 Register (SPMSC2)". For value of bandgap voltage reference see Section A.6, "DC Characteristics".

#### MC9S08EL32 Series and MC9S08SL16 Series Data Sheet, Rev. 3

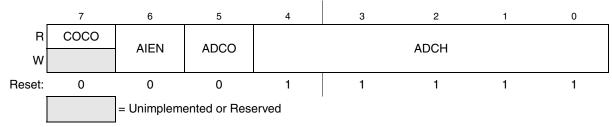

Figure 10-3. Status and Control Register (ADCSC1)

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7<br>COCO   | <ul> <li>Conversion Complete Flag — The COCO flag is a read-only bit which is set each time a conversion is completed when the compare function is disabled (ACFE = 0). When the compare function is enabled (ACFE = 1) the COCO flag is set upon completion of a conversion only if the compare result is true. This bit is cleared whenever ADCSC1 is written or whenever ADCRL is read.</li> <li>0 Conversion not completed</li> <li>1 Conversion completed</li> </ul>                                                                                                                                                                                                                                                                            |  |  |

| 6<br>AIEN   | Interrupt Enable — AIEN is used to enable conversion complete interrupts. When COCO becomes set while<br>AIEN is high, an interrupt is asserted.<br>0 Conversion complete interrupt disabled<br>1 Conversion complete interrupt enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 5<br>ADCO   | <ul> <li>Continuous Conversion Enable — ADCO is used to enable continuous conversions.</li> <li>One conversion following a write to the ADCSC1 when software triggered operation is selected, or one conversion following assertion of ADHWT when hardware triggered operation is selected.</li> <li>Continuous conversions initiated following a write to ADCSC1 when software triggered operation is selected. Continuous conversions are initiated by an ADHWT event when hardware triggered operation is selected.</li> </ul>                                                                                                                                                                                                                    |  |  |

| 4:0<br>ADCH | Input Channel Select — The ADCH bits form a 5-bit field which is used to select one of the input channels. The input channels are detailed in Figure 10-4.<br>The successive approximation converter subsystem is turned off when the channel select bits are all set to 1.<br>This feature allows for explicit disabling of the ADC and isolation of the input channel from all sources.<br>Terminating continuous conversions this way will prevent an additional, single conversion from being performed.<br>It is not necessary to set the channel select bits to all 1s to place the ADC in a low-power state when continuous conversion are not enabled because the module automatically enters a low-power state when a conversion completes. |  |  |

### Figure 10-4. Input Channel Select

| ADCH  | Input Select |

|-------|--------------|

| 00000 | AD0          |

| 00001 | AD1          |

| 00010 | AD2          |

| 00011 | AD3          |

| 00100 | AD4          |

| 00101 | AD5          |

| 00110 | AD6          |

| 00111 | AD7          |

| ADCH  | Input Select |

|-------|--------------|

| 10000 | AD16         |

| 10001 | AD17         |

| 10010 | AD18         |

| 10011 | AD19         |

| 10100 | AD20         |

| 10101 | AD21         |

| 10110 | AD22         |

| 10111 | AD23         |

#### MC9S08EL32 Series and MC9S08SL16 Series Data Sheet, Rev. 3

| ADCH  | Input Select |

|-------|--------------|

| 01000 | AD8          |

| 01001 | AD9          |

| 01010 | AD10         |

| 01011 | AD11         |

| 01100 | AD12         |

| 01101 | AD13         |

| 01110 | AD14         |

| 01111 | AD15         |

| Input Select      |

|-------------------|

| AD24              |

| AD25              |

| AD26              |

| AD27              |

| Reserved          |

| V <sub>REFH</sub> |

| V <sub>REFL</sub> |

| Module disabled   |

|                   |

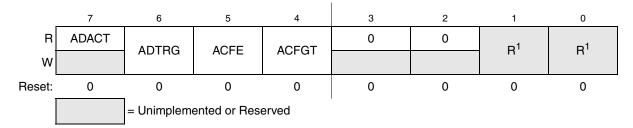

# 10.3.2 Status and Control Register 2 (ADCSC2)

The ADCSC2 register is used to control the compare function, conversion trigger and conversion active of the ADC module.

<sup>1</sup> Bits 1 and 0 are reserved bits that must always be written to 0.

#### Figure 10-5. Status and Control Register 2 (ADCSC2)

#### Table 10-4. ADCSC2 Register Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>ADACT | <ul> <li>Conversion Active — ADACT indicates that a conversion is in progress. ADACT is set when a conversion is initiated and cleared when a conversion is completed or aborted.</li> <li>Conversion not in progress</li> <li>Conversion in progress</li> </ul>                                                                                                                                                                                                                                      |

| 6<br>ADTRG | <ul> <li>Conversion Trigger Select — ADTRG is used to select the type of trigger to be used for initiating a conversion.</li> <li>Two types of trigger are selectable: software trigger and hardware trigger. When software trigger is selected, a conversion is initiated following a write to ADCSC1. When hardware trigger is selected, a conversion is initiated following the assertion of the ADHWT input.</li> <li>O Software trigger selected</li> <li>1 Hardware trigger selected</li> </ul> |

# **11.4 Functional Description**

This section provides a complete functional description of the IIC module.

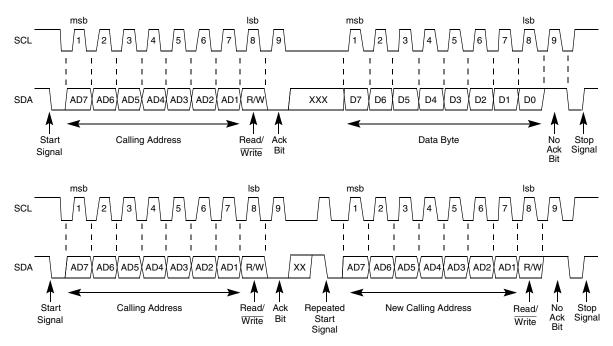

# 11.4.1 IIC Protocol

The IIC bus system uses a serial data line (SDA) and a serial clock line (SCL) for data transfer. All devices connected to it must have open drain or open collector outputs. A logic AND function is exercised on both lines with external pull-up resistors. The value of these resistors is system dependent.

Normally, a standard communication is composed of four parts:

- Start signal

- Slave address transmission

- Data transfer

- Stop signal

The stop signal should not be confused with the CPU stop instruction. The IIC bus system communication is described briefly in the following sections and illustrated in Figure 11-9.

Figure 11-9. IIC Bus Transmission Signals

### 11.4.1.1 Start Signal

When the bus is free, no master device is engaging the bus (SCL and SDA lines are at logical high), a master may initiate communication by sending a start signal. As shown in Figure 11-9, a start signal is defined as a high-to-low transition of SDA while SCL is high. This signal denotes the beginning of a new data transfer (each data transfer may contain several bytes of data) and brings all slaves out of their idle states.

The SLIC clock is the same as the CPU bus clock. The module is designed to provide better than 1% bit rate accuracy at the lowest value of the SLIC clock frequency and the accuracy improves as the SLIC clock frequency is increased. For this reason, it is advantageous to choose the fastest SLIC clock which is still within the acceptable operating range of the SLIC.Because the SLIC may be used with MCUs with internal oscillators, the tolerance of the oscillator must be taken into account to ensure that SLIC clock frequency does not exceed the bounds of the SLIC clock operating range. This is especially important if the user wishes to use the oscillator untrimmed, where process variations might result in MCU frequency offsets of  $\pm 25\%$ .

The acceptable range of SLIC clock frequencies is 2 to 20 MHz to guarantee LIN operations with greater than 1.5% accuracy across the 1–20 kbps range of LIN bit rates. The user must ensure that the fastest possible SLIC clock frequency never exceeds 20 MHz or that the slowest possible SLIC clock never falls below 2 MHz under worst case conditions. This would include, for example, oscillator frequency variations due to untrimmed oscillator tolerance, temperature variation, or supply voltage variation.

To initialize the SLIC module into LIN operating mode, the user must perform the following steps prior to needing to receive any LIN message traffic. These steps assume the MCU has been reset either by a power-on reset (POR) or any other MCU reset mechanism.

The steps for SLIC Initialization for LIN operation are:

- 1. Write SLCC1 to clear INITREQ.

- 2. When INITACK = 0, write SLCC1 & SLCC2 with desired values for:

- a) SLCWCM Wait clock mode.

- 3. Write SLCC2 to set up prescalers for:

- a) RXFP Digital receive filter clock prescaler.

- 4. Enable the SLIC module by writing SLCC2:

- a) SLCE = 1 to place SLIC module into run mode.

- b) BTM = 0 to disable byte transfer mode.

- 5. Write SLCC1 to enable SLIC interrupts (if desired).

# 12.6.6.2 Byte Transfer Mode Initialization

Bit rate synchronization is handled automatically in LIN mode, using the synchronization data contained in each LIN message to derive the desired bit rate. In byte transfer mode (BTM = 1); however, the user must set up the bit rate for communications using SLCBT.

More information on byte transfer mode is described in Section 12.6.16, "Byte Transfer Mode Operation," including the performance parameters on recommended maximum speeds, bit time resolution, and oscillator tolerance requirements.

After the desired settings of bit time are determined, the SLIC Initialization for BTM operation is virtually identical to that of LIN operation.

The steps are:

1. Write SLCC1 to clear INITREQ.

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>SPRF  | <ul> <li>SPI Read Buffer Full Flag — SPRF is set at the completion of an SPI transfer to indicate that received data may be read from the SPI data register (SPID). SPRF is cleared by reading SPRF while it is set, then reading the SPI data register.</li> <li>0 No data available in the receive data buffer</li> <li>1 Data available in the receive data buffer</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 5<br>SPTEF | <ul> <li>SPI Transmit Buffer Empty Flag — This bit is set when there is room in the transmit data buffer. It is cleared by reading SPIS with SPTEF set, followed by writing a data value to the transmit buffer at SPID. SPIS must be read with SPTEF = 1 before writing data to SPID or the SPID write will be ignored. SPTEF generates an SPTEF CPU interrupt request if the SPTIE bit in the SPIC1 is also set. SPTEF is automatically set when a data byte transfers from the transmit buffer into the transmit shift register. For an idle SPI (no data in the transmit buffer or the shift register and no transfer in progress), data written to SPID is transferred to the shifter almost immediately so SPTEF is set within two bus cycles allowing a second 8-bit data value to be queued into the transmit buffer. After completion of the transfer of the value in the shift register, the queued value from the transmit buffer will automatically move to the shifter and SPTEF will be set to indicate there is room for new data in the transmit buffer. If no new data is waiting in the transmit buffer, SPTEF simply remains set and no data moves from the buffer to the shifter.</li> <li>O SPI transmit buffer not empty</li> <li>1 SPI transmit buffer empty</li> </ul> |

| 4<br>MODF  | Master Mode Fault Flag — MODF is set if the SPI is configured as a master and the slave select input goes low, indicating some other SPI device is also configured as a master. The SS pin acts as a mode fault error input only when MSTR = 1, MODFEN = 1, and SSOE = 0; otherwise, MODF will never be set. MODF is cleared by reading MODF while it is 1, then writing to SPI control register 1 (SPIC1).<br>0 No mode fault error<br>1 Mode fault error detected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

# 13.4.5 SPI Data Register (SPID)

|        | 7     | 6 | 5 | 4 | 3 | 2 | 1 | 0     |

|--------|-------|---|---|---|---|---|---|-------|

| R<br>W | Bit 7 | 6 | 5 | 4 | 3 | 2 | 1 | Bit 0 |

| Reset  | 0     | 0 | 0 | 0 | 0 | 0 | 0 | 0     |

| Reset  | 0     | 0 | 0 | 0 | 0 | 0 | 0 | 0     |

Figure 13-9. SPI Data Register (SPID)

Reads of this register return the data read from the receive data buffer. Writes to this register write data to the transmit data buffer. When the SPI is configured as a master, writing data to the transmit data buffer initiates an SPI transfer.

Data should not be written to the transmit data buffer unless the SPI transmit buffer empty flag (SPTEF) is set, indicating there is room in the transmit buffer to queue a new transmit byte.

Data may be read from SPID any time after SPRF is set and before another transfer is finished. Failure to read the data out of the receive data buffer before a new transfer ends causes a receive overrun condition and the data from the new transfer is lost.

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>TDRE | Transmit Data Register Empty Flag — TDRE is set out of reset and when a transmit data value transfers from the transmit data buffer to the transmit shifter, leaving room for a new character in the buffer. To clear TDRE, read SCIxS1 with TDRE = 1 and then write to the SCI data register (SCIxD).         0       Transmit data register (buffer) full.         1       Transmit data register (buffer) empty.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6<br>TC   | Transmission Complete Flag — TC is set out of reset and when TDRE = 1 and no data, preamble, or break character is being transmitted.         0       Transmitter active (sending data, a preamble, or a break).         1       Transmitter idle (transmission activity complete).         TC is cleared automatically by reading SCIxS1 with TC = 1 and then doing one of the following three things:         •       Write to the SCI data register (SCIxD) to transmit new data         •       Queue a preamble by changing TE from 0 to 1         •       Queue a break character by writing 1 to SBK in SCIxC2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5<br>RDRF | <ul> <li>Receive Data Register Full Flag — RDRF becomes set when a character transfers from the receive shifter into the receive data register (SCIxD). To clear RDRF, read SCIxS1 with RDRF = 1 and then read the SCI data register (SCIxD).</li> <li>0 Receive data register empty.</li> <li>1 Receive data register full.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 4<br>IDLE | Idle Line Flag — IDLE is set when the SCI receive line becomes idle for a full character time after a period of activity. When ILT = 0, the receiver starts counting idle bit times after the start bit. So if the receive character is all 1s, these bit times and the stop bit time count toward the full character time of logic high (10 or 11 bit times depending on the M control bit) needed for the receiver to detect an idle line. When ILT = 1, the receiver doesn't start counting idle bit times until after the stop bit. So the stop bit and any logic high bit times at the end of the previous character do not count toward the full character time of logic high needed for the receiver to detect an idle line.         To clear IDLE, read SCIxS1 with IDLE = 1 and then read the SCI data register (SCIxD). After IDLE has been cleared, it cannot become set again until after a new character has been received and RDRF has been set. IDLE will get set only once even if the receive line remains idle for an extended period.         0       No idle line detected.         1       Idle line was detected. |

| 3<br>OR   | <ul> <li>Receiver Overrun Flag — OR is set when a new serial character is ready to be transferred to the receive data register (buffer), but the previously received character has not been read from SCIxD yet. In this case, the new character (and all associated error information) is lost because there is no room to move it into SCIxD. To clear OR, read SCIxS1 with OR = 1 and then read the SCI data register (SCIxD).</li> <li>0 No overrun.</li> <li>1 Receive overrun (new SCI data lost).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2<br>NF   | <ul> <li>Noise Flag — The advanced sampling technique used in the receiver takes seven samples during the start bit and three samples in each data bit and the stop bit. If any of these samples disagrees with the rest of the samples within any bit time in the frame, the flag NF will be set at the same time as the flag RDRF gets set for the character. To clear NF, read SCIxS1 and then read the SCI data register (SCIxD).</li> <li>0 No noise detected.</li> <li>1 Noise detected in the received character in SCIxD.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

### Table 14-5. SCIxS1 Field Descriptions

#### Timer/PWM Module (S08TPMV3)

(becomes unlatched) when the TPMxCnSC register is written (whether BDM mode is active or not). Any write to the channel registers will be ignored during the input capture mode.

When BDM is active, the coherency mechanism is frozen (unless reset by writing to TPMxCnSC register) such that the buffer latches remain in the state they were in when the BDM became active, even if one or both halves of the channel register are read while BDM is active. This assures that if the user was in the middle of reading a 16-bit register when BDM became active, it will read the appropriate value from the other half of the 16-bit value after returning to normal execution. The value read from the TPMxCnVH and TPMxCnVL registers in BDM mode is the value of these registers and not the value of their read buffer.

In output compare or PWM modes, writing to either byte (TPMxCnVH or TPMxCnVL) latches the value into a buffer. After both bytes are written, they are transferred as a coherent 16-bit value into the timer-channel registers according to the value of CLKSB:CLKSA bits and the selected mode, so:

- If (CLKSB:CLKSA = 0:0), then the registers are updated when the second byte is written.

- If (CLKSB:CLKSA not = 0:0 and in output compare mode) then the registers are updated after the second byte is written and on the next change of the TPM counter (end of the prescaler counting).

- If (CLKSB:CLKSA not = 0:0 and in EPWM or CPWM modes), then the registers are updated after the both bytes were written, and the TPM counter changes from (TPMxMODH:TPMxMODL - 1) to (TPMxMODH:TPMxMODL). If the TPM counter is a free-running counter then the update is made when the TPM counter changes from 0xFFFE to 0xFFFF.

The latching mechanism may be manually reset by writing to the TPMxCnSC register (whether BDM mode is active or not). This latching mechanism allows coherent 16-bit writes in either big-endian or little-endian order which is friendly to various compiler implementations.

When BDM is active, the coherency mechanism is frozen such that the buffer latches remain in the state they were in when the BDM became active even if one or both halves of the channel register are written while BDM is active. Any write to the channel registers bypasses the buffer latches and directly write to the channel register while BDM is active. The values written to the channel register while BDM is active are used for PWM & output compare operation once normal execution resumes. Writes to the channel registers while BDM is active do not interfere with partial completion of a coherency sequence. After the coherency mechanism has been fully exercised, the channel registers are updated using the buffered values written (while BDM was not active) by the user.

# 16.4 Functional Description

All TPM functions are associated with a central 16-bit counter which allows flexible selection of the clock source and prescale factor. There is also a 16-bit modulo register associated with the main counter.

The CPWMS control bit chooses between center-aligned PWM operation for all channels in the TPM (CPWMS=1) or general purpose timing functions (CPWMS=0) where each channel can independently be configured to operate in input capture, output compare, or edge-aligned PWM mode. The CPWMS control bit is located in the main TPM status and control register because it affects all channels within the TPM and influences the way the main counter operates. (In CPWM mode, the counter changes to an up/down mode rather than the up-counting mode used for general purpose timer functions.)

Timer/PWM Module (S08TPMV3)

### 16.6.2.1.2 Center-Aligned PWM Case

When CPWMS=1, TOF gets set when the timer counter changes direction from up-counting to down-counting at the end of the terminal count (the value in the modulo register). In this case the TOF corresponds to the end of a PWM period.

### 16.6.2.2 Channel Event Interrupt Description

The meaning of channel interrupts depends on the channel's current mode (input-capture, output-compare, edge-aligned PWM, or center-aligned PWM).

### 16.6.2.2.1 Input Capture Events

When a channel is configured as an input capture channel, the ELSnB:ELSnA control bits select no edge (off), rising edges, falling edges or any edge as the edge which triggers an input capture event. When the selected edge is detected, the interrupt flag is set. The flag is cleared by the two-step sequence described in Section 16.6.2, "Description of Interrupt Operation."

### 16.6.2.2.2 Output Compare Events

When a channel is configured as an output compare channel, the interrupt flag is set each time the main timer counter matches the 16-bit value in the channel value register. The flag is cleared by the two-step sequence described Section 16.6.2, "Description of Interrupt Operation."

### 16.6.2.2.3 PWM End-of-Duty-Cycle Events

For channels configured for PWM operation there are two possibilities. When the channel is configured for edge-aligned PWM, the channel flag gets set when the timer counter matches the channel value register which marks the end of the active duty cycle period. When the channel is configured for center-aligned PWM, the timer count matches the channel value register twice during each PWM cycle. In this CPWM case, the channel flag is set at the start and at the end of the active duty cycle period which are the times when the timer counter matches the channel value register. The flag is cleared by the two-step sequence described Section 16.6.2, "Description of Interrupt Operation."

# 16.7 The Differences from TPM v2 to TPM v3

1. Write to TPMxCNTH:L registers (Section 16.3.2, "TPM-Counter Registers (TPMxCNTH:TPMxCNTL)) [SE110-TPM case 7]

Any write to TPMxCNTH or TPMxCNTL registers in TPM v3 clears the TPM counter (TPMxCNTH:L) and the prescaler counter. Instead, in the TPM v2 only the TPM counter is cleared in this case.

- 2. Read of TPMxCNTH:L registers (Section 16.3.2, "TPM-Counter Registers (TPMxCNTH:TPMxCNTL))

- In TPM v3, any read of TPMxCNTH:L registers during BDM mode returns the value of the TPM counter that is frozen. In TPM v2, if only one byte of the TPMxCNTH:L registers was read before the BDM mode became active, then any read of TPMxCNTH:L registers during

| Command<br>Mnemonic | Active BDM/<br>Non-intrusive | Coding<br>Structure | Description                                                                             |  |  |

|---------------------|------------------------------|---------------------|-----------------------------------------------------------------------------------------|--|--|

| SYNC                | Non-intrusive                | n/a <sup>1</sup>    | Request a timed reference pulse to determine target BDC communication speed             |  |  |

| ACK_ENABLE          | Non-intrusive                | D5/d                | Enable acknowledge protocol. Refer to<br>Freescale document order no. HCS08RMv1/D.      |  |  |

| ACK_DISABLE         | Non-intrusive                | D6/d                | Disable acknowledge protocol. Refer to<br>Freescale document order no. HCS08RMv1/D.     |  |  |

| BACKGROUND          | Non-intrusive                | 90/d                | Enter active background mode if enabled (ignore if ENBDM bit equals 0)                  |  |  |

| READ_STATUS         | Non-intrusive                | E4/SS               | Read BDC status from BDCSCR                                                             |  |  |

| WRITE_CONTROL       | Non-intrusive                | C4/CC               | Write BDC controls in BDCSCR                                                            |  |  |

| READ_BYTE           | Non-intrusive                | E0/AAAA/d/RD        | Read a byte from target memory                                                          |  |  |

| READ_BYTE_WS        | Non-intrusive                | E1/AAAA/d/SS/RD     | Read a byte and report status                                                           |  |  |

| READ_LAST           | Non-intrusive                | E8/SS/RD            | Re-read byte from address just read and report status                                   |  |  |

| WRITE_BYTE          | Non-intrusive                | C0/AAAA/WD/d        | Write a byte to target memory                                                           |  |  |

| WRITE_BYTE_WS       | Non-intrusive                | C1/AAAA/WD/d/SS     | Write a byte and report status                                                          |  |  |

| READ_BKPT           | Non-intrusive                | E2/RBKP             | Read BDCBKPT breakpoint register                                                        |  |  |

| WRITE_BKPT          | Non-intrusive                | C2/WBKP             | Write BDCBKPT breakpoint register                                                       |  |  |

| GO                  | Active BDM                   | 08/d                | Go to execute the user application program starting at the address currently in the PC  |  |  |

| TRACE1              | Active BDM                   | 10/d                | Trace 1 user instruction at the address in th PC, then return to active background mode |  |  |

| TAGGO               | Active BDM                   | 18/d                | Same as GO but enable external tagging<br>(HCS08 devices have no external tagging p     |  |  |

| READ_A              | Active BDM                   | 68/d/RD             | Read accumulator (A)                                                                    |  |  |

| READ_CCR            | Active BDM                   | 69/d/RD             | Read condition code register (CCR)                                                      |  |  |

| READ_PC             | Active BDM                   | 6B/d/RD16           | Read program counter (PC)                                                               |  |  |

| READ_HX             | Active BDM                   | 6C/d/RD16           | Read H and X register pair (H:X)                                                        |  |  |

| READ_SP             | Active BDM                   | 6F/d/RD16           | Read stack pointer (SP)                                                                 |  |  |

| READ_NEXT           | Active BDM                   | 70/d/RD             | Increment H:X by one then read memory byte located at H:X                               |  |  |

| READ_NEXT_WS        | Active BDM                   | 71/d/SS/RD          | Increment H:X by one then read memory byte located at H:X. Report status and data.      |  |  |

| WRITE_A             | Active BDM                   | 48/WD/d             | Write accumulator (A)                                                                   |  |  |

| WRITE_CCR           | Active BDM                   | 49/WD/d             | Write condition code register (CCR)                                                     |  |  |

| WRITE_PC            | Active BDM                   | 4B/WD16/d           | Write program counter (PC)                                                              |  |  |

| WRITE_HX            | Active BDM                   | 4C/WD16/d           | Write H and X register pair (H:X)                                                       |  |  |

| WRITE_SP            | Active BDM                   | 4F/WD16/d           | Write stack pointer (SP)                                                                |  |  |

| WRITE_NEXT          | Active BDM                   | 50/WD/d             | Increment H:X by one, then write memory byte located at H:X                             |  |  |

| WRITE_NEXT_WS       | Active BDM                   | 51/WD/d/SS          | Increment H:X by one, then write memory byte located at H:X. Also report status.        |  |  |

| Table 17-1 | . BDC | Command | Summary |

|------------|-------|---------|---------|

|------------|-------|---------|---------|

<sup>1</sup> The SYNC command is a special operation that does not have a command code.

| Num <sup>1</sup> | С | Rating <sup>2</sup> |                 | Symbol                             | Min                          | Max                                   | Unit     |

|------------------|---|---------------------|-----------------|------------------------------------|------------------------------|---------------------------------------|----------|

| 11               | D |                     | laster<br>Slave | t <sub>HO</sub><br>t <sub>HO</sub> | -10<br>-10                   |                                       | ns<br>ns |

| 12               | D |                     | laster<br>Slave | f <sub>op</sub><br>f <sub>op</sub> | f <sub>Bus</sub> /2048<br>dc | 5 <sup>5</sup><br>f <sub>Bus</sub> /4 | MHz      |

Table A-15. SPI Electrical Characteristic (continued)

<sup>1</sup> Refer to Figure A-14 through Figure A-17.

<sup>2</sup> All timing is shown with respect to 20% V<sub>DD</sub> and 70% V<sub>DD</sub>, unless noted; 100 pF load on all SPI pins. All timing assumes slew rate control disabled and high drive strength enabled for SPI output pins.

$^{3}\,$  Time to data active from high-impedance state.

<sup>4</sup> Hold time to high-impedance state.

<sup>5</sup> Maximum baud rate must be limited to 5 MHz due to input filter characteristics.

NOTES:

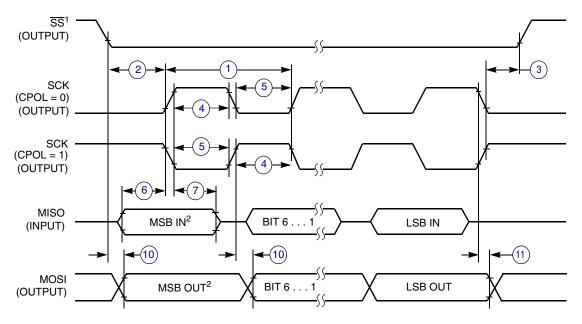

1.  $\overline{SS}$  output mode (MODFEN = 1, SSOE = 1).

2. LSBF = 0. For LSBF = 1, bit order is LSB, bit 1, ..., bit 6, MSB.

Figure A-14. SPI Master Timing (CPHA = 0)