# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | S08                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 40MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                                    |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 22                                                                    |

| Program Memory Size        | 32KB (32K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 512 x 8                                                               |

| RAM Size                   | 1K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                           |

| Data Converters            | A/D 16x10b                                                            |

| Oscillator Type            | External                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 28-TSSOP (0.173", 4.40mm Width)                                       |

| Supplier Device Package    | 28-TSSOP                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08el32ctl |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Contents

| Section Number | Title | Page |

|----------------|-------|------|

|                |       |      |

# Chapter 1 Device Overview

| 1.1 | Devices in the MC9S08EL32 Series and MC9S08SL16 Series | 19 |

|-----|--------------------------------------------------------|----|

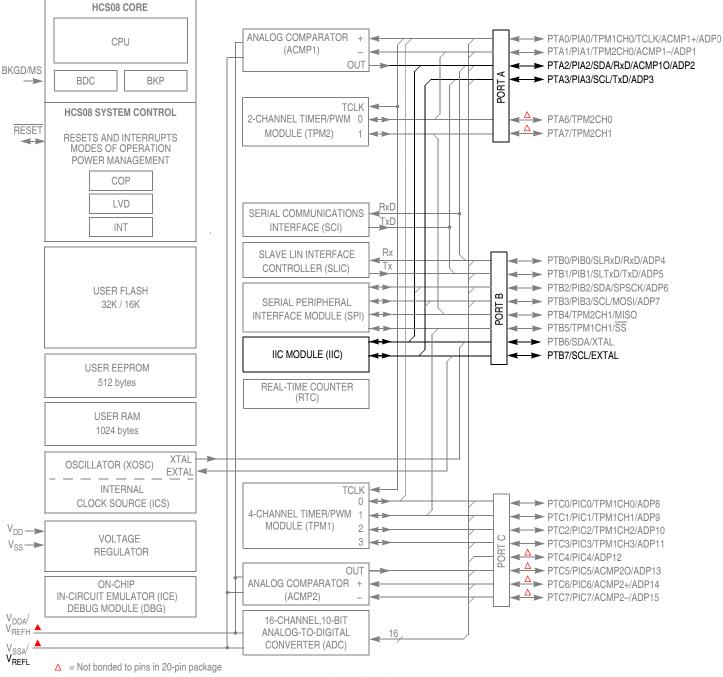

| 1.2 | MCU Block Diagram                                      | 20 |

|     | System Clock Distribution                              |    |

# Chapter 2 Pins and Connections

| 2.1 | Device | Pin Assignment                           |  |

|-----|--------|------------------------------------------|--|

|     |        | nended System Connections                |  |

|     |        | Power                                    |  |

|     | 2.2.2  | Oscillator                               |  |

|     | 2.2.3  | RESET                                    |  |

|     | 2.2.4  | Background / Mode Select (BKGD/MS)       |  |

|     |        | General-Purpose I/O and Peripheral Ports |  |

# Chapter 3 Modes of Operation

| 3.1 | Introduction                             | 31 |

|-----|------------------------------------------|----|

| 3.2 | Features                                 | 31 |

| 3.3 | Run Mode                                 | 31 |

| 3.4 | Active Background Mode                   | 31 |

|     | Wait Mode                                |    |

| 3.6 | Stop Modes                               | 32 |

|     | 3.6.1 Stop3 Mode                         | 33 |

| 3.7 | Stop2 Mode                               | 34 |

|     | On-Chip Peripheral Modules in Stop Modes |    |

## Chapter 4 Memory

|     |                                                       | mennery                             |  |  |  |  |

|-----|-------------------------------------------------------|-------------------------------------|--|--|--|--|

| 4.1 | .1 MC9S08EL32 Series and MC9S08SL16 Series Memory Map |                                     |  |  |  |  |

| 4.2 | Reset an                                              | nd Interrupt Vector Assignments     |  |  |  |  |

|     |                                                       | r Addresses and Bit Assignments     |  |  |  |  |

| 4.4 | RAM                                                   | ~                                   |  |  |  |  |

| 4.5 | FLASH                                                 | and EEPROM                          |  |  |  |  |

|     | 4.5.1                                                 | Features                            |  |  |  |  |

|     | 4.5.2                                                 | Program and Erase Times             |  |  |  |  |

|     | 4.5.3                                                 | Program and Erase Command Execution |  |  |  |  |

|     |                                                       | Burst Program Execution             |  |  |  |  |

|     |                                                       | C                                   |  |  |  |  |

## Section Number

Title

## Page

| A.12.2 TPM/MTIM Module Timing             |  |

|-------------------------------------------|--|

| A.12.3 SPI                                |  |

| A.13 Flash and EEPROM Specifications      |  |

| A.14 EMC Performance                      |  |

| A.14.1 Radiated Emissions                 |  |

| A.14.2 Conducted Transient Susceptibility |  |

# Appendix B Ordering Information and Mechanical Drawings

| <b>B</b> .1 | Ordering Information          |  |

|-------------|-------------------------------|--|

|             | B.1.1 Device Numbering Scheme |  |

| B.2         | Mechanical Drawings           |  |

Chapter 2 Pins and Connections

#### Table 4-2. Direct-Page Register Summary (Sheet 2 of 3)

| Address                            | Register<br>Name | Bit 7  | 6       | 5     | 4      | 3       | 2     | 1       | Bit 0    |

|------------------------------------|------------------|--------|---------|-------|--------|---------|-------|---------|----------|

| 0x00 <b>31</b> -<br>0x00 <b>37</b> | Reserved         | _      | _       | _     | _      | _       | _     |         | —        |

| 0x00 <b>38</b>                     | SCIBDH           | LBKDIE | RXEDGIE | 0     | SBR12  | SBR11   | SBR10 | SBR9    | SBR8     |

| 0x00 <b>39</b>                     | SCIBDL           | SBR7   | SBR6    | SBR5  | SBR4   | SBR3    | SBR2  | SBR1    | SBR0     |

| 0x00 <b>3A</b>                     | SCIC1            | LOOPS  | SCISWAI | RSRC  | М      | WAKE    | ILT   | PE      | PT       |

| 0x00 <b>3B</b>                     | SCIC2            | TIE    | TCIE    | RIE   | ILIE   | TE      | RE    | RWU     | SBK      |

| 0x00 <b>3C</b>                     | SCIS1            | TDRE   | TC      | RDRF  | IDLE   | OR      | NF    | FE      | PF       |

| 0x00 <b>3D</b>                     | SCIS2            | LBKDIF | RXEDGIF | 0     | RXINV  | RWUID   | BRK13 | LBKDE   | RAF      |

| 0x00 <b>3E</b>                     | SCIC3            | R8     | T8      | TXDIR | TXINV  | ORIE    | NEIE  | FEIE    | PEIE     |

| 0x00 <b>3F</b>                     | SCID             | Bit 7  | 6       | 5     | 4      | 3       | 2     | 1       | Bit 0    |

| 0x00 <b>40</b> –<br>0x00 <b>47</b> | Reserved         | _      | _       | _     | _      | _       |       | _       |          |

| 0x00 <b>48</b>                     | ICSC1            | CL     | KS      |       | RDIV   | L       | IREFS | IRCLKEN | IREFSTEN |

| 0x00 <b>49</b>                     | ICSC2            | BD     | DIV     | RANGE | HGO    | LP      | EREFS | ERCLKEN | EREFSTEN |

| 0x00 <b>4A</b>                     | ICSTRM           | -      |         |       | TR     | MIM     |       |         | •        |

| 0x00 <b>4B</b>                     | ICSSC            | 0      | 0       | 0     | IREFST | CLł     | KST   | OSCINIT | FTRIM    |

| 0x00 <b>4C</b> –<br>0x00 <b>4F</b> | Reserved         | _      |         | _     | _      | _       |       |         |          |

| 0x00 <b>50</b>                     | SPIC1            | SPIE   | SPE     | SPTIE | MSTR   | CPOL    | CPHA  | SSOE    | LSBFE    |

| 0x00 <b>51</b>                     | SPIC2            | 0      | 0       | 0     | MODFEN | BIDIROE | 0     | SPISWAI | SPC0     |

| 0x00 <b>52</b>                     | SPIBR            | 0      | SPPR2   | SPPR1 | SPPR0  | 0       | SPR2  | SPR1    | SPR0     |

| 0x00 <b>53</b>                     | SPIS             | SPRF   | 0       | SPTEF | MODF   | 0       | 0     | 0       | 0        |

| 0x00 <b>54</b>                     | Reserved         | 0      | 0       | 0     | 0      | 0       | 0     | 0       | 0        |

| 0x00 <b>55</b>                     | SPID             | Bit 7  | 6       | 5     | 4      | 3       | 2     | 1       | Bit 0    |

| 0x00 <b>56</b> –<br>0x00 <b>57</b> | Reserved         | _      |         | _     | _      | _       |       |         |          |

| 0x00 <b>58</b>                     | IICA             | AD7    | AD6     | AD5   | AD4    | AD3     | AD2   | AD1     | 0        |

| 0x00 <b>59</b>                     | licf             | MU     | JLT     |       | •      | IC      | R     | •       |          |

| 0x00 <b>5A</b>                     | IICC1            | IICEN  | IICIE   | MST   | ТХ     | TXAK    | RSTA  | 0       | 0        |

| 0x00 <b>5B</b>                     | IICS             | TCF    | IAAS    | BUSY  | ARBL   | 0       | SRW   | IICIF   | RXAK     |

| 0x00 <b>5C</b>                     | IICD             |        |         |       | DA     | TA      |       |         | •        |

| 0x00 <b>5D</b>                     | IICC2            | GCAEN  | ADEXT   | 0     | 0      | 0       | AD10  | AD9     | AD8      |

| 0x00 <b>5E</b> –<br>0x00 <b>5F</b> | Reserved         | _      |         | _     | _      | —       | _     |         | _<br>_   |

| 0x00 <b>60</b>                     | TPM2SC           | TOF    | TOIE    | CPWMS | CLKSB  | CLKSA   | PS2   | PS1     | PS0      |

| 0x00 <b>61</b>                     | TPM2CNTH         | Bit 15 | 14      | 13    | 12     | 11      | 10    | 9       | Bit 8    |

| 0x00 <b>62</b>                     | TPM2CNTL         | Bit 7  | 6       | 5     | 4      | 3       | 2     | 1       | Bit 0    |

| 0x00 <b>63</b>                     | TPM2MODH         | Bit 15 | 14      | 13    | 12     | 11      | 10    | 9       | Bit 8    |

| 0x00 <b>64</b>                     | TPM2MODL         | Bit 7  | 6       | 5     | 4      | 3       | 2     | 1       | Bit 0    |

| 0x00 <b>65</b>                     | TPM2C0SC         | CH0F   | CH0IE   | MS0B  | MS0A   | ELS0B   | ELS0A | 0       | 0        |

| Parameter          | Cycles of FCLK | Time if FCLK = 200 kHz |

|--------------------|----------------|------------------------|

| Byte program       | 9              | 45 μs                  |

| Burst program      | 4              | 20 μs <sup>1</sup>     |

| Sector erase       | 4000           | 20 ms                  |

| Mass erase         | 20,000         | 100 ms                 |

| Sector erase abort | 4              | 20 μs <sup>1</sup>     |

Table 4-5. Program and Erase Times

<sup>1</sup> Excluding start/end overhead

# 4.5.3 **Program and Erase Command Execution**

The FCDIV register must be initialized following any reset and any error flags cleared before beginning command execution. The command execution steps are:

1. Write a data value to an address in the FLASH or EEPROM array. The address and data information from this write is latched into the FLASH and EEPROM interface. This write is a required first step in any command sequence. For erase and blank check commands, the value of the data is not important. For sector erase commands, the address can be any address in the 512-byte sector of FLASH or 8-byte sector of EEPROM to be erased. For mass erase and blank check commands, the address can be any address in the FLASH or EEPROM memory. FLASH and EEPROM erase independently of each other.

#### NOTE

Do not program any byte in the FLASH or EEPROM more than once after a successful erase operation. Reprogramming bits in a byte which is already programmed is not allowed without first erasing the sector in which the byte resides or mass erasing the entire FLASH or EEPROM memory. Programming without first erasing may disturb data stored in the FLASH or EEPROM.

- 2. Write the command code for the desired command to FCMD. The six valid commands are blank check (0x05), byte program (0x20), burst program (0x25), sector erase (0x40), mass erase (0x41), and sector erase abort (0x47). The command code is latched into the command buffer.

- 3. Write a 1 to the FCBEF bit in FSTAT to clear FCBEF and launch the command (including its address and data information).

A partial command sequence can be aborted manually by writing a 0 to FCBEF any time after the write to the memory array and before writing the 1 that clears FCBEF and launches the complete command. Aborting a command in this way sets the FACCERR access error flag which must be cleared before starting a new command.

A strictly monitored procedure must be obeyed or the command will not be accepted. This minimizes the possibility of any unintended changes to the memory contents. The command complete flag (FCCF) indicates when a command is complete. The command sequence must be completed by clearing FCBEF to launch the command. Figure 4-2 is a flowchart for executing all of the commands except for burst programming and sector erase abort.

# 5.7.3 System Options Register 1 (SOPT1)

This high page register is a write-once register so only the first write after reset is honored. It can be read at any time. Any subsequent attempt to write to SOPT1 (intentionally or unintentionally) is ignored to avoid accidental changes to these sensitive settings. SOPT1 should be written during the user's reset initialization program to set the desired controls even if the desired settings are the same as the reset settings.

| _      | 7    | 6   | 5     | 4     | 3     | 2 | 1 | 0 |

|--------|------|-----|-------|-------|-------|---|---|---|

| R      | C    | ODT | STOPE | SCIPS |       |   | 0 | 0 |

| w      | COPT |     | STOPE | 50IP5 | IICPS |   |   |   |

| Reset: | 1    | 1   | 0     | 0     | 0     | 0 | 0 | 0 |

| Г      |      |     |       |       |       |   |   |   |

= Unimplemented or Reserved

#### Figure 5-4. System Options Register 1 (SOPT1)

#### Table 5-5. SOPT1 Register Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 7:6<br>COPT[1:0] | <b>COP Watchdog Timeout</b> — These write-once bits select the timeout period of the COP. COPT along with COPCLKS in SOPT2 defines the COP timeout period. See Table 5-1.                                                                                                   |  |  |  |  |  |  |  |

| 5<br>STOPE       | <ul> <li>Stop Mode Enable — This write-once bit is used to enable stop mode. If stop mode is disabled and a user program attempts to execute a STOP instruction, an illegal opcode reset is forced.</li> <li>0 Stop mode disabled.</li> <li>1 Stop mode enabled.</li> </ul> |  |  |  |  |  |  |  |

| 4<br>SCIPS       | <ul> <li>SCI Pin Select— This write-once bit selects the location of the RxD and TxD pins of the SCI module.</li> <li>0 RxD on PTB0, TxD on PTB1.</li> <li>1 RxD on PTA2, TxD on PTA3.</li> </ul>                                                                           |  |  |  |  |  |  |  |

| 3:2<br>IICPS     | <ul> <li>IIC Pin Select— These write-once bits select the location of the SCL and SDA pins of the IIC module.</li> <li>OD SDA on PTA2, SCL on PTA3.</li> <li>O1 SDA on PTB6, SCL on PTB7.</li> <li>1x SDA on PTB2, SCL on PTB3.</li> </ul>                                  |  |  |  |  |  |  |  |

# 5.7.7 System Power Management Status and Control 2 Register (SPMSC2)

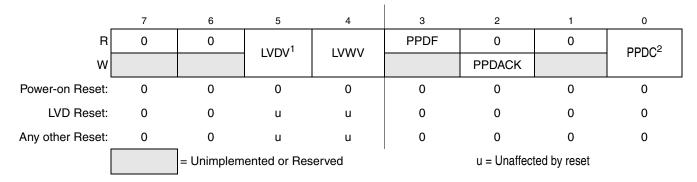

This register is used to report the status of the low voltage warning function, and to configure the stop mode behavior of the MCU.

<sup>1</sup> This bit can be written only one time after power-on reset. Additional writes are ignored.

<sup>2</sup> This bit can be written only one time after reset. Additional writes are ignored.

#### Figure 5-9. System Power Management Status and Control 2 Register (SPMSC2)

#### Table 5-10. SPMSC2 Register Field Descriptions

| Field       | Description                                                                                                                                                                                                               |  |  |  |  |  |  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 5<br>LVDV   | <b>Low-Voltage Detect Voltage Select</b> — This write-once bit selects the low voltage detect (LVD) trip point setting. It also selects the warning voltage range. See Table 5-11.                                        |  |  |  |  |  |  |

| 4<br>LVWV   | <b>Low-Voltage Warning Voltage Select</b> — This bit selects the low voltage warning (LVW) trip point voltage. See Table 5-11.                                                                                            |  |  |  |  |  |  |

| 3<br>PPDF   | <ul> <li>Partial Power Down Flag — This read-only status bit indicates that the MCU has recovered from stop2 mode.</li> <li>0 MCU has not recovered from stop2 mode.</li> <li>1 MCU recovered from stop2 mode.</li> </ul> |  |  |  |  |  |  |

| 2<br>PPDACK | Partial Power Down Acknowledge — Writing a 1 to PPDACK clears the PPDF bit                                                                                                                                                |  |  |  |  |  |  |

| 0<br>PPDC   | <ul> <li>Partial Power Down Control — This write-once bit controls whether stop2 or stop3 mode is selected.</li> <li>0 Stop3 mode enabled.</li> <li>1 Stop2, partial power down, mode enabled.</li> </ul>                 |  |  |  |  |  |  |

#### Table 5-11. LVD and LVW trip point typical values<sup>1</sup>

| LVDV:LVWV | LVW Trip Point             | LVD Trip Point             |

|-----------|----------------------------|----------------------------|

| 0:0       | V <sub>LVW0</sub> = 2.74 V | V <sub>LVD0</sub> = 2.56 V |

| 0:1       | V <sub>LVW1</sub> = 2.92 V |                            |

| 1:0       | V <sub>LVW2</sub> = 4.3 V  | V <sub>LVD1</sub> = 4.0 V  |

| 1:1       | V <sub>LVW3</sub> = 4.6 V  |                            |

<sup>1</sup> See Electrical Characteristics appendix for minimum and maximum values.

# 7.3.6.7 SP-Relative, 16-Bit Offset (SP2)

This variation of indexed addressing uses the 16-bit value in the stack pointer (SP) plus a 16-bit offset included in the instruction as the address of the operand needed to complete the instruction.

# 7.4 Special Operations

The CPU performs a few special operations that are similar to instructions but do not have opcodes like other CPU instructions. In addition, a few instructions such as STOP and WAIT directly affect other MCU circuitry. This section provides additional information about these operations.

# 7.4.1 Reset Sequence

Reset can be caused by a power-on-reset (POR) event, internal conditions such as the COP (computer operating properly) watchdog, or by assertion of an external active-low reset pin. When a reset event occurs, the CPU immediately stops whatever it is doing (the MCU does not wait for an instruction boundary before responding to a reset event). For a more detailed discussion about how the MCU recognizes resets and determines the source, refer to the Resets, Interrupts, and System Configuration chapter.

The reset event is considered concluded when the sequence to determine whether the reset came from an internal source is done and when the reset pin is no longer asserted. At the conclusion of a reset event, the CPU performs a 6-cycle sequence to fetch the reset vector from 0xFFFE and 0xFFFF and to fill the instruction queue in preparation for execution of the first program instruction.

# 7.4.2 Interrupt Sequence

When an interrupt is requested, the CPU completes the current instruction before responding to the interrupt. At this point, the program counter is pointing at the start of the next instruction, which is where the CPU should return after servicing the interrupt. The CPU responds to an interrupt by performing the same sequence of operations as for a software interrupt (SWI) instruction, except the address used for the vector fetch is determined by the highest priority interrupt that is pending when the interrupt sequence started.

The CPU sequence for an interrupt is:

- 1. Store the contents of PCL, PCH, X, A, and CCR on the stack, in that order.

- 2. Set the I bit in the CCR.

- 3. Fetch the high-order half of the interrupt vector.

- 4. Fetch the low-order half of the interrupt vector.

- 5. Delay for one free bus cycle.

- 6. Fetch three bytes of program information starting at the address indicated by the interrupt vector to fill the instruction queue in preparation for execution of the first instruction in the interrupt service routine.

After the CCR contents are pushed onto the stack, the I bit in the CCR is set to prevent other interrupts while in the interrupt service routine. Although it is possible to clear the I bit with an instruction in the

#### Internal Clock Source (S08ICSV2)

The CLKS bits can also be changed at anytime, but the RDIV bits must be changed simultaneously so that the resulting frequency stays in the range of 31.25 kHz to 39.0625 kHz. The actual switch to the newly selected clock will not occur until after a few full cycles of the new clock. If the newly selected clock is not available, the previous clock will remain selected.

## 8.4.3 Bus Frequency Divider

The BDIV bits can be changed at anytime and the actual switch to the new frequency will occur immediately.

## 8.4.4 Low Power Bit Usage

The low power bit (LP) is provided to allow the FLL to be disabled and thus conserve power when it is not being used. However, in some applications it may be desirable to enable the FLL and allow it to lock for maximum accuracy before switching to an FLL engaged mode. Do this by writing the LP bit to 0.

## 8.4.5 Internal Reference Clock

When IRCLKEN is set the internal reference clock signal will be presented as ICSIRCLK, which can be used as an additional clock source. The ICSIRCLK frequency can be re-targeted by trimming the period of the internal reference clock. This can be done by writing a new value to the TRIM bits in the ICSTRM register. Writing a larger value will slow down the ICSIRCLK frequency, and writing a smaller value to the ICSTRM register will speed up the ICSIRCLK frequency. The TRIM bits will effect the ICSOUT frequency if the ICS is in FLL engaged internal (FEI), FLL bypassed internal (FBI), or FLL bypassed internal low power (FBILP) mode. The TRIM and FTRIM value will not be affected by a reset.

Until ICSIRCLK is trimmed, programming low reference divider (RDIV) factors may result in ICSOUT frequencies that exceed the maximum chip-level frequency and violate the chip-level clock timing specifications (see the Device Overview chapter).

If IREFSTEN is set and the IRCLKEN bit is written to 1, the internal reference clock will keep running during stop mode in order to provide a fast recovery upon exiting stop.

All MCU devices are factory programmed with a trim value in a reserved memory location. This value can be copied to the ICSTRM register during reset initialization. The factory trim value does not include the FTRIM bit. For finer precision, the user can trim the internal oscillator in the application and set the FTRIM bit accordingly.

# 8.4.6 Optional External Reference Clock

The ICS module can support an external reference clock with frequencies between 31.25 kHz to 5 MHz in all modes. When the ERCLKEN is set, the external reference clock signal will be presented as ICSERCLK, which can be used as an additional clock source. When IREFS = 1, the external reference clock will not be used by the FLL and will only be used as ICSERCLK. In these modes, the frequency can be equal to the maximum frequency the chip-level timing specifications will support (see the Device Overview chapter).

#### Chapter 11 Inter-Integrated Circuit (S08IICV2)

In 20-pin packages, V<sub>DDA</sub>/V<sub>REFH</sub> is internally connected to V<sub>DD</sub> and V<sub>SSA</sub>/V<sub>REFL</sub> is internally connected to V<sub>SS</sub>.

Figure 11-1. MC9S08EL32 Block Diagram Highlighting IIC Block and Pins

# **11.4 Functional Description**

This section provides a complete functional description of the IIC module.

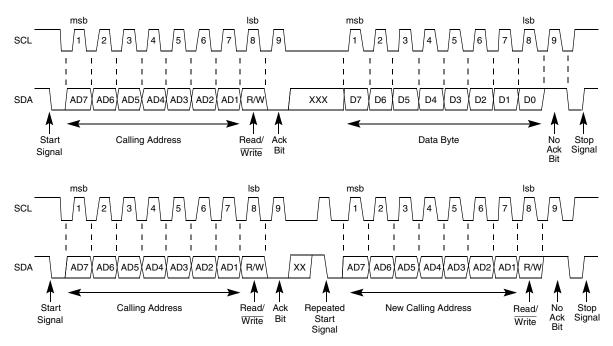

# 11.4.1 IIC Protocol

The IIC bus system uses a serial data line (SDA) and a serial clock line (SCL) for data transfer. All devices connected to it must have open drain or open collector outputs. A logic AND function is exercised on both lines with external pull-up resistors. The value of these resistors is system dependent.

Normally, a standard communication is composed of four parts:

- Start signal

- Slave address transmission

- Data transfer

- Stop signal

The stop signal should not be confused with the CPU stop instruction. The IIC bus system communication is described briefly in the following sections and illustrated in Figure 11-9.

Figure 11-9. IIC Bus Transmission Signals

## 11.4.1.1 Start Signal

When the bus is free, no master device is engaging the bus (SCL and SDA lines are at logical high), a master may initiate communication by sending a start signal. As shown in Figure 11-9, a start signal is defined as a high-to-low transition of SDA while SCL is high. This signal denotes the beginning of a new data transfer (each data transfer may contain several bytes of data) and brings all slaves out of their idle states.

# 11.4.1.5 Repeated Start Signal

As shown in Figure 11-9, a repeated start signal is a start signal generated without first generating a stop signal to terminate the communication. This is used by the master to communicate with another slave or with the same slave in different mode (transmit/receive mode) without releasing the bus.

# 11.4.1.6 Arbitration Procedure

The IIC bus is a true multi-master bus that allows more than one master to be connected on it. If two or more masters try to control the bus at the same time, a clock synchronization procedure determines the bus clock, for which the low period is equal to the longest clock low period and the high is equal to the shortest one among the masters. The relative priority of the contending masters is determined by a data arbitration procedure, a bus master loses arbitration if it transmits logic 1 while another master transmits logic 0. The losing masters immediately switch over to slave receive mode and stop driving SDA output. In this case, the transition from master to slave mode does not generate a stop condition. Meanwhile, a status bit is set by hardware to indicate loss of arbitration.

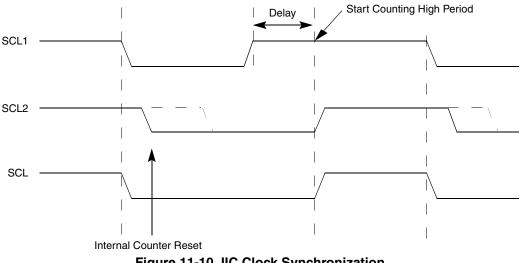

## 11.4.1.7 Clock Synchronization

Because wire-AND logic is performed on the SCL line, a high-to-low transition on the SCL line affects all the devices connected on the bus. The devices start counting their low period and after a device's clock has gone low, it holds the SCL line low until the clock high state is reached. However, the change of low to high in this device clock may not change the state of the SCL line if another device clock is still within its low period. Therefore, synchronized clock SCL is held low by the device with the longest low period. Devices with shorter low periods enter a high wait state during this time (see Figure 11-10). When all devices concerned have counted off their low period, the synchronized clock SCL line is released and pulled high. There is then no difference between the device clocks and the state of the SCL line and all the devices start counting their high periods. The first device to complete its high period pulls the SCL line low again.

Figure 11-10. IIC Clock Synchronization

entering SLIC stop mode, any activity on the network will cause the SLIC module to exit SLIC stop mode and generate an unmaskable interrupt of the CPU. This wakeup interrupt state is reflected in the SLCSV, encoded as the highest priority interrupt. This interrupt can be cleared by the CPU with a read of the SLCSV and clearing of the SLCF interrupt flag. Depending upon which low-power mode instruction the CPU executes to cause the SLIC module to enter SLIC stop, the message which wakes up the SLIC module (and the CPU) may or may not be received.

There are two different possibilities:

1. Wakeup from SLIC Stop with CPU in STOP

When the CPU executes the STOP instruction, all clocks in the MCU, including clocks to the SLIC module, are turned off. Therefore, the message which wakes up the SLIC module and the CPU from stop mode will not be received. This is due primarily to the amount of time required for the MCU's oscillator to stabilize before the clocks can be applied internally to the other MCU modules, including the SLIC module.

2. Wakeup from SLIC Stop with CPU in WAIT. If the CPU executes the WAIT instruction and the SLIC module enters the stop mode (SLCWCM = 1), the clocks to the SLIC module are turned off, but the clocks in the MCU continue to run. Therefore, the message which wakes up the SLIC module from stop and the CPU from wait mode will be received correctly by the SLIC module. This is because very little time is required for the CPU to turn the clocks to the SLIC module back on after the wakeup interrupt occurs.

#### NOTE

While the SLIC module will correctly receive a message which arrives when the SLIC module is in stop or wait mode and the MCU is in wait mode, if the user enters this mode while a message is being received, the data in the message will become corrupted. This is due to the steps required for the SLIC module to resume operation upon exiting stop or wait mode, and its subsequent resynchronization with the LIN bus.

#### 12.1.2.8 Normal and Emulation Mode Operation

The SLIC module operates in the same manner in all normal and emulation modes. All SLIC module registers can be read and written except those that are reserved, unimplemented, or write once. The user must be careful not to unintentionally change reserved bits to avoid unexpected SLIC module behavior.

## 12.1.2.9 Special Mode Operation

Some aspects of SLIC module operation can be modified in special test mode. This mode is reserved for internal use only.

## 12.1.2.10 Low-Power Options

The SLIC module can save power in disabled, wait, and stop modes.

## NOTE

Do not write the CHKMOD or data length values in SLCDLC more than one time per message frame. The SLIC tracks the number of sent or received bytes based on the value written to this register at the beginning of the data field and rewriting this register will corrupt the checksum calculation and cause unpredictable behavior in the SLIC module. The application software must track the number of sent or received bytes to know what the current byte count in the SLIC is. If programming in C, make sure to use the STATIC modifier on this variable (or make it a global variable) to ensure that it keeps its value between interrupts.

## 12.6.9.3 Transmit Abort

The transmit abort bit (TXABRT) in SLCC1 allows the user to cease transmission of data on the next byte boundary. When this bit is set to 1, it will finish transmitting the byte currently being transmitted, then cease transmission. After the transmission is successfully aborted, TXABRT will automatically be reset by the SLIC to 0. If the SLIC is not in process of transmitting at the time TXABRT is written to 1, there is no effect and TXABRT will read back as 0.

## 12.6.9.4 Possible Errors on Request Message Data

Possible errors on request message data are:

- Byte Framing Error

- Checksum-Error (LIN specified error)

- Bit-Error

# 12.6.10 Handling IMSG to Minimize Interrupts

The IMSG feature is designed to minimize the number of interrupts required to maintain LIN communications. On a network with many slave nodes, it is very likely that a particular slave will observe messages which are not intended for that node. When the SLIC module detects any message header, it synchronizes to that message frame and bit rate, then interrupts the CPU after the identifier byte has been successfully received and parity checked. At this time, if the software determines that the message may be ignored, IMSG may be set to indicate to the module that the data field of the message frame is to be ignored and no additional interrupts should be generated until the next valid message header is received. The bit is automatically reset to 0 after the current message frame is complete and the LIN bus returns to idle state. This reduces the load on the CPU and allows the application software to immediately begin performing any operations which might otherwise not be allowed while receiving messaging.

#### NOTE

IMSG will prevent another interrupt from occurring for the current message frame, however if data bytes are appearing on the bus they may be received and copied into the message buffer. This will delete any previous data which might have been present in the buffer, even though no interrupt is triggered to indicate the arrival of this data.

#### Serial Peripheral Interface (S08SPIV3)

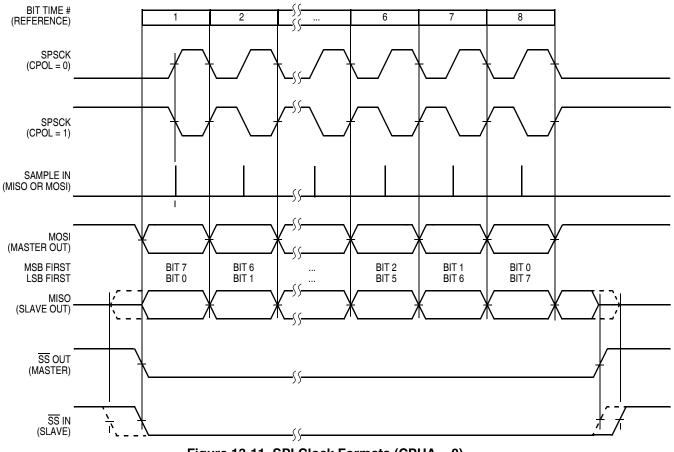

in LSBFE. Both variations of SPSCK polarity are shown, but only one of these waveforms applies for a specific transfer, depending on the value in CPOL. The SAMPLE IN waveform applies to the MOSI input of a slave or the MISO input of a master. The MOSI waveform applies to the MOSI output pin from a master and the MISO waveform applies to the MISO output from a slave. The  $\overline{SS}$  OUT waveform applies to the slave select output from a master (provided MODFEN and SSOE = 1). The master  $\overline{SS}$  output goes to active low at the start of the first bit time of the transfer and goes back high one-half SPSCK cycle after the end of the eighth bit time of the transfer. The  $\overline{SS}$  IN waveform applies to the slave select input of a slave.

When CPHA = 0, the slave begins to drive its MISO output with the first data bit value (MSB or LSB depending on LSBFE) when  $\overline{SS}$  goes to active low. The first SPSCK edge causes both the master and the slave to sample the data bit values on their MISO and MOSI inputs, respectively. At the second SPSCK edge, the SPI shifter shifts one bit position which shifts in the bit value that was just sampled and shifts the second data bit value out the other end of the shifter to the MOSI and MISO outputs of the master and slave, respectively. When CPHA = 0, the slave's  $\overline{SS}$  input must go to its inactive high level between transfers.

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 3<br>WAKE | Receiver Wakeup Method Select — Refer to Section 14.3.3.2, "Receiver Wakeup Operation" for more information.         0       Idle-line wakeup.         1       Address-mark wakeup.                                                                                                                                                                                                                                               |  |  |  |  |  |

| 2<br>ILT  | Idle Line Type Select — Setting this bit to 1 ensures that the stop bit and logic 1 bits at the end of a character do not count toward the 10 or 11 bit times of logic high level needed by the idle line detection logic. Refer to Section 14.3.3.2.1, "Idle-Line Wakeup" for more information.         0       Idle character bit count starts after start bit.         1       Idle character bit count starts after stop bit. |  |  |  |  |  |

| 1<br>PE   | <ul> <li>Parity Enable — Enables hardware parity generation and checking. When parity is enabled, the most significant bit (MSB) of the data character (eighth or ninth data bit) is treated as the parity bit.</li> <li>0 No hardware parity generation or checking.</li> <li>1 Parity enabled.</li> </ul>                                                                                                                       |  |  |  |  |  |

| 0<br>PT   | <ul> <li>Parity Type — Provided parity is enabled (PE = 1), this bit selects even or odd parity. Odd parity means the total number of 1s in the data character, including the parity bit, is odd. Even parity means the total number of 1s in the data character, including the parity bit, is even.</li> <li>0 Even parity.</li> <li>1 Odd parity.</li> </ul>                                                                    |  |  |  |  |  |

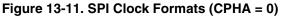

# 14.2.3 SCI Control Register 2 (SCIxC2)

This register can be read or written at any time.

Figure 14-7. SCI Control Register 2 (SCIxC2)

#### Table 14-4. SCIxC2 Field Descriptions

| Field     | Description                                                                                                                                                                                   |  |  |  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7<br>TIE  | Transmit Interrupt Enable (for TDRE)0Hardware interrupts from TDRE disabled (use polling).1Hardware interrupt requested when TDRE flag is 1.                                                  |  |  |  |

| 6<br>TCIE | <ul> <li>Transmission Complete Interrupt Enable (for TC)</li> <li>0 Hardware interrupts from TC disabled (use polling).</li> <li>1 Hardware interrupt requested when TC flag is 1.</li> </ul> |  |  |  |

| 5<br>RIE  | <ul> <li>Receiver Interrupt Enable (for RDRF)</li> <li>0 Hardware interrupts from RDRF disabled (use polling).</li> <li>1 Hardware interrupt requested when RDRF flag is 1.</li> </ul>        |  |  |  |

| 4<br>ILIE | Idle Line Interrupt Enable (for IDLE)00111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111 <td< td=""></td<>                               |  |  |  |

| Field                   | Description                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 4<br>TXINV <sup>1</sup> | Transmit Data Inversion — Setting this bit reverses the polarity of the transmitted data output.0011Transmit data inverted                                                                                                                       |  |  |  |  |  |  |

| 3<br>ORIE               | <ul> <li>Overrun Interrupt Enable — This bit enables the overrun flag (OR) to generate hardware interrupt requests.</li> <li>O OR interrupts disabled (use polling).</li> <li>1 Hardware interrupt requested when OR = 1.</li> </ul>             |  |  |  |  |  |  |

| 2<br>NEIE               | <ul> <li>Noise Error Interrupt Enable — This bit enables the noise flag (NF) to generate hardware interrupt requests.</li> <li>0 NF interrupts disabled (use polling).</li> <li>1 Hardware interrupt requested when NF = 1.</li> </ul>           |  |  |  |  |  |  |

| 1<br>FEIE               | <ul> <li>Framing Error Interrupt Enable — This bit enables the framing error flag (FE) to generate hardware interrupt requests.</li> <li>0 FE interrupts disabled (use polling).</li> <li>1 Hardware interrupt requested when FE = 1.</li> </ul> |  |  |  |  |  |  |

| 0<br>PEIE               | <ul> <li>Parity Error Interrupt Enable — This bit enables the parity error flag (PF) to generate hardware interrupt requests.</li> <li>0 PF interrupts disabled (use polling).</li> <li>1 Hardware interrupt requested when PF = 1.</li> </ul>   |  |  |  |  |  |  |

#### Table 14-7. SCIxC3 Field Descriptions (continued)

Setting TXINV inverts the TxD output for all cases: data bits, start and stop bits, break, and idle.

# 14.2.7 SCI Data Register (SCIxD)

This register is actually two separate registers. Reads return the contents of the read-only receive data buffer and writes go to the write-only transmit data buffer. Reads and writes of this register are also involved in the automatic flag clearing mechanisms for the SCI status flags.

|       | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|-------|----|----|----|----|----|----|----|----|

| R     | R7 | R6 | R5 | R4 | R3 | R2 | R1 | R0 |

| w     | T7 | Т6 | T5 | T4 | Т3 | T2 | T1 | Т0 |

| Reset | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

Figure 14-11. SCI Data Register (SCIxD)

# 14.3 Functional Description

The SCI allows full-duplex, asynchronous, NRZ serial communication among the MCU and remote devices, including other MCUs. The SCI comprises a baud rate generator, transmitter, and receiver block. The transmitter and receiver operate independently, although they use the same baud rate generator. During normal operation, the MCU monitors the status of the SCI, writes the data to be transmitted, and processes received data. The following describes each of the blocks of the SCI.

## 14.3.1 Baud Rate Generation

As shown in Figure 14-12, the clock source for the SCI baud rate generator is the bus-rate clock.

## 16.4.1.3 Counting Modes

The main timer counter has two counting modes. When center-aligned PWM is selected (CPWMS=1), the counter operates in up/down counting mode. Otherwise, the counter operates as a simple up counter. As an up counter, the timer counter counts from 0x0000 through its terminal count and then continues with 0x0000. The terminal count is 0xFFFF or a modulus value in TPMxMODH:TPMxMODL.

When center-aligned PWM operation is specified, the counter counts up from 0x0000 through its terminal count and then down to 0x0000 where it changes back to up counting. Both 0x0000 and the terminal count value are normal length counts (one timer clock period long). In this mode, the timer overflow flag (TOF) becomes set at the end of the terminal-count period (as the count changes to the next lower count value).

#### 16.4.1.4 Manual Counter Reset

The main timer counter can be manually reset at any time by writing any value to either half of TPMxCNTH or TPMxCNTL. Resetting the counter in this manner also resets the coherency mechanism in case only half of the counter was read before resetting the count.

## 16.4.2 Channel Mode Selection

Provided CPWMS=0, the MSnB and MSnA control bits in the channel n status and control registers determine the basic mode of operation for the corresponding channel. Choices include input capture, output compare, and edge-aligned PWM.

#### 16.4.2.1 Input Capture Mode

With the input-capture function, the TPM can capture the time at which an external event occurs. When an active edge occurs on the pin of an input-capture channel, the TPM latches the contents of the TPM counter into the channel-value registers (TPMxCnVH:TPMxCnVL). Rising edges, falling edges, or any edge may be chosen as the active edge that triggers an input capture.

In input capture mode, the TPMxCnVH and TPMxCnVL registers are read only.

When either half of the 16-bit capture register is read, the other half is latched into a buffer to support coherent 16-bit accesses in big-endian or little-endian order. The coherency sequence can be manually reset by writing to the channel status/control register (TPMxCnSC).

An input capture event sets a flag bit (CHnF) which may optionally generate a CPU interrupt request.

While in BDM, the input capture function works as configured by the user. When an external event occurs, the TPM latches the contents of the TPM counter (which is frozen because of the BDM mode) into the channel value registers and sets the flag bit.

## 16.4.2.2 Output Compare Mode

With the output-compare function, the TPM can generate timed pulses with programmable position, polarity, duration, and frequency. When the counter reaches the value in the channel-value registers of an output-compare channel, the TPM can set, clear, or toggle the channel pin.

# Chapter 17 Development Support

# 17.1 Introduction

Development support systems in the HCS08 include the background debug controller (BDC) and the on-chip debug module (DBG). The BDC provides a single-wire debug interface to the target MCU that provides a convenient interface for programming the on-chip FLASH and other nonvolatile memories. The BDC is also the primary debug interface for development and allows non-intrusive access to memory data and traditional debug features such as CPU register modify, breakpoints, and single instruction trace commands.

In the HCS08 Family, address and data bus signals are not available on external pins (not even in test modes). Debug is done through commands fed into the target MCU via the single-wire background debug interface. The debug module provides a means to selectively trigger and capture bus information so an external development system can reconstruct what happened inside the MCU on a cycle-by-cycle basis without having external access to the address and data signals.

# 17.1.1 Forcing Active Background

The method for forcing active background mode depends on the specific HCS08 derivative. For the MC9S08EL32 Series and MC9S08SL16 Series, you can force active background after a power-on reset by holding the BKGD pin low as the device exits the reset condition (independent of the reset source). You can also force active background by driving BKGD low immediately after a serial background command that writes a one to the BDFR bit in the SBDFR register. If no debug pod is connected to the BKGD pin, the MCU always resets into normal operating mode.

#### **Development Support**

When no debugger pod is connected to the 6-pin BDM interface connector, the internal pullup on BKGD chooses normal operating mode. When a debug pod is connected to BKGD it is possible to force the MCU into active background mode after reset. The specific conditions for forcing active background depend upon the HCS08 derivative (refer to the introduction to this Development Support section). It is not necessary to reset the target MCU to communicate with it through the background debug interface.

## 17.2.2 Communication Details

The BDC serial interface requires the external controller to generate a falling edge on the BKGD pin to indicate the start of each bit time. The external controller provides this falling edge whether data is transmitted or received.

BKGD is a pseudo-open-drain pin that can be driven either by an external controller or by the MCU. Data is transferred MSB first at 16 BDC clock cycles per bit (nominal speed). The interface times out if 512 BDC clock cycles occur between falling edges from the host. Any BDC command that was in progress when this timeout occurs is aborted without affecting the memory or operating mode of the target MCU system.

The custom serial protocol requires the debug pod to know the target BDC communication clock speed.

The clock switch (CLKSW) control bit in the BDC status and control register allows the user to select the BDC clock source. The BDC clock source can either be the bus or the alternate BDC clock source.

The BKGD pin can receive a high or low level or transmit a high or low level. The following diagrams show timing for each of these cases. Interface timing is synchronous to clocks in the target BDC, but asynchronous to the external host. The internal BDC clock signal is shown for reference in counting cycles.