Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | S08                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 40MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                                     |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 16                                                                     |

| Program Memory Size        | 16KB (16K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 256 x 8                                                                |

| RAM Size                   | 512 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | A/D 12x10b                                                             |

| Oscillator Type            | External                                                               |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 20-TSSOP (0.173", 4.40mm Width)                                        |

| Supplier Device Package    | 20-TSSOP                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s08sl16f1mtj |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **List of Chapters**

\_\_\_\_\_

| Chapter 1  | Device Overview                                | 19  |

|------------|------------------------------------------------|-----|

| Chapter 2  | Pins and Connections                           | 25  |

| Chapter 3  | Modes of Operation                             |     |

| Chapter 4  | Memory                                         |     |

| Chapter 5  | Resets, Interrupts, and General System Control | 63  |

| Chapter 6  | Parallel Input/Output Control                  | 79  |

| Chapter 7  | Central Processor Unit (S08CPUV3)              | 95  |

| Chapter 8  | Internal Clock Source (S08ICSV2)               | 115 |

| Chapter 9  | 5-V Analog Comparator (S08ACMPV2)              | 129 |

| Chapter 10 | Analog-to-Digital Converter (S08ADCV1)         |     |

| Chapter 11 | Inter-Integrated Circuit (S08IICV2)            | 165 |

| Chapter 12 | Slave LIN Interface Controller (S08SLICV1)     |     |

| Chapter 13 | Serial Peripheral Interface (S08SPIV3)         | 233 |

| Chapter 14 | Serial Communications Interface (S08SCIV4)     | 249 |

| Chapter 15 | Real-Time Counter (S08RTCV1)                   |     |

| Chapter 16 | Timer Pulse-Width Modulator (S08TPMV2)         | 279 |

| Chapter 17 | Development Support                            |     |

| Appendix A | Electrical Characteristics                     |     |

| Appendix B | Ordering Information and Mechanical Drawings   |     |

# **Section Number**

### Title

### Page

|      | 10.3.6 Compare Value Low Register (ADCCVL) | 147 |

|------|--------------------------------------------|-----|

|      | 10.3.7 Configuration Register (ADCCFG)     |     |

|      | 10.3.8 Pin Control 1 Register (APCTL1)     |     |

|      | 10.3.9 Pin Control 2 Register (APCTL2)     |     |

|      | 10.3.10Pin Control 3 Register (APCTL3)     |     |

| 10.4 | Functional Description                     |     |

|      | 10.4.1 Clock Select and Divide Control     | 152 |

|      | 10.4.2 Input Select and Pin Control        | 153 |

|      | 10.4.3 Hardware Trigger                    | 153 |

|      | 10.4.4 Conversion Control                  | 153 |

|      | 10.4.5 Automatic Compare Function          | 156 |

|      | 10.4.6 MCU Wait Mode Operation             | 156 |

|      | 10.4.7 MCU Stop3 Mode Operation            | 156 |

|      | 10.4.8 MCU Stop1 and Stop2 Mode Operation  | 157 |

| 10.5 | Initialization Information                 | 157 |

|      | 10.5.1 ADC Module Initialization Example   | 157 |

| 10.6 | Application Information                    | 159 |

|      | 10.6.1 External Pins and Routing           | 159 |

|      | 10.6.2 Sources of Error                    |     |

# Chapter 11 Inter-Integrated Circuit (S08IICV2)

| 11.1 | Introduc | ction                                 | .165 |

|------|----------|---------------------------------------|------|

|      | 11.1.1   | Module Configuration                  | .165 |

|      | 11.1.2   | Features                              | .167 |

|      | 11.1.3   | Modes of Operation                    | .167 |

|      | 11.1.4   | Block Diagram                         | .168 |

| 11.2 | Externa  | l Signal Description                  | .168 |

|      | 11.2.1   | SCL — Serial Clock Line               | .168 |

|      | 11.2.2   | SDA — Serial Data Line                | .168 |

| 11.3 | Register | Definition                            | .168 |

|      | 11.3.1   | IIC Address Register (IICA)           | .169 |

|      | 11.3.2   | IIC Frequency Divider Register (IICF) | .169 |

|      | 11.3.3   | IIC Control Register (IICC1)          | .172 |

|      | 11.3.4   | IIC Status Register (IICS)            | .172 |

|      | 11.3.5   | IIC Data I/O Register (IICD)          | .173 |

|      | 11.3.6   | IIC Control Register 2 (IICC2)        | .174 |

| 11.4 | Function | nal Description                       | .175 |

|      | 11.4.1   | IIC Protocol                          | .175 |

|      | 11.4.2   | 10-bit Address                        | .178 |

|      | 11.4.3   | General Call Address                  | .179 |

| 11.5 | Resets   |                                       | .179 |

|      |          |                                       |      |

# **Section Number**

Title

| 11.6 | Interrupts                             |  |

|------|----------------------------------------|--|

|      | 11.6.1 Byte Transfer Interrupt         |  |

|      | 11.6.2 Address Detect Interrupt        |  |

|      | 11.6.3 Arbitration Lost Interrupt      |  |

| 11.7 | Initialization/Application Information |  |

# Chapter 12 Slave LIN Interface Controller (S08SLICV1)

| 12.1 | Introduction                                                   |  |

|------|----------------------------------------------------------------|--|

|      | 12.1.1 Features                                                |  |

|      | 12.1.2 Modes of Operation                                      |  |

|      | 12.1.3 Block Diagram                                           |  |

| 12.2 | External Signal Description                                    |  |

|      | 12.2.1 SLCTx — SLIC Transmit Pin                               |  |

|      | 12.2.2 SLCRx — SLIC Receive Pin                                |  |

| 12.3 | Register Definition                                            |  |

|      | 12.3.1 SLIC Control Register 1 (SLCC1)                         |  |

|      | 12.3.2 SLIC Control Register 2 (SLCC2)                         |  |

|      | 12.3.3 SLIC Bit Time Registers (SLCBTH, SLCBTL)                |  |

|      | 12.3.4 SLIC Status Register (SLCS)                             |  |

|      | 12.3.5 SLIC State Vector Register (SLCSV)                      |  |

|      | 12.3.6 SLIC Data Length Code Register (SLCDLC)                 |  |

|      | 12.3.7 SLIC Identifier and Data Registers (SLCID, SLCD7-SLCD0) |  |

| 12.4 | Functional Description                                         |  |

| 12.5 | Interrupts                                                     |  |

|      | 12.5.1 SLIC During Break Interrupts                            |  |

| 12.6 | Initialization/Application Information                         |  |

|      | 12.6.1 LIN Message Frame Header                                |  |

|      | 12.6.2 LIN Data Field                                          |  |

|      | 12.6.3 LIN Checksum Field                                      |  |

|      | 12.6.4 SLIC Module Constraints                                 |  |

|      | 12.6.5 SLCSV Interrupt Handling                                |  |

|      | 12.6.6 SLIC Module Initialization Procedure                    |  |

|      | 12.6.7 Handling LIN Message Headers                            |  |

|      | 12.6.8 Handling Command Message Frames                         |  |

|      | 12.6.9 Handling Request LIN Message Frames                     |  |

|      | 12.6.10Handling IMSG to Minimize Interrupts                    |  |

|      | 12.6.11Sleep and Wakeup Operation                              |  |

|      | 12.6.12Polling Operation                                       |  |

|      | 12.6.13LIN Data Integrity Checking Methods                     |  |

|      | 12.6.14High-Speed LIN Operation                                |  |

|      | 12.6.15Bit Error Detection and Physical Layer Delay            |  |

# **Section Number**

Title

### Page

| 14.3 | Functional Description                    |  |

|------|-------------------------------------------|--|

|      | 14.3.1 Baud Rate Generation               |  |

|      | 14.3.2 Transmitter Functional Description |  |

|      | 14.3.3 Receiver Functional Description    |  |

|      | 14.3.4 Interrupts and Status Flags        |  |

|      | 14.3.5 Additional SCI Functions           |  |

# Chapter 15 Real-Time Counter (S08RTCV1)

| Introduction                                   |                                                                                                                                                                                                                                                                                                                                                                        |

|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15.1.1 Features                                |                                                                                                                                                                                                                                                                                                                                                                        |

| 15.1.2 Modes of Operation                      |                                                                                                                                                                                                                                                                                                                                                                        |

| 15.1.3 Block Diagram                           |                                                                                                                                                                                                                                                                                                                                                                        |

| External Signal Description                    |                                                                                                                                                                                                                                                                                                                                                                        |

| Register Definition                            |                                                                                                                                                                                                                                                                                                                                                                        |

| 15.3.1 RTC Status and Control Register (RTCSC) |                                                                                                                                                                                                                                                                                                                                                                        |

| 15.3.2 RTC Counter Register (RTCCNT)           |                                                                                                                                                                                                                                                                                                                                                                        |

| 15.3.3 RTC Modulo Register (RTCMOD)            |                                                                                                                                                                                                                                                                                                                                                                        |

| Functional Description                         |                                                                                                                                                                                                                                                                                                                                                                        |

| 15.4.1 RTC Operation Example                   |                                                                                                                                                                                                                                                                                                                                                                        |

| Initialization/Application Information         |                                                                                                                                                                                                                                                                                                                                                                        |

|                                                | <ul> <li>15.1.2 Modes of Operation</li> <li>15.1.3 Block Diagram</li> <li>External Signal Description</li> <li>Register Definition</li> <li>15.3.1 RTC Status and Control Register (RTCSC)</li> <li>15.3.2 RTC Counter Register (RTCCNT)</li> <li>15.3.3 RTC Modulo Register (RTCMOD)</li> <li>Functional Description</li> <li>15.4.1 RTC Operation Example</li> </ul> |

# Chapter 16 Timer Pulse-Width Modulator (S08TPMV2)

| 16.1 | Introduction                                                |  |

|------|-------------------------------------------------------------|--|

|      | 16.1.1 Features                                             |  |

|      | 16.1.2 Modes of Operation                                   |  |

|      | 16.1.3 Block Diagram                                        |  |

| 16.2 | Signal Description                                          |  |

|      | 16.2.1 Detailed Signal Descriptions                         |  |

| 16.3 | Register Definition                                         |  |

|      | 16.3.1 TPM Status and Control Register (TPMxSC)             |  |

|      | 16.3.2 TPM-Counter Registers (TPMxCNTH:TPMxCNTL)            |  |

|      | 16.3.3 TPM Counter Modulo Registers (TPMxMODH:TPMxMODL)     |  |

|      | 16.3.4 TPM Channel n Status and Control Register (TPMxCnSC) |  |

|      | 16.3.5 TPM Channel Value Registers (TPMxCnVH:TPMxCnVL)      |  |

| 16.4 | Functional Description                                      |  |

|      | 16.4.1 Counter                                              |  |

|      | 16.4.2 Channel Mode Selection                               |  |

| 16.5 | Reset Overview                                              |  |

|      | 16.5.1 General                                              |  |

|      | 16.5.2 Description of Reset Operation                       |  |

|      |                                                             |  |

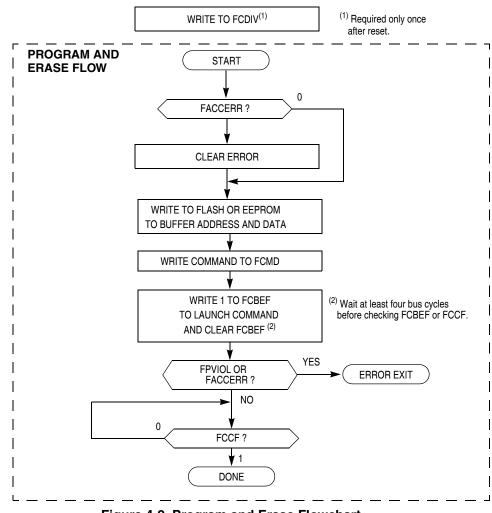

#### Figure 4-2. Program and Erase Flowchart

### 4.5.4 Burst Program Execution

The burst program command is used to program sequential bytes of data in less time than would be required using the standard program command. This is possible because the high voltage to the FLASH array does not need to be disabled between program operations. Ordinarily, when a program or erase command is issued, an internal charge pump associated with the FLASH memory must be enabled to supply high voltage to the array. Upon completion of the command, the charge pump is turned off. When a burst program command is issued, the charge pump is enabled and then remains enabled after completion of the burst program operation if these two conditions are met:

- The next burst program command has been queued before the current program operation has completed.

- The next sequential address selects a byte on the same burst block as the current byte being programmed. A burst block in this FLASH memory consists of 64 bytes. A new burst block begins at each 64-byte address boundary.

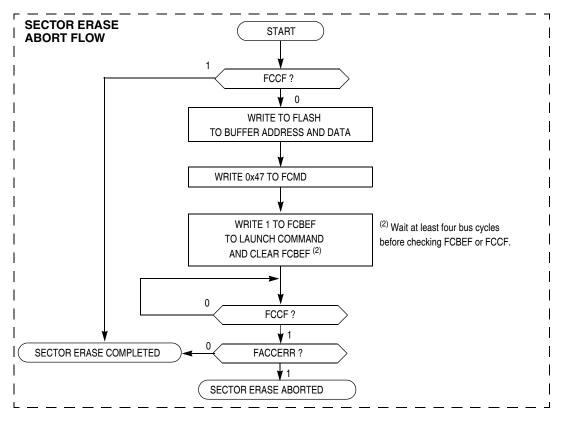

#### 4.5.5 Sector Erase Abort

The sector erase abort operation will terminate the active sector erase operation so that other sectors are available for read and program operations without waiting for the sector erase operation to complete.

The sector erase abort command write sequence is as follows:

- 1. Write to any FLASH or EEPROM address to start the command write sequence for the sector erase abort command. The address and data written are ignored.

- 2. Write the sector erase abort command, 0x47, to the FCMD register.

- 3. Clear the FCBEF flag in the FSTAT register by writing a "1" to FCBEF to launch the sector erase abort command.

If the sector erase abort command is launched resulting in the early termination of an active sector erase operation, the FACCERR flag will set once the operation completes as indicated by the FCCF flag being set. The FACCERR flag sets to inform the user that the FLASH sector may not be fully erased and a new sector erase command must be launched before programming any location in that specific sector.

If the sector erase abort command is launched but the active sector erase operation completes normally, the FACCERR flag will not set upon completion of the operation as indicated by the FCCF flag being set. Therefore, if the FACCERR flag is not set after the sector erase abort command has completed, a sector being erased when the abort command was launched will be fully erased.

A flowchart to execute the sector erase abort operation is shown in Figure 4-4.

Figure 4-4. Sector Erase Abort Flowchart

| FPS  | FPOPEN | Address Area<br>Protected | Memory Size<br>Protected (bytes) | Number of Sectors<br>Protected |

|------|--------|---------------------------|----------------------------------|--------------------------------|

| 0x1F |        | N/A                       | 0                                | 0                              |

| 0x1E |        | 0xFC00-0xFFFF             | 1K                               | 2                              |

| 0x1D |        | 0xF800-0xFFFF             | 2K                               | 4                              |

| 0x1C |        | 0xF400-0xFFFF             | ЗК                               | 6                              |

| 0x1B |        | 0xF000-0xFFFF             | 4K                               | 8                              |

| 0x1A |        | 0xEC00-0xFFFF             | 5K                               | 10                             |

| 0x19 |        | 0xE800-0xFFFF             | 6K                               | 12                             |

| 0x18 |        | 0xE400-0xFFFF             | 7K                               | 14                             |

| 0x17 | - 1    | 0xE000-0xFFFF             | 8K                               | 16                             |

|      |        |                           |                                  | 18                             |

| 0x07 |        | 0xA000-0xFFFF             | 24K                              | 48                             |

| 0x06 |        | 0x9C00-0xFFFF             | 25K                              | 50                             |

| 0x05 |        | 0x9800-0xFFFF             | 26K                              | 52                             |

| 0x04 |        | 0x9400-0xFFFF             | 27K                              | 54                             |

| 0x03 |        | 0x9000-0xFFFF             | 28K                              | 56                             |

| 0x02 |        | 0x8C00-0xFFFF             | 29K                              | 58                             |

| 0x01 |        | 0x8800-0xFFFF             | 30K                              | 60                             |

| 0x00 |        | 0x8400-0xFFFF             | 31K                              | 62                             |

| N/A  | 0      | 0x8000-0xFFFF             | 32K                              | 64                             |

#### Table 4-13. FLASH Block Protection

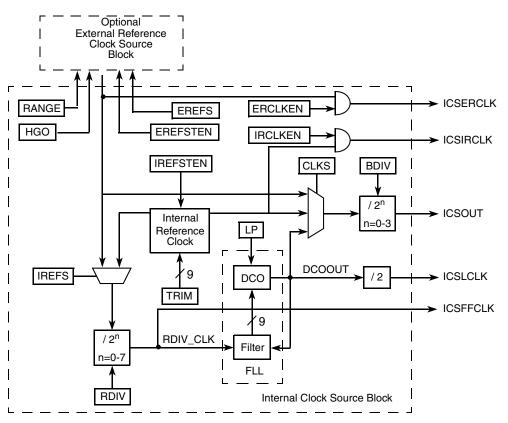

Internal Clock Source (S08ICSV2)

Figure 8-2. Internal Clock Source (ICS) Block Diagram

### 8.1.4 Modes of Operation

There are seven modes of operation for the ICS: FEI, FEE, FBI, FBILP, FBE, FBELP, and stop.

### 8.1.4.1 FLL Engaged Internal (FEI)

In FLL engaged internal mode, which is the default mode, the ICS supplies a clock derived from the FLL which is controlled by the internal reference clock. The BDC clock is supplied from the FLL.

### 8.1.4.2 FLL Engaged External (FEE)

In FLL engaged external mode, the ICS supplies a clock derived from the FLL which is controlled by an external reference clock. The BDC clock is supplied from the FLL.

### 8.1.4.3 FLL Bypassed Internal (FBI)

In FLL bypassed internal mode, the FLL is enabled and controlled by the internal reference clock, but is bypassed. The ICS supplies a clock derived from the internal reference clock. The BDC clock is supplied from the FLL.

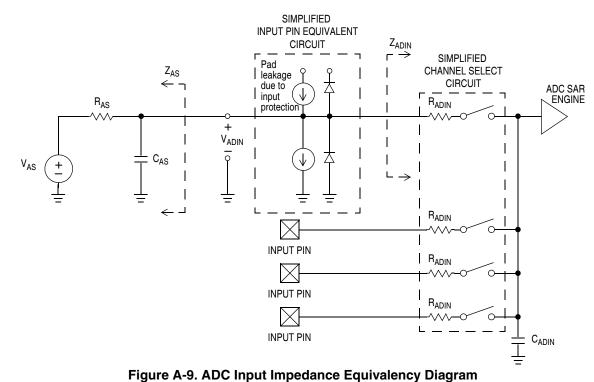

# 10.2.1 Analog Power (V<sub>DDAD</sub>)

The ADC analog portion uses  $V_{DDAD}$  as its power connection. In some packages,  $V_{DDAD}$  is connected internally to  $V_{DD}$ . If externally available, connect the  $V_{DDAD}$  pin to the same voltage potential as  $V_{DD}$ . External filtering may be necessary to ensure clean  $V_{DDAD}$  for good results.

# 10.2.2 Analog Ground (V<sub>SSAD</sub>)

The ADC analog portion uses  $V_{SSAD}$  as its ground connection. In some packages,  $V_{SSAD}$  is connected internally to  $V_{SS}$ . If externally available, connect the  $V_{SSAD}$  pin to the same voltage potential as  $V_{SS}$ .

# 10.2.3 Voltage Reference High (V<sub>REFH</sub>)

$V_{REFH}$  is the high reference voltage for the converter. In some packages,  $V_{REFH}$  is connected internally to  $V_{DDAD}$ . If externally available,  $V_{REFH}$  may be connected to the same potential as  $V_{DDAD}$ , or may be driven by an external source that is between the minimum  $V_{DDAD}$  spec and the  $V_{DDAD}$  potential ( $V_{REFH}$  must never exceed  $V_{DDAD}$ ).

# 10.2.4 Voltage Reference Low (V<sub>REFL</sub>)

$V_{REFL}$  is the low reference voltage for the converter. In some packages,  $V_{REFL}$  is connected internally to  $V_{SSAD}$ . If externally available, connect the  $V_{REFL}$  pin to the same voltage potential as  $V_{SSAD}$ .

### 10.2.5 Analog Channel Inputs (ADx)

The ADC module supports up to 28 separate analog inputs. An input is selected for conversion through the ADCH channel select bits.

# **10.3 Register Definition**

These memory mapped registers control and monitor operation of the ADC:

- Status and control register, ADCSC1

- Status and control register, ADCSC2

- Data result registers, ADCRH and ADCRL

- Compare value registers, ADCCVH and ADCCVL

- Configuration register, ADCCFG

- Pin enable registers, APCTL1, APCTL2, APCTL3

# 10.3.1 Status and Control Register 1 (ADCSC1)

This section describes the function of the ADC status and control register (ADCSC1). Writing ADCSC1 aborts the current conversion and initiates a new conversion (if the ADCH bits are equal to a value other than all 1s).

# Chapter 11 Inter-Integrated Circuit (S08IICV2)

# 11.1 Introduction

The inter-integrated circuit (IIC) provides a method of communication between a number of devices. The interface is designed to operate up to 100 kbps with maximum bus loading and timing. The device is capable of operating at higher baud rates, up to a maximum of clock/20, with reduced bus loading. The maximum communication length and the number of devices that can be connected are limited by a maximum bus capacitance of 400 pF.

#### NOTE

The SDA and SCL should not be driven above  $V_{DD}$ . These pins are pseudo-open-drain containing a protection diode to  $V_{DD}$ .

### 11.1.1 Module Configuration

The IIC module pins, SDA and SCL, can be repositioned under software control using IICPS in SOPT1, as as shown in Table 11-1. This bit selects which general-purpose I/O ports are associated with IIC operation.

| SOPT1[IICPS] | Port Pin for SDA | Port Pin for SCL |

|--------------|------------------|------------------|

| 0 (default   | PTA2             | PTA3             |

| 1            | PTB6             | PTB7             |

#### Table 11-1. IIC Position Options

Figure 11-1 shows the MC9S08EL32 Series and MC9S08SL16 Series block diagram with the IIC module highlighted.

#### Table 13-3. SPIC2 Register Field Descriptions

| Field        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4<br>MODFEN  | Master Mode-Fault Function Enable — When the SPI is configured for slave mode, this bit has no meaning or<br>effect. (The SS pin is the slave select input.) In master mode, this bit determines how the SS pin is used (refer to<br>Table 13-2 for more details).0Mode fault function disabled, master SS pin reverts to general-purpose I/O not controlled by SPI<br>11Mode fault function enabled, master SS pin acts as the mode fault input or the slave select output                                                                                  |

| 3<br>BIDIROE | <b>Bidirectional Mode Output Enable</b> — When bidirectional mode is enabled by SPI pin control 0 (SPC0) = 1,<br>BIDIROE determines whether the SPI data output driver is enabled to the single bidirectional SPI I/O pin.<br>Depending on whether the SPI is configured as a master or a slave, it uses either the MOSI (MOMI) or MISO<br>(SISO) pin, respectively, as the single SPI data I/O pin. When SPC0 = 0, BIDIROE has no meaning or effect.<br>0 Output driver disabled so SPI data I/O pin acts as an input<br>1 SPI I/O pin enabled as an output |

| 1<br>SPISWAI | SPI Stop in Wait Mode         0 SPI clocks continue to operate in wait mode         1 SPI clocks stop when the MCU enters wait mode                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 0<br>SPC0    | <b>SPI Pin Control 0</b> — The SPC0 bit chooses single-wire bidirectional mode. If MSTR = 0 (slave mode), the SPI uses the MISO (SISO) pin for bidirectional SPI data transfers. If MSTR = 1 (master mode), the SPI uses the MOSI (MOMI) pin for bidirectional SPI data transfers. When SPC0 = 1, BIDIROE is used to enable or disable the output driver for the single bidirectional SPI I/O pin.<br>0 SPI uses separate pins for data input and data output<br>1 SPI configured for single-wire bidirectional operation                                    |

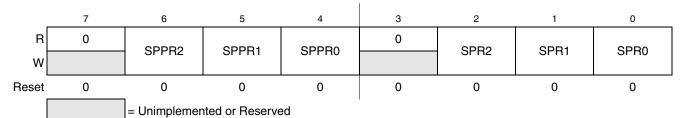

### 13.4.3 SPI Baud Rate Register (SPIBR)

This register is used to set the prescaler and bit rate divisor for an SPI master. This register may be read or written at any time.

Figure 13-7. SPI Baud Rate Register (SPIBR)

#### Table 13-4. SPIBR Register Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                              |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6:4<br>SPPR[2:0] | <b>SPI Baud Rate Prescale Divisor</b> — This 3-bit field selects one of eight divisors for the SPI baud rate prescaler as shown in Table 13-5. The input to this prescaler is the bus rate clock (BUSCLK). The output of this prescaler drives the input of the SPI baud rate divider (see Figure 13-4). |

| 2:0<br>SPR[2:0]  | <b>SPI Baud Rate Divisor</b> — This 3-bit field selects one of eight divisors for the SPI baud rate divider as shown in Table 13-6. The input to this divider comes from the SPI baud rate prescaler (see Figure 13-4). The output of this divider is the SPI bit rate clock for master mode.            |

| Field                   | Description                                                                                                                                                                                                                                      |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4<br>TXINV <sup>1</sup> | Transmit Data Inversion — Setting this bit reverses the polarity of the transmitted data output.0011Transmit data inverted                                                                                                                       |

| 3<br>ORIE               | <ul> <li>Overrun Interrupt Enable — This bit enables the overrun flag (OR) to generate hardware interrupt requests.</li> <li>O OR interrupts disabled (use polling).</li> <li>1 Hardware interrupt requested when OR = 1.</li> </ul>             |

| 2<br>NEIE               | <ul> <li>Noise Error Interrupt Enable — This bit enables the noise flag (NF) to generate hardware interrupt requests.</li> <li>0 NF interrupts disabled (use polling).</li> <li>1 Hardware interrupt requested when NF = 1.</li> </ul>           |

| 1<br>FEIE               | <ul> <li>Framing Error Interrupt Enable — This bit enables the framing error flag (FE) to generate hardware interrupt requests.</li> <li>0 FE interrupts disabled (use polling).</li> <li>1 Hardware interrupt requested when FE = 1.</li> </ul> |

| 0<br>PEIE               | <ul> <li>Parity Error Interrupt Enable — This bit enables the parity error flag (PF) to generate hardware interrupt requests.</li> <li>0 PF interrupts disabled (use polling).</li> <li>1 Hardware interrupt requested when PF = 1.</li> </ul>   |

#### Table 14-7. SCIxC3 Field Descriptions (continued)

Setting TXINV inverts the TxD output for all cases: data bits, start and stop bits, break, and idle.

### 14.2.7 SCI Data Register (SCIxD)

This register is actually two separate registers. Reads return the contents of the read-only receive data buffer and writes go to the write-only transmit data buffer. Reads and writes of this register are also involved in the automatic flag clearing mechanisms for the SCI status flags.

|       | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|-------|----|----|----|----|----|----|----|----|

| R     | R7 | R6 | R5 | R4 | R3 | R2 | R1 | R0 |

| w     | T7 | Т6 | T5 | T4 | Т3 | T2 | T1 | Т0 |

| Reset | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

Figure 14-11. SCI Data Register (SCIxD)

# 14.3 Functional Description

The SCI allows full-duplex, asynchronous, NRZ serial communication among the MCU and remote devices, including other MCUs. The SCI comprises a baud rate generator, transmitter, and receiver block. The transmitter and receiver operate independently, although they use the same baud rate generator. During normal operation, the MCU monitors the status of the SCI, writes the data to be transmitted, and processes received data. The following describes each of the blocks of the SCI.

#### 14.3.1 Baud Rate Generation

As shown in Figure 14-12, the clock source for the SCI baud rate generator is the bus-rate clock.

#### Serial Communications Interface (S08SCIV4)

status flag is set. If RDRF was already set indicating the receive data register (buffer) was already full, the overrun (OR) status flag is set and the new data is lost. Because the SCI receiver is double-buffered, the program has one full character time after RDRF is set before the data in the receive data buffer must be read to avoid a receiver overrun.

When a program detects that the receive data register is full (RDRF = 1), it gets the data from the receive data register by reading SCIxD. The RDRF flag is cleared automatically by a 2-step sequence which is normally satisfied in the course of the user's program that handles receive data. Refer to Section 14.3.4, "Interrupts and Status Flags" for more details about flag clearing.

#### 14.3.3.1 Data Sampling Technique

The SCI receiver uses a 16× baud rate clock for sampling. The receiver starts by taking logic level samples at 16 times the baud rate to search for a falling edge on the RxD serial data input pin. A falling edge is defined as a logic 0 sample after three consecutive logic 1 samples. The 16× baud rate clock is used to divide the bit time into 16 segments labeled RT1 through RT16. When a falling edge is located, three more samples are taken at RT3, RT5, and RT7 to make sure this was a real start bit and not merely noise. If at least two of these three samples are 0, the receiver assumes it is synchronized to a receive character.

The receiver then samples each bit time, including the start and stop bits, at RT8, RT9, and RT10 to determine the logic level for that bit. The logic level is interpreted to be that of the majority of the samples taken during the bit time. In the case of the start bit, the bit is assumed to be 0 if at least two of the samples at RT3, RT5, and RT7 are 0 even if one or all of the samples taken at RT8, RT9, and RT10 are 1s. If any sample in any bit time (including the start and stop bits) in a character frame fails to agree with the logic level for that bit, the noise flag (NF) will be set when the received character is transferred to the receive data buffer.

The falling edge detection logic continuously looks for falling edges, and if an edge is detected, the sample clock is resynchronized to bit times. This improves the reliability of the receiver in the presence of noise or mismatched baud rates. It does not improve worst case analysis because some characters do not have any extra falling edges anywhere in the character frame.

In the case of a framing error, provided the received character was not a break character, the sampling logic that searches for a falling edge is filled with three logic 1 samples so that a new start bit can be detected almost immediately.

In the case of a framing error, the receiver is inhibited from receiving any new characters until the framing error flag is cleared. The receive shift register continues to function, but a complete character cannot transfer to the receive data buffer if FE is still set.

#### 14.3.3.2 Receiver Wakeup Operation

Receiver wakeup is a hardware mechanism that allows an SCI receiver to ignore the characters in a message that is intended for a different SCI receiver. In such a system, all receivers evaluate the first character(s) of each message, and as soon as they determine the message is intended for a different receiver, they write logic 1 to the receiver wake up (RWU) control bit in SCIxC2. When RWU bit is set, the status flags associated with the receiver (with the exception of the idle bit, IDLE, when RWUID bit is set) are inhibited from setting, thus eliminating the software overhead for handling the unimportant

message characters. At the end of a message, or at the beginning of the next message, all receivers automatically force RWU to 0 so all receivers wake up in time to look at the first character(s) of the next message.

#### 14.3.3.2.1 Idle-Line Wakeup

When WAKE = 0, the receiver is configured for idle-line wakeup. In this mode, RWU is cleared automatically when the receiver detects a full character time of the idle-line level. The M control bit selects 8-bit or 9-bit data mode that determines how many bit times of idle are needed to constitute a full character time (10 or 11 bit times because of the start and stop bits).

When RWU is one and RWUID is zero, the idle condition that wakes up the receiver does not set the IDLE flag. The receiver wakes up and waits for the first data character of the next message which will set the RDRF flag and generate an interrupt if enabled. When RWUID is one, any idle condition sets the IDLE flag and generates an interrupt if enabled, regardless of whether RWU is zero or one.

The idle-line type (ILT) control bit selects one of two ways to detect an idle line. When ILT = 0, the idle bit counter starts after the start bit so the stop bit and any logic 1s at the end of a character count toward the full character time of idle. When ILT = 1, the idle bit counter does not start until after a stop bit time, so the idle detection is not affected by the data in the last character of the previous message.

#### 14.3.3.2.2 Address-Mark Wakeup

When WAKE = 1, the receiver is configured for address-mark wakeup. In this mode, RWU is cleared automatically when the receiver detects a logic 1 in the most significant bit of a received character (eighth bit in M = 0 mode and ninth bit in M = 1 mode).

Address-mark wakeup allows messages to contain idle characters but requires that the MSB be reserved for use in address frames. The logic 1 MSB of an address frame clears the RWU bit before the stop bit is received and sets the RDRF flag. In this case the character with the MSB set is received even though the receiver was sleeping during most of this character time.

# 14.3.4 Interrupts and Status Flags

The SCI system has three separate interrupt vectors to reduce the amount of software needed to isolate the cause of the interrupt. One interrupt vector is associated with the transmitter for TDRE and TC events. Another interrupt vector is associated with the receiver for RDRF, IDLE, RXEDGIF and LBKDIF events, and a third vector is used for OR, NF, FE, and PF error conditions. Each of these ten interrupt sources can be separately masked by local interrupt enable masks. The flags can still be polled by software when the local masks are cleared to disable generation of hardware interrupt requests.

The SCI transmitter has two status flags that optionally can generate hardware interrupt requests. Transmit data register empty (TDRE) indicates when there is room in the transmit data buffer to write another transmit character to SCIxD. If the transmit interrupt enable (TIE) bit is set, a hardware interrupt will be requested whenever TDRE = 1. Transmit complete (TC) indicates that the transmitter is finished transmitting all data, preamble, and break characters and is idle with TxD at the inactive level. This flag is often used in systems with modems to determine when it is safe to turn off the modem. If the transmit complete interrupt enable (TCIE) bit is set, a hardware interrupt will be requested whenever TC = 1.

{

#### Real-Time Counter (S08RTCV1)

```

#pragma TRAP_PROC

void RTC_ISR(void)

/* Clear the interrupt flag */

RTCSC.byte = RTCSC.byte | 0x80;

/* RTC interrupts every 1 Second */

Seconds++;

/* 60 seconds in a minute */

if (Seconds > 59)

Minutes++;

Seconds = 0;

}

/* 60 minutes in an hour */

if (Minutes > 59) {

Hours++;

Minutes = 0;

}

/* 24 hours in a day */

if (Hours > 23) {

Days ++;

Hours = 0;

}

```

# Chapter 16 Timer Pulse-Width Modulator (S08TPMV2)

# 16.1 Introduction

The TPM uses one input/output (I/O) pin per channel, TPMxCHn where x is the TPM number (for example, 1 or 2) and n is the channel number (for example, 0–4). The TPM shares its I/O pins with general-purpose I/O port pins (refer to the Pins and Connections chapter for more information).

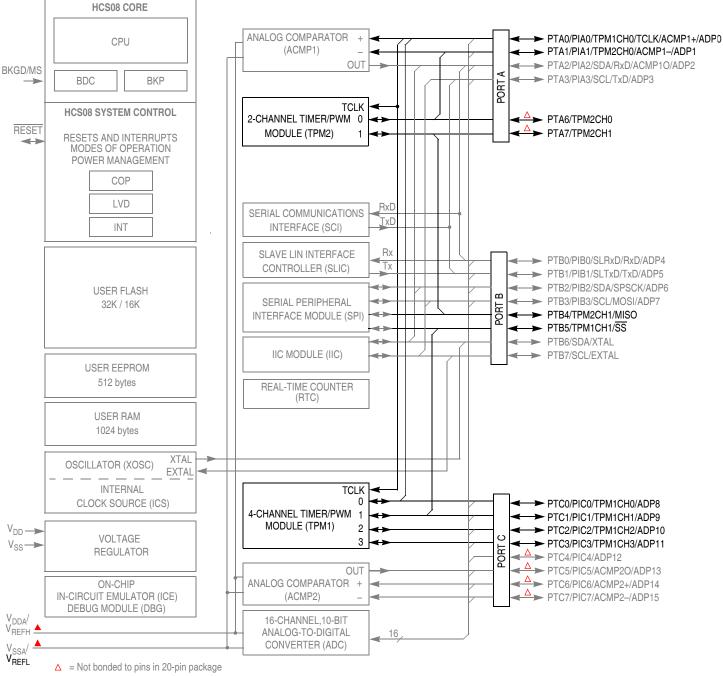

All MC9S08EL32 Series and MC9S08SL16 Series MCUs have two TPM modules. In all packages, TPM2 is 2-channel. The number of channels available in TPM1 depends on the device, as shown in Table 16-1:

| Feature       | 9S08  | EL32  | 9508  | EL16  | 9S08  | SL16  | 9508  | BSL8  |

|---------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Pin quantity  | 28    | 20    | 28    | 20    | 28    | 20    | 28    | 20    |

| Package type  | TSSOP |

| TPM1 channels |       |       | 4     |       |       | 2     | 2     |       |

| TPM2 channels |       | 2     | 2     |       |       | 2     | 2     |       |

Table 16-1. MC9S08EL32 Series and MC9S08SL16 Series Features by MCU and Package

Chapter 16 Timer Pulse-Width Modulator (S08TPMV2)

Figure 16-1. MC9S08EL32 Block Diagram Highlighting TPM Block and Pins

# 17.3 On-Chip Debug System (DBG)

Because HCS08 devices do not have external address and data buses, the most important functions of an in-circuit emulator have been built onto the chip with the MCU. The debug system consists of an 8-stage FIFO that can store address or data bus information, and a flexible trigger system to decide when to capture bus information and what information to capture. The system relies on the single-wire background debug system to access debug control registers and to read results out of the eight stage FIFO.

The debug module includes control and status registers that are accessible in the user's memory map. These registers are located in the high register space to avoid using valuable direct page memory space.

Most of the debug module's functions are used during development, and user programs rarely access any of the control and status registers for the debug module. The one exception is that the debug system can provide the means to implement a form of ROM patching. This topic is discussed in greater detail in Section 17.3.6, "Hardware Breakpoints."

### 17.3.1 Comparators A and B

Two 16-bit comparators (A and B) can optionally be qualified with the R/W signal and an opcode tracking circuit. Separate control bits allow you to ignore R/W for each comparator. The opcode tracking circuitry optionally allows you to specify that a trigger will occur only if the opcode at the specified address is actually executed as opposed to only being read from memory into the instruction queue. The comparators are also capable of magnitude comparisons to support the inside range and outside range trigger modes. Comparators are disabled temporarily during all BDC accesses.

The A comparator is always associated with the 16-bit CPU address. The B comparator compares to the CPU address or the 8-bit CPU data bus, depending on the trigger mode selected. Because the CPU data bus is separated into a read data bus and a write data bus, the RWAEN and RWA control bits have an additional purpose, in full address plus data comparisons they are used to decide which of these buses to use in the comparator B data bus comparisons. If RWAEN = 1 (enabled) and RWA = 0 (write), the CPU's write data bus is used. Otherwise, the CPU's read data bus is used.

The currently selected trigger mode determines what the debugger logic does when a comparator detects a qualified match condition. A match can cause:

- Generation of a breakpoint to the CPU

- Storage of data bus values into the FIFO

- Starting to store change-of-flow addresses into the FIFO (begin type trace)

- Stopping the storage of change-of-flow addresses into the FIFO (end type trace)

### 17.3.2 Bus Capture Information and FIFO Operation

The usual way to use the FIFO is to setup the trigger mode and other control options, then arm the debugger. When the FIFO has filled or the debugger has stopped storing data into the FIFO, you would read the information out of it in the order it was stored into the FIFO. Status bits indicate the number of words of valid information that are in the FIFO as data is stored into it. If a trace run is manually halted by writing 0 to ARM before the FIFO is full (CNT = 1:0:0:0), the information is shifted by one position and

| Characteristic               | Conditions                    | С | Symb                                   | Min  | Typ <sup>1</sup> | Max | Unit | Comment              |

|------------------------------|-------------------------------|---|----------------------------------------|------|------------------|-----|------|----------------------|

|                              | ADLPC=1<br>ADLSMP=1<br>ADCO=1 | Т | I <sub>DD</sub> +<br>I <sub>DDAD</sub> | _    | 133              | _   | μΑ   | ADC current<br>only  |

| Supply ourrent               | ADLPC=1<br>ADLSMP=0<br>ADCO=1 | Т | I <sub>DD</sub> +<br>I <sub>DDAD</sub> | _    | 218              | _   | μA   | ADC current<br>only  |

| Supply current               | ADLPC=0<br>ADLSMP=1<br>ADCO=1 | Т | I <sub>DD</sub> +<br>I <sub>DDAD</sub> | _    | 327              | _   | μΑ   | ADC current<br>only  |

|                              | ADLPC=0<br>ADLSMP=0<br>ADCO=1 | Ρ | I <sub>DD</sub> +<br>I <sub>DDAD</sub> |      | 0.582            | 1   | mA   | ADC current<br>only  |

| ADC                          | High speed (ADLPC=0)          | Р | f <sub>ADACK</sub>                     | 2    | 3.3              | 5   | MHz  | t <sub>ADACK</sub> = |

| asynchronous<br>clock source | Low power (ADLPC=1)           |   |                                        | 1.25 | 2                | 3.3 |      | 1/f <sub>ADACK</sub> |

|--|