# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                              |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | S08                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 40MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                                    |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 22                                                                    |

| Program Memory Size        | 8KB (8K x 8)                                                          |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 256 x 8                                                               |

| RAM Size                   | 512 x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                           |

| Data Converters            | A/D 16x10b                                                            |

| Oscillator Type            | External                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 28-TSSOP (0.173", 4.40mm Width)                                       |

| Supplier Device Package    | 28-TSSOP                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s08sl8f1ctl |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

**Chapter 2 Pins and Connections**

# 2.2 Recommended System Connections

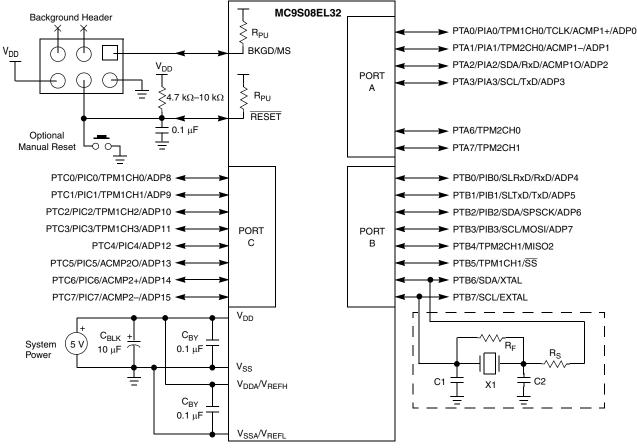

Figure 2-3 shows pin connections that are common to MC9S08EL32 Series and MC9S08SL16 Series application systems.

Figure 2-3. Basic System Connections

# 2.2.1 Power

$V_{DD}$  and  $V_{SS}$  are the primary power supply pins for the MCU. This voltage source supplies power to all I/O buffer circuitry and to an internal voltage regulator. The internal voltage regulator provides a regulated lower-voltage source to the CPU and other internal circuitry of the MCU.

Typically, application systems have two separate capacitors across the power pins. In this case, there should be a bulk electrolytic capacitor, such as a  $10-\mu$ F tantalum capacitor, to provide bulk charge storage for the overall system and a  $0.1-\mu$ F ceramic bypass capacitor located as near to the MCU power pins as practical to suppress high-frequency noise. Each pin must have a bypass capacitor for best noise suppression.

$V_{DDA}$  and  $V_{SSA}$  are the analog power supply pins for the MCU. This voltage source supplies power to the ADC module. A 0.1- $\mu$ F ceramic bypass capacitor should be located as near to the MCU power pins as practical to suppress high-frequency noise. The  $V_{REFH}$  and  $V_{REFL}$  pins are the voltage reference high and voltage reference low inputs, respectively, for the ADC module.

**Chapter 2 Pins and Connections**

### NOTE

In EMC-sensitive applications, use an external RC filter on  $\overline{\text{RESET}}$ . See Figure 2-3 for an example.

# 2.2.4 Background / Mode Select (BKGD/MS)

While in reset, the BKGD/MS pin functions as a mode select pin. Immediately after reset rises, the pin functions as the background pin and can be used for background debug communication. While functioning as a background or mode select pin, the pin includes an internal pull-up device, input hysteresis, a standard output driver, and no output slew rate control.

If nothing is connected to this pin, the MCU will enter normal operating mode at the rising edge of reset. If a debug system is connected to the 6-pin standard background debug header, it can hold BKGD low during the rising edge of reset which forces the MCU to active background mode.

The BKGD/MS pin is used primarily for background debug controller (BDC) communications using a custom protocol that uses 16 clock cycles of the target MCU's BDC clock per bit time. The target MCU's BDC clock could be as fast as the bus clock rate, so there should never be any significant capacitance connected to the BKGD/MS pin that could interfere with background serial communications.

Although the BKGD/MS pin is a pseudo open-drain pin, the background debug communication protocol provides brief, actively driven, high speedup pulses to ensure fast rise times. Small capacitances from cables and the absolute value of the internal pull-up device play almost no role in determining rise and fall times on the BKGD/MS pin.

# 2.2.5 General-Purpose I/O and Peripheral Ports

The MC9S08EL32 Series and MC9S08SL16 Series of MCUs support up to 22 general-purpose I/O pins which are shared with on-chip peripheral functions (timers, serial I/O, ADC, etc.).

When a port pin is configured as a general-purpose output or a peripheral uses the port pin as an output, software can select one of two drive strengths and enable or disable slew rate control. When a port pin is configured as a general-purpose input or a peripheral uses the port pin as an input, software can enable a pull-up device. Immediately after reset, all of these pins are configured as high-impedance general-purpose inputs with internal pull-up devices disabled.

When an on-chip peripheral system is controlling a pin, data direction control bits still determine what is read from port data registers even though the peripheral module controls the pin direction by controlling the enable for the pin's output buffer. For information about controlling these pins as general-purpose I/O pins, see Chapter 6, "Parallel Input/Output Control."

### NOTE

To avoid extra current drain from floating input pins, the reset initialization routine in the application program should either enable on-chip pull-up devices or change the direction of unused or non-bonded pins to outputs so they do not float.

# 4.5 FLASH and EEPROM

The MC9S08EL32 Series and MC9S08SL16 Series includes FLASH and EEPROM memory intended primarily for program and data storage. In-circuit programming allows the operating program and data to be loaded into FLASH and EEPROM, respectively, after final assembly of the application product. It is possible to program the arrays through the single-wire background debug interface. Because no special voltages are needed for erase and programming operations, in-application programming is also possible through other software-controlled communication paths. For a more detailed discussion of in-circuit and in-application programming, refer to the *HCS08 Family Reference Manual, Volume I*, Freescale Semiconductor document order number HCS08RMv1/D.

# 4.5.1 Features

Features of the FLASH and EEPROM memory include:

- Array size

- MC9S08EL32: 32,768 bytes of FLASH, 512 bytes of EEPROM

- MC9S08EL16: 16,384 bytes of FLASH, 512 bytes of EEPROM

- MC9S08SL16: 16,384 bytes of FLASH, 256 bytes of EEPROM

- MC9S08SL8: 8,192 bytes of FLASH, 256 bytes of EEPROM

- Sector size: 512 bytes for FLASH, 8 bytes for EEPROM

- Single power supply program and erase

- Command interface for fast program and erase operation

- Up to 100,000 program/erase cycles at typical voltage and temperature

- Flexible block protection and vector redirection

- Security feature for FLASH, EEPROM, and RAM

# 4.5.2 **Program and Erase Times**

Before any program or erase command can be accepted, the FLASH and EEPROM clock divider register (FCDIV) must be written to set the internal clock for the FLASH and EEPROM module to a frequency ( $f_{FCLK}$ ) between 150 kHz and 200 kHz (see Section 4.5.11.1, "FLASH and EEPROM Clock Divider Register (FCDIV)"). This register can be written only once, so normally this write is performed during reset initialization. FCDIV cannot be written if the access error flag, FACCERR in FSTAT, is set. The user must ensure that FACCERR is not set before writing to the FCDIV register. One period of the resulting clock ( $1/f_{FCLK}$ ) is used by the command processor to time program and erase pulses. An integer number of these timing pulses is used by the command processor to complete a program or erase command.

Table 4-5 shows program and erase times. The bus clock frequency and FCDIV determine the frequency of FCLK ( $f_{FCLK}$ ). The time for one cycle of FCLK is  $t_{FCLK} = 1/f_{FCLK}$ . The times are shown as a number of cycles of FCLK and as an absolute time for the case where  $t_{FCLK} = 5 \ \mu$ s. Program and erase times shown include overhead for the command state machine and enabling and disabling of program and erase voltages.

The COP counter is initialized by the first writes to the SOPT1 and SOPT2 registers after any system reset. Subsequent writes to SOPT1 and SOPT2 have no effect on COP operation. Even if the application will use the reset default settings of COPT, COPCLKS, and COPW bits, the user should write to the write-once SOPT1 and SOPT2 registers during reset initialization to lock in the settings. This will prevent accidental changes if the application program gets lost.

The write to SRS that services (clears) the COP counter should not be placed in an interrupt service routine (ISR) because the ISR could continue to be executed periodically even if the main application program fails.

If the bus clock source is selected, the COP counter does not increment while the MCU is in background debug mode or while the system is in stop mode. The COP counter resumes when the MCU exits background debug mode or stop mode.

If the 1-kHz clock source is selected, the COP counter is re-initialized to zero upon entry to either background debug mode or stop mode and begins from zero upon exit from background debug mode or stop mode.

# 5.5 Interrupts

Interrupts provide a way to save the current CPU status and registers, execute an interrupt service routine (ISR), and then restore the CPU status so processing resumes where it left off before the interrupt. Other than the software interrupt (SWI), which is a program instruction, interrupts are caused by hardware events such as an edge on an external interrupt pin or a timer-overflow event. The debug module can also generate an SWI under certain circumstances.

If an event occurs in an enabled interrupt source, an associated read-only status flag will become set. The CPU will not respond unless the local interrupt enable is a 1 to enable the interrupt and the I bit in the CCR is 0 to allow interrupts. The global interrupt mask (I bit) in the CCR is initially set after reset which prevents all maskable interrupt sources. The user program initializes the stack pointer and performs other system setup before clearing the I bit to allow the CPU to respond to interrupts.

When the CPU receives a qualified interrupt request, it completes the current instruction before responding to the interrupt. The interrupt sequence obeys the same cycle-by-cycle sequence as the SWI instruction and consists of:

- Saving the CPU registers on the stack

- Setting the I bit in the CCR to mask further interrupts

- Fetching the interrupt vector for the highest-priority interrupt that is currently pending

- Filling the instruction queue with the first three bytes of program information starting from the address fetched from the interrupt vector locations

While the CPU is responding to the interrupt, the I bit is automatically set to avoid the possibility of another interrupt interrupting the ISR itself (this is called nesting of interrupts). Normally, the I bit is restored to 0 when the CCR is restored from the value stacked on entry to the ISR. In rare cases, the I bit can be cleared inside an ISR (after clearing the status flag that generated the interrupt) so that other interrupts can be serviced without waiting for the first service routine to finish. This practice is not

The status flag corresponding to the interrupt source must be acknowledged (cleared) before returning from the ISR. Typically, the flag is cleared at the beginning of the ISR so that if another interrupt is generated by this same source, it will be registered so it can be serviced after completion of the current ISR.

# 5.5.2 Interrupt Vectors, Sources, and Local Masks

Table 5-2 provides a summary of all interrupt sources. Higher-priority sources are located toward the bottom of the table. The high-order byte of the address for the interrupt service routine is located at the first address in the vector address column, and the low-order byte of the address for the interrupt service routine is located at the next higher address.

When an interrupt condition occurs, an associated flag bit becomes set. If the associated local interrupt enable is 1, an interrupt request is sent to the CPU. Within the CPU, if the global interrupt mask (I bit in the CCR) is 0, the CPU will finish the current instruction; stack the PCL, PCH, X, A, and CCR CPU registers; set the I bit; and then fetch the interrupt vector for the highest priority pending interrupt. Processing then continues in the interrupt service routine.

| Source<br>Form                                                                                                   | Operation                                                                                                                                                                                                                                                           | dress<br>ode                                                                                             | Saupo<br>Dobject Code                                                                        | Cycles                                              | Cyc-by-Cyc<br>Details                                                         | Affect<br>on CCR      |      |  |

|------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-----------------------------------------------------|-------------------------------------------------------------------------------|-----------------------|------|--|

| 1 Onn                                                                                                            |                                                                                                                                                                                                                                                                     | Pd<br>M                                                                                                  |                                                                                              | Ś                                                   | Details                                                                       | <b>V</b> 1 1 <b>H</b> | INZC |  |

| BLE rel                                                                                                          | Branch if Less Than or Equal To<br>(if Z I (N $\oplus$ V) = 1) (Signed)                                                                                                                                                                                             | REL                                                                                                      | 93 rr                                                                                        | 3                                                   | ppp                                                                           | - 1 1 -               |      |  |

| BLO <i>rel</i>                                                                                                   | Branch if Lower (if $C = 1$ ) (Same as BCS)                                                                                                                                                                                                                         | REL                                                                                                      | 25 rr                                                                                        | 3                                                   | ррр                                                                           | - 1 1 -               |      |  |

| BLS rel                                                                                                          | Branch if Lower or Same (if $C \mid Z = 1$ )                                                                                                                                                                                                                        | REL                                                                                                      | 23 rr                                                                                        | 3                                                   | ррр                                                                           | - 1 1 -               |      |  |

| BLT <i>rel</i>                                                                                                   | Branch if Less Than (if $N \oplus V = 1$ ) (Signed)                                                                                                                                                                                                                 | REL                                                                                                      | 91 rr                                                                                        | 3                                                   | ррр                                                                           | -11-                  |      |  |

| BMC rel                                                                                                          | Branch if Interrupt Mask Clear (if I = 0)                                                                                                                                                                                                                           | REL                                                                                                      | 2C rr                                                                                        | 3                                                   | ppp                                                                           | -11-                  |      |  |

| BMI <i>rel</i>                                                                                                   | Branch if Minus (if N = 1)                                                                                                                                                                                                                                          | REL                                                                                                      | 2B rr                                                                                        | 3                                                   | ppp                                                                           | -11-                  |      |  |

| BMS rel                                                                                                          | Branch if Interrupt Mask Set (if I = 1)                                                                                                                                                                                                                             | REL                                                                                                      | 2D rr                                                                                        | 3                                                   | ppp                                                                           | -11-                  |      |  |

| BNE rel                                                                                                          | Branch if Not Equal (if Z = 0)                                                                                                                                                                                                                                      | REL                                                                                                      | 26 rr                                                                                        | 3                                                   | ppp                                                                           | -11-                  |      |  |

| BPL rel                                                                                                          | Branch if Plus (if N = 0)                                                                                                                                                                                                                                           | REL                                                                                                      | 2A rr                                                                                        | 3                                                   | ppp                                                                           | -11-                  |      |  |

| BRA rel                                                                                                          | Branch Always (if I = 1)                                                                                                                                                                                                                                            | REL                                                                                                      | 20 rr                                                                                        | 3                                                   | ppp                                                                           | -11-                  |      |  |

| BRCLR n,opr8a,rel                                                                                                | Branch if Bit <i>n</i> in Memory Clear (if (Mn) = 0)                                                                                                                                                                                                                | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 01 dd rr<br>03 dd rr<br>05 dd rr<br>07 dd rr<br>09 dd rr<br>0B dd rr<br>0D dd rr<br>0F dd rr | 5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5      | rpppp<br>rpppp<br>rpppp<br>rpppp<br>rpppp<br>rpppp<br>rpppp<br>rpppp          | - 1 1 -               | ‡    |  |

| BRN rel                                                                                                          | Branch Never (if I = 0)                                                                                                                                                                                                                                             | REL                                                                                                      | 21 rr                                                                                        | 3                                                   | ppp                                                                           | - 1 1 -               |      |  |

| BRSET n,opr8a,rel                                                                                                | Branch if Bit <i>n</i> in Memory Set (if (Mn) = 1)                                                                                                                                                                                                                  | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 00 dd rr<br>02 dd rr<br>04 dd rr<br>06 dd rr<br>08 dd rr<br>0A dd rr<br>0C dd rr<br>0E dd rr | 5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5      | rpppp<br>rpppp<br>rpppp<br>rpppp<br>rpppp<br>rpppp<br>rpppp<br>rpppp          | - 1 1 -               | t    |  |

| BSET <i>n,opr8a</i>                                                                                              | Set Bit <i>n</i> in Memory (Mn ← 1)                                                                                                                                                                                                                                 | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7)             | 10 dd<br>12 dd<br>14 dd<br>16 dd<br>18 dd<br>1A dd<br>1C dd<br>1E dd                         | 5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5 | rfwpp<br>rfwpp<br>rfwpp<br>rfwpp<br>rfwpp<br>rfwpp<br>rfwpp<br>rfwpp<br>rfwpp | - 1 1 -               |      |  |

| BSR <i>rel</i>                                                                                                   | $\begin{array}{c} \text{Branch to Subroutine} \\ \text{PC} \leftarrow (\text{PC}) + \$0002 \\ \text{push (PCL); SP} \leftarrow (\text{SP}) - \$0001 \\ \text{push (PCH); SP} \leftarrow (\text{SP}) - \$0001 \\ \text{PC} \leftarrow (\text{PC}) + rel \end{array}$ | REL                                                                                                      | AD rr                                                                                        | 5                                                   | ssppp                                                                         | - 1 1 -               |      |  |

| CBEQ opr8a,rel<br>CBEQA #opr8i,rel<br>CBEQX #opr8i,rel<br>CBEQ oprx8,X+,rel<br>CBEQ ,X+,rel<br>CBEQ oprx8,SP,rel | Compare and Branch if $(A) = (M)$<br>Branch if $(A) = (M)$<br>Branch if $(X) = (M)$<br>Branch if $(A) = (M)$<br>Branch if $(A) = (M)$<br>Branch if $(A) = (M)$                                                                                                      | DIR<br>IMM<br>IX1+<br>IX+<br>SP1                                                                         | 31 dd rr<br>41 ii rr<br>51 ii rr<br>61 ff rr<br>71 rr<br>9E 61 ff rr                         | 5<br>4<br>5<br>5<br>6                               | rpppp<br>pppp<br>rppp<br>rfppp<br>prpppp                                      | - 1 1 -               |      |  |

Table 7-2. Instruction Set Summary (Sheet 3 of 9)

#### Chapter 7 Central Processor Unit (S08CPUV3)

| Dia Mara                | -Manipulation Branch Read-Modify-Write |                      |                                                                                                                              |                       |                       |                      |                       |                        |                      |                                                                                                                                                 |                      |                      |                      |                      |                     |  |

|-------------------------|----------------------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|----------------------|-----------------------|------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------|----------------------|----------------------|---------------------|--|

|                         |                                        | Branch               | Read-Modify-Write           30         5         40         1         50         1         60         5         70         4 |                       |                       |                      |                       |                        |                      | Register/Memory           3         A0         2         B0         3         C0         4         D0         4         E0         3         F0 |                      |                      |                      |                      |                     |  |

| 00 5                    | 10 5                                   | 20 3                 | 30 5                                                                                                                         | 40 1                  | 50 1                  | 60 5                 | 70 4                  | 80 9                   | 90 3                 | A0 2                                                                                                                                            | B0 3                 | SUB                  | D0 4                 | E0 3                 | 50 3                |  |

| BRSET0                  | BSET0                                  | BRA                  | NEG                                                                                                                          | NEGA                  | NEGX                  | NEG                  | NEG                   | RTI                    | BGE                  | SUB                                                                                                                                             | SUB                  |                      | SUB                  | SUB                  | SUB                 |  |

| 3 DIR                   | 2 DIR                                  | 2 REL                | 2 DIR                                                                                                                        | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                  | 1 INH                  | 2 REL                | 2 IMM                                                                                                                                           | 2 DIR                |                      | 3 IX2                | 2 IX1                | 1 IX                |  |

| 01 5                    | 11 5                                   | 21 3                 | 31 5                                                                                                                         | 41 4                  | 51 4                  | 61 5                 | 71 5                  | 81 6                   | 91 3                 | A1 2                                                                                                                                            | B1 3                 | CMP                  | D1 4                 | E1 3                 | F1 3                |  |

| BRCLR0                  | BCLR0                                  | BRN                  | CBEQ                                                                                                                         | CBEQA                 | CBEQX                 | CBEQ                 | CBEQ                  | RTS                    | BLT                  | CMP                                                                                                                                             | CMP                  |                      | CMP                  | CMP                  | CMP                 |  |

| 3 DIR                   | 2 DIR                                  | 2 REL                | 3 DIR                                                                                                                        | 3 IMM                 | 3 IMM                 | 3 IX1+               | 2 IX+                 | 1 INH                  | 2 REL                | 2 IMM                                                                                                                                           | 2 DIR                |                      | 3 IX2                | 2 IX1                | 1 IX                |  |

| 02 5<br>BRSET1<br>3 DIR | 12 5<br>BSET1<br>2 DIR                 | 22 3<br>BHI<br>2 REL | 32 5<br>LDHX                                                                                                                 | 42 5<br>MUL<br>1 INH  | 52 6<br>DIV           | 62 1<br>NSA<br>1 INH | 72 1<br>DAA<br>1 INH  | 82 5+<br>BGND<br>1 INH | 92 3<br>BGT<br>2 REL | A2 2<br>SBC<br>2 IMM                                                                                                                            | B2 3<br>SBC          |                      |                      | E2 3<br>SBC<br>2 IX1 | F2 3<br>SBC<br>1 IX |  |

| 03 5                    | 13 5                                   | 23 3                 |                                                                                                                              | 43 1                  | 53 1                  | 63 5                 | 73 4                  | 83 11                  | 93 3                 | A3 2                                                                                                                                            | B3 3                 | C3 4                 | D3 4                 | E3 3                 | F3 3                |  |

| BRCLR1                  | BCLR1                                  | BLS                  |                                                                                                                              | COMA                  | COMX                  | COM                  | COM                   | SWI                    | BLE                  | CPX                                                                                                                                             | CPX                  | CPX                  | CPX                  | CPX                  | CPX                 |  |

| 3 DIR                   | 2 DIR                                  | 2 REL                |                                                                                                                              | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                  | 1 INH                  | 2 REL                | 2 IMM                                                                                                                                           | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |  |

| 04 5                    | 14 5                                   | 24 3                 | 34 5                                                                                                                         | 44 1                  | 54 1                  | 64 5                 | 74 4                  | 84 1                   | 94 2                 | A4 2                                                                                                                                            | B4 3                 | C4 4                 | D4 4                 | E4 3                 | F4 3                |  |

| BRSET2                  | BSET2                                  | BCC                  | LSR                                                                                                                          | LSRA                  | LSRX                  | LSR                  | LSR                   | TAP                    | TXS                  | AND                                                                                                                                             | AND                  | AND                  | AND                  | AND                  | AND                 |  |

| 3 DIR                   | 2 DIR                                  | 2 REL                | 2 DIR                                                                                                                        | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                  | 1 INH                  | 1 INH                | 2 IMM                                                                                                                                           | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |  |

| 05 5                    | 15 5                                   | 25 3                 | 35 4                                                                                                                         | 45 3                  | 55 4                  | 65 3                 | 75 5                  | 85 1                   | 95 2                 | A5 2                                                                                                                                            | B5 3                 | C5 4                 | D5 4                 | E5 3                 | F5 3                |  |

| BRCLR2                  | BCLR2                                  | BCS                  | STHX                                                                                                                         | LDHX                  | LDHX                  | CPHX                 | CPHX                  | TPA                    | TSX                  | BIT                                                                                                                                             | BIT                  | BIT                  | BIT                  | BIT                  | BIT                 |  |

| 3 DIR                   | 2 DIR                                  | 2 REL                | 2 DIR                                                                                                                        | 3 IMM                 | 2 DIR                 | 3 IMM                | 2 DIR                 | 1 INH                  | 1 INH                | 2 IMM                                                                                                                                           | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |  |

| 06 5                    | 16 5                                   | 26 3                 | 36 5                                                                                                                         | 46 1                  | 56 1                  | 66 5                 | 76 4                  | 86 3                   | 96 5                 | A6 2                                                                                                                                            | B6 3                 | C6 4                 | D6 4                 | E6 3                 | F6 3                |  |

| BRSET3                  | BSET3                                  | BNE                  | ROR                                                                                                                          | RORA                  | RORX                  | ROR                  | ROR                   | PULA                   | STHX                 | LDA                                                                                                                                             | LDA                  | LDA                  | LDA                  | LDA                  | LDA                 |  |

| 3 DIR                   | 2 DIR                                  | 2 REL                | 2 DIR                                                                                                                        | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                  | 1 INH                  | 3 EXT                | 2 IMM                                                                                                                                           | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |  |

| 07 5                    | 17 5                                   | 27 3                 | 37 5                                                                                                                         | 47 1                  | 57 1                  | 67 5                 | 77 4                  | 87 2                   | 97 1                 | A7 2                                                                                                                                            | B7 3                 | C7 4                 | D7 4                 | E7 3                 | F7 2                |  |

| BRCLR3                  | BCLR3                                  | BEQ                  | ASR                                                                                                                          | ASRA                  | ASRX                  | ASR                  | ASR                   | PSHA                   | TAX                  | AIS                                                                                                                                             | STA                  | STA                  | STA                  | STA                  | STA                 |  |

| 3 DIR                   | 2 DIR                                  | 2 REL                | 2 DIR                                                                                                                        | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                  | 1 INH                  | 1 INH                | 2 IMM                                                                                                                                           | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |  |

| 08 5                    | 18 5                                   | 28 3                 | 38 5                                                                                                                         | 48 1                  | 58 1                  | 68 5                 | 78 4                  | 88 3                   | 98 1                 | A8 2                                                                                                                                            | B8 3                 | C8 4                 | D8 4                 | E8 3                 | F8 3                |  |

| BRSET4                  | BSET4                                  | BHCC                 | LSL                                                                                                                          | LSLA                  | LSLX                  | LSL                  | LSL                   | PULX                   | CLC                  | EOR                                                                                                                                             | EOR                  | EOR                  | EOR                  | EOR                  | EOR                 |  |

| 3 DIR                   | 2 DIR                                  | 2 REL                | 2 DIR                                                                                                                        | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                  | 1 INH                  | 1 INH                | 2 IMM                                                                                                                                           | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |  |

| 09 5                    | 19 5                                   | 29 3                 | 39 5                                                                                                                         | 49 1                  | 59 1                  | 69 5                 | <sup>79</sup> 4       | 89 2                   | 99 1                 | A9 2                                                                                                                                            | B9 3                 | C9 4                 | D9 4                 | E9 3                 | F9 3                |  |

| BRCLR4                  | BCLR4                                  | BHCS                 | ROL                                                                                                                          | ROLA                  | ROLX                  | ROL                  | ROL                   | PSHX                   | SEC                  | ADC                                                                                                                                             | ADC                  | ADC                  | ADC                  | ADC                  | ADC                 |  |

| 3 DIR                   | 2 DIR                                  | 2 REL                | 2 DIR                                                                                                                        | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                  | 1 INH                  | 1 INH                | 2 IMM                                                                                                                                           | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |  |

| 0A 5                    | 1A 5                                   | 2A 3                 | 3A 5                                                                                                                         | 4A 1                  | 5A 1                  | 6A 5                 | 7A 4                  | 8A 3                   | 9A 1                 | AA 2                                                                                                                                            | BA 3                 | CA 4                 | DA 4                 | EA 3                 | FA 3                |  |

| BRSET5                  | BSET5                                  | BPL                  | DEC                                                                                                                          | DECA                  | DECX                  | DEC                  | DEC                   | PULH                   | CLI                  | ORA                                                                                                                                             | ORA                  | ORA                  | ORA                  | ORA                  | ORA                 |  |

| 3 DIR                   | 2 DIR                                  | 2 REL                | 2 DIR                                                                                                                        | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                  | 1 INH                  | 1 INH                | 2 IMM                                                                                                                                           | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |  |

| 0B 5                    |                                        | 2B 3                 | 3B 7                                                                                                                         | 4B 4                  | 5B 4                  | 6B 7                 | 7B 6                  | 8B 2                   | 9B 1                 | AB 2                                                                                                                                            | BB 3                 | CB 4                 | DB 4                 | EB 3                 | FB 3                |  |

| BRCLR5                  |                                        | BMI                  | DBNZ                                                                                                                         | DBNZA                 | DBNZX                 | DBNZ                 | DBNZ                  | PSHH                   | SEI                  | ADD                                                                                                                                             | ADD                  | ADD                  | ADD                  | ADD                  | ADD                 |  |

| 3 DIR                   |                                        | 2 REL                | 3 DIR                                                                                                                        | 2 INH                 | 2 INH                 | 3 IX1                | 2 IX                  | 1 INH                  | 1 INH                | 2 IMM                                                                                                                                           | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |  |

| 0C 5                    | 1C 5                                   | 2C 3                 | 3C 5                                                                                                                         | 4C 1                  | 5C 1                  | 6C 5                 | 7C 4                  | 8C 1                   | 9C 1                 |                                                                                                                                                 | BC 3                 | CC 4                 | DC 4                 | EC 3                 | FC 3                |  |

| BRSET6                  | BSET6                                  | BMC                  | INC                                                                                                                          | INCA                  | INCX                  | INC                  | INC                   | CLRH                   | RSP                  |                                                                                                                                                 | JMP                  | JMP                  | JMP                  | JMP                  | JMP                 |  |

| 3 DIR                   | 2 DIR                                  | 2 REL                | 2 DIR                                                                                                                        | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                  | 1 INH                  | 1 INH                |                                                                                                                                                 | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |  |

| 0D 5<br>BRCLR6<br>3 DIR | 1D 5<br>BCLR6<br>2 DIR                 | 2D 3<br>BMS<br>2 REL | 3D 4<br>TST<br>2 DIR                                                                                                         | 4D 1<br>TSTA<br>1 INH | 5D 1<br>TSTX<br>1 INH | 6D 4<br>TST<br>2 IX1 | 7D 3<br>TST<br>1 IX   |                        | 9D 1<br>NOP<br>1 INH | AD 5<br>BSR<br>2 REL                                                                                                                            |                      | CD 6<br>JSR<br>3 EXT | DD 6<br>JSR<br>3 IX2 | ED 5<br>JSR<br>2 IX1 | FD 5<br>JSR<br>1 IX |  |

| 0E 5<br>BRSET7<br>3 DIR | BSET7<br>2 DIR                         | 2E 3<br>BIL<br>2 REL | 3E 6<br>CPHX<br>3 EXT                                                                                                        | 4E 5<br>MOV<br>3 DD   | 5E 5<br>MOV<br>2 DIX+ | 6E 4<br>MOV<br>3 IMD | 7E 5<br>MOV<br>2 IX+D | 8E 2+<br>STOP<br>1 INH | 9E<br>Page 2         | AE 2<br>LDX<br>2 IMM                                                                                                                            | BE 3<br>LDX<br>2 DIR | LDX<br>3 EXT         | LDX<br>3 IX2         | EE 3<br>LDX<br>2 IX1 | FE 3<br>LDX<br>1 IX |  |

| 0F 5                    | 1F 5                                   | 2F 3                 | 3F 5                                                                                                                         | 4F 1                  | 5F 1                  | 6F 5                 | 7F 4                  | 8F 2+                  | 9F 1                 | AF 2                                                                                                                                            | BF 3                 | CF 4                 | DF 4                 | EF 3                 | FF 2                |  |

| BRCLR7                  | BCLR7                                  | BIH                  | CLR                                                                                                                          | CLRA                  | CLRX                  | CLR                  | CLR                   | WAIT                   | TXA                  | AIX                                                                                                                                             | STX                  | STX                  | STX                  | STX                  | STX                 |  |

| 3 DIR                   | 2 DIR                                  | 2 REL                | 2 DIR                                                                                                                        | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                  | 1 INH                  | 1 INH                | 2 IMM                                                                                                                                           | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |  |

#### Table 7-3. Opcode Map (Sheet 1 of 2)

Relative Indexed, No Offset Indexed, 8-Bit Offset Indexed, 16-Bit Offset IMM to DIR DIR to IX+ REL IX IX1 IX2 IMD DIX+

SP1 SP2 IX+

IX1+

Stack Pointer, 8-Bit Offset Stack Pointer, 16-Bit Offset Indexed, No Offset with Post Increment Indexed, 1-Byte Offset with Post Increment

Opcode in Hexadecimal F0 3 SUB Instruction Mnemonic 1 IX Addressing Mode Number of Bytes

| Bit-Manipulation | Branch | Rea | d-Modify-W | rite                             | • | Con | ,                      |                         | Register                | /Memory                                                                    |                        |                                   |

|------------------|--------|-----|------------|----------------------------------|---|-----|------------------------|-------------------------|-------------------------|----------------------------------------------------------------------------|------------------------|-----------------------------------|

|                  |        |     |            | 9E60 6<br>NEG<br>3 SP1<br>9E61 6 |   |     |                        |                         |                         | 9ED0 5<br>SUB<br>4 SP2<br>9ED1 5<br>CMP<br>4 SP2<br>9ED2 5<br>SBC<br>4 SP2 | 9EE0 4<br>SUB<br>3 SP1 |                                   |

|                  |        |     |            | 9E61 6<br>CBEQ<br>4 SP1          |   |     |                        |                         |                         | 9ED1 5<br>CMP<br>4 SP2                                                     | 9EE1 4<br>CMP<br>3 SP1 |                                   |

|                  |        |     |            |                                  |   |     |                        |                         |                         | 9ED2 5<br>SBC<br>4 SP2                                                     | 9EE2 4<br>SBC<br>3 SP1 |                                   |

|                  |        |     |            | 9E63 6<br>COM<br>3 SP1           |   |     |                        |                         |                         | 4 SP2<br>9ED3 5<br>CPX<br>4 SP2                                            | 9EE3 4<br>CPX<br>3 SP1 | 9EF3 6<br>CPHX<br>3 SP1           |

|                  |        |     |            | 9E64 6<br>LSR<br>3 SP1           |   |     |                        |                         |                         | 9ED4 5<br>AND<br>4 SP2                                                     | 9EE4 4<br>AND<br>3 SP1 |                                   |

|                  |        |     |            |                                  |   |     |                        |                         |                         | 9ED4 5<br>AND<br>4 SP2<br>9ED5 5<br>BIT<br>4 SP2                           | 9EE5 4<br>BIT<br>3 SP1 |                                   |

|                  |        |     |            | 9E66 6<br>ROR<br>3 SP1           |   |     |                        |                         |                         | 9ED6 5<br>LDA<br>4 SP2                                                     | 9EE6 4<br>LDA<br>3 SP1 |                                   |

|                  |        |     |            | 9E67 6<br>ASR<br>3 SP1           |   |     |                        |                         |                         | 9ED7 5<br>STA<br>4 SP2                                                     | 9EE7 4<br>STA<br>3 SP1 |                                   |

|                  |        |     |            | 9E68 6<br>LSL<br>3 SP1           |   |     |                        |                         |                         | 9ED8 5<br>EOR<br>4 SP2                                                     | EOR<br>3 SP1           |                                   |

|                  |        |     |            | 9E69 6<br>ROL<br>3 SP1           |   |     |                        |                         |                         | 9ED9 5<br>ADC<br>4 SP2                                                     | ADC<br>3 SP1           |                                   |

|                  |        |     |            | 9E6A 6<br>DEC<br>3 SP1           |   |     |                        |                         |                         | 9EDA 5<br>ORA<br>4 SP2                                                     | ORA<br>3 SP1           |                                   |

|                  |        |     |            | 9E6B 8<br>DBNZ<br>4 SP1          |   |     |                        |                         |                         | 9EDB 5<br>ADD<br>4 SP2                                                     | 9EEB 4<br>ADD<br>3 SP1 |                                   |

|                  |        |     |            | 9E6C 6<br>INC<br>3 SP1           |   |     |                        |                         |                         |                                                                            |                        |                                   |

|                  |        |     |            | 9E6D 5<br>TST<br>3 SP1           |   |     |                        |                         |                         |                                                                            |                        |                                   |

|                  |        |     |            |                                  |   |     | 9EAE 5<br>LDHX<br>2 IX | 9EBE 6<br>LDHX<br>4 IX2 | 9ECE 5<br>LDHX<br>3 IX1 | 9EDE 5<br>LDX<br>4 SP2                                                     | 9EEE 4<br>LDX<br>3 SP1 | 9EFE 5<br>LDHX<br>3 SP1<br>9EFF 5 |

|                  |        |     |            | 9E6F 6<br>CLR<br>3 SP1           |   |     |                        |                         |                         | 9EDF 5<br>STX<br>4 SP2                                                     | 9EEF 4<br>STX<br>3 SP1 | 9EFF 5<br>STHX<br>3 SP1           |

#### Table 7-3. Opcode Map (Sheet 2 of 2)

Inherent Immediate Direct Extended DIR to DIR IX+ to DIR REL IX IX1 IX2 IMD DIX+ INH IMM DIR EXT DD IX+D

Relative Indexed, No Offset Indexed, 8-Bit Offset Indexed, 16-Bit Offset IMM to DIR DIR to IX+

Stack Pointer, 8-Bit Offset Stack Pointer, 16-Bit Offset Indexed, No Offset with Post Increment Indexed, 1-Byte Offset with Post Increment

SP1 SP2 IX+

IX1+

Note: All Sheet 2 Opcodes are Preceded by the Page 2 Prebyte (9E)

Prebyte (9E) and Opcode in Hexadecimal HCS08 Cycles EG SP1 Addressing Mode Number of Bytes 3

Internal Clock Source (S08ICSV2)

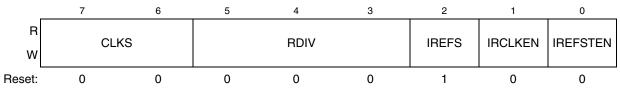

# 8.3.1 ICS Control Register 1 (ICSC1)

Figure 8-3. ICS Control Register 1 (ICSC1)

| Table 8-2. ICS Control Register | 1 Field Descriptions |

|---------------------------------|----------------------|

|---------------------------------|----------------------|

| Field         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6<br>CLKS   | <ul> <li>Clock Source Select — Selects the clock source that controls the bus frequency. The actual bus frequency depends on the value of the BDIV bits.</li> <li>O Output of FLL is selected.</li> <li>O1 Internal reference clock is selected.</li> <li>10 External reference clock is selected.</li> <li>11 Reserved, defaults to 00.</li> </ul>                                                                                                                                                                                                                                                                                                                                                       |

| 5:3<br>RDIV   | Reference Divider — Selects the amount to divide down the FLL reference clock selected by the IREFS bits.         Resulting frequency must be in the range 31.25 kHz to 39.0625 kHz.         000       Encoding 0 — Divides reference clock by 1 (reset default)         001       Encoding 1 — Divides reference clock by 2         010       Encoding 2 — Divides reference clock by 4         011       Encoding 3 — Divides reference clock by 8         100       Encoding 4 — Divides reference clock by 16         101       Encoding 5 — Divides reference clock by 32         110       Encoding 6 — Divides reference clock by 64         111       Encoding 7 — Divides reference clock by 128 |

| 2<br>IREFS    | Internal Reference Select — The IREFS bit selects the reference clock source for the FLL.<br>1 Internal reference clock selected<br>0 External reference clock selected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 1<br>IRCLKEN  | Internal Reference Clock Enable — The IRCLKEN bit enables the internal reference clock for use as<br>ICSIRCLK.<br>1 ICSIRCLK active<br>0 ICSIRCLK inactive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0<br>IREFSTEN | <ul> <li>Internal Reference Stop Enable — The IREFSTEN bit controls whether or not the internal reference clock remains enabled when the ICS enters stop mode.</li> <li>1 Internal reference clock stays enabled in stop if IRCLKEN is set or if ICS is in FEI, FBI, or FBILP mode before entering stop</li> <li>0 Internal reference clock is disabled in stop</li> </ul>                                                                                                                                                                                                                                                                                                                                |

# 8.4.1.5 FLL Bypassed External (FBE)

The FLL bypassed external (FBE) mode is entered when all the following conditions occur:

- CLKS bits are written to 10.

- IREFS bit is written to 0.

- BDM mode is active or LP bit is written to 0.

In FLL bypassed external mode, the ICSOUT clock is derived from the external reference clock. The FLL clock is controlled by the external reference clock, and the FLL loop will lock the FLL frequency to 1024 times the reference frequency, as selected by the RDIV bits, so that the ICSLCLK will be available for BDC communications, and the external reference clock is enabled.

### 8.4.1.6 FLL Bypassed External Low Power (FBELP)

The FLL bypassed external low power (FBELP) mode is entered when all the following conditions occur:

- CLKS bits are written to 10.

- IREFS bit is written to 0.

- BDM mode is not active and LP bit is written to 1.

In FLL bypassed external low power mode, the ICSOUT clock is derived from the external reference clock and the FLL is disabled. The ICSLCLK will be not be available for BDC communications. The external reference clock is enabled.

### 8.4.1.7 Stop

Stop mode is entered whenever the MCU enters a STOP state. In this mode, all ICS clock signals are static except in the following cases:

ICSIRCLK will be active in stop mode when all the following conditions occur:

- IRCLKEN bit is written to 1

- IREFSTEN bit is written to 1

ICSERCLK will be active in stop mode when all the following conditions occur:

- ERCLKEN bit is written to 1

- EREFSTEN bit is written to 1

### 8.4.2 Mode Switching

When switching between FLL engaged internal (FEI) and FLL engaged external (FEE) modes the IREFS bit can be changed at anytime, but the RDIV bits must be changed simultaneously so that the resulting frequency stays in the range of 31.25 kHz to 39.0625 kHz. After a change in the IREFS value the FLL will begin locking again after a few full cycles of the resulting divided reference frequency. The completion of the switch is shown by the IREFST bit.

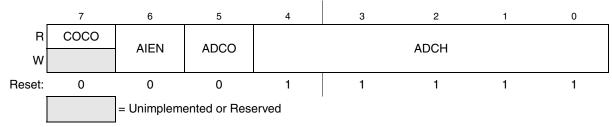

Figure 10-3. Status and Control Register (ADCSC1)

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>COCO   | <ul> <li>Conversion Complete Flag — The COCO flag is a read-only bit which is set each time a conversion is completed when the compare function is disabled (ACFE = 0). When the compare function is enabled (ACFE = 1) the COCO flag is set upon completion of a conversion only if the compare result is true. This bit is cleared whenever ADCSC1 is written or whenever ADCRL is read.</li> <li>0 Conversion not completed</li> <li>1 Conversion completed</li> </ul>                                                                                                                                                                                                                                                                            |

| 6<br>AIEN   | Interrupt Enable — AIEN is used to enable conversion complete interrupts. When COCO becomes set while<br>AIEN is high, an interrupt is asserted.<br>0 Conversion complete interrupt disabled<br>1 Conversion complete interrupt enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5<br>ADCO   | <ul> <li>Continuous Conversion Enable — ADCO is used to enable continuous conversions.</li> <li>One conversion following a write to the ADCSC1 when software triggered operation is selected, or one conversion following assertion of ADHWT when hardware triggered operation is selected.</li> <li>Continuous conversions initiated following a write to ADCSC1 when software triggered operation is selected. Continuous conversions are initiated by an ADHWT event when hardware triggered operation is selected.</li> </ul>                                                                                                                                                                                                                    |

| 4:0<br>ADCH | Input Channel Select — The ADCH bits form a 5-bit field which is used to select one of the input channels. The input channels are detailed in Figure 10-4.<br>The successive approximation converter subsystem is turned off when the channel select bits are all set to 1.<br>This feature allows for explicit disabling of the ADC and isolation of the input channel from all sources.<br>Terminating continuous conversions this way will prevent an additional, single conversion from being performed.<br>It is not necessary to set the channel select bits to all 1s to place the ADC in a low-power state when continuous conversion are not enabled because the module automatically enters a low-power state when a conversion completes. |

#### Figure 10-4. Input Channel Select

| ADCH  | Input Select |

|-------|--------------|

| 00000 | AD0          |

| 00001 | AD1          |

| 00010 | AD2          |

| 00011 | AD3          |

| 00100 | AD4          |

| 00101 | AD5          |

| 00110 | AD6          |

| 00111 | AD7          |

| ADCH  | Input Select |

|-------|--------------|

| 10000 | AD16         |

| 10001 | AD17         |

| 10010 | AD18         |

| 10011 | AD19         |

| 10100 | AD20         |

| 10101 | AD21         |

| 10110 | AD22         |

| 10111 | AD23         |

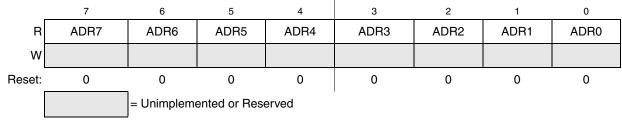

Figure 10-7. Data Result Low Register (ADCRL)

# 10.3.5 Compare Value High Register (ADCCVH)

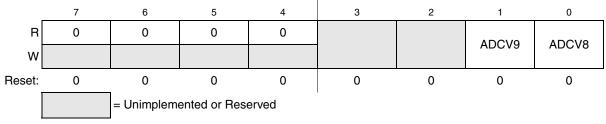

This register holds the upper two bits of the 10-bit compare value. These bits are compared to the upper two bits of the result following a conversion in 10-bit mode when the compare function is enabled. In 8-bit operation, ADCCVH is not used during compare.

Figure 10-8. Compare Value High Register (ADCCVH)

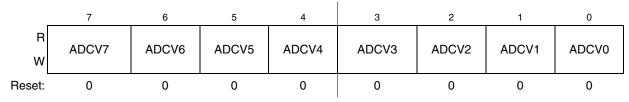

# 10.3.6 Compare Value Low Register (ADCCVL)

This register holds the lower 8 bits of the 10-bit compare value, or all 8 bits of the 8-bit compare value. Bits ADCV7:ADCV0 are compared to the lower 8 bits of the result following a conversion in either 10-bit or 8-bit mode.

# 10.3.7 Configuration Register (ADCCFG)

ADCCFG is used to select the mode of operation, clock source, clock divide, and configure for low power or long sample time.

# 10.6.2 Sources of Error

Several sources of error exist for A/D conversions. These are discussed in the following sections.

# 10.6.2.1 Sampling Error

For proper conversions, the input must be sampled long enough to achieve the proper accuracy. Given the maximum input resistance of approximately  $7k\Omega$  and input capacitance of approximately 5.5 pF, sampling to within 1/4LSB (at 10-bit resolution) can be achieved within the minimum sample window (3.5 cycles @ 8 MHz maximum ADCK frequency) provided the resistance of the external analog source (R<sub>AS</sub>) is kept below 5 kΩ.

Higher source resistances or higher-accuracy sampling is possible by setting ADLSMP (to increase the sample window to 23.5 cycles) or decreasing ADCK frequency to increase sample time.

# 10.6.2.2 Pin Leakage Error

Leakage on the I/O pins can cause conversion error if the external analog source resistance ( $R_{AS}$ ) is high. If this error cannot be tolerated by the application, keep  $R_{AS}$  lower than  $V_{DDAD} / (2^{N*}I_{LEAK})$  for less than 1/4LSB leakage error (N = 8 in 8-bit mode or 10 in 10-bit mode).

# 10.6.2.3 Noise-Induced Errors

System noise which occurs during the sample or conversion process can affect the accuracy of the conversion. The ADC accuracy numbers are guaranteed as specified only if the following conditions are met:

- There is a 0.1  $\mu$ F low-ESR capacitor from V<sub>REFH</sub> to V<sub>REFL</sub>.

- There is a 0.1  $\mu$ F low-ESR capacitor from V<sub>DDAD</sub> to V<sub>SSAD</sub>.

- If inductive isolation is used from the primary supply, an additional 1  $\mu$ F capacitor is placed from V<sub>DDAD</sub> to V<sub>SSAD</sub>.

- $V_{SSAD}$  (and  $V_{REFL}$ , if connected) is connected to  $V_{SS}$  at a quiet point in the ground plane.

- Operate the MCU in wait or stop3 mode before initiating (hardware triggered conversions) or immediately after initiating (hardware or software triggered conversions) the ADC conversion.