#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2014.10                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Obsolete                                                               |

| Core Processor             | CIP-51 8051                                                            |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 48MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, SMBus, SPI, UART/USART, USB                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                  |

| Number of I/O              | 13                                                                     |

| Program Memory Size        | 40KB (40K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | ·                                                                      |

| RAM Size                   | 3.25K x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                           |

| Data Converters            | A/D 12x12b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 20-WFQFN Exposed Pad                                                   |

| Supplier Device Package    | 20-QFN (3x3)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm8ub30f40g-a-qfn20 |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1. Feature List

The EFM8UB3 highlighted features are listed below.

- High-speed CIP-51 MCU Core

- Pipelined instruction architecture; executes 70% of instruction set in 1 or 2 system clocks

- Up to 48 MIPS throughput with 48 MHz clock

- Uses standard 8051 instruction set

- Expanded interrupt handler

## • Memory

- 40 KB Flash

- Flash is in-system programmable in 512-byte sectors

- 3328 bytes RAM, including:

- · 256 bytes standard 8051 RAM

- 2048 bytes on-chip XRAM

- 1024 bytes of USB buffer

## • On-chip Debug

- On-chip debug circuitry facilitates full speed, non-intrusive in-system debug (no emulator required)

- Provides 4 hardware breakpoints, single stepping, inspect/ modify memory and registers

## 12-bit Analog-to-Digital Converter

- Multiple selectable inputs

- Up to 800 ksps 10-bit mode

- Precise Internal VREF 1.65 V or external VREF supported

## Clock Sources

- + 48 MHz  $\pm$  1.5% precision internal oscillator and  $\pm 0.25\%$  using USB clock recovery

- + 24.5 MHz low power internal oscillator with  $\pm 2\%$  accuracy

- 80 kHz low-frequency, low power internal oscillator (LFO)

- External CMOS clock option

- Flexible clock divider: Reduce frequency by up to 128x from any clock source

## • 2 x Analog Comparators

- Multiplexed selectable inputs

- Integrated 6-bit programmable reference voltage selectable as comparator input channel

- Programmable hysteresis and response time

- 400 nA current consumption in low power mode

### Power Management

- 5 V-input LDO regulator for direct connection to USB supply

- External LDO is needed for USB-C VBUS powered applications that require more than 5 V.

- Internal low dropout (LDO) regulator for CPU core voltage

- Power-on reset and brownout detect circuit

- Multiple power modes supported to minimize power consumption while maintaining performance

## General-Purpose I/O

- Up to 17 pins

- V<sub>IO</sub> + 2.5 V tolerant; push-pull or open-drain

- Priority crossbar to support flexible digital peripheral pin assignments

## Timers/Counters/PWM

- 6 general purpose 16-bit counters/timers

- 16-bit Programmable Counter Array (PCA) with 3 channels of PWM, capture/compare, or frequency output capability, and hardware kill/safe state capability

- Independent watchdog timer, clocked from the low frequency oscillator

- Communication Interfaces and Digital Peripherals

- UART, up to 3 Mbaud

- SMBus (1 Mbps)

- USB 2.0-compliant full speed with integrated low-power transceiver, 4 bidirectional endpoints and dedicated 1024byte buffer

- 16-bit CRC unit, supporting automatic CRC of flash at 256byte boundaries

- Single Voltage Supply

- (VREGIN shorted to VDD): 2.3 to 3.6 V

- (VREGIN not shorted to VDD): 2.7 to 5.25 V

- Pre-loaded USB Bootloader

- Package Options: QFN20, QFN24, QSOP24

- Temperature Range: -40 to +85 °C

With on-chip power-on reset, voltage supply monitor, watchdog timer, and clock oscillator, the EFM8UB3 devices are truly standalone system-on-a-chip solutions. The flash memory is reprogrammable in-circuit, providing nonvolatile data storage and allowing field upgrades of the firmware. The on-chip debugging interface (C2) allows non-intrusive (uses no on-chip resources), full speed, in-circuit debugging using the production MCU installed in the final application. This debug logic supports inspection and modification of memory and registers, setting breakpoints, single stepping, and run and halt commands. All analog and digital peripherals are fully functional while debugging. Devices are available in 20-pin QFN, 24-pin QFN, or 24-pin QSOP packages. All package options are lead-free and RoHS compliant.

### 3.6 Communications and Other Digital Peripherals

### Universal Serial Bus (USB0)

The USB0 peripheral provides a full-speed USB 2.0 compliant device controller and PHY with additional Low Energy USB features. The device supports both full-speed (12MBit/s) and low speed (1.5MBit/s) operation, and includes a dedicated USB oscillator with clock recovery mechanism for crystal-free operation. No external components are required. The USB function controller (USB0) consists of a Serial Interface Engine (SIE), USB transceiver (including matching resistors and configurable pull-up resistors), and 1 KB FIFO block. The Low Energy Mode ensures the current consumption is optimized and enables USB communication on a strict power budget.

The USB0 module includes the following features:

- · Full and Low Speed functionality.

- Implements 4 bidirectional endpoints.

- Low Energy Mode to reduce active supply current based on bus bandwidth.

- · USB 2.0 compliant USB peripheral support (no host capability).

- Direct module access to 1 KB of RAM for FIFO memory.

- Clock recovery to meet USB clocking requirements with no external components.

- · Charger detection circuitry with automatic detection of SDP, CDP, and DCP interfaces.

- D+ and D- can be routed to ADC input to support ACM and proprietary charger architectures.

#### Universal Asynchronous Receiver/Transmitter (UART1)

UART1 is an asynchronous, full duplex serial port offering a variety of data formatting options. A dedicated baud rate generator with a 16-bit timer and selectable prescaler is included, which can generate a wide range of baud rates. A received data FIFO allows UART1 to receive multiple bytes before data is lost and an overflow occurs.

UART1 provides the following features:

- · Asynchronous transmissions and receptions.

- Dedicated baud rate generator supports baud rates up to SYSCLK/2 (transmit) or SYSCLK/8 (receive).

- 5, 6, 7, 8, or 9 bit data.

- Automatic start and stop generation.

- · Automatic parity generation and checking.

- · Four byte FIFO on transmit and receive.

- Auto-baud detection.

- LIN break and sync field detection.

- CTS / RTS hardware flow control.

### Serial Peripheral Interface (SPI0)

The serial peripheral interface (SPI) module provides access to a flexible, full-duplex synchronous serial bus. The SPI can operate as a master or slave device in both 3-wire or 4-wire modes, and supports multiple masters and slaves on a single SPI bus. The slave-select (NSS) signal can be configured as an input to select the SPI in slave mode, or to disable master mode operation in a multi-master environment, avoiding contention on the SPI bus when more than one master attempts simultaneous data transfers. NSS can also be configured as a firmware-controlled chip-select output in master mode, or disable to reduce the number of pins required. Additional general purpose port I/O pins can be used to select multiple slave devices in master mode.

- · Supports 3- or 4-wire master or slave modes.

- · Supports external clock frequencies up to 12 Mbps in master or slave mode.

- · Support for all clock phase and polarity modes.

- 8-bit programmable clock rate (master).

- Programmable receive timeout (slave).

- Two byte FIFO on transmit and receive.

- · Can operate in suspend or snooze modes and wake the CPU on reception of a byte.

- · Support for multiple masters on the same data lines.

# 4. Electrical Specifications

### 4.1 Electrical Characteristics

All electrical parameters in all tables are specified under the conditions listed in 4.1.1 Recommended Operating Conditions, unless stated otherwise.

Table 4.1. Recommended Operating Conditions

### 4.1.1 Recommended Operating Conditions

| Parameter                                            | Symbol              | Test Condition | Min              | Тур | Мах             | Unit |

|------------------------------------------------------|---------------------|----------------|------------------|-----|-----------------|------|

| Operating Supply Voltage on VDD                      | V <sub>DD</sub>     |                | 2.3 <sup>1</sup> | _   | 3.6             | V    |

| Operating Supply Voltage on VIO 3, 4                 | V <sub>IO</sub>     |                | 1.71             |     | V <sub>DD</sub> | V    |

| Operating Supply Voltage on VRE-<br>GIN <sup>1</sup> | V <sub>REGIN</sub>  |                | 3.0 <sup>1</sup> | _   | 5.5             | V    |

| System Clock Frequency                               | f <sub>SYSCLK</sub> |                | 0                | _   | 48              | MHz  |

| Operating Ambient Temperature                        | T <sub>A</sub>      |                | -40              | _   | 85              | °C   |

#### Note:

1. Standard USB compliance tests require 3.0 V on VDD for compliant operation. If using the internal regulator to supply this voltage on VDD, the minimum regulator input voltage is 3.7 V.

2. All voltages with respect to GND.

3. On devices without a VIO pin,  $V_{IO} = V_{DD}$ .

4. GPIO levels are undefined whenever VIO is less than 1 V.

| Parameter                                                   | Symbol              | Test Condition                     | Min | Тур  | Max  | Unit |

|-------------------------------------------------------------|---------------------|------------------------------------|-----|------|------|------|

| ADC0 Always-on <sup>4</sup>                                 | I <sub>ADC</sub>    | 800 ksps, 10-bit conversions or    | _   | 850  | 1085 | μA   |

|                                                             |                     | 200 ksps, 12-bit conversions       |     |      |      |      |

|                                                             |                     | Normal bias settings               |     |      |      |      |

|                                                             |                     | V <sub>DD</sub> = 3.0 V            |     |      |      |      |

|                                                             |                     | 250 ksps, 10-bit conversions or    | _   | 420  | 545  | μA   |

|                                                             |                     | 62.5 ksps 12-bit conversions       |     |      |      |      |

|                                                             |                     | Low power bias settings            |     |      |      |      |

|                                                             |                     | V <sub>DD</sub> = 3.0 V            |     |      |      |      |

| ADC0 Burst Mode, 10-bit single                              | I <sub>ADC</sub>    | 200 ksps, V <sub>DD</sub> = 3.0 V  | _   | 385  | _    | μA   |

| conversions, external reference                             |                     | 100 ksps, V <sub>DD</sub> = 3.0 V  | _   | 193  | _    | μA   |

|                                                             |                     | 10 ksps, V <sub>DD</sub> = 3.0 V   | _   | 20   | _    | μA   |

| ADC0 Burst Mode, 10-bit single                              | I <sub>ADC</sub>    | 200 ksps, V <sub>DD</sub> = 3.0 V  | _   | 495  | _    | μA   |

| conversions, internal reference,<br>Low power bias settings |                     | 100 ksps, V <sub>DD</sub> = 3.0 V  | _   | 250  | _    | μA   |

|                                                             |                     | 10 ksps, V <sub>DD</sub> = 3.0 V   | _   | 25.5 | _    | μA   |

| ADC0 Burst Mode, 12-bit single                              | I <sub>ADC</sub>    | 100 ksps, V <sub>DD</sub> = 3.0 V  |     | 520  | _    | μA   |

| conversions, external reference                             |                     | 50 ksps, V <sub>DD</sub> = 3.0 V   | _   | 260  | _    | μA   |

|                                                             |                     | 10 ksps, V <sub>DD</sub> = 3.0 V   | _   | 53   | _    | μA   |

| ADC0 Burst Mode, 12-bit single                              | I <sub>ADC</sub>    | 100 ksps, V <sub>DD</sub> = 3.0 V, | _   | 970  | _    | μA   |

| conversions, internal reference                             |                     | Normal bias                        |     |      |      |      |

|                                                             |                     | 50 ksps, V <sub>DD</sub> = 3.0 V,  | _   | 425  | _    | μA   |

|                                                             |                     | Low power bias                     |     |      |      | -    |

|                                                             |                     | 10 ksps, V <sub>DD</sub> = 3.0 V,  | _   | 86   | _    | μA   |

|                                                             |                     | Low power bias                     |     |      |      | -    |

| Internal ADC0 Reference, Always-                            | I <sub>VREFFS</sub> | Normal Power Mode                  | _   | 690  | 765  | μA   |

| on <sup>5</sup>                                             |                     | Low Power Mode                     | _   | 166  | 195  | μA   |

| Temperature Sensor                                          | ITSENSE             |                                    | _   | 68   | 110  | μA   |

| Comparator 0 (CMP0, CMP1)                                   | I <sub>CMP</sub>    | CPMD = 11                          | _   | 0.5  | _    | μA   |

|                                                             |                     | CPMD = 10                          | _   | 3    | _    | μA   |

|                                                             |                     | CPMD = 01                          | _   | 9.1  | _    | μA   |

|                                                             |                     | CPMD = 00                          |     | 24.2 | -    | μA   |

| Comparator Reference <sup>6</sup>                           | I <sub>CPREF</sub>  |                                    | _   | 25.3 | -    | μA   |

| Voltage Supply Monitor (VMON0)                              | I <sub>VMON</sub>   |                                    |     | 14   | 20   | μA   |

#### 4.1.4 Flash Memory

| Parameter                                               | Symbol             | Test Condition                 | Min | Тур  | Max | Units  |

|---------------------------------------------------------|--------------------|--------------------------------|-----|------|-----|--------|

| Write Time <sup>1 , 2</sup>                             | t <sub>WRITE</sub> | One Byte,                      | 19  | 20   | 21  | μs     |

|                                                         |                    | F <sub>SYSCLK</sub> = 24.5 MHz |     |      |     |        |

| Erase Time <sup>1, 2</sup>                              | t <sub>ERASE</sub> | One Page,                      | 5.2 | 5.35 | 5.5 | ms     |

|                                                         |                    | F <sub>SYSCLK</sub> = 24.5 MHz |     |      |     |        |

| V <sub>DD</sub> Voltage During Programming <sup>3</sup> | V <sub>PROG</sub>  | 5 V Voltage Regulator used     | 2.7 | _    | 5.5 | V      |

|                                                         |                    | 5 V Voltage Regulator bypassed | 2.3 | —    | 3.6 | V      |

| Endurance (Write/Erase Cycles)                          | N <sub>WE</sub>    |                                | 20k | 100k | _   | Cycles |

| CRC Calculation Time                                    | t <sub>CRC</sub>   | One 256-Byte Block             | _   | 5.5  | _   | μs     |

|                                                         |                    | SYSCLK = 48 MHz                |     |      |     |        |

### Table 4.4. Flash Memory

#### Note:

1. Does not include sequencing time before and after the write/erase operation, which may be multiple SYSCLK cycles.

2. The internal High-Frequency Oscillator 0 has a programmable output frequency, which is factory programmed to 24.5 MHz. If user firmware adjusts the oscillator speed, it must be between 22 and 25 MHz during any flash write or erase operation. It is recommended to write the HFO0CAL register back to its reset value when writing or erasing flash.

3. Flash can be safely programmed at any voltage above the supply monitor threshold (V<sub>VDDM</sub>).

4. Data Retention Information is published in the Quarterly Quality and Reliability Report.

#### 4.1.5 Power Management Timing

### Table 4.5. Power Management Timing

| Parameter                 | Symbol               | Test Condition  | Min | Тур | Max | Units   |

|---------------------------|----------------------|-----------------|-----|-----|-----|---------|

| Idle Mode Wake-up Time    | t <sub>IDLEWK</sub>  |                 | 2   | _   | 3   | SYSCLKs |

| Suspend Mode Wake-up Time | t <sub>SUS-</sub>    | SYSCLK = HFOSC0 | —   | 170 | _   | ns      |

|                           | PENDWK               | CLKDIV = 0x00   |     |     |     |         |

| Snooze Mode Wake-up Time  | t <sub>SLEEPWK</sub> | SYSCLK = HFOSC0 | —   | 12  | _   | μs      |

|                           |                      | CLKDIV = 0x00   |     |     |     |         |

### 4.1.6 Internal Oscillators

| Parameter                     | Symbol                    | Test Condition                    | Min  | Тур  | Max  | Unit   |

|-------------------------------|---------------------------|-----------------------------------|------|------|------|--------|

| High Frequency Oscillator 0 ( | (24.5 MHz)                |                                   |      | 1    |      |        |

| Oscillator Frequency          | f <sub>HFOSC0</sub>       | Full Temperature and Supply Range | 24   | 24.5 | 25   | MHz    |

| Power Supply Sensitivity      | PSS <sub>HFOS</sub><br>co | T <sub>A</sub> = 25 °C            | _    | 0.5  | _    | %/V    |

| Temperature Sensitivity       | TS <sub>HFOSC0</sub>      | V <sub>DD</sub> = 3.0 V           | _    | 40   | _    | ppm/°C |

| High Frequency Oscillator 1 ( | (48 MHz)                  |                                   |      | 1    |      |        |

| Oscillator Frequency          | f <sub>HFOSC1</sub>       | Full Temperature and Supply Range | 47.3 | 48   | 48.7 | MHz    |

| Power Supply Sensitivity      | PSS <sub>HFOS</sub><br>C1 | T <sub>A</sub> = 25 °C            | _    | 0.02 |      | %/V    |

| Temperature Sensitivity       | TS <sub>HFOSC1</sub>      | V <sub>DD</sub> = 3.0 V           | _    | 45   | _    | ppm/°C |

| Low Frequency Oscillator (80  | ) kHz)                    |                                   | 1    | 1    | L    | 1      |

| Oscillator Frequency          | f <sub>LFOSC</sub>        | Full Temperature and Supply Range | 75   | 80   | 85   | kHz    |

| Power Supply Sensitivity      | PSS <sub>LFOSC</sub>      | T <sub>A</sub> = 25 °C            | _    | 0.05 | —    | %/V    |

| Temperature Sensitivity       | TS <sub>LFOSC</sub>       | V <sub>DD</sub> = 3.0 V           | _    | 65   |      | ppm/°C |

#### Table 4.6. Internal Oscillators

### 4.1.7 External Clock Input

### Table 4.7. External Clock Input

| Parameter                           | Symbol             | Test Condition | Min | Тур | Мах | Unit |

|-------------------------------------|--------------------|----------------|-----|-----|-----|------|

| External Input CMOS Clock           | f <sub>CMOS</sub>  |                | 0   | —   | 48  | MHz  |

| Frequency (at EXTCLK pin)           |                    |                |     |     |     |      |

| External Input CMOS Clock High Time | t <sub>CMOSH</sub> |                | 9   | _   | _   | ns   |

| External Input CMOS Clock Low Time  | t <sub>CMOSL</sub> |                | 9   | _   | _   | ns   |

## 4.1.14 Configurable Logic

| Parameter                         | Symbol               | Test Condition               | Min | Тур | Max  | Unit |

|-----------------------------------|----------------------|------------------------------|-----|-----|------|------|

| Propagation Delay through LUT     | t <sub>DLY_LUT</sub> | Through single CLU           | _   | —   | 38.7 | ns   |

|                                   |                      | Using an external pin        |     |     |      |      |

|                                   |                      | Through single CLU           | —   | 1.6 | 5.0  | ns   |

|                                   |                      | Using an internal connection |     |     |      |      |

| Propagation Delay through D flip- | t <sub>DLY_DFF</sub> | Through single CLU           | —   | _   | 38.7 | ns   |

| flop clock                        |                      | Using an external pin        |     |     |      |      |

|                                   |                      | Through single CLU           | _   | 1.4 | 5.6  | ns   |

|                                   |                      | Using an internal connection |     |     |      |      |

| Clocking Frequency                | F <sub>CLK</sub>     | 1 or 2 CLUs Cascaded         | _   | _   | 48   | MHz  |

|                                   |                      | 3 or 4 CLUs Cascaded         | —   | —   | 48   | MHz  |

### Table 4.14. Configurable Logic

#### 4.1.17 SMBus

| Parameter                                       | Symbol               | Test Condition | Min              | Тур | Мах              | Unit |

|-------------------------------------------------|----------------------|----------------|------------------|-----|------------------|------|

| Standard Mode (100 kHz Class)                   |                      |                |                  |     |                  |      |

| I2C Operating Frequency                         | f <sub>I2C</sub>     |                | 0                | —   | 70 <sup>2</sup>  | kHz  |

| SMBus Operating Frequency                       | f <sub>SMB</sub>     |                | 40 <sup>1</sup>  | _   | 70 <sup>2</sup>  | kHz  |

| Bus Free Time Between STOP and START Conditions | t <sub>BUF</sub>     |                | 9.4              | _   | -                | μs   |

| Hold Time After (Repeated)<br>START Condition   | t <sub>HD:STA</sub>  |                | 4.7              | _   | _                | μs   |

| Repeated START Condition Setup<br>Time          | t <sub>SU:STA</sub>  |                | 9.4              | _   | _                | μs   |

| STOP Condition Setup Time                       | t <sub>su:sтo</sub>  |                | 9.4              | —   | _                | μs   |

| Data Hold Time                                  | t <sub>HD:DAT</sub>  |                | 275 <sup>3</sup> | _   | _                | ns   |

| Data Setup Time                                 | t <sub>SU:DAT</sub>  |                | 300 <sup>3</sup> | _   | _                | ns   |

| Detect Clock Low Timeout                        | t <sub>TIMEOUT</sub> |                | 25               | —   | _                | ms   |

| Clock Low Period                                | t <sub>LOW</sub>     |                | 4.7              |     | _                | μs   |

| Clock High Period                               | t <sub>HIGH</sub>    |                | 9.4              | _   | 50 <sup>4</sup>  | μs   |

| Fast Mode (400 kHz Class)                       | 1                    |                |                  |     |                  | 1    |

| I2C Operating Frequency                         | f <sub>I2C</sub>     |                | 0                | _   | 255 <sup>2</sup> | kHz  |

| SMBus Operating Frequency                       | f <sub>SMB</sub>     |                | 40 <sup>1</sup>  | —   | 255 <sup>2</sup> | kHz  |

| Bus Free Time Between STOP and START Conditions | t <sub>BUF</sub>     |                | 2.6              | _   | _                | μs   |

| Hold Time After (Repeated)<br>START Condition   | t <sub>HD:STA</sub>  |                | 1.3              | —   | -                | μs   |

| Repeated START Condition Setup<br>Time          | t <sub>SU:STA</sub>  |                | 2.6              | _   | -                | μs   |

| STOP Condition Setup Time                       | t <sub>SU:STO</sub>  |                | 2.6              | —   | _                | μs   |

| Data Hold Time                                  | t <sub>HD:DAT</sub>  |                | 275 <sup>3</sup> | —   | _                | ns   |

| Data Setup Time                                 | t <sub>SU:DAT</sub>  |                | 300 <sup>3</sup> | _   | _                | ns   |

| Detect Clock Low Timeout                        | t <sub>TIMEOUT</sub> |                | 25               | _   | _                | ms   |

| Clock Low Period                                | t <sub>LOW</sub>     |                | 1.3              | _   | -                | μs   |

| Clock High Period                               | t <sub>HIGH</sub>    |                | 2.6              | —   | 50 <sup>4</sup>  | μs   |

| Fast Mode Plus (1 MHz Class)                    |                      | ,              | 1                |     |                  |      |

| I2C Operating Frequency                         | f <sub>I2C</sub>     |                | 0                | _   | 666 <sup>2</sup> | kHz  |

| SMBus Operating Frequency                       | f <sub>SMB</sub>     |                | 40 <sup>1</sup>  | _   | 666 <sup>2</sup> | kHz  |

| Bus Free Time Between STOP and START Conditions | t <sub>BUF</sub>     |                | 0.67             | _   | -                | μs   |

### Table 4.17. SMBus Peripheral Timing Performance (Master Mode)

#### 4.3 Absolute Maximum Ratings

Stresses above those listed in 4.3 Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the devices at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability. For more information on the available quality and reliability data, see the Quality and Reliability Monitor Report at http://www.silabs.com/support/quality/pages/default.aspx.

#### Table 4.20. Absolute Maximum Ratings

| Parameter                                         | Symbol             | Test Condition          | Min     | Мах                  | Unit |

|---------------------------------------------------|--------------------|-------------------------|---------|----------------------|------|

| Ambient Temperature Under Bias                    | T <sub>BIAS</sub>  |                         | -55     | 125                  | °C   |

| Storage Temperature                               | T <sub>STG</sub>   |                         | -65     | 150                  | °C   |

| Voltage on VDD                                    | V <sub>DD</sub>    |                         | GND-0.3 | 4.2                  | V    |

| Voltage on VIO <sup>2</sup>                       | V <sub>IO</sub>    |                         | GND-0.3 | 4.2                  | V    |

| Voltage on VREGIN                                 | V <sub>REGIN</sub> |                         | GND-0.3 | 5.8                  | V    |

| Voltage on D+ or D- <sup>2</sup>                  | V <sub>USBD</sub>  |                         | GND-0.3 | V <sub>DD</sub> +0.3 | V    |

| Voltage on I/O pins (including VBUS /             | V <sub>IN</sub>    | V <sub>IO</sub> > 3.3 V | GND-0.3 | 5.8                  | V    |

| P2.1) or RSTb <sup>2</sup>                        |                    | V <sub>IO</sub> < 3.3 V | GND-0.3 | V <sub>IO</sub> +2.5 | V    |

| Total Current Sunk into Supply Pin                | I <sub>VDD</sub>   |                         | -       | 400                  | mA   |

| Total Current Sourced out of Ground<br>Pin        | I <sub>GND</sub>   |                         | 400     | -                    | mA   |

| Current Sourced or Sunk by any I/O<br>Pin or RSTb | I <sub>IO</sub>    |                         | -100    | 100                  | mA   |

| Operating Junction Temperature                    | TJ                 |                         | -40     | 105                  | °C   |

#### Note:

1. Exposure to maximum rating conditions for extended periods may affect device reliability.

2. On devices without a VIO pin,  $V_{IO}$  =  $V_{DD}$ .

### 5. Typical Connection Diagrams

### 5.1 Power

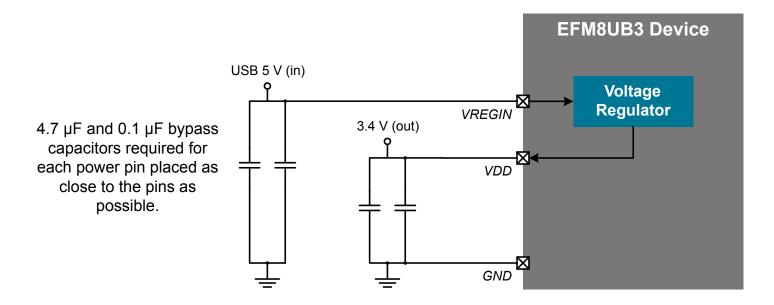

The figure below shows a typical connection diagram for the power pins of the EFM8UB3 devices when the internal regulator used and USB is connected (bus-powered).

Figure 5.1. Connection Diagram with Voltage Regulator Used and USB Connected (Bus-Powered)

| Pin<br>Number | Pin Name | Description          | Crossbar Capability | Additional Digital<br>Functions | Analog Functions |

|---------------|----------|----------------------|---------------------|---------------------------------|------------------|

| 1             | P0.2     | Multifunction I/O    | Yes                 | P0MAT.2                         | ADC0.2           |

|               |          |                      |                     | INT0.2                          | CMP0P.2          |

|               |          |                      |                     | INT1.2                          | CMP0N.2          |

|               |          |                      |                     | CLU2B.7                         |                  |

|               |          |                      |                     | CLU3B.6                         |                  |

|               |          |                      |                     | CLU0OUT                         |                  |

| 2             | P0.1     | Multifunction I/O    | Yes                 | P0MAT.1                         | ADC0.1           |

|               |          |                      |                     | INT0.1                          | CMP0P.1          |

|               |          |                      |                     | INT1.1                          | CMP0N.1          |

|               |          |                      |                     | CLU0A.6                         | AGND             |

|               |          |                      |                     | CLU3A.7                         |                  |

| 3             | P0.0     | Multifunction I/O    | Yes                 | P0MAT.0                         | ADC0.0           |

|               |          |                      |                     | INT0.0                          | CMP0P.0          |

|               |          |                      |                     | INT1.0                          | CMP0N.0          |

|               |          |                      |                     |                                 | VREF             |

| 4             | GND      | Ground               |                     |                                 | ADC0.19          |

| 5             | D+       | USB Data Positive    |                     |                                 | ADC0.28          |

| 6             | D-       | USB Data Negative    |                     |                                 | ADC0.29          |

| 7             | VIO      | I/O Power Input      |                     |                                 |                  |

| 8             | VDD      | Supply Power Input / |                     |                                 | ADC0.18          |

|               |          | 5V Regulator Output  |                     |                                 |                  |

| 9             | VREGIN   | 5V Regulator Input   |                     |                                 |                  |

| 10            | P2.1     | Multifunction I/O    |                     | VBUS                            | ADC0.24          |

|               |          |                      |                     |                                 | CMP1P.13         |

|               |          |                      |                     |                                 | CMP1N.13         |

| 11            | RSTb /   | Active-low Reset /   |                     |                                 |                  |

|               | C2CK     | C2 Debug Clock       |                     |                                 |                  |

| 12            | P2.0 /   | Multifunction I/O /  |                     |                                 |                  |

|               | C2D      | C2 Debug Data        |                     |                                 |                  |

| 13            | P1.6     | Multifunction I/O    | Yes                 | CLU0A.7                         | ADC0.14          |

|               |          |                      |                     |                                 | CMP1P.6          |

|               |          |                      |                     |                                 | CMP1N.6          |

### Table 6.1. Pin Definitions for EFM8UB3x-QSOP24

| Pin<br>Number | Pin Name | Description       | Crossbar Capability | Additional Digital<br>Functions | Analog Functions |

|---------------|----------|-------------------|---------------------|---------------------------------|------------------|

| 12            | P1.5     | Multifunction I/O | Yes                 |                                 | ADC0.13          |

|               |          |                   |                     |                                 | CMP1P.5          |

|               |          |                   |                     |                                 | CMP1N.5          |

| 15            | P1.4     | Multifunction I/O | Yes                 | P1MAT.4                         | ADC0.12          |

|               |          |                   |                     |                                 | CMP1P.4          |

|               |          |                   |                     |                                 | CMP1N.4          |

| 16            | P1.3     | Multifunction I/O | Yes                 | P1MAT.3                         | ADC0.11          |

|               |          |                   |                     |                                 | CMP1P.3          |

|               |          |                   |                     |                                 | CMP1N.3          |

| 17            | P1.2     | Multifunction I/O | Yes                 | P1MAT.2                         | ADC0.10          |

|               |          |                   |                     |                                 | CMP1P.2          |

|               |          |                   |                     |                                 | CMP1N.2          |

| 18            | P1.1     | Multifunction I/O | Yes                 | P1MAT.1                         | ADC0.9           |

|               |          |                   |                     |                                 | CMP1P.1          |

|               |          |                   |                     |                                 | CMP1N.1          |

| 19            | P1.0     | Multifunction I/O | Yes                 | P1MAT.0                         | ADC0.8           |

|               |          |                   |                     | CLU0B.6                         | CMP1P.0          |

|               |          |                   |                     | CLU2A.7                         | CMP1N.0          |

|               |          |                   |                     | CLU3OUT                         |                  |

| 20            | P0.7     | Multifunction I/O | Yes                 | P0MAT.7                         | ADC0.7           |

|               |          |                   |                     | INT0.7                          | CMP0P.7          |

|               |          |                   |                     | INT1.7                          | CMP0N.7          |

|               |          |                   |                     | CLU1A.7                         |                  |

|               |          |                   |                     | CLU3A.6                         |                  |

| 21            | P0.6     | Multifunction I/O | Yes                 | P0MAT.6                         | ADC0.6           |

|               |          |                   |                     | CNVSTR                          | CMP0P.6          |

|               |          |                   |                     | INT0.6                          | CMP0N.6          |

|               |          |                   |                     | INT1.6                          |                  |

|               |          |                   |                     | CLU1B.6                         |                  |

|               |          |                   |                     | CLU2OUT                         |                  |

| 22            | P0.5     | Multifunction I/O | Yes                 | P0MAT.5                         | ADC0.5           |

|               |          |                   |                     | INT0.5                          | CMP0P.5          |

|               |          |                   |                     | INT1.5                          | CMP0N.5          |

|               |          |                   |                     | UART1_RX                        |                  |

|               |          |                   |                     | CLU1B.7                         |                  |

|               |          |                   |                     | CLU2A.6                         |                  |

| Pin<br>Number | Pin Name | Description       | Crossbar Capability | Additional Digital<br>Functions | Analog Functions |

|---------------|----------|-------------------|---------------------|---------------------------------|------------------|

| 23            | P0.4     | Multifunction I/O | Yes                 | P0MAT.4                         | ADC0.4           |

|               |          |                   |                     | INT0.4                          | CMP0P.4          |

|               |          |                   |                     | INT1.4                          | CMP0N.4          |

|               |          |                   |                     | CLU0B.7                         |                  |

|               |          |                   |                     | CLU2B.6                         |                  |

|               |          |                   |                     | CLU1OUT                         |                  |

|               |          |                   |                     | UART1_TX                        |                  |

| 24            | P0.3     | Multifunction I/O | Yes                 | P0MAT.3                         | ADC0.3           |

|               |          |                   |                     | EXTCLK                          | CMP0P.3          |

|               |          |                   |                     | INT0.3                          | CMP0N.3          |

|               |          |                   |                     | INT1.3                          |                  |

|               |          |                   |                     | CLU1A.6                         |                  |

|               |          |                   |                     | CLU3B.7                         |                  |

| Pin         | Pin Name | Description          | Crossbar Capability | Additional Digital<br>Functions | Analog Functions |

|-------------|----------|----------------------|---------------------|---------------------------------|------------------|

| Number<br>2 | P0.0     | Multifunction I/O    | Yes                 | POMAT.0                         | ADC0.0           |

| -           |          |                      |                     | INT0.0                          | CMP0P.0          |

|             |          |                      |                     | INT1.0                          | CMP0N.0          |

|             |          |                      |                     |                                 | VREF             |

| 3           | GND      | Ground               |                     |                                 | ADC0.19          |

| 4           | D+       | USB Data Positive    |                     |                                 | ADC0.28          |

| 5           | D-       | USB Data Negative    |                     |                                 | ADC0.29          |

| 6           | VDD      | Supply Power Input / |                     |                                 | ADC0.18          |

| 0           |          | 5V Regulator Output  |                     |                                 |                  |

| 7           | VREGIN   | 5V Regulator Input   |                     |                                 |                  |

| 8           | P2.1     | Multifunction I/O    |                     | VBUS                            | ADC0.24          |

|             |          |                      |                     |                                 | CMP1P.13         |

|             |          |                      |                     |                                 | CMP1N.13         |

| 9           | RSTb /   | Active-low Reset /   |                     |                                 |                  |

|             | C2CK     | C2 Debug Clock       |                     |                                 |                  |

| 10          | P2.0 /   | Multifunction I/O /  |                     |                                 |                  |

|             | C2D      | C2 Debug Data        |                     |                                 |                  |

| 11          | P1.2     | Multifunction I/O    | Yes                 | P1MAT.2                         | ADC0.10          |

|             |          |                      |                     |                                 | CMP1P.2          |

|             |          |                      |                     |                                 | CMP1N.2          |

| 12          | GND      | Ground               |                     |                                 |                  |

| 13          | P1.1     | Multifunction I/O    | Yes                 | P1MAT.1                         | ADC0.9           |

|             |          |                      |                     |                                 | CMP1P.1          |

|             |          |                      |                     |                                 | CMP1N.1          |

| 14          | P1.0     | Multifunction I/O    | Yes                 | P1MAT.0                         | ADC0.8           |

|             |          |                      |                     | CLU0B.6                         | CMP1P.0          |

|             |          |                      |                     | CLU2A.7                         | CMP1N.0          |

|             |          |                      |                     | CLU3OUT                         |                  |

| 15          | P0.7     | Multifunction I/O    | Yes                 | P0MAT.7                         | ADC0.7           |

|             |          |                      |                     | INT0.7                          | CMP0P.7          |

|             |          |                      |                     | INT1.7                          | CMP0N.7          |

|             |          |                      |                     | CLU1A.7                         |                  |

|             |          |                      |                     | CLU3A.6                         |                  |

| Pin<br>Number | Pin Name | Description       | Crossbar Capability | Additional Digital<br>Functions | Analog Functions |

|---------------|----------|-------------------|---------------------|---------------------------------|------------------|

| 16            | P0.6     | Multifunction I/O | Yes                 | P0MAT.6                         | ADC0.6           |

|               |          |                   |                     | CNVSTR                          | CMP0P.6          |

|               |          |                   |                     | INT0.6                          | CMP0N.6          |

|               |          |                   |                     | INT1.6                          |                  |

|               |          |                   |                     | CLU1B.6                         |                  |

|               |          |                   |                     | CLU2OUT                         |                  |

| 17            | P0.5     | Multifunction I/O | Yes                 | P0MAT.5                         | ADC0.5           |

|               |          |                   |                     | INT0.5                          | CMP0P.5          |

|               |          |                   |                     | INT1.5                          | CMP0N.5          |

|               |          |                   |                     | UART1_RX                        |                  |

|               |          |                   |                     | CLU1B.7                         |                  |

|               |          |                   |                     | CLU2A.6                         |                  |

| 18            | P0.4     | Multifunction I/O | Yes                 | P0MAT.4                         | ADC0.4           |

|               |          |                   |                     | INT0.4                          | CMP0P.4          |

|               |          |                   |                     | INT1.4                          | CMP0N.4          |

|               |          |                   |                     | CLU0B.7                         |                  |

|               |          |                   |                     | CLU2B.6                         |                  |

|               |          |                   |                     | CLU1OUT                         |                  |

|               |          |                   |                     | UART1_TX                        |                  |

| 19            | P0.3     | Multifunction I/O | Yes                 | P0MAT.3                         | ADC0.3           |

|               |          |                   |                     | EXTCLK                          | CMP0P.3          |

|               |          |                   |                     | INT0.3                          | CMP0N.3          |

|               |          |                   |                     | INT1.3                          |                  |

|               |          |                   |                     | CLU1A.6                         |                  |

|               |          |                   |                     | CLU3B.7                         |                  |

| 20            | P0.2     | Multifunction I/O | Yes                 | P0MAT.2                         | ADC0.2           |

|               |          |                   |                     | INT0.2                          | CMP0P.2          |

|               |          |                   |                     | INT1.2                          | CMP0N.2          |

|               |          |                   |                     | CLU2B.7                         |                  |

|               |          |                   |                     | CLU3B.6                         |                  |

|               |          |                   |                     | CLU0OUT                         |                  |

| Center        | GND      | Ground            |                     |                                 |                  |

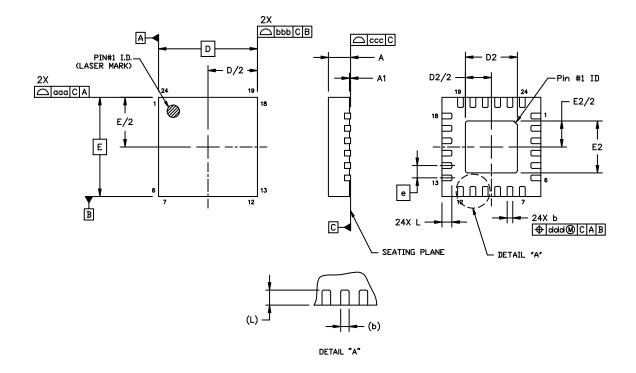

# 7. QFN24 Package Specifications

### 7.1 QFN24 Package Dimensions

| Table 7.1. | QFN24 Package Dimensions |

|------------|--------------------------|

|            |                          |

| Dimension | Min            | Тур  | Мах  |

|-----------|----------------|------|------|

| A         | 0.70           | 0.75 | 0.80 |

| A1        | 0.00           | —    | 0.05 |

| b         | 0.18           | 0.25 | 0.30 |

| D         | 4.00 BSC       |      |      |

| D2        | 2.35           | 2.45 | 2.55 |

| е         | 0.50 BSC       |      |      |

| E         | 4.00 BSC       |      |      |

| E2        | 2.35 2.45 2.55 |      | 2.55 |

| L         | 0.30           | 0.40 | 0.50 |

| ааа       | _              | _    | 0.10 |

| bbb       | —              | —    | 0.10 |

| ссс       | _              |      | 0.08 |

| ddd       | _              |      | 0.10 |

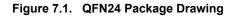

#### 7.2 PCB Land Pattern

Figure 7.2. PCB Land Pattern Drawing

### Table 7.2. PCB Land Pattern Dimensions

| Dimension | Min | Мах |

|-----------|-----|-----|

| C1        | 3.9 | 90  |

| C2        | 3.9 | 90  |

| E         | 0.5 | 50  |

| X1        | 0.3 | 30  |

| X2        | 2.5 | 55  |

| Y1        | 0.8 | 35  |

| Y2        | 2.5 | 55  |

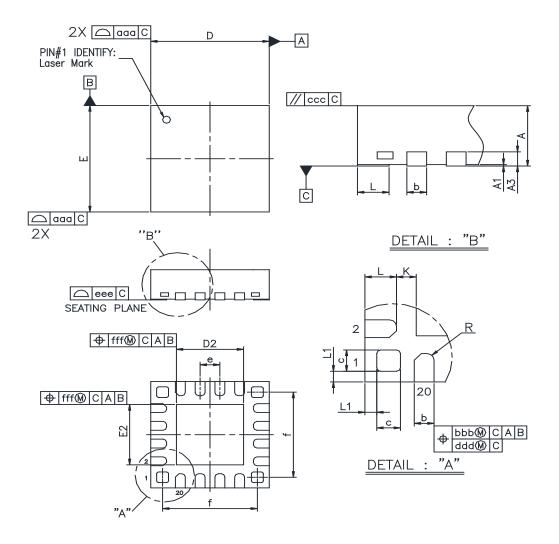

## 9. QFN20 Package Specifications

### 9.1 QFN20 Package Dimensions

| Dimension | Min      | Тур  | Мах  |

|-----------|----------|------|------|

| A         | 0.70     | 0.75 | 0.80 |

| A1        | 0.00     | 0.02 | 0.05 |

| A3        | 0.20 REF |      |      |

| b         | 0.18     | 0.25 | 0.30 |

| С         | 0.25     | 0.30 | 0.35 |

| D         | 3.00 BSC |      |      |

| D2        | 1.6      | 1.70 | 1.80 |

| е         | 0.50 BSC |      |      |

| E         | 3.00 BSC |      |      |

| Dimension | Min      | Тур      | Мах  |

|-----------|----------|----------|------|

| E2        | 1.60     | 1.70     | 1.80 |

| f         | 2.50 BSC |          |      |

| L         | 0.30     | 0.40     | 0.50 |

| К         |          | 0.25 REF |      |

| R         | 0.09     | 0.125    | 0.15 |

| ааа       | 0.15     |          |      |

| bbb       | 0.10     |          |      |

| ссс       | 0.10     |          |      |

| ddd       | 0.05     |          |      |

| eee       | 0.08     |          |      |

| fff       | 0.10     |          |      |

### Note:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

3. The drawing complies with JEDEC MO-220.

4. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

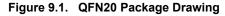

#### 9.2 QFN20 PCB Land Pattern

| Dimension | Min  | Мах  |  |

|-----------|------|------|--|

| C1        | 3.10 |      |  |

| C2        | 3.10 |      |  |

| C3        | 2.5  | 50   |  |

| C4        | 2.5  | 50   |  |

| E         | 0.50 |      |  |

| X1        | 0.30 |      |  |

| X2        | 0.25 | 0.35 |  |

| Х3        | 1.8  | 80   |  |

| Y1        | 0.90 |      |  |

| Y2        | 0.25 | 0.35 |  |

| Y3        | 1.8  | 80   |  |

| Table 9.2. | QFN20 PCB Land Pattern Dimensions |

|------------|-----------------------------------|

|------------|-----------------------------------|