Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Product Status             | Not For New Designs                                                             |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | C166SV2                                                                         |

| Core Size                  | 16/32-Bit                                                                       |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                       |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                            |

| Number of I/O              | 33                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                       |

| Data Converters            | A/D 8x12b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 48-VFQFN Exposed Pad                                                            |

| Supplier Device Package    | PG-VQFN-48-54                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xe161fu8f40vaakxuma1 |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 4.7.2<br>4.7.2.1<br>4.7.2.2<br>4.7.2.3<br>4.7.3<br>4.7.4<br>4.7.5<br>4.7.6 | Definition of Internal Timing       7         Phase Locked Loop (PLL)       7         Wakeup Clock       7         Selecting and Changing the Operating Frequency       7         External Clock Input Parameters       7         Pad Properties       8         Synchronous Serial Interface Timing       8         Debug Interface Timing       8 | 75<br>78<br>79<br>31<br>34 |

|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| <b>5</b><br>5.1<br>5.2<br>5.3                                              | Package and Reliability9Packaging9Thermal Considerations9Quality Declarations9                                                                                                                                                                                                                                                                      | 95<br>97                   |

### **Summary of Features**

### 1.2 Definition of Feature Variants

The XE161FU types are offered with several Flash memory sizes. **Table 3** and **Table 4** describe the location of the available Flash memory.

### Table 3 Continuous Flash Memory Ranges

| Total Flash Size                                       | 1st Range <sup>1)</sup>                      | 2nd Range                                    | 3rd Range |

|--------------------------------------------------------|----------------------------------------------|----------------------------------------------|-----------|

| 64 Kbytes                                              | C0'0000 <sub>H</sub><br>C0'EFFF <sub>H</sub> | C1'0000 <sub>H</sub><br>C1'0FFF <sub>H</sub> | n.a.      |

| 32 Kbytes C0'0000 <sub>H</sub><br>C0'7FFF <sub>F</sub> |                                              | n.a.                                         | n.a.      |

1) The uppermost 4-Kbyte sector of the first Flash segment is reserved for internal use (C0'F000<sub>H</sub> to C0'FFFF<sub>H</sub>).

#### Table 4 Flash Memory Module Allocation (in Kbytes)

| Total Flash Size | Flash 0 <sup>1)</sup> | Flash 1 |  |

|------------------|-----------------------|---------|--|

| 64               | 64                    | n.a.    |  |

| 32               | 32                    | n.a.    |  |

1) The uppermost 4-Kbyte sector of the first Flash segment is reserved for internal use (C0'F000<sub>H</sub> to C0'FFFF<sub>H</sub>).

The XE161FU types are offered with different interface options. **Table 5** lists the available channels for each option.

### Table 5 Interface Channel Association

| Total Number      | Available Channels / Message Objects                 |  |  |  |  |

|-------------------|------------------------------------------------------|--|--|--|--|

| 10 ADC0 channels  | CH0, CH2, CH3, CH4, CH8, CH9, CH16, CH17, CH19, CH20 |  |  |  |  |

| 2 serial channels | U0C0, U0C1                                           |  |  |  |  |

### **General Device Information**

### Key to Pin Definitions

- Ctrl.: The output signal for a port pin is selected by bit field PC in the associated register Px\_IOCRy. Output O0 is selected by setting the respective bit field PC to 1x00<sub>B</sub>, output O1 is selected by 1x01<sub>B</sub>, etc.

Output signal OH is controlled by hardware.

- Type: Indicates the pad type and its power supply domain (B, M).

- St: Standard pad

- Sp: Special pad e.g. XTALx

- DA: Digital IO and analog input

- In: Input only pad

- PS: Power supply pad

| Pin | Symbol           | Ctrl.  | Туре | Function                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|-----|------------------|--------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1   | TESTM            | I      | In/B | <b>Testmode Enable</b><br>Enables factory test modes, must be held HIGH for<br>normal operation (connect to $V_{\rm DDPB}$ ).<br>An internal pullup device will hold this pin high<br>when nothing is driving it.                                                                                                                                          |  |  |  |

| 2   | TRST             | 1      | In/B | Test-System Reset Input<br>For normal system operation, pin TRST should be<br>held low. A high level at this pin at the rising edge<br>of PORST activates the XE161FU's debug<br>system. In this case, pin TRST must be driven low<br>once to reset the debug system.<br>An internal pulldown device will hold this pin low<br>when nothing is driving it. |  |  |  |

| 3   | P6.3             | O0 / I | St/B | Bit 3 of Port 6, General Purpose Input/Output                                                                                                                                                                                                                                                                                                              |  |  |  |

|     | T3OUT            | O2     | St/B | GPT12E Timer T3 Toggle Latch Output                                                                                                                                                                                                                                                                                                                        |  |  |  |

|     | ADC0_REQT<br>RyF | I      | St/B | External Request Trigger Input for ADC0/1                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 4   | P6.1             | O0 / I | DA/B | Bit 1 of Port 6, General Purpose Input/Output                                                                                                                                                                                                                                                                                                              |  |  |  |

|     | ADC0_CH17        | I      | DA/B | Analog Input Channel 17 for ADC0                                                                                                                                                                                                                                                                                                                           |  |  |  |

|     | EMUX1            | O1     | DA/B | External Analog MUX Control Output 1 (ADC0)                                                                                                                                                                                                                                                                                                                |  |  |  |

|     | T3OUT            | O2     | DA/B | GPT12E Timer T3 Toggle Latch Output                                                                                                                                                                                                                                                                                                                        |  |  |  |

|     | ADC0_REQT<br>RyE | I      | DA/B | External Request Trigger Input for ADC0                                                                                                                                                                                                                                                                                                                    |  |  |  |

|     | ESR1_6           | I      | DA/B | ESR1 Trigger Input 6                                                                                                                                                                                                                                                                                                                                       |  |  |  |

### Table 6 Pin Definitions and Functions

### **General Device Information**

| Table | Table 6         Pin Definitions and Functions (cont'd) |        |      |                                                |  |  |  |

|-------|--------------------------------------------------------|--------|------|------------------------------------------------|--|--|--|

| Pin   | Symbol                                                 | Ctrl.  | Туре | Function                                       |  |  |  |

| 5     | P6.0                                                   | O0 / I | DA/B | Bit 0 of Port 6, General Purpose Input/Output  |  |  |  |

|       | ADC0_CH16                                              | I      | DA/B | Analog Input Channel 16 for ADC0               |  |  |  |

|       | EMUX0                                                  | O1     | DA/B | External Analog MUX Control Output 0 (ADC0)    |  |  |  |

|       | BRKOUT                                                 | O3     | DA/B | OCDS Break Signal Output                       |  |  |  |

|       | ADC0_REQG<br>TyG                                       | I      | DA/B | External Request Gate Input for ADC0           |  |  |  |

| 10    | P5.0                                                   | I      | In/B | Bit 0 of Port 5, General Purpose Input         |  |  |  |

|       | ADC0_CH0                                               | I      | In/B | Analog Input Channel 0 for ADC0                |  |  |  |

| 11    | P5.2                                                   | 1      | In/B | Bit 2 of Port 5, General Purpose Input         |  |  |  |

|       | ADC0_CH2                                               | I      | In/B | Analog Input Channel 2 for ADC0                |  |  |  |

|       | TDI_A                                                  | I      | In/B | JTAG Test Data Input                           |  |  |  |

| 12    | P5.3                                                   | I      | In/B | Bit 3 of Port 5, General Purpose Input         |  |  |  |

|       | ADC0_CH3                                               | I      | In/B | Analog Input Channel 3 for ADC0                |  |  |  |

|       | T3INA                                                  | I      | In/B | GPT12E Timer T3 Count/Gate Input               |  |  |  |

| 13    | P5.4                                                   | I      | In/B | Bit 4 of Port 5, General Purpose Input         |  |  |  |

|       | ADC0_CH4                                               | I      | In/B | Analog Input Channel 4 for ADC0                |  |  |  |

|       | T3EUDA                                                 | I      | In/B | GPT12E Timer T3 External Up/Down Control Input |  |  |  |

|       | TMS_A                                                  | 1      | In/B | JTAG Test Mode Selection Input                 |  |  |  |

| 14    | P5.8                                                   | I      | In/B | Bit 8 of Port 5, General Purpose Input         |  |  |  |

|       | ADC0_CH8                                               | I      | In/B | Analog Input Channel 8 for ADC0                |  |  |  |

|       | CCU60_T12<br>HRC                                       | I      | In/B | External Run Control Input for T12 of CCU60    |  |  |  |

|       | CCU60_T13<br>HRC                                       | I      | In/B | External Run Control Input for T13 of CCU60    |  |  |  |

| 15    | P5.9                                                   | I      | In/B | Bit 9 of Port 5, General Purpose Input         |  |  |  |

|       | ADC0_CH9                                               | I      | In/B | Analog Input Channel 9 for ADC0                |  |  |  |

|       | CC2_T7IN                                               | I      | In/B | CAPCOM2 Timer T7 Count Input                   |  |  |  |

| 16    | P2.0                                                   | O0 / I | DA/B | Bit 0 of Port 2, General Purpose Input/Output  |  |  |  |

|       | ADC0_CH19                                              | I      | DA/B | Analog Input Channel 19 for ADC0               |  |  |  |

|       | T5INB                                                  | I      | DA/B | GPT12E Timer T5 Count/Gate Input               |  |  |  |

# **General Device Information**

| Tabl |                   | 1      |      | Functions (cont'd)                             |

|------|-------------------|--------|------|------------------------------------------------|

| Pin  | Symbol            | Ctrl.  | Туре |                                                |

| 33   | P10.2             | O0 / I | St/B | Bit 2 of Port 10, General Purpose Input/Output |

|      | U0C0_SCLK<br>OUT  | O1     | St/B | USIC0 Channel 0 Shift Clock Output             |

|      | CCU60_CC6<br>2    | O2     | St/B | CCU60 Channel 2 Output                         |

|      | CCU60_CC6<br>2INA | I      | St/B | CCU60 Channel 2 Input                          |

|      | U0C0_DX1B         | I      | St/B | USIC0 Channel 0 Shift Clock Input              |

| 34   | P10.3             | O0 / I | St/B | Bit 3 of Port 10, General Purpose Input/Output |

|      | CCU60_COU<br>T60  | O2     | St/B | CCU60 Channel 0 Output                         |

|      | U0C0_DX2A         | I      | St/B | USIC0 Channel 0 Shift Control Input            |

|      | U0C1_DX2A         | I      | St/B | USIC0 Channel 1 Shift Control Input            |

| 35   | P10.4             | O0 / I | St/B | Bit 4 of Port 10, General Purpose Input/Output |

|      | U0C0_SELO<br>3    | O1     | St/B | USIC0 Channel 0 Select/Control 3 Output        |

|      | CCU60_COU<br>T61  | O2     | St/B | CCU60 Channel 1 Output                         |

|      | U0C0_DX2B         | I      | St/B | USIC0 Channel 0 Shift Control Input            |

|      | U0C1_DX2B         | I      | St/B | USIC0 Channel 1 Shift Control Input            |

|      | ESR1_9            | I      | St/B | ESR1 Trigger Input 9                           |

| 36   | P10.5             | O0 / I | St/B | Bit 5 of Port 10, General Purpose Input/Output |

|      | U0C1_SCLK<br>OUT  | O1     | St/B | USIC0 Channel 1 Shift Clock Output             |

|      | CCU60_COU<br>T62  | O2     | St/B | CCU60 Channel 2 Output                         |

|      | U0C1_DX1B         | I      | St/B | USIC0 Channel 1 Shift Clock Input              |

| 37   | P10.6             | O0 / I | St/B | Bit 6 of Port 10, General Purpose Input/Output |

|      | U0C0_DOUT         | O1     | St/B | USIC0 Channel 0 Shift Data Output              |

|      | U0C0_DX0C         | I      | St/B | USIC0 Channel 0 Shift Data Input               |

|      | CCU60_CTR<br>APA  | I      | St/B | CCU60 Emergency Trap Input                     |

# **General Device Information**

| Table | Table 6         Pin Definitions and Functions (cont'd) |        |      |                                                   |  |  |

|-------|--------------------------------------------------------|--------|------|---------------------------------------------------|--|--|

| Pin   | Symbol                                                 | Ctrl.  | Туре | Function                                          |  |  |

| 38    | P10.7                                                  | O0 / I | St/B | Bit 7 of Port 10, General Purpose Input/Output    |  |  |

|       | U0C1_DOUT                                              | O1     | St/B | USIC0 Channel 1 Shift Data Output                 |  |  |

|       | CCU60_COU<br>T63                                       | O2     | St/B | CCU60 Channel 3 Output                            |  |  |

|       | U0C1_DX0B                                              | I      | St/B | USIC0 Channel 1 Shift Data Input                  |  |  |

|       | CCU60_CCP<br>OS0A                                      | 1      | St/B | CCU60 Position Input 0                            |  |  |

|       | T4INB                                                  | I      | St/B | GPT12E Timer T4 Count/Gate Input                  |  |  |

| 39    | P10.8                                                  | O0 / I | St/B | Bit 8 of Port 10, General Purpose Input/Output    |  |  |

|       | U0C0_MCLK<br>OUT                                       | 01     | St/B | USIC0 Channel 0 Master Clock Output               |  |  |

| -     | U0C1_SELO<br>0                                         | O2     | St/B | USIC0 Channel 1 Select/Control 0 Output           |  |  |

|       | CCU60_CCP<br>OS1A                                      | 1      | St/B | CCU60 Position Input 1                            |  |  |

|       | U0C0_DX1C                                              | I      | St/B | USIC0 Channel 0 Shift Clock Input                 |  |  |

|       | BRKIN_B                                                | I      | St/B | OCDS Break Signal Input                           |  |  |

|       | T3EUDB                                                 | I      | St/B | GPT12E Timer T3 External Up/Down Control<br>Input |  |  |

|       | ESR2_11                                                | I      | St/B | ESR2 Trigger Input 11                             |  |  |

| 40    | P10.9                                                  | O0 / I | St/B | Bit 9 of Port 10, General Purpose Input/Output    |  |  |

|       | U0C0_SELO<br>4                                         | O1     | St/B | USIC0 Channel 0 Select/Control 4 Output           |  |  |

|       | U0C1_MCLK<br>OUT                                       | O2     | St/B | USIC0 Channel 1 Master Clock Output               |  |  |

|       | CCU60_CCP<br>OS2A                                      | 1      | St/B | CCU60 Position Input 2                            |  |  |

|       | TCK_B                                                  | I      | St/B | DAP0/JTAG Clock Input                             |  |  |

|       | T3INB                                                  | I      | St/B | GPT12E Timer T3 Count/Gate Input                  |  |  |

# **General Device Information**

| Pin             | Symbol            | Ctrl. | Туре | Function                                                                                                                                                                            |

|-----------------|-------------------|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18,<br>43       | V <sub>DDIM</sub> | -     | PS/M | <b>Digital Core Supply Voltage for Domain M</b><br>Decouple with a ceramic capacitor, see Data<br>Sheet for details.<br>All $V_{\text{DDIM}}$ pins must be connected to each other. |

| 7,<br>20,<br>41 | V <sub>DDPB</sub> | -     | PS/B | <b>Digital Pad Supply Voltage for Domain B</b><br>Connect decoupling capacitors to adjacent $V_{\text{DDP}}/V_{\text{SS}}$ pin pairs as close as possible to the pins.              |

| 6,<br>19,<br>42 | V <sub>SS</sub>   | -     | PS/  | <b>Digital Ground</b><br>All $V_{SS}$ pins must be connected to the ground-line<br>or ground-plane.                                                                                 |

# Table 6 Pin Definitions and Functions (cont'd)

### **Functional Description**

# 3.1 Memory Subsystem and Organization

The memory space of the XE161FU is configured in the von Neumann architecture. In this architecture all internal and external resources, including code memory, data memory, registers and I/O ports, are organized in the same linear address space.

| Address Area             | Start Loc.           | End Loc.             | Area Size <sup>2)</sup> | Notes                            |

|--------------------------|----------------------|----------------------|-------------------------|----------------------------------|

| IMB register space       | FF'FF00 <sub>H</sub> | FF'FFFF <sub>H</sub> | 256 bytes               |                                  |

| Reserved                 | F0'0000 <sub>H</sub> | FF'FEFF <sub>H</sub> | < 1 Mbyte               | Minus IMB registers.             |

| Reserved for EPSRAM      | E8'1000 <sub>H</sub> | EF'FFFF <sub>H</sub> | 508 Kbytes              | Mirrors EPSRAM                   |

| Emulated PSRAM           | E8'0000 <sub>H</sub> | E8'0FFF <sub>H</sub> | up to 4 Kbytes          | With Flash timing.               |

| Reserved for PSRAM       | E0'1000 <sub>H</sub> | E7'FFFF <sub>H</sub> | 508 Kbytes              | Mirrors PSRAM                    |

| PSRAM                    | E0'0000 <sub>H</sub> | E0'0FFF <sub>H</sub> | up to 4 Kbytes          | Program SRAM.                    |

| Reserved for Flash       | C1'1000 <sub>H</sub> | DF'FFFF <sub>H</sub> | 1980 Kbytes             |                                  |

| Flash 0                  | C0'0000 <sub>H</sub> | C1'0FFF <sub>H</sub> | 68 Kbytes <sup>3)</sup> |                                  |

| External memory area     | 40'0000 <sub>H</sub> | BF'FFFF <sub>H</sub> | 8 Mbytes                |                                  |

| External IO area4)       | 21'0000 <sub>H</sub> | 3F'FFFF <sub>H</sub> | 1984 Kbytes             |                                  |

| Reserved                 | 20'B400 <sub>H</sub> | 20'FFFF <sub>H</sub> | 19 Kbytes               |                                  |

| USIC0 alternate regs.    | 20'B000 <sub>H</sub> | 20'B3FF <sub>H</sub> | 1 Kbytes                | Accessed via<br>LXBus controller |

| Reserved                 | 20'4800 <sub>H</sub> | 20'AFFF <sub>H</sub> | 26 Kbytes               |                                  |

| USIC0 registers          | 20'4000 <sub>H</sub> | 20'47FF <sub>H</sub> | 2 Kbytes                | Accessed via<br>LXBus controller |

| Reserved                 | 20'0000 <sub>H</sub> | 20'3FFF <sub>H</sub> | 16 Kbytes               |                                  |

| External memory area     | 01'0000 <sub>H</sub> | 1F'FFFF <sub>H</sub> | 1984 Kbytes             |                                  |

| SFR area                 | 00'FE00 <sub>H</sub> | 00'FFFF <sub>H</sub> | 0.5 Kbytes              |                                  |

| Dual-port RAM<br>(DPRAM) | 00'F600 <sub>H</sub> | 00'FDFF <sub>H</sub> | 2 Kbytes                |                                  |

| Reserved for DPRAM       | 00'F200 <sub>H</sub> | 00'F5FF <sub>H</sub> | 1 Kbytes                |                                  |

| ESFR area                | 00'F000 <sub>H</sub> | 00'F1FF <sub>H</sub> | 0.5 Kbytes              |                                  |

| XSFR area                | 00'E000 <sub>H</sub> | 00'EFFF <sub>H</sub> | 4 Kbytes                |                                  |

| Data SRAM (DSRAM)        | 00'D800 <sub>H</sub> | 00'DFFF <sub>H</sub> | 2 Kbytes                |                                  |

### Table 8XE161FU Memory Map 1)

### **Functional Description**

**2 Kbytes of on-chip Data SRAM (DSRAM)** are used for storage of general user data. The DSRAM is accessed via a separate interface and is optimized for data access.

**2 Kbytes of on-chip Dual-Port RAM (DPRAM)** provide storage for user-defined variables, for the system stack, and for general purpose register banks. A register bank can consist of up to 16 word-wide (R0 to R15) and/or byte-wide (RL0, RH0, ..., RL7, RH7) General Purpose Registers (GPRs).

The upper 256 bytes of the DPRAM are directly bit addressable. When used by a GPR, any location in the DPRAM is bit addressable.

**1024 bytes (2** × **512 bytes)** of the address space are reserved for the Special Function Register areas (SFR space and ESFR space). SFRs are word-wide registers which are used to control and monitor functions of the different on-chip units. Unused SFR addresses are reserved for future members of the XE166 Family. In order to ensure upward compatibility they should either not be accessed or written with zeros.

**The on-chip Flash memory** stores code, constant data, and control data. The on-chip Flash memory consist of 1 module of 64 Kbytes. Each module is organized in 4-Kbyte sectors.

The uppermost 4-Kbyte sector of segment 0 (located in Flash module 0) is used internally to store operation control parameters and protection information.

Each sector can be separately write protected<sup>1)</sup>, erased and programmed (in blocks of 128 Bytes). The complete Flash area can be read-protected. A user-defined password sequence temporarily unlocks protected areas. The Flash modules combine 128-bit read access with protected and efficient writing algorithms for programming and erasing. Dynamic error correction provides extremely high read data security for all read access operations. Access to different Flash modules can be executed in parallel.

For Flash parameters, please see Section 4.6.

### Memory Content Protection

The contents of on-chip memories can be protected against soft errors (induced e.g. by radiation) by activating the parity mechanism or the Error Correction Code (ECC).

The parity mechanism can detect a single-bit error and prevent the software from using incorrect data or executing incorrect instructions.

The ECC mechanism can detect and automatically correct single-bit errors. This supports the stable operation of the system.

It is strongly recommended to activate the ECC mechanism wherever possible because this dramatically increases the robustness of an application against such soft errors.

To save control bits, sectors are clustered for protection purposes, they remain separate for programming/erasing.

### **Functional Description**

### 3.17 Power Management

The XE161FU provides the means to control the power it consumes either at a given time or averaged over a certain duration.

Two mechanisms can be used (and partly in parallel):

Clock Generation Management controls the frequency of internal and external clock signals. Clock signals for currently inactive parts of logic are disabled automatically. The user can drastically reduce the consumed power by reducing the XE161FU system clock frequency.

External circuits can be controlled using the programmable frequency output EXTCLK.

Peripheral Management permits temporary disabling of peripheral modules. Each peripheral can be disabled and enabled separately. The CPU can be switched off while the peripherals can continue to operate.

Wake-up from power reduction modes can be triggered either externally with signals generated by the external system, or internally by the on-chip wake-up timer. This supports intermittent operation of the XE161FU by generating cyclic wake-up signals. Full performance is available to quickly react to action requests while the intermittent sleep phases greatly reduce the average system power consumption.

Note: When selecting the supply voltage and the clock source and generation method, the required parameters must be carefully written to the respective bit fields, to avoid unintended intermediate states. Recommended sequences are provided which ensure the intended operation of power supply system and clock system. Please refer to the Programmer's Guide.

# 4.3.1 DC Parameters for Upper Voltage Area

Keeping signal levels within the limits specified in this table ensures operation without overload conditions. For signal levels outside these specifications, also refer to the specification of the overload current  $I_{OV}$ .

Note: Operating Conditions apply.

**Table 16** is valid under the following conditions:  $V_{\text{DDP}} \le 5.5 \text{ V}$ ;  $V_{\text{DDP}}$  typ. 5 V;  $V_{\text{DDP}} \ge 4.5 \text{ V}$

| Parameter                                                                  | Symbol                   |                                     | Values | 5                      | Unit | Note /<br>Test Condition                                                                                      |

|----------------------------------------------------------------------------|--------------------------|-------------------------------------|--------|------------------------|------|---------------------------------------------------------------------------------------------------------------|

|                                                                            |                          | Min.                                | Тур.   | Max.                   |      |                                                                                                               |

| Pin capacitance (digital inputs/outputs).                                  | C <sub>IO</sub> CC       | -                                   | -      | 10                     | pF   | not subject to production test                                                                                |

| Input Hysteresis <sup>1)</sup>                                             | HYS CC                   | 0.11 x<br>V <sub>DDP</sub>          | -      | -                      | V    | $R_{\rm S}$ = 0 Ohm                                                                                           |

| Absolute input leakage<br>current on pins of analog<br>ports <sup>2)</sup> | I <sub>OZ1</sub>  <br>CC | -                                   | 10     | 200                    | nA   | $V_{\rm IN}$ > $V_{\rm SS}$ ;<br>$V_{\rm IN}$ < $V_{\rm DDP}$                                                 |

| Absolute input leakage<br>current for all other pins.<br>2)3)              | I <sub>OZ2</sub>  <br>CC | -                                   | 0.2    | 5                      | μA   | $T_{ m J} \leq$ 110 °C;<br>$V_{ m IN} > V_{ m SS}$ ;<br>$V_{ m IN} < V_{ m DDP}$                              |

|                                                                            |                          | -                                   | 0.2    | 10                     | μA   | $T_{ m J} \leq$ 150 °C;<br>$V_{ m IN} > V_{ m SS}$ ;<br>$V_{ m IN} < V_{ m DDP}$                              |

| Pull Level Force Current <sup>4)</sup>                                     | $ I_{PLF} $ SR           | 220                                 | _      | -                      | μΑ   | $V_{\rm IN} \ge V_{\rm IHmin}$ (pulldown_ena<br>bled);<br>$V_{\rm IN} \le V_{\rm ILmax}$ (pullup_enable<br>d) |

| Pull Level Keep Current <sup>5)</sup>                                      | I <sub>PLK</sub>  <br>SR | _                                   | -      | 30                     | μΑ   | $V_{IN} \ge V_{IHmin}$<br>(pullup_enable<br>d);<br>$V_{IN} \le V_{ILmax}$<br>(pulldown_ena<br>bled)           |

| Input high voltage (all<br>except XTAL1)                                   | $V_{\rm IH}{\rm SR}$     | $0.7 	ext{ x}$<br>$V_{	extsf{DDP}}$ | -      | V <sub>DDP</sub> + 0.3 | V    |                                                                                                               |

Table 16

DC Characteristics for Upper Voltage Range

| Parameter                               | Symbol               |                           | Value | S                         | Unit | Note /<br>Test Condition                 |

|-----------------------------------------|----------------------|---------------------------|-------|---------------------------|------|------------------------------------------|

|                                         |                      | Min.                      | Тур.  | Max.                      |      |                                          |

| Input low voltage<br>(all except XTAL1) | $V_{IL}SR$           | -0.3                      | _     | 0.3 x<br>V <sub>DDP</sub> | V    |                                          |

| Output High voltage <sup>6)</sup>       | V <sub>OH</sub> CC   | V <sub>DDP</sub> -<br>1.0 | -     | -                         | V    | $I_{\text{OH}} \ge I_{\text{OHmax}}$     |

|                                         |                      | V <sub>DDP</sub> - 0.4    | -     | -                         | V    | $I_{\text{OH}} \ge I_{\text{OHnom}}^{7}$ |

| Output Low Voltage <sup>6)</sup>        | $V_{\rm OL}{\rm CC}$ | -                         | -     | 0.4                       | V    | $I_{\rm OL} \le I_{\rm OLnom}^{8)}$      |

|                                         |                      | -                         | -     | 1.0                       | V    | $I_{\rm OL} \le I_{\rm OLmax}$           |

#### Table 16 DC Characteristics for Upper Voltage Range (cont'd)

Not subject to production test - verified by design/characterization. Hysteresis is implemented to avoid metastable states and switching due to internal ground bounce. It cannot suppress switching due to external system noise under all conditions.

- 2) If the input voltage exceeds the respective supply voltage due to ground bouncing ( $V_{\rm IN} < V_{\rm SS}$ ) or supply ripple ( $V_{\rm IN} > V_{\rm DDP}$ ), a certain amount of current may flow through the protection diodes. This current adds to the leakage current. An additional error current ( $I_{\rm INJ}$ ) will flow if an overload current flows through an adjacent pin. Please refer to the definition of the overload coupling factor  $K_{\rm OV}$ .

- 3) The given values are worst-case values. In production test, this leakage current is only tested at 125 °C; other values are ensured by correlation. For derating, please refer to the following descriptions: Leakage derating depending on temperature (*T*<sub>J</sub> = junction temperature [°C]): *I*<sub>OZ</sub> = 0.05 x e<sup>(1.5 + 0.028 x TJ-)</sup> [µA]. For example, at a temperature of 95 °C the resulting leakage current is 3.2 µA. Leakage derating depending on voltage level (DV = *V*<sub>DDP</sub> *V*<sub>PIN</sub> [V]): *I*<sub>OZ</sub> = *I*<sub>OZtempmax</sub> (1.6 x DV) (µA]. This voltage derating formula is an approximation which applies for maximum temperature.

- Drive the indicated minimum current through this pin to change the default pin level driven by the enabled pull device.

- 5) Limit the current through this pin to the indicated value so that the enabled pull device can keep the default pin level.

- 6) The maximum deliverable output current of a port driver depends on the selected output driver mode. This specification is not valid for outputs which are switched to open drain mode. In this case the respective output will float and the voltage is determined by the external circuit.

- As a rule, with decreasing output current the output levels approach the respective supply level (VOL->VSS, VOH->VDDP). However, only the levels for nominal output currents are verified.

- 8) As a rule, with decreasing output current the output levels approach the respective supply level ( $V_{OL}$ -> $V_{SS}$ ,  $V_{OH}$ -> $V_{DDP}$ ). However, only the levels for nominal output currents are verified.

# 4.3.3 Power Consumption

The power consumed by the XE161FU depends on several factors such as supply voltage, operating frequency, active circuits, and operating temperature. The power consumption specified here consists of two components:

- The switching current  $I_{\rm S}$  depends on the device activity

- The leakage current I<sub>LK</sub> depends on the device temperature

To determine the actual power consumption, always both components, switching current  $I_{\rm S}$  and leakage current  $I_{\rm LK}$  must be added:

$I_{\text{DDP}} = I_{\text{S}} + I_{\text{LK}}.$

Note: The power consumption values are not subject to production test. They are verified by design/characterization.

To determine the total power consumption for dimensioning the external power supply, also the pad driver currents must be considered.

The given power consumption parameters and their values refer to specific operating conditions:

Active mode:

Regular operation, i.e. peripherals are active, code execution out of Flash.

Stopover mode:

Crystal oscillator and PLL stopped, Flash switched off, clock in most parts of domain DMP\_M stopped.

Note: The maximum values cover the complete specified operating range of all manufactured devices.

The typical values refer to average devices under typical conditions, such as nominal supply voltage, room temperature, application-oriented activity.

After a power reset, the decoupling capacitors for  $V_{\rm DDIM}$  are charged with the maximum possible current.

For additional information, please refer to Section 5.2, Thermal Considerations.

Note: Operating Conditions apply.

# 4.4 Analog/Digital Converter Parameters

These parameters describe the conditions for optimum ADC performance. *Note: Operating Conditions apply.*

### Table 20 ADC Parameters for All Voltage Ranges

| Parameter                                               | Symbol                     |                             | Values               |                             | Unit | Note /<br>Test Condition          |

|---------------------------------------------------------|----------------------------|-----------------------------|----------------------|-----------------------------|------|-----------------------------------|

|                                                         |                            | Min.                        | Тур.                 | Max.                        |      |                                   |

| Switched capacitance at an analog input                 | C <sub>AINSW</sub><br>CC   | -                           | 9                    | 20                          | pF   | not subject to<br>production test |

| Total capacitance at an analog input                    | C <sub>AINT</sub><br>CC    | _                           | 20                   | 30                          | pF   | not subject to<br>production test |

| Switched capacitance at the reference input             | C <sub>AREFSW</sub><br>CC  | -                           | 15                   | 30                          | pF   | not subject to<br>production test |

| Total capacitance at the reference input                | C <sub>AREFT</sub><br>CC   | -                           | 20                   | 40                          | pF   | not subject to<br>production test |

| Broken wire detection delay against VAGND <sup>2)</sup> | t <sub>BWG</sub> CC        | -                           | -                    | 50 <sup>3)</sup>            |      |                                   |

| Broken wire detection delay against VAREF <sup>2)</sup> | t <sub>BWR</sub> CC        | -                           | -                    | 50 <sup>4)</sup>            |      |                                   |

| Conversion time for 8-bit result <sup>2)</sup>          | t <sub>c8</sub> CC         | (10 + S<br>t <sub>SYS</sub> | TC x t <sub>AD</sub> | <sub>CI</sub> + 2 x         |      |                                   |

| Conversion time for 10-bit result <sup>2)</sup>         | <i>t</i> <sub>c10</sub> CC | (12 + S<br>t <sub>SYS</sub> | TC x t <sub>AD</sub> | <sub>CI</sub> + 2 x         |      |                                   |

| Conversion time for 12-bit result <sup>2)</sup>         | $t_{c12} CC$               | (16 + S<br>t <sub>SYS</sub> | TC x t <sub>AD</sub> | <sub>CI</sub> + 2 x         |      |                                   |

| Analog reference ground                                 | $V_{AGND}$ SR              | V <sub>SS</sub> -<br>0.05   | -                    | 1.5                         | V    |                                   |

| Analog input voltage range                              | $V_{\rm AIN}{ m SR}$       | $V_{\rm AGND}$              | -                    | $V_{AREF}$                  | V    | 5)                                |

| Analog reference voltage                                | $V_{AREF}$ SR              | V <sub>AGND</sub><br>+ 1.0  | -                    | V <sub>DDPB</sub><br>+ 0.05 | V    |                                   |

1) These parameter values cover the complete operating range. Under relaxed operating conditions (temperature, supply voltage) typical values can be used for calculation.

### 4.5 System Parameters

The following parameters specify several aspects which are important when integrating the XE161FU into an application system.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Note: Operating Conditions apply.

| Parameter                                                             | Symbol                 |                                         | Values       | ;                                     | Unit | Note /<br>Test Condition                    |

|-----------------------------------------------------------------------|------------------------|-----------------------------------------|--------------|---------------------------------------|------|---------------------------------------------|

|                                                                       |                        | Min.                                    | Тур.         | Max.                                  |      |                                             |

| Short-term deviation of internal clock source frequency <sup>1)</sup> | ∆f <sub>INT</sub> CC   | -1                                      | _            | 1                                     | %    | $\Delta T_{\rm J} = \le 10^{\circ} {\rm C}$ |

| Internal clock source frequency                                       | $f_{\rm INT}{\rm CC}$  | 4.8                                     | 5.0          | 5.2                                   | MHz  |                                             |

| Wakeup clock source                                                   | $f_{\rm WU}{\rm CC}$   | 400                                     | -            | 700                                   | kHz  | FREQSEL= 00                                 |

| frequency <sup>2)</sup>                                               |                        | 210                                     | -            | 390                                   | kHz  | FREQSEL= 01                                 |

|                                                                       |                        | 140                                     | -            | 260                                   | kHz  | FREQSEL= 10                                 |

|                                                                       |                        | 110                                     | -            | 200                                   | kHz  | FREQSEL= 11                                 |

| Startup time from power-<br>on with code execution<br>from Flash      | t <sub>SPO</sub> CC    | 1.4                                     | 1.9          | 2.4                                   | ms   | $f_{\rm WU}$ = 500 kHz                      |

| Startup time from stopover<br>mode with code execution<br>from PSRAM  | t <sub>SSO</sub> CC    | 11 /<br>f <sub>WU</sub> <sup>3)</sup>   | -            | 12 /<br>f <sub>WU</sub> <sup>3)</sup> | μS   |                                             |

| Core voltage (PVC) supervision level                                  | $V_{\rm PVC}{ m CC}$   | V <sub>LV</sub> -<br>0.03               | $V_{\rm LV}$ | V <sub>LV</sub> + 0.07 <sup>4)</sup>  | V    | 5)                                          |

| Supply watchdog (SWD) supervision level                               | V <sub>SWD</sub><br>CC | V <sub>LV</sub> -<br>0.10 <sup>6)</sup> | $V_{\rm LV}$ | V <sub>LV</sub> + 0.15                | V    | voltage_range=<br>lower 5)                  |

|                                                                       |                        | V <sub>LV</sub> -<br>0.15               | $V_{\rm LV}$ | V <sub>LV</sub> + 0.15                | V    | voltage_range=<br>upper <sup>5)</sup>       |

### Table 24Various System Parameters

The short-term frequency deviation refers to a timeframe of a few hours and is measured relative to the current frequency at the beginning of the respective timeframe. This parameter is useful to determine a time span for re-triggering a LIN synchronization.

This parameter is tested for the fastest and the slowest selection. The medium selections are not subject to production test - verified by design/characterization.

3)  $f_{WU}$  in MHz.

### 4.6 Flash Memory Parameters

The XE161FU is delivered with all Flash sectors erased and with no protection installed. The data retention time of the XE161FU's Flash memory (i.e. the time after which stored data can still be retrieved) depends on the number of times the Flash memory has been erased and programmed.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Note: Operating Conditions apply.

| Parameter                                                                           | Symbol                     |      | Values          |                 | Unit       | Note /<br>Test Condition                |

|-------------------------------------------------------------------------------------|----------------------------|------|-----------------|-----------------|------------|-----------------------------------------|

|                                                                                     |                            | Min. | Тур.            | Max.            |            |                                         |

| Parallel Flash module<br>program/erase limit<br>depending on Flash read<br>activity | N <sub>PP</sub> SR         | -    | _               | 1 <sup>1)</sup> |            | $N_{\rm FL_RD} \le 1$                   |

| Flash erase endurance for security pages                                            | $N_{\rm SEC}{ m SR}$       | 10   | -               | -               | cycle<br>s | $t_{\text{RET}} \ge 20$ years           |

| Flash wait states <sup>2)</sup>                                                     | N <sub>WSFLASH</sub><br>SR | 1    | -               | -               |            | f <sub>SYS</sub> ≤8 MHz                 |

|                                                                                     |                            | 2    | -               | -               |            | f <sub>SYS</sub> ≤ 13 MHz               |

|                                                                                     |                            | 3    | -               | -               |            | $f_{\rm SYS}$ $\leq$ 17 MHz             |

|                                                                                     |                            | 4    | -               | -               |            | $f_{\rm SYS}$ > 17 MHz                  |

| Erase time per<br>sector/page                                                       | t <sub>ER</sub> CC         | -    | 7 <sup>3)</sup> | 8.0             | ms         |                                         |

| Programming time per page                                                           | t <sub>PR</sub> CC         | -    | 3 <sup>3)</sup> | 3.5             | ms         |                                         |

| Data retention time                                                                 | t <sub>RET</sub> CC        | 20   | _               | -               | year<br>s  | $N_{\rm ER} \le 1,000 \; {\rm cycl}$ es |

| Drain disturb limit                                                                 | $N_{\rm DD}{ m SR}$        | 32   | -               | -               | cycle<br>s |                                         |

#### Table 27 Flash Parameters

# 4.7.2 Definition of Internal Timing

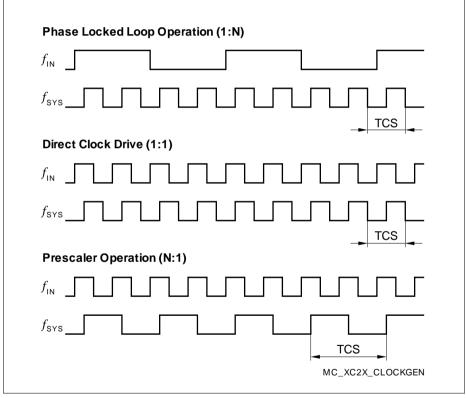

The internal operation of the XE161FU is controlled by the internal system clock  $f_{SYS}$ .

Because the system clock signal  $f_{\rm SYS}$  can be generated from a number of internal and external sources using different mechanisms, the duration of the system clock periods (TCSs) and their variation (as well as the derived external timing) depend on the mechanism used to generate  $f_{\rm SYS}$ . This must be considered when calculating the timing for the XE161FU.

Figure 17 Generation Mechanisms for the System Clock

Note: The example of PLL operation shown in **Figure 17** uses a PLL factor of 1:4; the example of prescaler operation uses a divider factor of 2:1.

The specification of the external timing (AC Characteristics) depends on the period of the system clock (TCS).

| Table 31 | Standard Pad Parameters for Lower Voltage Range (cont'd) |

|----------|----------------------------------------------------------|

|----------|----------------------------------------------------------|

| Parameter                                      | Symbol                  | Values |      |                                   | Unit | Note /                                                                                                            |

|------------------------------------------------|-------------------------|--------|------|-----------------------------------|------|-------------------------------------------------------------------------------------------------------------------|

|                                                |                         | Min.   | Тур. | Max.                              |      | Test Condition                                                                                                    |

| Nominal output driver current (absolute value) | I <sub>Onom</sub><br>CC | -      | -    | 0.8                               | mA   | Driver_Strength<br>= Medium                                                                                       |

|                                                |                         | -      | -    | 1.0                               | mA   | Driver_Strength<br>= Strong                                                                                       |

|                                                |                         | -      | _    | 0.15                              | mA   | Driver_Strength<br>= Weak                                                                                         |

| Rise and Fall times (10% -<br>90%)             | t <sub>RF</sub> CC      | _      | -    | 73 +<br>0.85 x<br>C <sub>L</sub>  | ns   | $C_{L} \ge 20 \text{ pF};$<br>$C_{L} \le 100 \text{ pF};$<br>Driver_Strength<br>= Medium                          |

|                                                |                         | -      | -    | 6+0.6<br>x C <sub>L</sub>         | ns   | $C_{L} \ge 20 \text{ pF};$<br>$C_{L} \le 100 \text{ pF};$<br>Driver_Strength<br>= Strong;<br>Driver_Edge=<br>Soft |

|                                                |                         | -      | _    | 33 +<br>0.6 x<br>C <sub>L</sub>   | ns   | $C_{L} \ge 20 \text{ pF};$<br>$C_{L} \le 100 \text{ pF};$<br>Driver_Strength<br>= Strong;<br>Driver_Edge=<br>Slow |

|                                                |                         | _      | -    | 385 +<br>3.25 x<br>C <sub>L</sub> | ns   | $C_{L} \ge 20 \text{ pF};$<br>$C_{L} \le 100 \text{ pF};$<br>Driver_Strength<br>= Weak                            |

The total output current that may be drawn at a given time must be limited to protect the supply rails from damage. For any group of 16 neighboring output pins, the total output current in each direction (ΣI<sub>OL</sub> and Σ-I<sub>OH</sub>) must remain below 25 mA.

# 4.7.5 Synchronous Serial Interface Timing

The following parameters are applicable for a USIC channel operated in SSC mode.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Note: Operating Conditions apply.

**Table 32** is valid under the following conditions:  $C_L$ = 20 pF; *SSC*= master ; voltage\_range= upper

| Parameter                                                               | Symbol            | Values                                |      |      | Unit | Note /         |

|-------------------------------------------------------------------------|-------------------|---------------------------------------|------|------|------|----------------|

|                                                                         |                   | Min.                                  | Тур. | Max. | 1    | Test Condition |

| Slave select output SELO<br>active to first SCLKOUT<br>transmit edge    | t <sub>1</sub> CC | t <sub>SYS</sub> -<br>8 <sup>1)</sup> | -    | -    | ns   |                |

| Slave select output SELO<br>inactive after last<br>SCLKOUT receive edge | t <sub>2</sub> CC | t <sub>SYS</sub> - 6 <sup>1)</sup>    | -    | -    | ns   |                |

| Data output DOUT valid time                                             | t <sub>3</sub> CC | -6                                    | -    | 9    | ns   |                |

| Receive data input setup time to SCLKOUT receive edge                   | t <sub>4</sub> SR | 31                                    | -    | -    | ns   |                |

| Data input DX0 hold time<br>from SCLKOUT receive<br>edge                | t <sub>5</sub> SR | -4                                    | -    | -    | ns   |                |

### Table 32 USIC SSC Master Mode Timing for Upper Voltage Range

1)  $t_{SYS} = 1 / f_{SYS}$

Table 39 is valid under the following conditions: C<sub>L</sub>= 20 pF; voltage\_range= lower

|                                                                          | r                         | -                 |      | •    | -    |                |

|--------------------------------------------------------------------------|---------------------------|-------------------|------|------|------|----------------|

| Parameter                                                                | Symbol                    | Values            |      |      | Unit | Note /         |

|                                                                          |                           | Min.              | Тур. | Max. |      | Test Condition |

| TCK clock period                                                         | t <sub>1</sub> SR         | 100 <sup>1)</sup> | -    | -    | ns   |                |

| TCK high time                                                            | $t_2  \mathrm{SR}$        | 16                | -    | -    | ns   |                |

| TCK low time                                                             | t <sub>3</sub> SR         | 16                | -    | -    | ns   |                |

| TCK clock rise time                                                      | t <sub>4</sub> SR         | -                 | -    | 8    | ns   |                |

| TCK clock fall time                                                      | t <sub>5</sub> SR         | -                 | -    | 8    | ns   |                |

| TDI/TMS setup to TCK rising edge                                         | t <sub>6</sub> SR         | 6                 | -    | -    | ns   |                |

| TDI/TMS hold after TCK rising edge                                       | t <sub>7</sub> SR         | 6                 | -    | -    | ns   |                |

| TDO valid from TCK falling edge (propagation delay) <sup>2)</sup>        | t <sub>8</sub> CC         | -                 | 39   | 43   | ns   |                |

| TDO high impedance to valid output from TCK falling edge <sup>3)2)</sup> | t <sub>9</sub> CC         | -                 | 39   | 43   | ns   |                |

| TDO valid output to high impedance from TCK falling edge <sup>2)</sup>   | <i>t</i> <sub>10</sub> CC | -                 | 39   | 43   | ns   |                |

| TDO hold after TCK falling edge <sup>2)</sup>                            | <i>t</i> <sub>18</sub> CC | 5                 | -    | -    | ns   |                |

Table 39

JTAG Interface Timing for Lower Voltage Range

1) The debug interface cannot operate faster than the overall system, therefore  $t_1 \ge t_{SYS}$ .

2) The falling edge on TCK is used to generate the TDO timing.

3) The setup time for TDO is given implicitly by the TCK cycle time.