Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4F                                                             |

| Core Size                  | 32-Bit Single-Core                                                           |

| Speed                      | 160MHz                                                                       |

| Connectivity               | CANbus, CSIO, EBI/EMI, I <sup>2</sup> C, LINbus, UART/USART                  |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 63                                                                           |

| Program Memory Size        | 544KB (544K x 8)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | <u>.</u>                                                                     |

| RAM Size                   | 64K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                  |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                        |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 80-LQFP                                                                      |

| Supplier Device Package    | 80-LQFP (12x12)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/s6e2h46e0agv20000 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

□ Various error detect functions available (parity errors, framing errors, and overrun errors)

#### ■CSIO

- □ Full-duplex double buffer

- Built-in dedicated baud rate generator

- $\square$  Overrun error detect function available

- □ Serial chip select function (ch.6 and ch.7 only)

- □ Supports high-speed SPI (ch.4 and ch.6 only)

- □ Data length 5 to 16-bit

#### ■LIN

- □ LIN protocol Rev.2.1 supported

- □ Full-duplex double buffer

- □ Master/Slave mode supported

- □ LIN break field generation (can change to 13 to 16-bit length)

- □ LIN break delimiter generation (can change to 1 to 4-bit length)

- □ Various error detect functions available (parity errors, framing errors, and overrun errors)

#### ■I<sup>2</sup>C

- □ Standard mode (Max 100 kbps) / High-speed mode (Max 400 kbps) supported

- □ Fast mode Plus (Fm+) (Max 1000 kbps, only for ch.3=ch.A and ch.7=ch.B) supported

#### DMA Controller (8 channels)

DMA Controller has an independent bus for CPU, so CPU and DMA Controller can process simultaneously.

- ■8 independently configured and operated channels

- Transfer can be started by software or request from the built-in peripherals

- Transfer address area: 32-bit (4 Gbytes)

- Transfer mode: Block transfer/Burst transfer/Demand transfer

- Transfer data type: bytes/half-word/word

- Transfer block count: 1 to 16

- ■Number of transfers: 1 to 65536

# DSTC (Descriptor System data Transfer Controller) (256 channels)

The DSTC can transfer data at high-speed without going via the CPU. The DSTC adopts the Descriptor system and, following the specified contents of the Descriptor which has already been constructed on the memory, can access directly the memory /peripheral device and performs the data transfer operation.

It supports the software activation, the hardware activation and the chain activation functions.

### A/D Converter (Max 24 channels) [12-bit A/D Converter]

- Successive Approximation type

- Built-in 3 units

- ■Conversion time: 0.5 µs @ 5 V

- Priority conversion available (priority at 2 levels)

- Scanning conversion mode

- Built-in FIFO for conversion data storage (for SCAN conversion: 16 steps, for Priority conversion: 4 steps)

#### DA Converter (Max 2 channels)

- ■R-2R type

- ■12-bit resolution

#### Base Timer (Max 8 channels)

Operation mode is selectable from the followings for each channel.

- ■16-bit PWM timer

- ■16-bit PPG timer

- ■16-/32-bit reload timer

- ■16-/32-bit PWC timer

- Event counter mode ( external clock mode )

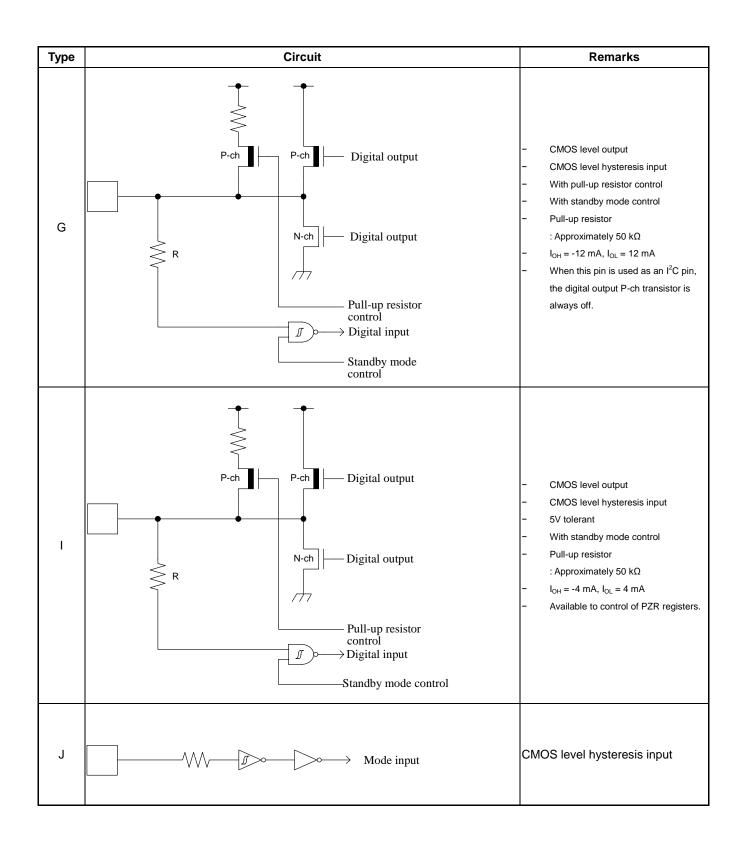

#### **General Purpose I/O Port**

This series can use its pins as general purpose I/O ports when they are not used for external bus or peripherals. Moreover, the port relocate function is built in. It can set which I/O port the peripheral function can be allocated.

- Capable of pull-up control per pin

- Capable of reading pin level directly

- ■Built-in the port relocate function

- Up to 100 high-speed general-purpose I/O ports @ 120 pin Package

Some pin is 5 V tolerant I/O. See 4. Pin Description and 5. I/O Circuit Type for the corresponding pins.

#### Multi-function Timer (Max 3 units)

The Multi-function timer is composed of the following blocks.

Minimum resolution: 6.25 ns

- ■16-bit free-run timer × 3ch./unit

- ■Input capture × 4ch./unit

- ■Output compare × 6ch./unit

- A/D activation compare × 6ch./unit

- ■Waveform generator × 3ch./unit

- ■16-bit PPG timer × 3ch./unit

The following function can be used to achieve the motor control.

- ■PWM signal output function

- ■DC chopper waveform output function

- Dead time function

- ■Input capture function

Document Number: 001-98941 Rev.\*B

| Di                            |                                         |                                                    | Pin No      |             |            |                 |  |  |

|-------------------------------|-----------------------------------------|----------------------------------------------------|-------------|-------------|------------|-----------------|--|--|

| Pin<br>Function               | Pin Name                                | Function Description                               | LQFP<br>120 | LQFP<br>100 | LQFP<br>80 | FBGA<br>121     |  |  |

| MSDCLK_0                      |                                         | SDRAM interface<br>SDRAM clock output pin          | 23          | 18          | -          | H1              |  |  |

|                               | MSDCKE_0                                | SDRAM interface<br>SDRAM clock enable pin          | 24          | 19          | -          | H2              |  |  |

| External<br>Bus               | MRASX_0                                 | SDRAM interface<br>SDRAM row address strobe pin    | 25          | 20          | -          | H3              |  |  |

|                               | MCASX_0                                 | SDRAM interface<br>SDRAM column address strobe pin | 26          | 21          | -          | H4              |  |  |

|                               | MSDWEX_0                                | SDRAM interface<br>SDRAM write enable pin          | 34          | 29          | -          | J5              |  |  |

|                               | INT00_0                                 |                                                    | 2           | 2           | 2          | C1              |  |  |

|                               | INT00_1                                 | External interrupt request 00 input pin            | 95          | 80          | 65         | B8              |  |  |

|                               | INT00_2                                 |                                                    | 108         | -           | -          | E6              |  |  |

|                               | INT01_0                                 |                                                    | 3           | 3           | 3          | C2              |  |  |

|                               | INT01_1                                 | External interrupt request 01 input pin            | 101         | 86          | -          | D6              |  |  |

| ſ                             | INT01_2                                 |                                                    | 85          | -           | -          | B10             |  |  |

|                               | INT02_0                                 |                                                    | 6           | 6           | 6          | D3              |  |  |

|                               | INT02_1                                 | External interrupt request 02 input pin            | 62          | 52          | 41         | J10             |  |  |

| INT02_2<br>INT03_0<br>INT03_1 |                                         | 82                                                 | -           | -           | E7         |                 |  |  |

|                               | INT03_0                                 |                                                    | 113         | 93          | 73         | B4              |  |  |

|                               | External interrupt request 03 input pin | 65                                                 | 55          | 44          | G10        |                 |  |  |

|                               | INT03_2                                 |                                                    | 54          | -           | -          | H8              |  |  |

| •                             | INT04_0                                 |                                                    | 17          | 12          | 12         | F2              |  |  |

|                               | INT04_1                                 | External interrupt request 04 input pin            | 114         | 94          | 74         | C3              |  |  |

|                               | INT04_2                                 |                                                    | 10          | -           | -          | F5              |  |  |

| -                             | INT05_0                                 |                                                    | 89          | 74          | -          | B11             |  |  |

| -                             | INT05_1                                 | External interrupt request 05 input pin            | 75          | 65          | 54         | E11             |  |  |

| -                             | INT05_2                                 |                                                    | 21          | 16          | -          | G3              |  |  |

| External                      | INT06_1                                 |                                                    | 88          | 73          | 59         | C11             |  |  |

| Interrupt                     | INT06_2                                 | External interrupt request 06 input pin            | 22          | 17          |            | G4              |  |  |

| interrupt                     | INT07_1                                 |                                                    | 11          | -           |            | F6              |  |  |

|                               | INT07_1                                 | External interrupt request 07 input pin            | 7           | 7           | - 7        | E2              |  |  |

|                               | INT07_2                                 |                                                    | 19          | 14          | -          | G1              |  |  |

|                               | INT08_2                                 | External interrupt request 08 input pin            | 8           | 8           | 8          | E3              |  |  |

|                               | INT09_1                                 |                                                    | 20          | 15          | -          | G2              |  |  |

|                               | INT09_1                                 | External interrupt request 09 input pin            | 15          | 10          | 10         | 62<br>F4        |  |  |

|                               | INT09_2<br>INT10_1                      |                                                    | 15          | 11          | 10         | F4<br>F3        |  |  |

|                               | INT10_1<br>INT10_2                      | External interrupt request 10 input pin            | 112         |             |            | <u>гз</u><br>С4 |  |  |

| -                             |                                         |                                                    |             | -           | -          |                 |  |  |

|                               | INT11_1<br>INT11_2                      | External interrupt request 11 input pin            | 50<br>110   | 45<br>-     | 35<br>-    | K8<br>D5        |  |  |

|                               | INT12_1<br>INT12_2                      | External interrupt request 12 input pin            | 32<br>96    | 27<br>81    | -<br>66    | L2<br>A8        |  |  |

|                               | INT13_1                                 |                                                    | 33          | 28          | -          | J3              |  |  |

|                               | INT13_2                                 | External interrupt request 13 input pin            | 49          | 44          | 34         | <br>J8          |  |  |

|                               | INT14_1                                 |                                                    | 68          | 58          | 47         | F10             |  |  |

| ł                             | INT14_2                                 | External interrupt request 14 input pin            | 53          | -           | -          | G7              |  |  |

| •                             | INT15_1                                 |                                                    | 52          | -           | -          | H7              |  |  |

| -                             | INT15_1                                 | External interrupt request 15 input pin            | 14          | 9           | 9          | E1              |  |  |

|                                |                    |                                                                                                             | Pin No      |             |            |             |  |

|--------------------------------|--------------------|-------------------------------------------------------------------------------------------------------------|-------------|-------------|------------|-------------|--|

| Pin<br>Function                | Pin Name           | Function Description                                                                                        | LQFP<br>120 | LQFP<br>100 | LQFP<br>80 | FBGA<br>121 |  |

|                                | SIN2_0             |                                                                                                             | 53          | -           | -          | G7          |  |

|                                | SIN2_1             | Multi-function serial interface ch.2 input pin                                                              | 85          | -           | -          | B10         |  |

| _                              | SIN2_2             |                                                                                                             | 68          | 58          | 47         | F10         |  |

|                                | SOT2_0<br>(SDA2_0) | Multi-function serial interface ch.2 output<br>pin.                                                         | 54          | -           | -          | H8          |  |

| Multi-                         | SOT2_1<br>(SDA2_1) | This pin operates as SOT2 when it is used<br>in a UART/CSIO/LIN (operation modes 0 to                       | 84          | -           | -          | C9          |  |

| function<br>Serial 2           | SOT2_2<br>(SDA2_2) | 3) and as SDA2 when it is used in an I2C (operation mode 4).                                                | 69          | 59          | 48         | F9          |  |

|                                | SCK2_0<br>(SCL2_0) | Multi-function serial interface ch.2 clock I/O pin.                                                         | 55          | -           | -          | J9          |  |

|                                | SCK2_1<br>(SCL2_1) | This pin operates as SCK2 when it is used in a CSIO (operation modes 2) and as                              | 83          | -           | -          | D8          |  |

|                                | SCK2_2<br>(SCL2_2) | SCL2 when it is used in an I2C (operation mode 4).                                                          | 74          | 64          | 53         | F8          |  |

|                                | SIN3_0             | Multi-function serial interface ch.3 input pin                                                              | 110         | -           | -          | D5          |  |

|                                | SIN3_1             | -Multi-function senai internace cn.s input pin                                                              | 15          | 10          | 10         | F4          |  |

|                                | SOT3_0<br>(SDA3_0) | Multi-function serial interface ch.3 output<br>pin.<br>This pin operates as SOT3 when it is used            | 109         | -           | -          | E5          |  |

| Multi-<br>function<br>Serial 3 | SOT3_1<br>(SDA3_1) | in a UART/CSIO/LIN (operation modes 0 to<br>3) and as SDA3 when it is used in an I2C<br>(operation mode 4). | 16          | 11          | 11         | F3          |  |

|                                | SCK3_0<br>(SCL3_0) | Multi-function serial interface ch.3 clock I/O<br>pin.<br>This pin operates as SCK3 when it is used         | 108         | -           | -          | E6          |  |

|                                | SCK3_1<br>(SCL3_1) | in a CSIO (operation modes 2) and as<br>SCL3 when it is used in an I2C (operation<br>mode 4).               | 17          | 12          | 12         | F2          |  |

#### Latch-up

Semiconductor devices are constructed by the formation of P-type and N-type areas on a substrate. When subjected to abnormally high voltages, internal parasitic PNPN junctions (called thyristor structures) may be formed, causing large current levels in excess of several hundred mA to flow continuously at the power supply pin. This condition is called latch-up.

CAUTION: The occurrence of latch-up not only causes loss of reliability in the semiconductor device, but can cause injury or damage from high heat, smoke or flame. To prevent this from happening, do the following:

(1) Be sure that voltages applied to pins do not exceed the absolute maximum ratings. This should include attention to abnormal noise, surge levels, etc.

(2) Be sure that abnormal current flows do not occur during the power-on sequence.

#### **Observance of Safety Regulations and Standards**

Most countries in the world have established standards and regulations regarding safety, protection from electromagnetic interference, etc. Customers are requested to observe applicable regulations and standards in the design of products.

#### Fail-Safe Design

Any semiconductor devices have inherently a certain rate of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

#### Precautions Related to Usage of Devices

Cypress semiconductor devices are intended for use in standard applications (computers, office automation and other office equipment, industrial, communications, and measurement equipment, personal or household devices, etc.).

CAUTION: Customers considering the use of our products in special applications where failure or abnormal operation may directly affect human lives or cause physical injury or property damage, or where extremely high levels of reliability are demanded (such as aerospace systems, atomic energy controls, sea floor repeaters, vehicle operating controls, medical devices for life support, etc.) are requested to consult with sales representatives before such use. The company will not be responsible for damages arising from such use without prior approval.

#### 6.2 Precautions for Package Mounting

Package mounting may be either lead insertion type or surface mount type. In either case, for heat resistance during soldering, you should only mount under Cypress's recommended conditions. For detailed information about mount conditions, contact your sales representative.

#### Lead Insertion Type

Mounting of lead insertion type packages onto printed circuit boards may be done by two methods: direct soldering on the board, or mounting by using a socket.

Direct mounting onto boards normally involves processes for inserting leads into through-holes on the board and using the flow soldering (wave soldering) method of applying liquid solder. In this case, the soldering process usually causes leads to be subjected to thermal stress in excess of the absolute ratings for storage temperature. Mounting processes should conform to Cypress recommended mounting conditions.

If socket mounting is used, differences in surface treatment of the socket contacts and IC lead surfaces can lead to contact deterioration after long periods. For this reason it is recommended that the surface treatment of socket contacts and IC leads be verified before mounting.

#### Surface Mount Type

Surface mount packaging has longer and thinner leads than lead-insertion packaging, and therefore leads are more easily deformed or bent. The use of packages with higher pin counts and narrower pin pitch results in increased susceptibility to open connections caused by deformed pins, or shorting due to solder bridges.

You must use appropriate mounting techniques. Cypress recommends the solder reflow method, and has established a ranking of mounting conditions for each product. Users are advised to mount packages in accordance with Cypress ranking of recommended conditions.

# 7. Handling Devices

#### **Power Supply Pins**

In products with multiple VCC and VSS pins, respective pins at the same potential are interconnected within the device in order to prevent malfunctions such as latch-up. However, all of these pins should be connected externally to the power supply or ground lines in order to reduce electromagnetic emission levels, to prevent abnormal operation of strobe signals caused by the rise in the ground level, and to conform to the total output current rating.

Moreover, connect the current supply source with each POWER pins and GND pins of this device at low impedance. It is also advisable that a ceramic capacitor of approximately 0.1 µF be connected as a bypass capacitor between VCC and VSS near this device.

#### **Power Supply Pins**

A malfunction may occur when the power supply voltage fluctuates rapidly even though the fluctuation is within the guaranteed operating range of the VCC power supply voltage. As a rule of voltage stabilization, suppress voltage fluctuation so that the fluctuation in VCC ripple (peak-to-peak value) at the commercial frequency (50 Hz/60 Hz) does not exceed 10% of the standard VCC value, and the transient fluctuation rate does not exceed 0.1 V/µs at a momentary fluctuation such as switching the power supply.

#### **Crystal Oscillator Circuit**

Noise near the X0/X1 and X0A/X1A pins may cause the device to malfunction. Design the printed circuit board so that X0/X1, X0A/X1A pins, the crystal oscillator (or ceramic oscillator), and the bypass capacitor to ground are located as close to the device as possible.

It is strongly recommended that the PC board artwork be designed such that the X0/X1 and X0A/X1A pins are surrounded by ground plane as this is expected to produce stable operation.

Evaluate oscillation of your using crystal oscillator by your mount board.

#### Sub Crystal Oscillator

This series sub oscillator circuit is low gain to keep the low current consumption.

The crystal oscillator to fill the following conditions is recommended for sub crystal oscillator to stabilize the oscillation.

| Surface mount type |                            |

|--------------------|----------------------------|

| Size:              | More than 3.2 mm x 1.5 mm  |

| Load capacitance:  | Approximately 6 pF to 7 pF |

| □ Lead type        |                            |

| Load capacitance:  | Approximately 6 pF to 7 pF |

# 11. Pin Status in Each CPU State

The terms used for pin status have the following meanings.

This is the period when the INITX pin is the L level. ■INITX=1

This is the period when the INITX pin is the H level.

■SPL=0

■INITX=0

This is the status that the standby pin level setting bit (SPL) in the standby mode control register (STB\_CTL) is set to 0.

■SPL=1

This is the status that the standby pin level setting bit (SPL) in the standby mode control register (STB\_CTL) is set to 1.

Input enabled Indicates that the input function can be used.

Internal input fixed at 0 This is the status that the input function cannot be used. Internal input is fixed at L.

■Hi-Z

Indicates that the pin drive transistor is disabled and the pin is put in the Hi-Z state.

Setting disabled Indicates that the setting is disabled.

#### Maintain previous state

Maintains the state that was immediately prior to entering the current mode. If a built-in peripheral function is operating, the output follows the peripheral function. If the pin is being used as a port, that output is maintained.

Analog input is enabled Indicates that the analog input is enabled.

Trace output Indicates that the trace function can be used.

■GPIO selected

In Deep standby mode, pins switch to the general-purpose I/O port.

Setting prohibition

Prohibition of a setting by specification limitation.

# S6E2H4 Series

| status Type | Function<br>Group                                               |                             |                               | Device<br>Internal<br>Reset<br>State | Run<br>Mode<br>or Sleep<br>Mode<br>State | RTC M                         | Mode,<br>ode, or<br>ode State             | Deep Sta<br>Mode or De<br>Stop Mo                   | ndby RTC<br>ep Standby<br>de State                  | Return from<br>Deep<br>Standby<br>Mode State |

|-------------|-----------------------------------------------------------------|-----------------------------|-------------------------------|--------------------------------------|------------------------------------------|-------------------------------|-------------------------------------------|-----------------------------------------------------|-----------------------------------------------------|----------------------------------------------|

| Pin         |                                                                 | Power<br>Supply<br>Unstable | Power<br>Sta                  | ble                                  | Power<br>Supply<br>Stable                | Sta                           | Power Supply<br>Stable                    |                                                     | Supply<br>ble                                       | Power<br>Supply<br>Stable                    |

|             |                                                                 | -                           | INITX=0                       | INITX=1                              | INITX=1                                  | SPL=0                         | X=1<br>SPL=1                              | INIT<br>SPL=0                                       | SPL=1                                               | INITX=1                                      |

|             | Mode<br>input pin                                               | -<br>Input<br>enabled       | -<br>Input<br>enabled         | -<br>Input<br>enabled                | -<br>Input<br>enabled                    | Input<br>enabled              | Input<br>enabled                          | Input<br>enabled                                    | Input<br>enabled                                    | Input<br>enabled                             |

| E           | GPIO<br>selected                                                | Setting<br>disabled         | Setting disabled              | Setting disabled                     | Maintain<br>previous<br>state            | Maintain<br>previous<br>state | Hi-Z /<br>Input<br>enabled                | GPIO<br>selected                                    | Hi-Z /<br>Input<br>enabled                          | GPIO<br>selected                             |

|             | NMIX selected                                                   | Setting disabled            | Setting disabled              | Setting disabled                     |                                          |                               | Maintain<br>previous<br>state             |                                                     |                                                     | GPIO                                         |

| F           | Resource<br>other than<br>above<br>selected Hi-Z                | Hi-Z                        | Input Inp                     | Hi-Z /<br>Input                      | Maintain<br>previous<br>state            |                               | Hi-Z /<br>Internal input<br>fixed         | WKUP<br>input enabled                               | Hi-Z /<br>WKUP<br>input enabled                     | selected                                     |

|             | GPIO<br>selected                                                |                             | enabled                       | enabled                              |                                          |                               | at 0                                      |                                                     |                                                     | Maintain<br>previous<br>state                |

|             | JTAG<br>selected                                                | Hi-Z                        | Pull-up /<br>Input<br>enabled | Pull-up /<br>Input<br>enabled        | Maintain<br>previous<br>state            | Maintain                      | Maintain<br>previous<br>state             | Maintain<br>previous<br>state                       | Maintain<br>previous<br>state                       | Maintain<br>previous<br>state                |

| G           | GPIO<br>selected                                                | Setting<br>disabled         | Setting<br>disabled           | Setting<br>disabled                  |                                          |                               | previous<br>state                         | Hi-Z /<br>Internal input<br>fixed<br>at 0           | GPIO<br>selected<br>Internal input<br>fixed<br>at 0 | Hi-Z /<br>Internal input<br>fixed<br>at 0    |

|             | JTAG<br>selected                                                | Hi-Z                        | Pull-up /<br>Input<br>enabled | Pull-up /<br>Input<br>enabled        | Maintain                                 | Maintain                      | Maintain<br>previous<br>state             | Maintain<br>previous<br>state                       | Maintain<br>previous<br>state                       | Maintain<br>previous<br>state                |

| н           | Resource<br>other than<br>above<br>selected<br>GPIO<br>selected | Setting<br>disabled         | Setting<br>disabled           | Setting<br>disabled                  | Maintain<br>previous<br>state            | Maintain<br>previous<br>state | Hi-Z /<br>Internal input<br>fixed<br>at 0 | GPIO<br>selected<br>Internal input<br>fixed<br>at 0 | Hi-Z /<br>Internal input<br>fixed<br>at 0           | GPIO<br>selected                             |

| I           | Resource<br>selected<br>GPIO                                    | Hi-Z                        | Hi-Z /<br>Input<br>enabled    | Hi-Z /<br>Input<br>enabled           | Maintain<br>previous<br>state            | Maintain<br>previous<br>state | Hi-Z /<br>Internal input<br>fixed<br>at 0 | GPIO<br>selected<br>Internal input<br>fixed         | Hi-Z /<br>Internal input<br>fixed<br>at 0           | GPIO<br>selected                             |

#### List of VBAT Domain Pin Status

| Pin Status Type | Function<br>Group                                                                   | VBAT<br>Power-on<br>reset                                         | INITX<br>Input<br>State       | Device<br>Internal<br>Reset<br>State | Run<br>Mode or<br>Sleep<br>Mode<br>State | RTC M                                                                        | Mode,<br>ode, or<br>ode State                                            | Deep S<br>RTC Sode<br>Standby S<br>Sta                                   | e or Deep<br>stop Mode                                                   | Return<br>from<br>Deep<br>Standby<br>Mode<br>State | VBAT<br>RTC<br>Mode<br>State  | Return<br>from<br>VBAT<br>RTC<br>Mode<br>State |

|-----------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------|-------------------------------|--------------------------------------|------------------------------------------|------------------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------|----------------------------------------------------|-------------------------------|------------------------------------------------|

| VBAT F          |                                                                                     | Power<br>Supply<br>Unstable                                       | Sta                           | Supply<br>able                       | Power<br>Supply<br>Stable                | Sta                                                                          | Supply<br>able                                                           | Power<br>Sta                                                             | ble                                                                      | Power<br>Supply<br>Stable                          | Power<br>Supply<br>Stable     | Power<br>Supply<br>Stable                      |

| -               |                                                                                     | -                                                                 | INITX=0                       | INITX=1                              | INITX=1                                  |                                                                              | <sup>-</sup> X=1                                                         | INIT                                                                     |                                                                          | INITX=1                                            | -                             | -                                              |

|                 |                                                                                     | -                                                                 | -                             | -                                    | -                                        | SPL=0                                                                        | SPL=1                                                                    | SPL=0                                                                    | SPL=1                                                                    | -                                                  | -                             | -                                              |

|                 | GPIO<br>selected                                                                    | Setting disabled                                                  | Maintain<br>previous<br>state | Maintain<br>previous<br>state        | Maintain<br>previous<br>state            | Maintain<br>previous<br>state                                                | Maintain<br>previous<br>state                                            | Maintain<br>previous<br>state                                            | Maintain<br>previous<br>state                                            | GPIO<br>selected                                   | Setting<br>prohibitio<br>n    | -                                              |

| S               | Sub crystal<br>oscillator<br>input pin /<br>External sub<br>clock input<br>selected | Input<br>enabled                                                  | Input<br>enabled              | Input<br>enabled                     | Input<br>enabled                         | Input<br>enabled                                                             | Input<br>enabled                                                         | Input<br>enabled                                                         | Input<br>enabled                                                         | Input<br>enabled                                   | Maintain<br>previous<br>state | Maintain<br>previous<br>state                  |

|                 | GPIO<br>selected                                                                    | Setting disabled                                                  | Maintain<br>previous<br>state | Maintain<br>previous<br>state        | Maintain<br>previous<br>state            | Maintain<br>previous<br>state                                                | Maintain<br>previous<br>state                                            | Maintain<br>previous<br>state                                            | Maintain<br>previous<br>state                                            | GPIO<br>selected                                   | Setting<br>prohibitio<br>n    | -                                              |

|                 | External sub<br>clock input<br>selected                                             | Setting disabled                                                  | Maintain<br>previous<br>state | Maintain<br>previous<br>state        | Maintain<br>previous<br>state            | Maintain<br>previous<br>state                                                | Maintain<br>previous<br>state                                            | Maintain<br>previous<br>state                                            | Maintain<br>previous<br>state                                            | Maintain<br>previous<br>state                      | Maintain<br>previous<br>state | Maintain<br>previous<br>state                  |

| Т               | Sub crystal<br>oscillator<br>output pin                                             | Hi-Z /<br>Internal<br>input fixed<br>at 0/<br>or Input<br>enabled | Maintain<br>previous<br>state | Maintain<br>previous<br>state        | Maintain<br>previous<br>state            | Maintain<br>previous<br>state<br>/When<br>oscillatio<br>n<br>stops,<br>Hi-Z* | Maintain<br>previous<br>state<br>/When<br>oscillation<br>stops,<br>Hi-Z* | Maintain<br>previous<br>state<br>/When<br>oscillation<br>stops,<br>Hi-Z* | Maintain<br>previous<br>state<br>/When<br>oscillation<br>stops,<br>Hi-Z* | Maintain<br>previous<br>state                      | Maintain<br>previous<br>state | Maintain<br>previous<br>state                  |

| U               | Resource<br>selected                                                                | Hi-Z                                                              | Maintain<br>previous          | Maintain<br>previous                 | Maintain<br>previous                     | Maintain<br>previous                                                         | Maintain<br>previous                                                     | Maintain<br>previous                                                     | Maintain<br>previous                                                     | Maintain<br>previous                               | Maintain<br>previous          | Maintain<br>previous                           |

|                 | GPIO<br>selected                                                                    |                                                                   | state                         | state                                | state                                    | state                                                                        | state                                                                    | state                                                                    | state                                                                    | state                                              | state                         | state                                          |

\*: When The SOSCNTL bit in the WTOSCCNT Register is 0, Sub crystal oscillator output pin is maintain previous state. When The SOSCNTL bit in the WTOSCCNT Register is 1, Oscillation is stopped at Stop mode and Deep standby Stop mode.

# Separate Bus Access Synchronous SRAM Mode

$(V_{CC} = 2.7V \text{ to } 5.5V, V_{SS} = 0V)$

| Deremeter                   | Symbol                        | Pin Name     | Conditions              | Va     | alue    | Unit |  |

|-----------------------------|-------------------------------|--------------|-------------------------|--------|---------|------|--|

| Parameter                   | Symbol                        | Pin Name     | Conditions              | Min    | Max     | Unit |  |

| Addross dolay time          | <b>t</b>                      | MCLK,        | $V_{CC} \ge 4.5 V$      | - 1    | 9       | ns   |  |

| Address delay time          | t <sub>AV</sub>               | MAD[24:0]    | $V_{CC} < 4.5 V$        |        | 12      | 115  |  |

|                             | 4                             |              | $V_{CC} \ge 4.5 V$      | - 1    | 9       | 20   |  |

| MCSX dolou time             | tcs∟                          | MCLK,        | $V_{CC} < 4.5 V$        |        | 12      | ns   |  |

| MCSX delay time             |                               | MCSX[7:0]    | V <sub>CC</sub> ≥ 4.5 V | - 1    | 9       | 20   |  |

|                             | t <sub>CSH</sub>              |              | $V_{CC} < 4.5 V$        |        | 12      | ns   |  |

|                             | 4                             |              | $V_{CC} \ge 4.5 V$      | - 1    | 9       | 20   |  |

| MOEV dolou time             | t <sub>REL</sub>              | MCLK,        | $V_{CC} < 4.5 V$        |        | 12      | ns   |  |

| MOEX delay time             | +                             | MOEX         | V <sub>CC</sub> ≥ 4.5 V | - 1    | 9       | 20   |  |

|                             | t <sub>REH</sub>              |              | $V_{CC} < 4.5 V$        |        | 12      | ns   |  |

| Data set up                 |                               | MCLK,        | V <sub>CC</sub> ≥ 4.5 V | 19     |         | 20   |  |

| →MCLK↑ time t <sub>DS</sub> |                               | MADATA[15:0] | $V_{CC} < 4.5 V$        | 37     | -       | ns   |  |

| MCLK↑→                      | MCLK, V <sub>CC</sub> ≥ 4.5 V |              | - 0                     |        | 20      |      |  |

| Data hold time              | t <sub>DH</sub>               | MADATA[15:0] | $V_{CC} < 4.5 V$        | 0      | -       | ns   |  |

|                             |                               |              | $V_{CC} \ge 4.5 V$      | - 1    | 9       | 20   |  |

| MM/EX dolou time            | t <sub>WEL</sub>              | MCLK,        | $V_{CC} < 4.5 V$        |        | 12      | ns   |  |

| MWEX delay time             | +                             | MWEX         | V <sub>CC</sub> ≥ 4.5 V | - 1    | 9       | 20   |  |

|                             | t <sub>WEH</sub>              |              | $V_{CC} < 4.5 V$        |        | 12      | ns   |  |

|                             |                               |              | V <sub>CC</sub> ≥ 4.5 V | - 1    | 9       | 20   |  |

| MDQM[1:0]                   | t <sub>DQML</sub>             | MCLK,        | $V_{CC} < 4.5 V$        |        | 12      | ns   |  |

| delay time                  |                               | MDQM[1:0]    | V <sub>CC</sub> ≥ 4.5 V | - 1    | 9       | 20   |  |

|                             | t <sub>DQMH</sub>             |              | V <sub>CC</sub> < 4.5 V |        | 12      | ns   |  |

| MCLK↑→                      |                               | MCLK,        | $V_{CC} \ge 4.5 V$      | MCLK+1 | MCLK+18 | 20   |  |

| Data output time            | t <sub>ODS</sub>              | MADATA[15:0] | $V_{CC}$ < 4.5 V        |        | MCLK+24 | ns   |  |

| MCLK↑→                      | +                             | MCLK,        | $V_{CC} \ge 4.5 V$      | - 1    | 18      | 20   |  |

| Data hold time              | t <sub>OD</sub>               | MADATA[15:0] | V <sub>CC</sub> < 4.5 V |        | 24      | ns   |  |

#### Note:

\_

When the external load capacitance  $C_L = 30 \ pF$

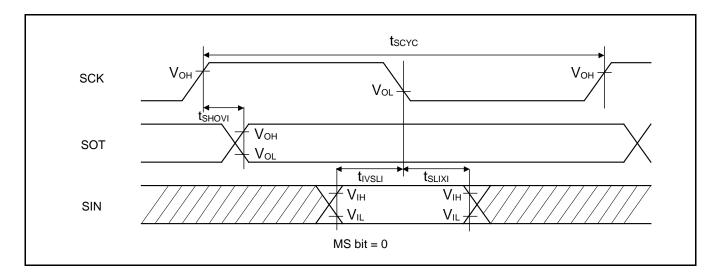

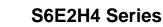

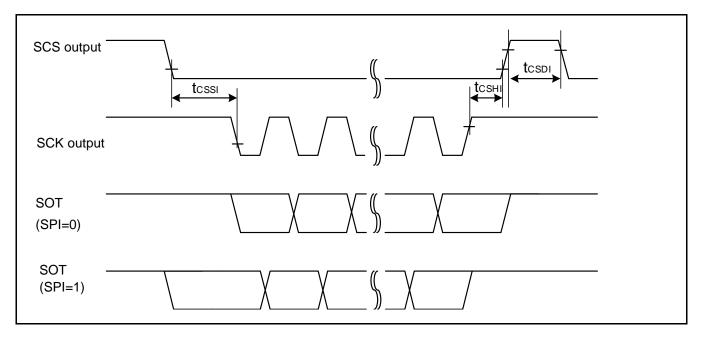

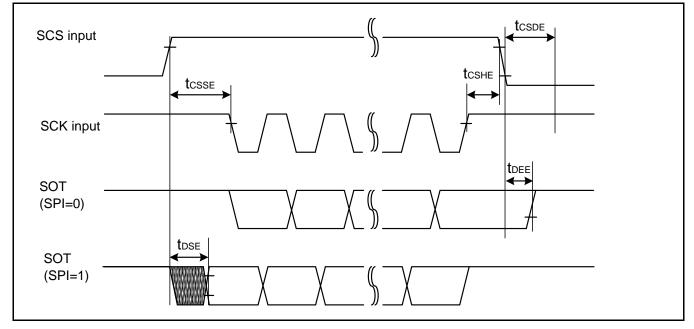

#### Synchronous Serial (SPI = 1, SCINV = 1)

| $(V_{CC} = 2.7V \text{ to } 5.5V)$ | $V_{SS} = 0V$ ) |

|------------------------------------|-----------------|

|------------------------------------|-----------------|

| D                          |                    | <b>D</b> ' <b>N</b> |                         | V <sub>CC</sub> < 4.5   | 5 V  | $V_{CC} \ge 4.$         |      |      |

|----------------------------|--------------------|---------------------|-------------------------|-------------------------|------|-------------------------|------|------|

| Parameter                  | Symbol             | Pin Name            | Conditions              | Min                     | Max  | Min                     | Max  | Unit |

| Serial clock cycle time    | t <sub>SCYC</sub>  | SCKx                |                         | 4t <sub>CYCP</sub>      | -    | 4t <sub>CYCP</sub>      | -    | ns   |

| SCK↓→SOT delay time        | t <sub>SLOVI</sub> | SCKx,<br>SOTx       |                         | - 30                    | + 30 | - 20                    | + 20 | ns   |

| SIN→SCK↑<br>setup time     | t <sub>IVSHI</sub> | SCKx,<br>SINx       | Internal shift<br>clock | 50                      | -    | 30                      | -    | ns   |

| SCK↑→SIN hold time         | t <sub>SHIXI</sub> | SCKx,<br>SINx       | operation               | 0                       | -    | 0                       | -    | ns   |

| SOT→SCK↑ delay time        | t <sub>SOVHI</sub> | SCKx,<br>SOTx       |                         | 2t <sub>CYCP</sub> - 30 | -    | 2tC <sub>YCP</sub> - 30 | -    | ns   |

| Serial clock L pulse width | t <sub>SLSH</sub>  | SCKx                |                         | 2t <sub>CYCP</sub> - 10 | -    | 2t <sub>CYCP</sub> - 10 | -    | ns   |

| Serial clock H pulse width | t <sub>SHSL</sub>  | SCKx                | ]                       | t <sub>CYCP</sub> + 10  | -    | t <sub>CYCP</sub> + 10  | -    | ns   |

| SCK↓→SOT delay time        | t <sub>SLOVE</sub> | SCKx,<br>SOTx       |                         | -                       | 50   | -                       | 30   | ns   |

| SIN→SCK↑<br>setup time     | t <sub>IVSHE</sub> | SCKx,<br>SINx       | External shift<br>clock | 10                      | -    | 10                      | -    | ns   |

| SCK↑→SIN hold time         | t <sub>SHIXE</sub> | SCKx,<br>SINx       | operation               | 20                      | -    | 20                      | -    | ns   |

| SCK falling time           | t <sub>F</sub>     | SCKx                | 1                       | -                       | 5    | -                       | 5    | ns   |

| SCK rising time            | t <sub>R</sub>     | SCKx                |                         | -                       | 5    | -                       | 5    | ns   |

#### Notes:

- The above characteristics apply to CLK synchronous mode.

- t<sub>CYCP</sub> indicates the APB bus clock cycle time.

About the APB bus number which multi-function serial is connected to, see 8. Block Diagram in this data sheet.

- These characteristics only guarantee the same relocate port number. For example, the combination of SCLKx\_0 and SOTx\_1 is not guaranteed.

- When the external load capacitance  $C_L = 30 \text{ pF}$ .

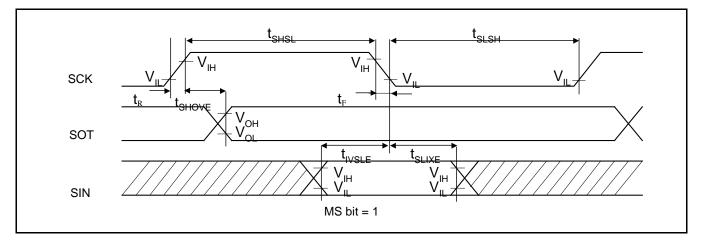

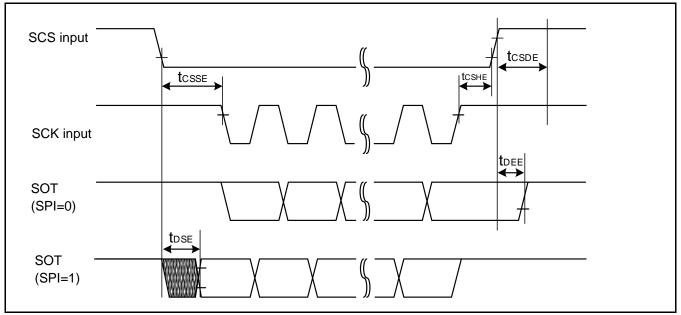

#### High-speed Synchronous Serial (SPI = 0, SCINV = 0)

$(V_{CC} = 2.7V \text{ to } 5.5V, V_{SS} = 0V)$

| Parameter                  | Symbol             | Pin Name      | Conditions                        | $V_{CC}$ < 4.5 V       |     | V <sub>CC</sub> ≥ 4.5 V |     | Unit |

|----------------------------|--------------------|---------------|-----------------------------------|------------------------|-----|-------------------------|-----|------|

| Parameter                  | Symbol             | Pin Name      | Conditions                        | Min                    | Max | Min                     | Max | Unit |

| Serial clock cycle time    | t <sub>scyc</sub>  | SCKx          |                                   | 4t <sub>CYCP</sub>     | -   | 4t <sub>CYCP</sub>      | -   | ns   |

| SCK↓→SOT delay time        | t <sub>SLOVI</sub> | SCKx,<br>SOTx |                                   | -10                    | +10 | -10                     | +10 | ns   |

| SIN→SCK↑                   |                    | SCKx,         | Internal shift<br>clock operation | 14                     |     | 12.5                    | _   | 20   |

| setup time                 | t <sub>IVSHI</sub> | SINx          | clock operation                   | 12.5*                  | -   | 12.0                    | -   | ns   |

| SCK∱→SIN hold time         | t <sub>SHIXI</sub> | SCKx,<br>SINx |                                   | 5                      | -   | 5                       | -   | ns   |

| Serial clock L pulse width | t <sub>SLSH</sub>  | SCKx          |                                   | 2t <sub>CYCP</sub> – 5 | -   | 2t <sub>CYCP</sub> – 5  | -   | ns   |

| Serial clock H pulse width | t <sub>SHSL</sub>  | SCKx          |                                   | t <sub>CYCP</sub> + 10 | -   | t <sub>CYCP</sub> + 10  | -   | ns   |

| SCK↓→SOT delay time        | t <sub>SLOVE</sub> | SCKx,<br>SOTx | External shift                    | -                      | 15  | -                       | 15  | ns   |

| SIN→SCK↑<br>setup time     | t <sub>IVSHE</sub> | SCKx,<br>SINx | clock operation                   | 5                      | -   | 5                       | -   | ns   |

|                            |                    | SCKx,         | -                                 | 5                      |     | <b>_</b>                |     |      |

| SCK∱→SIN hold time         | t <sub>SHIXE</sub> | SINx          |                                   | 5                      | -   | 5                       | -   | ns   |

| SCK falling time           | t <sub>F</sub>     | SCKx          |                                   | -                      | 5   | -                       | 5   | ns   |

| SCK rising time            | t <sub>R</sub>     | SCKx          |                                   | -                      | 5   | -                       | 5   | ns   |

#### Notes:

- The above characteristics apply to CLK synchronous mode.

- t<sub>CYCP</sub> indicates the APB bus clock cycle time.

About the APB bus number which multi-function serial is connected to, see 8. Block Diagram in this data sheet.

- These characteristics only guarantee the following pins.

- No chip select: SIN4\_1, SOT4\_1, SCK4\_1

- Chip select: SIN6\_1, SOT6\_1, SCK6\_1, SCS6\_1

- When the external load capacitance  $C_L = 30 \text{ pF}$ . (For \*, when  $C_L = 10 \text{ pF}$ )

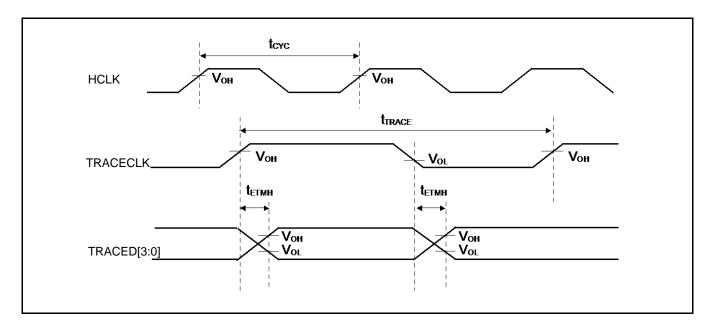

#### 12.4.15 ETM Timing

(V<sub>CC</sub> = 2.7V to 5.5V, V<sub>SS</sub> = 0V)

|                             |                       |                  | •                  | Va    | alue | Unit | Bernarke |

|-----------------------------|-----------------------|------------------|--------------------|-------|------|------|----------|

| Parameter                   | Symbol                | Pin Name         | Conditions         | Min   | Max  | Unit | Remarks  |

| Data hald                   | t===                  | TRACECLK,        | $V_{CC} \ge 4.5 V$ | 2     | 9    |      |          |

| Data hold t <sub>ETMH</sub> | TRACED[3:0]           | $V_{CC}$ < 4.5 V | 2                  | 15    | ns   |      |          |

| TRACECLK                    | 1/+                   | TRACECLK         | $V_{CC} \ge 4.5 V$ | -     | 50   | MHz  |          |

| frequency                   | 1/ t <sub>TRACE</sub> |                  | $V_{CC}$ < 4.5 V   | -     | 32   | MHz  |          |

| TRACECLK                    | +                     |                  | $V_{CC} \ge 4.5 V$ | 20    | -    | ns   |          |

| clock cycle                 | t <sub>TRACE</sub>    |                  | $V_{CC}$ < 4.5 V   | 31.25 | -    | ns   |          |

#### Note:

\_

When the external load capacitance  $C_L$ = 30 pF.

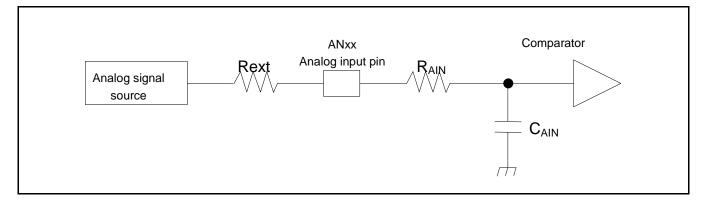

# (Equation 1) $t_S \ge (R_{AIN} + Rext) \times C_{AIN} \times 9$

|                                        | ts:                | Sampling time                                                       |

|----------------------------------------|--------------------|---------------------------------------------------------------------|

|                                        | R <sub>AIN</sub> : | Input resistance of A/D = 1.2 k $\Omega$ at 4.5 V < AV_{CC} < 5.5 V |

|                                        |                    | Input resistance of A/D = 1.8 k $\Omega$ at 2.7 V < AV_{CC} < 4.5 V |

|                                        | C <sub>AIN</sub> : | Input capacity of A/D = 12.05 pF at 2.7 V < AV_{CC} < 5.5 V         |

|                                        | Rext:              | Output impedance of external circuit                                |

| (Equation 2) $t_c = t_{CCK} \times 14$ | 4                  |                                                                     |

|                                        | t <sub>C</sub> :   | Compare time                                                        |

|                                        | t <sub>сск</sub> : | Compare clock cycle                                                 |

|                                        |                    |                                                                     |

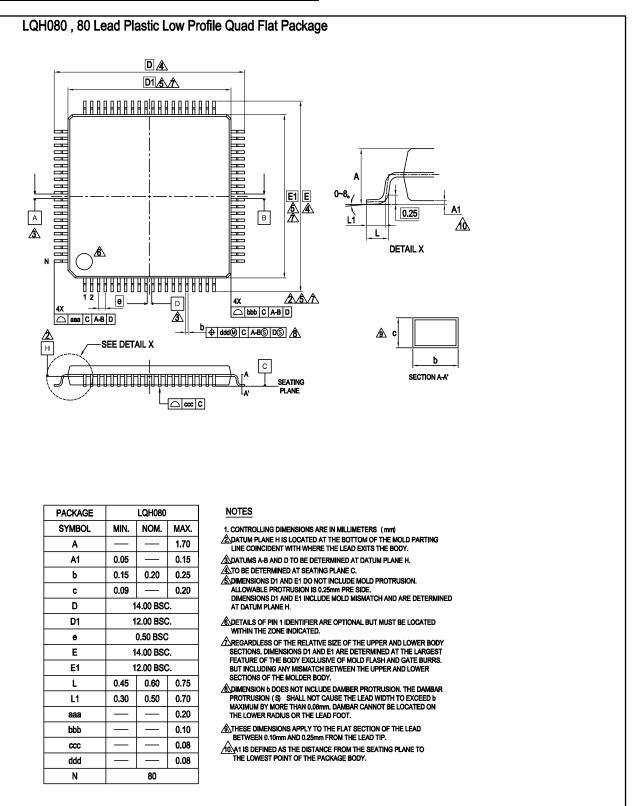

| Package Type | Package Code |

|--------------|--------------|

| LQFP 80      | LQH080       |

## Sales, Solutions, and Legal Information

#### Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

| Products                 |                           |

|--------------------------|---------------------------|

| Automotive               | cypress.com/go/automotive |

| Clocks & Buffers         | cypress.com/go/clocks     |

| Interface                | cypress.com/go/interface  |

| Lighting & Power Control | cypress.com/go/powerpsoc  |

| Memory                   | cypress.com/go/memory     |

| PSoC                     | cypress.com/go/psoc       |

| Touch Sensing            | cypress.com/go/touch      |

| USB Controllers          | cypress.com/go/USB        |

| Wireless/RF              | cypress.com/go/wireless   |

| Spansion Products        | spansion.com/products     |

PSoC® Solutions psoc.cypress.com/solutions

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP

Cypress Developer Community Community | Forums | Blogs | Video | Training

Technical Support cypress.com/go/support

Cypress, the Cypress logo, Spansion<sup>®</sup>, the Spansion logo, MirrorBit<sup>®</sup>, MirrorBit<sup>®</sup> Eclipse<sup>TM</sup>, ORNAND<sup>TM</sup>, Easy DesignSim<sup>TM</sup>, Traveo<sup>TM</sup> and combinations thereof, are trademarks and registered trademarks of Cypress Semiconductor Corp. ARM and Cortex are the registered trademarks of ARM Limited in the EU and other countries. All other trademarks or registered trademarks referenced herein are the property of their respective owners.

© Cypress Semiconductor Corporation, 2015. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

This Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, compilation, or representation of this Source Code except as specified above is prohibited without the express written permission of Cypress.

Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress' product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Use may be limited by and subject to the applicable Cypress software license agreement.