#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 16                                                                         |

| Program Memory Size        | 16KB (8K x 16)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 3.8K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.15V ~ 3.6V                                                               |

| Data Converters            | A/D 10x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-QFN (6x6)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f24j11-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

#### 6.3.5 STATUS REGISTER

The STATUS register in Register 6-2, contains the arithmetic status of the ALU. The STATUS register can be the operand for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC, C, OV or N bits, then the write to these five bits is disabled.

These bits are set or cleared according to the device logic. Therefore, the result of an instruction with the STATUS register as destination may be different than intended. For example, CLRF STATUS will set the Z bit but leave the other bits unchanged. The STATUS

register then reads back as '000u u1uu'. It is recommended, therefore, that only BCF, BSF, SWAPF, MOVFF and MOVWF instructions are used to alter the STATUS register because these instructions do not affect the Z, C, DC, OV or N bits in the STATUS register.

For other instructions not affecting any Status bits, see the instruction set summary in Table 27-2 and Table 27-3.

Note: The <u>C</u> and <u>DC</u> bits operate as a borrow and <u>digit</u> borrow bits respectively, in subtraction.

#### REGISTER 6-2: STATUS REGISTER (ACCESS FD8h)

| U-0           | U-0                                                                                                                              | U-0                                    | R/W-x            | R/W-x                    | R/W-x           | R/W-x             | R/W-x            |  |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|------------------|--------------------------|-----------------|-------------------|------------------|--|--|

| —             | —                                                                                                                                | —                                      | N                | OV                       | Z               | DC <sup>(1)</sup> | C <sup>(2)</sup> |  |  |

| bit 7         |                                                                                                                                  |                                        |                  |                          |                 |                   | bit (            |  |  |

|               |                                                                                                                                  |                                        |                  |                          |                 |                   |                  |  |  |

| Legend:       |                                                                                                                                  |                                        |                  |                          |                 |                   |                  |  |  |

| R = Readabl   | e bit                                                                                                                            | W = Writable                           | bit              | U = Unimplen             | nented bit, rea | d as '0'          |                  |  |  |

| -n = Value at | t POR                                                                                                                            | '1' = Bit is set                       | t                | '0' = Bit is clea        | ared            | x = Bit is unkr   | nown             |  |  |

|               |                                                                                                                                  |                                        |                  |                          |                 |                   |                  |  |  |

| bit 7-5       | Unimplemer                                                                                                                       | nted: Read as '                        | 0'               |                          |                 |                   |                  |  |  |

| bit 4         | N: Negative                                                                                                                      | bit                                    |                  |                          |                 |                   |                  |  |  |

|               | This bit is use<br>(ALU MSB =                                                                                                    | •                                      | rithmetic (2's c | omplement). It i         | ndicates wheth  | ner the result wa | as negative      |  |  |

|               | 1 = Result wa<br>0 = Result wa                                                                                                   |                                        |                  |                          |                 |                   |                  |  |  |

| bit 3         | OV: Overflow bit                                                                                                                 |                                        |                  |                          |                 |                   |                  |  |  |

|               |                                                                                                                                  | ed for signed ar<br>s the sign bit (bi |                  | omplement). It in state. | ndicates an ov  | erflow of the 7-b | oit magnitude,   |  |  |

|               | 1 = Overflow<br>0 = No overfl                                                                                                    |                                        | gned arithmeti   | c (in this arithm        | etic operation) |                   |                  |  |  |

| bit 2         | Z: Zero bit                                                                                                                      |                                        |                  |                          |                 |                   |                  |  |  |

|               | 1 = The result of an arithmetic or logic operation is zero                                                                       |                                        |                  |                          |                 |                   |                  |  |  |

|               | 0 = The result of an arithmetic or logic operation is not zero                                                                   |                                        |                  |                          |                 |                   |                  |  |  |

| bit 1         | DC: Digit carry/borrow bit <sup>(1)</sup>                                                                                        |                                        |                  |                          |                 |                   |                  |  |  |

|               | For ADDWF, ADDLW, SUBLW and SUBWF instructions:<br>1 = A carry-out from the 4 <sup>th</sup> low-order bit of the result occurred |                                        |                  |                          |                 |                   |                  |  |  |

|               |                                                                                                                                  | out from the 4 <sup>th</sup>           |                  |                          | ineu            |                   |                  |  |  |

| bit 0         | C: Carry/bor                                                                                                                     |                                        |                  |                          |                 |                   |                  |  |  |

|               |                                                                                                                                  | ADDLW, SUBLW                           | and SUBWF in     | structions:              |                 |                   |                  |  |  |

|               | 1 = A carry-c                                                                                                                    | out from the MS                        | b of the result  | occurred                 |                 |                   |                  |  |  |

|               | 0 = No carry-                                                                                                                    | out from the M                         | Sb of the resu   | It occurred              |                 |                   |                  |  |  |

| Note 1: Fo    | or borrow. the p                                                                                                                 | olaritv is revers                      | ed. A subtract   | on is executed b         | by adding the 2 | 's complement     | of the second    |  |  |

**Note 1:** For borrow, the polarity is reversed. A subtraction is executed by adding the 2's complement of the second operand.

### 7.0 FLASH PROGRAM MEMORY

The Flash program memory is readable, writable and erasable during normal operation over the entire VDD range.

A read from program memory is executed on 1 byte at a time. A write to program memory is executed on blocks of 64 bytes at a time or 2 bytes at a time. Program memory is erased in blocks of 1024 bytes at a time. A bulk erase operation may not be issued from user code.

Writing or erasing program memory will cease instruction fetches until the operation is complete. The program memory cannot be accessed during the write or erase, therefore, code cannot execute. An internal programming timer terminates program memory writes and erases.

A value written to program memory does not need to be a valid instruction. Executing a program memory location that forms an invalid instruction results in a NOP.

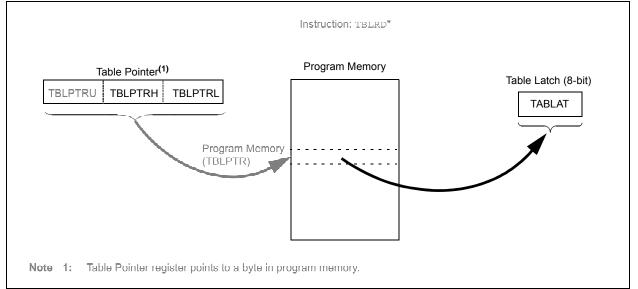

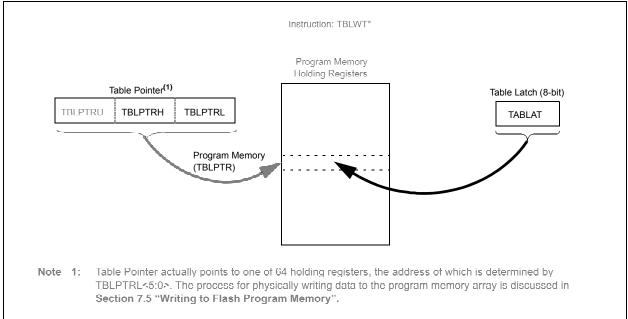

#### 7.1 Table Reads and Table Writes

In order to read and write program memory, there are two operations that allow the processor to move bytes between the program memory space and the data RAM:

- Table Read (TBLRD)

- Table Write (TBLWT)

The program memory space is 16 bits wide, while the data RAM space is 8 bits wide. Table reads and table writes move data between these two memory spaces through an 8-bit register (TABLAT).

Table read operations retrieve data from program memory and place it into the data RAM space. Figure 7-1 illustrates the operation of a table read with program memory and data RAM.

Table write operations store data from the data memory space into holding registers in program memory. The procedure to write the contents of the holding registers into program memory is detailed in **Section 7.5** "**Writing to Flash Program Memory**". Figure 7-2 illustrates the operation of a table write with program memory and data RAM.

Table operations work with byte entities. A table block containing data, rather than program instructions, is not required to be word-aligned. Therefore, a table block can start and end at any byte address. If a table write is being used to write executable code into program memory, program instructions will need to be word-aligned.

FIGURE 7-1:

#### TABLE READ OPERATION

#### FIGURE 7-2: TABLE WRITE OPERATION

### 7.2 Control Registers

Several control registers are used in conjunction with the TBLRD and TBLWT instructions. Those are:

- EECON1 register

- · EECON2 register

- TABLAT register

- TBLPTR registers

#### 7.2.1 EECON1 AND EECON2 REGISTERS

The EECON1 register (Register 7-1) is the control register for memory accesses. The EECON2 register is not a physical register; it is used exclusively in the memory write and erase sequences. Reading EECON2 will read all '0's.

The WPROG bit, when set, will allow programming two bytes per word on the execution of the WR command. If this bit is cleared, the WR command will result in programming on a block of 64 bytes. The FREE bit, when set, will allow a program memory erase operation. When FREE is set, the erase operation is initiated on the next WR command. When FREE is clear, only writes are enabled.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. The WRERR bit is set in hardware when the WR bit is set, and cleared when the internal programming timer expires and the write operation is complete.

| Note: | During normal operation, the WRERR is       |  |  |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|--|--|

|       | read as '1'. This can indicate that a write |  |  |  |  |  |  |  |

|       | operation was prematurely terminated by     |  |  |  |  |  |  |  |

|       | a Reset, or a write operation was           |  |  |  |  |  |  |  |

|       | attempted improperly.                       |  |  |  |  |  |  |  |

The WR control bit initiates write operations. The bit cannot be cleared, only set, in software. It is cleared in hardware at the completion of the write operation.

#### REGISTER 10-3: ODCON3: PERIPHERAL OPEN-DRAIN CONTROL REGISTER 3 (BANKED F40h)

| U-0       | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  | R/W-0  |  |

|-----------|-----|-----|-----|-----|-----|--------|--------|--|

| —         | _   | -   | —   | —   | _   | SPI2OD | SPI10D |  |

| bit 7 bit |     |     |     |     |     |        |        |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

| bit 7-2 | Unimplemented: Read as '0'                                                                        |

|---------|---------------------------------------------------------------------------------------------------|

| bit 1   | SPI2OD: SPI2 Open-Drain Output Enable bit                                                         |

|         | <ol> <li>1 = Open-drain capability enabled</li> <li>0 = Open-drain capability disabled</li> </ol> |

| bit 0   | SPI10D: SPI1 Open-Drain Output Enable bit                                                         |

|         | <ol> <li>1 = Open-drain capability enabled</li> <li>0 = Open-drain capability disabled</li> </ol> |

#### REGISTER 10-4: PADCFG1: PAD CONFIGURATION CONTROL REGISTER 1 (BANKED F3Ch)

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0                    | R/W-0                    | R/W-0  |

|-------|-----|-----|-----|-----|--------------------------|--------------------------|--------|

| —     | _   | —   | —   | —   | RTSECSEL1 <sup>(1)</sup> | RTSECSEL0 <sup>(1)</sup> | PMPTTL |

| bit 7 |     |     |     |     |                          |                          | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7-3 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                        |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 2-1 | RTSECSEL<1:0>: RTCC Seconds Clock Output Select bits <sup>(1)</sup>                                                                                                                                                                                                                                               |

|         | <ul> <li>11 = Reserved; do not use</li> <li>10 = RTCC source clock is selected for the RTCC pin (can be INTRC or T1OSC, depending on the RTCOSC (CONFIG3L&lt;1&gt;) setting)</li> <li>01 = RTCC seconds clock is selected for the RTCC pin</li> <li>00 = RTCC alarm pulse is selected for the RTCC pin</li> </ul> |

| bit 0   | <ul> <li>PMPTTL: PMP Module TTL Input Buffer Select bit</li> <li>1 = PMP module uses TTL input buffers</li> <li>0 = PMP module uses Schmitt Trigger input buffers</li> </ul>                                                                                                                                      |

#### 10.7.3.2 Output Mapping

In contrast to inputs, the outputs of the PPS options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPORx registers are used to control output mapping. The value of the bit field corresponds to one of the peripherals and that peripheral's output is mapped to the pin (see Table 10-14).

Because of the mapping technique, the list of peripherals for output mapping also includes a null value of '00000'. This permits any given pin to remain disconnected from the output of any of the pin selectable peripherals.

| Function | Output Function<br>Number <sup>(1)</sup> | Output Name                                             |

|----------|------------------------------------------|---------------------------------------------------------|

| NULL     | 0                                        | NULL <sup>(2)</sup>                                     |

| C10UT    | 1                                        | Comparator 1 Output                                     |

| C2OUT    | 2                                        | Comparator 2 Output                                     |

| TX2/CK2  | 5                                        | EUSART2 Asynchronous Transmit/Asynchronous Clock Output |

| DT2      | 6                                        | EUSART2 Synchronous Transmit                            |

| SDO2     | 9                                        | SPI2 Data Output                                        |

| SCK2     | 10                                       | SPI2 Clock Output                                       |

| SSDMA    | 12                                       | SPI DMA Slave Select                                    |

| ULPOUT   | 13                                       | Ultra Low-Power Wake-up Event                           |

| CCP1/P1A | 14                                       | ECCP1 Compare or PWM Output Channel A                   |

| P1B      | 15                                       | ECCP1 Enhanced PWM Output, Channel B                    |

| P1C      | 16                                       | ECCP1 Enhanced PWM Output, Channel C                    |

| P1D      | 17                                       | ECCP1 Enhanced PWM Output, Channel D                    |

| CCP2/P2A | 18                                       | ECCP2 Compare or PWM Output                             |

| P2B      | 19                                       | ECCP2 Enhanced PWM Output, Channel B                    |

| P2C      | 20                                       | ECCP2 Enhanced PWM Output, Channel C                    |

| P2D      | 21                                       | ECCP2 Enhanced PWM Output, Channel D                    |

#### TABLE 10-14: SELECTABLE OUTPUT SOURCES (MAPS FUNCTION TO OUTPUT)

**Note 1:** Value assigned to the RPn<4:0> pins corresponds to the peripheral output function number.

2: The NULL function is assigned to all RPn outputs at device Reset and disables the RPn output function.

#### **11.4** Application Examples

This section introduces some potential applications for the PMP module.

#### 11.4.1 MULTIPLEXED MEMORY OR PERIPHERAL

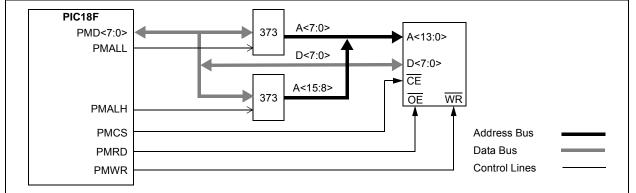

Figure 11-27 demonstrates the hookup of a memory or another addressable peripheral in Full Multiplex mode. Consequently, this mode achieves the best pin saving from the microcontroller perspective. However, for this configuration, there needs to be some external latches to maintain the address.

#### 11.4.2 PARTIALLY MULTIPLEXED MEMORY OR PERIPHERAL

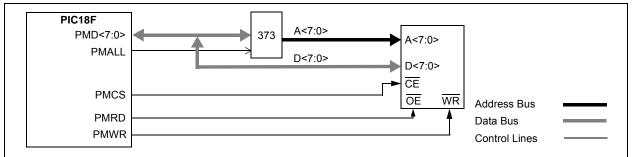

Partial multiplexing implies using more pins; however, for a few extra pins, some extra performance can be achieved. Figure 11-28 provides an example of a memory or peripheral that is partially multiplexed with an external latch. If the peripheral has internal latches, as displayed in Figure 11-29, then no extra circuitry is required except for the peripheral itself.

#### FIGURE 11-28: EXAMPLE OF A PARTIALLY MULTIPLEXED ADDRESSING APPLICATION

#### FIGURE 11-29: EXAMPLE OF AN 8-BIT MULTIPLEXED ADDRESS AND DATA APPLICATION

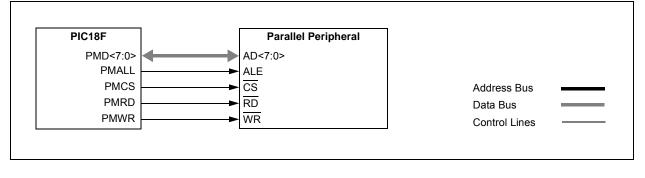

#### 13.8.4 TIMER1 GATE SINGLE PULSE MODE

When Timer1 Gate Single Pulse mode is enabled, it is possible to capture a single pulse gate event. Timer1 Gate Single Pulse mode is first enabled by setting the T1GSPM bit in the T1GCON register. Next, the T1GGO/T1DONE bit in the T1GCON register must be set. The Timer1 will be fully enabled on the next incrementing edge. On the next trailing edge of the pulse, the T1GGO/T1DONE bit will automatically be cleared. No other gate events will be allowed to increment Timer1 until the T1GGO/T1DONE bit is once again set in software. Clearing the T1GSPM bit of the T1GCON register will also clear the T1GGO/T1DONE bit. See Figure 13-6 for timing details.

Enabling the Toggle mode and the Single Pulse mode, simultaneously, will permit both sections to work together. This allows the cycle times on the Timer1 gate source to be measured. See Figure 13-7 for timing details.

#### 13.8.5 TIMER1 GATE VALUE STATUS

When the Timer1 gate value status is utilized, it is possible to read the most current level of the gate control value. The value is stored in the T1GVAL bit in the T1GCON register. The T1GVAL bit is valid even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

### FIGURE 13-6: TIMER1 GATE SINGLE PULSE MODE

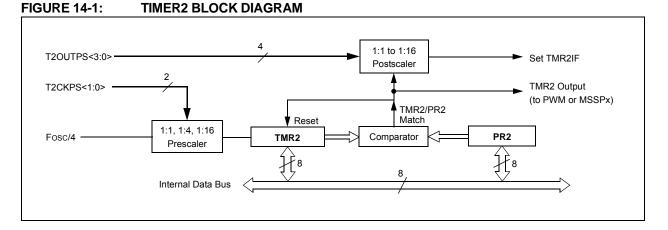

### 14.2 Timer2 Interrupt

Timer2 can also generate an optional device interrupt. The Timer2 output signal (TMR2 to PR2 match) provides the input for the 4-bit output counter/postscaler. This counter generates the TMR2 Match Interrupt Flag, which is latched in TMR2IF (PIR1<1>). The interrupt is enabled by setting the TMR2 Match Interrupt Enable bit, TMR2IE (PIE1<1>).

A range of 16 postscaler options (from 1:1 through 1:16 inclusive) can be selected with the postscaler control bits, T2OUTPS<3:0> (T2CON<6:3>).

### 14.3 Timer2 Output

The unscaled output of TMR2 is available primarily to the ECCP modules, where it is used as a time base for operations in PWM mode.

Timer2 can be optionally used as the shift clock source for the MSSP modules operating in SPI mode. Additional information is provided in Section 19.0 "Master Synchronous Serial Port (MSSP) Module".

#### TABLE 14-1: REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER

| Name   | Bit 7                | Bit 6         | Bit 5    | Bit 4         | Bit 3    | Bit 2  | Bit 1   | Bit 0   | Reset<br>Values<br>on Page: |

|--------|----------------------|---------------|----------|---------------|----------|--------|---------|---------|-----------------------------|

| INTCON | GIE/GIEH             | PEIE/GIEL     | TMR0IE   | <b>INTOIE</b> | RBIE     | TMR0IF | INT0IF  | RBIF    | 90                          |

| PIR1   | PMPIF <sup>(1)</sup> | ADIF          | RC1IF    | TX1IF         | SSP1IF   | CCP1IF | TMR2IF  | TMR1IF  | 92                          |

| PIE1   | PMPIE <sup>(1)</sup> | ADIE          | RC1IE    | TX1IE         | SSP1IE   | CCP1IE | TMR2IE  | TMR1IE  | 92                          |

| IPR1   | PMPIP <sup>(1)</sup> | ADIP          | RC1IP    | TX1IP         | SSP1IP   | CCP1IP | TMR2IP  | TMR1IP  | 92                          |

| TMR2   | Timer2 Register      |               |          |               |          |        |         |         | 91                          |

| T2CON  | _                    | T2OUTPS3      | T2OUTPS2 | T2OUTPS1      | T2OUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | 91                          |

| PR2    | Timer2 Per           | riod Register |          |               |          |        |         |         | 91                          |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the Timer2 module.

Note 1: These bits are only available in 44-pin devices.

#### 17.1.1 RTCC CONTROL REGISTERS

### REGISTER 17-1: RTCCFG: RTCC CONFIGURATION REGISTER (BANKED F3Fh)<sup>(1)</sup>

| R/W-0         | U-0                      | R/W-0                                                     | R-0            | R-0                    | R/W-0           | R/W-0            | R/W-0           |

|---------------|--------------------------|-----------------------------------------------------------|----------------|------------------------|-----------------|------------------|-----------------|

| RTCEN         | (2)                      | RTCWREN                                                   | RTCSYNC        | HALFSEC <sup>(3)</sup> | RTCOE           | RTCPTR1          | RTCPTR0         |

| bit 7         |                          |                                                           |                | -1                     |                 |                  | bit 0           |

|               |                          |                                                           |                |                        |                 |                  |                 |

| Legend:       |                          |                                                           |                |                        |                 |                  |                 |

| R = Reada     | able bit                 | W = Writable                                              | bit            | U = Unimplen           | nented bit, rea | d as '0'         |                 |

| -n = Value    | at POR                   | '1' = Bit is set                                          |                | '0' = Bit is clea      | ared            | x = Bit is unk   | nown            |

| bit 7         |                          | ГСС Enable bit <sup>(2)</sup>                             |                |                        |                 |                  |                 |

|               |                          | module is enable                                          |                |                        |                 |                  |                 |

|               |                          | module is disable                                         |                |                        |                 |                  |                 |

| bit 6         | Unimpleme                | ented: Read as '                                          | כי             |                        |                 |                  |                 |

| bit 5         | RTCWREN                  | : RTCC Value Re                                           | egisters Write | Enable bit             |                 |                  |                 |

|               |                          | ALH and RTCVAL                                            | •              |                        | •               |                  |                 |

| <b>h</b> :+ 4 |                          | ALH and RTCVAL                                            | -              |                        | -               | en to by the use | r               |

| bit 4         |                          | : RTCC Value Re<br>ALH, RTCVALL a                         | -              | -                      |                 | anding due to a  | rollover ripple |

|               |                          | in an invalid da                                          |                |                        | shariye wille h |                  |                 |

|               | •                        | er is read twice a                                        |                |                        |                 |                  |                 |

|               |                          | ALH, RTCVALL of                                           |                | registers can b        | e read without  | concern over a   | rollover ripple |

| bit 3         |                          | Half-Second Sta                                           |                |                        |                 |                  |                 |

|               |                          | d half period of a<br>alf period of a sec                 |                |                        |                 |                  |                 |

| bit 2         |                          | TCC Output Enat                                           |                |                        |                 |                  |                 |

|               | 1 = RTCC                 | clock output enal                                         | bled           |                        |                 |                  |                 |

|               |                          | clock output disa                                         |                |                        |                 |                  |                 |

| bit 1-0       |                          | :0>: RTCC Value                                           | -              |                        |                 |                  |                 |

|               | RTCVALL<                 | the correspondi<br>7:0> registers;<br>7:0> until it react | the RTCPTI     |                        |                 |                  |                 |

|               | RTCVALH<                 | <u>:7:0&gt;:</u>                                          |                |                        |                 |                  |                 |

|               | 00 = Minute              |                                                           |                |                        |                 |                  |                 |

|               | 01 = Weeko<br>10 = Month |                                                           |                |                        |                 |                  |                 |

|               | 11 <b>= Reser</b>        |                                                           |                |                        |                 |                  |                 |

|               | RTCVALL<                 | <u>7:0&gt;:</u>                                           |                |                        |                 |                  |                 |

|               | 00 = Secon               |                                                           |                |                        |                 |                  |                 |

|               | 01 = Hours<br>10 = Day   |                                                           |                |                        |                 |                  |                 |

|               | 11 = Year                |                                                           |                |                        |                 |                  |                 |

| Note 1:       |                          | gister is only affe                                       | cted by a $PO$ | P                      |                 |                  |                 |

|               |                          | CEN hit is only and                                       | -              |                        |                 |                  |                 |

- 2: A write to the RTCEN bit is only allowed when RTCWREN = 1.

- 3: This bit is read-only. It is cleared to '0' on a write to the lower half of the MINSEC register.

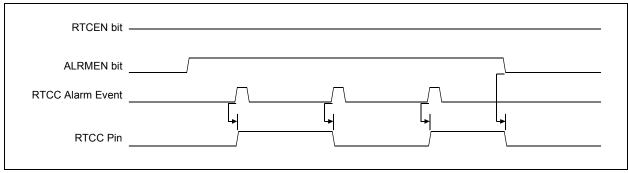

When ALRMCFG = 00 and the CHIME bit = 0 (ALRMCFG<6>), the repeat function is disabled and only a single alarm will occur. The alarm can be repeated up to 255 times by loading the ALRMRPT register with FFh.

After each alarm is issued, the ALRMRPT register is decremented by one. Once the register has reached '00', the alarm will be issued one last time.

After the alarm is issued a last time, the ALRMEN bit is cleared automatically and the alarm turned off. Indefinite repetition of the alarm can occur if the CHIME bit = 1.

When CHIME = 1, the alarm is not disabled when the ALRMRPT register reaches '00', but it rolls over to FF and continues counting indefinitely.

#### 17.3.2 ALARM INTERRUPT

At every alarm event, an interrupt is generated. Additionally, an alarm pulse output is provided that operates at half the frequency of the alarm.

The alarm pulse output is completely synchronous with the RTCC clock and can be used as a trigger clock to other peripherals. This output is available on the RTCC pin. The output pulse is a clock with a 50% duty cycle and a frequency half that of the alarm event (see Figure 17-6).

The RTCC pin also can output the seconds clock. The user can select between the alarm pulse, generated by the RTCC module, or the seconds clock output.

The RTSECSEL (PADCFG1<1:0>) bits select between these two outputs:

- Alarm pulse RTSECSEL<1:0> = 00

- Seconds clock RTSECSEL<1:0> = 0

#### FIGURE 17-6: TIMER PULSE GENERATION

#### 17.4 Low-Power Modes

The timer and alarm can optionally continue to operate while in Sleep, Idle and even Deep Sleep mode. An alarm event can be used to wake-up the microcontroller from any of these Low-Power modes.

#### 17.5 Reset

#### 17.5.1 DEVICE RESET

When a device Reset occurs, the ALRMCFG and ALRMRPT registers are forced to a Reset state causing the alarm to be disabled (if enabled prior to the Reset). If the RTCC was enabled, it will continue to operate when a basic device Reset occurs.

#### 17.5.2 POWER-ON RESET (POR)

The RTCCFG and ALRMRPT registers are reset only on a POR. Once the device exits the POR state, the clock registers should be reloaded with the desired values.

The timer prescaler values can be reset only by writing to the SECONDS register. No device Reset can affect the prescalers.

### 18.0 ENHANCED CAPTURE/COMPARE/PWM (ECCP) MODULE

PIC18F46J11 family devices have two Enhanced Capture/Compare/PWM (ECCP) modules: ECCP1 and ECCP2. These modules contain a 16-bit register, which can operate as a 16-bit Capture register, a 16-bit Compare register or a PWM Master/Slave Duty Cycle register. These ECCP modules are upward compatible with CCP

Note: Register and bit names referencing one of the two ECCP modules substitute an 'x' for the module number. For example, registers CCP1CON and CCP2CON, which have the same definitions, are called CCPxCON. Figures and diagrams use ECCP1-based names, but those names also apply to ECCP2, with a "2" replacing the illustration name's "1". When writing firmware, the "x" in register and bit names must be replaced with the appropriate module number.

ECCP1 and ECCP2 are implemented as standard CCP modules with enhanced PWM capabilities. These include:

- Provision for two or four output channels

- Output Steering modes

- · Programmable polarity

- Programmable dead-band control

- · Automatic shutdown and restart

The enhanced features are discussed in detail in Section 18.5 "PWM (Enhanced Mode)".

Note: PxA, PxB, PxC and PxD are associated with the remappable pins (RPn).

#### 18.5.3 START-UP CONSIDERATIONS

When any PWM mode is used, the application hardware must use the proper external pull-up and/or pull-down resistors on the PWM output pins.

| Note: | When the microcontroller is released from |

|-------|-------------------------------------------|

|       | Reset, all of the I/O pins are in the     |

|       | high-impedance state. The external        |

|       | circuits must keep the power switch       |

|       | devices in the OFF state until the micro- |

|       | controller drives the I/O pins with the   |

|       | proper signal levels or activates the PWM |

|       | output(s).                                |

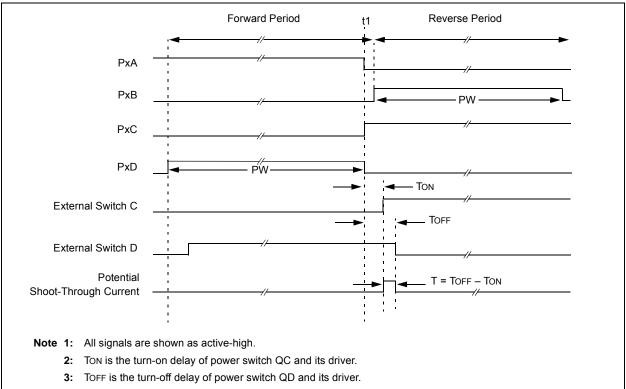

The CCPxM<1:0> bits of the CCPxCON register allow the user to choose whether the PWM output signals are active-high or active-low for each pair of PWM output pins (PxA/PxC and PxB/PxD). The PWM output polarities must be selected before the PWM pin output drivers are enabled. Changing the polarity configuration while the PWM pin output drivers are enabled is not recommended since it may result in damage to the application circuits.

The PxA, PxB, PxC and PxD output latches may not be in the proper states when the PWM module is initialized. Enabling the PWM pin output drivers at the same time as the Enhanced PWM modes may cause damage to the application circuit. The Enhanced PWM modes must be enabled in the proper Output mode and complete a full PWM cycle before enabling the PWM pin output drivers. The completion of a full PWM cycle is indicated by the TMR2IF or TMR4IF bit of the PIR1 or PIR3 register being set as the second PWM period begins.

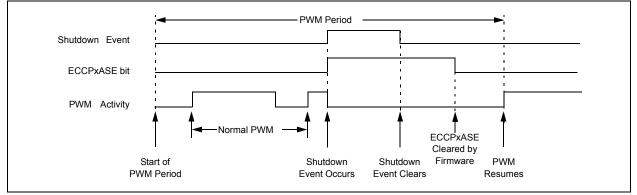

#### 18.5.5 AUTO-RESTART MODE

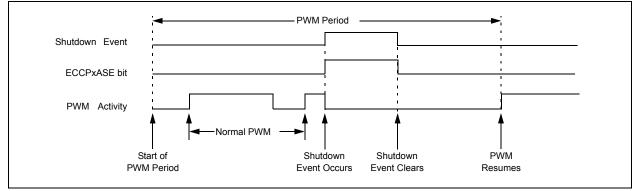

The Enhanced PWM can be configured to automatically restart the PWM signal once the auto-shutdown condition has been removed. Auto-restart is enabled by setting the PxRSEN bit in the ECCPxDEL register.

If auto-restart is enabled, the ECCPxASE bit will remain set as long as the auto-shutdown condition is active. When the auto-shutdown condition is removed, the ECCPxASE bit will be cleared via hardware and normal operation will resume. The module will wait until the next PWM period begins, however, before re-enabling the output pin. This behavior allows the auto-shutdown with auto-restart features to be used in applications based on current mode PWM control.

#### FIGURE 18-15: PWM AUTO-SHUTDOWN WITH AUTO-RESTART ENABLED (PxRSEN = 1)

### 19.3.4 ENABLING SPI I/O

To enable the serial port, MSSP Enable bit, SSPEN (SSPxCON1<5>), must be set. To reset or reconfigure SPI mode, clear the SSPEN bit, reinitialize the SSPxCON1 registers and then set the SSPEN bit. This configures the SDIx, SDOx, SCKx and SSx pins as serial port pins. For the pins to behave as the serial port function, the appropriate TRIS bits, ANCON/PCFG bits and Peripheral Pin Select registers (if using MSSP2) should be correctly initialized prior to setting the SSPEN bit.

A typical SPI serial port initialization process follows:

- Initialize ODCON3 register (optional open-drain output control)

- Initialize remappable pin functions (if using MSSP2, see Section 10.7 "Peripheral Pin Select (PPS)")

- Initialize SCKx LAT value to desired Idle SCK level (if master device)

- Initialize SCKx ANCON/PCFG bit (if Slave mode and multiplexed with ANx function)

- Initialize SCKx TRIS bit as output (Master mode) or input (Slave mode)

- Initialize SDIx ANCON/PCFG bit (if SDIx is multiplexed with ANx function)

- Initialize SDIx TRIS bit

- Initialize SSx ANCON/PCFG bit (if Slave mode and multiplexed with ANx function)

- Initialize SSx TRIS bit (Slave modes)

- Initialize SDOx TRIS bit

- Initialize SSPxSTAT register

- Initialize SSPxCON1 register

- Set SSPEN bit to enable the module

Any MSSP1 serial port function that is not desired may be overridden by programming the corresponding Data Direction (TRIS) register to the opposite value. If individual MSSP2 serial port functions will not be used, they may be left unmapped.

Note: When MSSP2 is used in SPI Master mode, the SCK2 function must be configured as both an output and input in the PPS module. SCK2 must be initialized as an output pin (by writing 0x0A to one of the RPORx registers). Additionally, SCK2IN must also be mapped to the same pin, by initializing the RPINR22 register. Failure to initialize SCK2/SCK2IN as both output and input will prevent the module from receiving data on the SDI2 pin, as the module uses the SCK2IN signal to latch the received data.

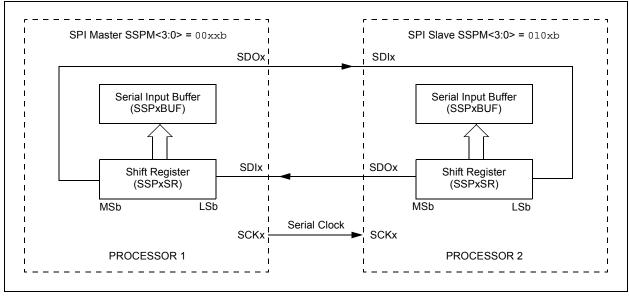

### 19.3.5 TYPICAL CONNECTION

Figure 19-2 illustrates a typical connection between two microcontrollers. The master controller (Processor 1) initiates the data transfer by sending the SCKx signal. Data is shifted out of both shift registers on their programmed clock edge and latched on the opposite edge of the clock. Both processors should be programmed to the same Clock Polarity (CKP), then both controllers would send and receive data at the same time. Whether the data is meaningful (or dummy data) depends on the application software. This leads to three scenarios for data transmission:

- Master sends valid data Slave sends dummy data

- Master sends valid data Slave sends valid data

- Master sends dummy data Slave sends valid data

#### FIGURE 19-2: SPI MASTER/SLAVE CONNECTION

#### REGISTER 22-2: CMSTAT: COMPARATOR STATUS REGISTER (ACCESS F70h)

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R-1   | R-1   |

|-------|-----|-----|-----|-----|-----|-------|-------|

| —     | —   | —   | —   | —   | —   | COUT2 | COUT1 |

| bit 7 |     |     |     |     |     |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7-2 Unimplemented: Read as '0' |

|------------------------------------|

|------------------------------------|

bit 1-0 COUT<2:1>: Comparator x Status bits

If CPOL = 0 (non-inverted polarity):

1 = Comparator VIN+ > VIN-

0 = Comparator VIN+ < VIN-

If CPOL = 1 (inverted polarity):

1 = Comparator VIN+ < VIN-

0 = Comparator VIN+ > VIN-

| TSTF                                                                            | sz                                               | Test f, Skip                                                                                                                            | Test f, Skip if 0                                                                                                                                                   |                 |  |  |  |  |  |

|---------------------------------------------------------------------------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|--|--|--|

| Synta                                                                           | ax:                                              | TSTFSZ f {                                                                                                                              | ,a}                                                                                                                                                                 |                 |  |  |  |  |  |

| Operands:                                                                       |                                                  | 0 ≤ f ≤ 255<br>a ∈ [0,1]                                                                                                                | $0 \le f \le 255$                                                                                                                                                   |                 |  |  |  |  |  |

| Oper                                                                            | ation:                                           | skip if f = 0                                                                                                                           |                                                                                                                                                                     |                 |  |  |  |  |  |

| Statu                                                                           | s Affected:                                      | None                                                                                                                                    |                                                                                                                                                                     |                 |  |  |  |  |  |

| Enco                                                                            | ding:                                            | 0110                                                                                                                                    | 011a fff                                                                                                                                                            | f ffff          |  |  |  |  |  |

| Desc                                                                            | ription:                                         | during the c<br>is discarded                                                                                                            | If 'f' = 0, the next instruction fetched<br>during the current instruction execution<br>is discarded and a NOP is executed,<br>making this a two-cycle instruction. |                 |  |  |  |  |  |

|                                                                                 |                                                  | lf 'a' is '1', tl                                                                                                                       | If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank (default).                                                  |                 |  |  |  |  |  |

|                                                                                 |                                                  | nd the extended<br>ed, this instruct<br>Literal Offset $A$<br>lever $f \le 95$ (51<br>.2.3 "Byte-Ori<br>ed Instruction<br>set Mode" for | ction operates<br>addressing<br>=h). See<br>iented and<br>s in Indexed                                                                                              |                 |  |  |  |  |  |

| Words: 1                                                                        |                                                  |                                                                                                                                         |                                                                                                                                                                     |                 |  |  |  |  |  |

| Cycles: 1(2)<br>Note: 3 cycles if skip and followed<br>by a 2-word instruction. |                                                  |                                                                                                                                         |                                                                                                                                                                     |                 |  |  |  |  |  |

| QC                                                                              | 04                                               |                                                                                                                                         |                                                                                                                                                                     |                 |  |  |  |  |  |

| 1                                                                               | Q1<br>Decode                                     | Q2<br>Read                                                                                                                              | Q3<br>Process                                                                                                                                                       | Q4<br>No        |  |  |  |  |  |

|                                                                                 | Debbue                                           | register 'f'                                                                                                                            | Data                                                                                                                                                                | operation       |  |  |  |  |  |

| lf sk                                                                           | ip:                                              | -                                                                                                                                       |                                                                                                                                                                     |                 |  |  |  |  |  |

|                                                                                 | Q1                                               | Q2                                                                                                                                      | Q3                                                                                                                                                                  | Q4              |  |  |  |  |  |

|                                                                                 | No                                               | No                                                                                                                                      | No                                                                                                                                                                  | No              |  |  |  |  |  |

| lf ek                                                                           | operation<br>ip and followed                     | operation                                                                                                                               | operation                                                                                                                                                           | operation       |  |  |  |  |  |

| 11 51                                                                           | Q1                                               | Q2                                                                                                                                      | Q3                                                                                                                                                                  | Q4              |  |  |  |  |  |

|                                                                                 | No                                               | No                                                                                                                                      | No                                                                                                                                                                  | No              |  |  |  |  |  |

|                                                                                 | operation                                        | operation                                                                                                                               | operation                                                                                                                                                           | operation       |  |  |  |  |  |

|                                                                                 | No<br>operation                                  | No<br>operation                                                                                                                         | No<br>operation                                                                                                                                                     | No<br>operation |  |  |  |  |  |

| Example: HERE TSTFSZ CNT, 1<br>NZERO :<br>ZERO :                                |                                                  |                                                                                                                                         |                                                                                                                                                                     |                 |  |  |  |  |  |

|                                                                                 | Before Instruc<br>PC                             | = Ad                                                                                                                                    | dress (here                                                                                                                                                         | )               |  |  |  |  |  |

|                                                                                 | After Instructic<br>If CNT<br>PC<br>If CNT<br>PC | = 00<br>= Ad<br>≠ 00                                                                                                                    | dress (ZERO                                                                                                                                                         |                 |  |  |  |  |  |

| XORLW                               |                                    | Exclusive           | e OR Lite     | ral w | ith V | v             |  |  |  |

|-------------------------------------|------------------------------------|---------------------|---------------|-------|-------|---------------|--|--|--|

| Syntax:                             | XORLW                              | k                   |               |       |       |               |  |  |  |

| Operands:                           | $0 \le k \le 25$                   | $0 \le k \le 255$   |               |       |       |               |  |  |  |

| Operation:                          | (W) .XOR                           | $k \to W$           |               |       |       |               |  |  |  |

| Status Affected                     | :                                  | N, Z                | N, Z          |       |       |               |  |  |  |

| Encoding:                           |                                    | 0000                | 1010          | kkł   | ck    | kkkk          |  |  |  |

| Description:                        | The conte<br>the 8-bit li<br>in W. |                     |               | ••••  |       |               |  |  |  |

| Words:                              |                                    | 1                   |               |       |       |               |  |  |  |

| Cycles:                             |                                    | 1                   |               |       |       |               |  |  |  |

| Q Cycle Activi                      | ty:                                |                     |               |       |       |               |  |  |  |

| Q1                                  |                                    | Q2                  | Q3            |       | Q4    |               |  |  |  |

| Decode                              | e                                  | Read<br>literal 'k' | Proce<br>Data |       | V     | /rite to<br>W |  |  |  |

| Example:                            |                                    | XORLW               | 0xAF          |       |       |               |  |  |  |

| Before Ins<br>W<br>After Instr<br>W | =                                  | B5h                 |               |       |       |               |  |  |  |

#### 28.2 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for all PIC MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

#### 28.3 MPLAB C18 and MPLAB C30 C Compilers

The MPLAB C18 and MPLAB C30 Code Development Systems are complete ANSI C compilers for Microchip's PIC18 and PIC24 families of microcontrollers and the dsPIC30 and dsPIC33 family of digital signal controllers. These compilers provide powerful integration capabilities, superior code optimization and ease of use not found with other compilers.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

#### 28.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler and the MPLAB C18 C Compiler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

## 28.5 MPLAB ASM30 Assembler, Linker and Librarian

MPLAB ASM30 Assembler produces relocatable machine code from symbolic assembly language for dsPIC30F devices. MPLAB C30 C Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- Support for the entire dsPIC30F instruction set

- · Support for fixed-point and floating-point data

- · Command line interface

- Rich directive set

- Flexible macro language

- · MPLAB IDE compatibility

#### 28.6 MPLAB SIM Software Simulator

The MPLAB SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC<sup>®</sup> DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB SIM Software Simulator fully supports symbolic debugging using the MPLAB C18 and MPLAB C30 C Compilers, and the MPASM and MPLAB ASM30 Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

#### 29.2 DC Characteristics: Power-Down and Supply Current PIC18F46J11 Family (Industrial) (Continued)

| PIC18LFXXJ11 Family |                                     |       |      | <b>rating C</b><br>perature |       | (unless otherwise s<br>$C \le TA \le +85^{\circ}C$ for inc | ,                            |  |  |

|---------------------|-------------------------------------|-------|------|-----------------------------|-------|------------------------------------------------------------|------------------------------|--|--|

| PIC18FXXJ11 Family  |                                     |       |      | <b>rating C</b><br>perature |       | (unless otherwise s<br>$C \le TA \le +85^{\circ}C$ for inc |                              |  |  |

| Param<br>No.        | Device                              | Тур   | Max  | Units                       |       | Conditions                                                 |                              |  |  |

|                     | Supply Current (IDD) <sup>(2)</sup> |       |      |                             |       |                                                            |                              |  |  |

|                     | PIC18LFXXJ11                        | 0.879 | 1.25 | mA                          | -40°C |                                                            |                              |  |  |

|                     |                                     | 0.881 | 1.25 | mA                          | +25°C | VDD = 2.0V,<br>VDDCORE = 2.0V                              |                              |  |  |

|                     |                                     | 0.891 | 1.36 | mA                          | +85°C |                                                            | Fosc = 4 MHz, <b>PRI_RUN</b> |  |  |

|                     | PIC18LFXXJ11                        | 1.35  | 1.70 | mA                          | -40°C | $\lambda (pp - 2, 0) $                                     |                              |  |  |

|                     |                                     | 1.30  | 1.70 | mA                          | +25°C | VDD = 2.0V,<br>VDDCORE = 2.0V                              |                              |  |  |

|                     |                                     | 1.27  | 1.82 | mA                          | +85°C | VBBOOKE 2.0V                                               |                              |  |  |

|                     | PIC18FXXJ11                         | 1.09  | 1.60 | mA                          | -40°C | VDD = 2.15V,                                               | mode, EC Oscillator          |  |  |

|                     |                                     | 1.09  | 1.60 | mA                          | +25°C | VDDCORE = $10 \mu F$                                       | -                            |  |  |

|                     |                                     | 1.11  | 1.70 | mA                          | +85°C | Capacitor                                                  |                              |  |  |

|                     | PIC18FXXJ11                         | 1.36  | 1.95 | mA                          | -40°C | VDD = 3.3V,                                                |                              |  |  |

|                     |                                     | 1.36  | 1.89 | mA                          | +25°C | VDDCORE = 10 µF                                            |                              |  |  |

|                     |                                     | 1.41  | 1.92 | mA                          | +85°C | Capacitor                                                  |                              |  |  |

|                     | PIC18LFXXJ11                        | 10.9  | 14.8 | mA                          | -40°C | VDD = 2.5V,                                                |                              |  |  |

|                     |                                     | 10.6  | 14.8 | mA                          | +25°C | VDD = 2.5V,<br>VDDCORE = 2.5V                              |                              |  |  |

|                     |                                     | 10.6  | 15.2 | mA                          | +85°C |                                                            | Fosc = 48 MHz, PRI_RUN       |  |  |

|                     | PIC18FXXJ11                         |       | 23.2 | mA                          | -40°C | VDD = 3.3V,                                                | mode, EC Oscillator          |  |  |

|                     |                                     | 12.8  | 22.7 | mA                          | +25°C | VDDCORE = $10  \mu F$                                      |                              |  |  |

|                     |                                     | 12.7  | 22.7 | mA                          | +85°C | Capacitor                                                  |                              |  |  |

**Note 1:** The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or VSs and all features that add delta current disabled (such as WDT, Timer1 oscillator, BOR, etc.).

- 2: The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption. All features that add delta current are disabled (WDT, etc.). The test conditions for all IDD measurements in active operation mode are:

- OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD/VSS;

- MCLR = VDD; WDT disabled unless otherwise specified.

- **3:** Low-Power Timer1 with standard, low-cost 32 kHz crystals have an operating temperature range of -10°C to +70°C. Extended temperature crystals are available at a much higher cost.

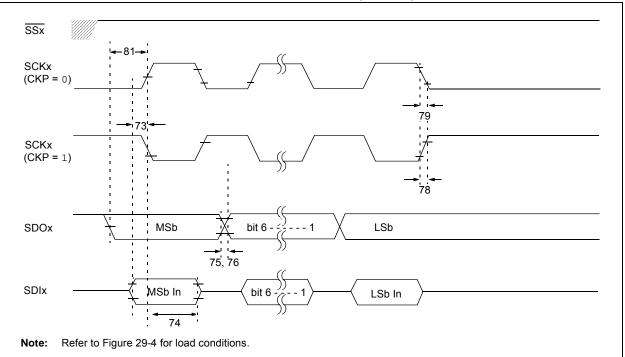

#### TABLE 29-21: EXAMPLE SPI MODE REQUIREMENTS (MASTER MODE, CKE = 1)

| Param.<br>No. | Symbol                | Characteristic                             | Min | Max | Units | Conditions                      |

|---------------|-----------------------|--------------------------------------------|-----|-----|-------|---------------------------------|

| 73            | TDIV2SCH,<br>TDIV2SCL | Setup Time of SDIx Data Input to SCKx Edge | 35  |     | ns    | VDD = 3.3V,<br>VDDCORE = 2.5V   |

|               |                       |                                            | 100 | —   | ns    | VDD = 2.15V,<br>VDDCORE = 2.15V |

| 74            | TscH2DIL,<br>TscL2DIL | Hold Time of SDIx Data Input to SCKx Edge  | 30  | —   | ns    | VDD = 3.3V,<br>VDDCORE = 2.5V   |

|               | IGOLLDIE              |                                            | 83  | _   | ns    | VDD = 2.15V                     |

| 75            | TDOR                  | SDOx Data Output Rise Time                 | _   | 25  | ns    | PORTB or PORTC                  |

| 76            | TdoF                  | SDOx Data Output Fall Time                 | _   | 25  | ns    | PORTB or PORTC                  |

| 78            | TscR                  | SCKx Output Rise Time (Master mode)        | _   | 25  | ns    | PORTB or PORTC                  |

| 79            | TscF                  | SCKx Output Fall Time (Master mode)        | _   | 25  | ns    | PORTB or PORTC                  |

| 81            | TDOV2scH,<br>TDOV2scL | SDOx Data Output Setup to SCKx Edge        | Тсү | -   | ns    |                                 |