Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 16                                                                         |

| Program Memory Size        | 16KB (8K x 16)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 3.8K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.15V ~ 3.6V                                                               |

| Data Converters            | A/D 10x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f24j11-i-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 4.6.7 TYPICAL DEEP SLEEP SEQUENCE

This section gives the typical sequence for using the Deep Sleep mode. Optional steps are indicated, and additional information is given in notes at the end of the procedure.

- 1. Enable DSWDT (optional). (1)

- 2. Configure DSWDT clock source (optional). (2)

- 3. Enable DSBOR (optional).(1)

- 4. Enable RTCC (optional). (3)

- 5. Configure the RTCC peripheral (optional). (3)

- 6. Configure the ULPWU peripheral (optional). (4)

- 7. Enable the INTO Interrupt (optional). (4)

- Context save SRAM data by writing to the DSGPR0 and DSGPR1 registers (optional).

- Set the REGSLP bit (WDTCON<7>) and clear the IDLEN bit (OSCCON<7>).

- 10. If using an RTCC alarm for wake-up, wait until the RTCSYNC (RTCCFG<4>) bit is clear.

- Enter Deep Sleep mode by setting the DSEN bit (DSCONH<7>) and issuing a SLEEP instruction.

These two instructions must be executed back to back.

- Once a wake-up event occurs, the device will perform a POR reset sequence. Code execution resumes at the device's Reset vector.

- Determine if the device exited Deep Sleep by reading the Deep Sleep bit, DS (WDTCON<3>).

This bit will be set if there was an exit from Deep Sleep mode.

- 14. Clear the Deep Sleep bit, DS (WDTCON<3>).

- 15. Determine the wake-up source by reading the DSWAKEH and DSWAKEL registers.

- Determine if a DSBOR event occurred during Deep Sleep mode by reading the DSBOR bit (DSCONL<1>).

- 17. Read the DSGPR0 and DSGPR1 context save registers (optional).

- 18. Clear the RELEASE bit (DSCONL<0>).

- Note 1: DSWDT and DSBOR are enabled through the devices' Configuration bits. For more information, see Section 26.1 "Configuration Bits".

- 2: The DSWDT and RTCC clock sources are selected through the devices' Configuration bits. For more information, see Section 26.1 "Configuration Bits".

- 3: For more information, see Section 17.0 "Real-Time Clock and Calendar (RTCC)".

- 4: For more information on configuring this peripheral, see Section 4.7 "Ultra Low-Power Wake-up".

#### 4.6.8 DEEP SLEEP FAULT DETECTION

If during Deep Sleep the device is subjected to unusual operating conditions, such as an Electrostatic Discharge (ESD) event, it is possible that the internal circuit states used by the Deep Sleep module could become corrupted. If this were to happen, the device may exhibit unexpected behavior, such as a failure to wake back up.

In order to prevent this type of scenario from occurring, the Deep Sleep module includes automatic self-monitoring capability. During Deep Sleep, critical internal nodes are continuously monitored in order to detect possible Fault conditions (which would not ordinarily occur). If a Fault condition is detected, the circuitry will set the DSFLT status bit (DSWAKEL<7>) and automatically wake the microcontroller from Deep Sleep, causing a POR Reset.

During Deep Sleep, the Fault detection circuitry is always enabled and does not require any specific configuration prior to entering Deep Sleep.

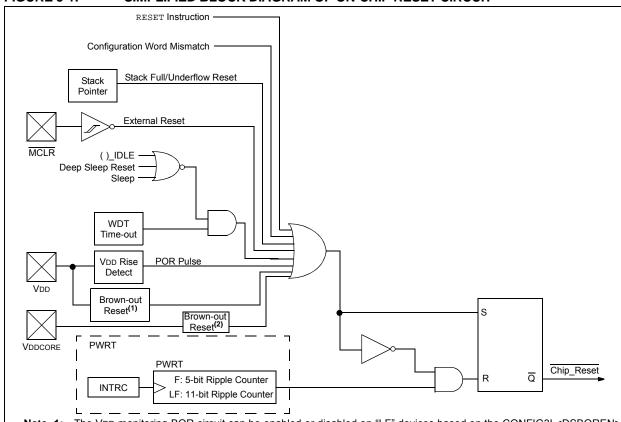

### 5.0 RESET

The PIC18F46J11 family of devices differentiates among various kinds of Reset:

- a) Power-on Reset (POR)

- b) MCLR Reset during normal operation

- c) MCLR Reset during power-managed modes

- d) Watchdog Timer (WDT) Reset (during execution)

- e) Configuration Mismatch (CM)

- f) Brown-out Reset (BOR)

- g) RESET Instruction

- h) Stack Full Reset

- i) Stack Underflow Reset

- j) Deep Sleep Reset

This section discusses Resets generated by  $\overline{\text{MCLR}}$ , POR and BOR, and covers the operation of the various start-up timers.

For information on WDT Resets, see Section 26.2 "Watchdog Timer (WDT)". For Stack Reset events, see Section 6.1.4.4 "Stack Full and Underflow Resets" and for Deep Sleep mode, see Section 4.6 "Deep Sleep Mode".

Figure 5-1 provides a simplified block diagram of the on-chip Reset circuit.

### 5.1 RCON Register

Device Reset events are tracked through the RCON register (Register 5-1). The lower five bits of the register indicate that a specific Reset event has occurred. In most cases, these bits can only be set by the event and must be cleared by the application after the event. The state of these flag bits, taken together, can be read to indicate the type of Reset that just occurred. This is described in more detail in **Section 5.7** "**Reset State of Registers**".

The ECON register also has a control bit for setting interrupt priority (IPEN). Interrupt priority is discussed in **Section 9.0 "Interrupts"**.

FIGURE 5-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

- Note 1: The VDD monitoring BOR circuit can be enabled or disabled on "LF" devices based on the CONFIG3L<DSBOREN> Configuration bit. On "F" devices, the VDD monitoring BOR circuit is only enabled during Deep Sleep mode by CONFIG3L<DSBOREN>.

- 2: The VDDCORE monitoring BOR circuit is only implemented on "F" devices. It is always used, except while in Deep Sleep mode. The VDDCORE monitoring BOR circuit has a trip point threshold of VBOR (parameter D005).

### 6.4 Data Addressing Modes

Note:

The execution of some instructions in the core PIC18 instruction set is changed when the PIC18 extended instruction set is enabled. See Section 6.6 "Data Memory and the Extended Instruction Set" for more information.

While the program memory can be addressed in only one way, through the PC, information in the data memory space can be addressed in several ways. For most instructions, the addressing mode is fixed. Other instructions may use up to three modes, depending on which operands are used and whether or not the extended instruction set is enabled.

The addressing modes are:

- Inherent

- Literal

- · Direct

- Indirect

An additional addressing mode, Indexed Literal Offset, is available when the extended instruction set is enabled (XINST Configuration bit = 1). Its operation is discussed in more detail in **Section 6.6.1 "Indexed Addressing with Literal Offset"**.

## 6.4.1 INHERENT AND LITERAL ADDRESSING

Many PIC18 control instructions do not need any argument at all; they either perform an operation that globally affects the device, or they operate implicitly on one register. This addressing mode is known as Inherent Addressing. Examples include SLEEP, RESET and DAW.

Other instructions work in a similar way, but require an additional explicit argument in the opcode. This is known as Literal Addressing mode, because they require some literal value as an argument. Examples include ADDLW and MOVLW, which respectively, add or move a literal value to the W register. Other examples include CALL and GOTO, which include a 20-bit program memory address.

#### 6.4.2 DIRECT ADDRESSING

Direct Addressing specifies all or part of the source and/or destination address of the operation within the opcode itself. The options are specified by the arguments accompanying the instruction.

In the core PIC18 instruction set, bit-oriented and byte-oriented instructions use some version of Direct Addressing by default. All of these instructions include some 8-bit Literal Address as their LSB. This address specifies either a register address in one of the banks of data RAM (Section 6.3.3 "General Purpose

**Register File"**), or a location in the Access Bank (**Section 6.3.2 "Access Bank"**) as the data source for the instruction.

The Access RAM bit, 'a', determines how the address is interpreted. When 'a' is '1', the contents of the BSR (Section 6.3.1 "Bank Select Register") are used with the address to determine the complete 12-bit address of the register. When 'a' is '0', the address is interpreted as being a register in the Access Bank. Addressing that uses the Access RAM is sometimes also known as Direct Forced Addressing mode.

A few instructions, such as MOVFF, include the entire 12-bit address (either source or destination) in their opcodes. In these cases, the BSR is ignored entirely.

The destination of the operation's results is determined by the destination bit, 'd'. When 'd' is '1', the results are stored back in the source register, overwriting its original contents. When 'd' is '0', the results are stored in the W register. Instructions without the 'd' argument have a destination that is implicit in the instruction; their destination is either the target register being operated on or the W register.

#### 6.4.3 INDIRECT ADDRESSING

Indirect Addressing allows the user to access a location in data memory without giving a fixed address in the instruction. This is done by using File Select Registers (FSRs) as pointers to the locations to be read or written to. Since the FSRs are themselves located in RAM as SFRs, they can also be directly manipulated under program control. This makes FSRs very useful in implementing data structures such as tables and arrays in data memory.

The registers for Indirect Addressing are also implemented with Indirect File Operands (INDFs) that permit automatic manipulation of the pointer value with auto-incrementing, auto-decrementing or offsetting with another value. This allows for efficient code using loops, such as the example of clearing an entire RAM bank in Example 6-5. It also enables users to perform Indexed Addressing and other Stack Pointer operations for program memory in data memory.

EXAMPLE 6-5: HOW TO CLEAR RAM

(BANK 1) USING INDIRECT

ADDRESSING

| LFSR  | FSR0, 0x100          | ;                                     |                                                 |

|-------|----------------------|---------------------------------------|-------------------------------------------------|

| CLRF  | POSTINC0             | ;                                     | Clear INDF                                      |

|       |                      | ;                                     | register then                                   |

|       |                      | ;                                     | inc pointer                                     |

| BTFSS | FSROH, 1             | ;                                     | All done with                                   |

|       |                      | ;                                     | Bank1?                                          |

| BRA   | NEXT                 | ;                                     | NO, clear next                                  |

| Ε     |                      | ;                                     | YES, continue                                   |

|       | CLRF<br>BTFSS<br>BRA | CLRF POSTINCO BTFSS FSR0H, 1 BRA NEXT | CLRF POSTINCO ; ; BTFSS FSROH, 1 ; ; BRA NEXT ; |

## 6.6.1 INDEXED ADDRESSING WITH LITERAL OFFSET

Enabling the PIC18 extended instruction set changes the behavior of Indirect Addressing using the FSR2 register pair and its associated file operands. Under proper conditions, instructions that use the Access Bank, that is, most bit and byte-oriented instructions, can invoke a form of Indexed Addressing using an offset specified in the instruction. This special addressing mode is known as Indexed Addressing with Literal Offset, or Indexed Literal Offset mode.

When using the extended instruction set, this addressing mode requires the following:

- The use of the Access Bank is forced ('a' = 0); and

- The file address argument is less than or equal to 5Fh

Under these conditions, the file address of the instruction is not interpreted as the lower byte of an address (used with the BSR in Direct Addressing) or as an 8-bit address in the Access Bank. Instead, the value is interpreted as an offset value to an Address Pointer specified by FSR2. The offset and the contents of FSR2 are added to obtain the target address of the operation.

## 6.6.2 INSTRUCTIONS AFFECTED BY INDEXED LITERAL OFFSET MODE

Any of the core PIC18 instructions that can use Direct Addressing are potentially affected by the Indexed Literal Offset Addressing mode. This includes all byte and bit-oriented instructions, or almost one-half of the standard PIC18 instruction set. Instructions that only use Inherent or Literal Addressing modes are unaffected.

Additionally, byte and bit-oriented instructions are not affected if they do not use the Access Bank (Access RAM bit is '1') or include a file address of 60h or above. Instructions meeting these criteria will continue to execute as before. A comparison of the different possible addressing modes when the extended instruction set is enabled is provided in Figure 6-9.

Those who desire to use byte or bit-oriented instructions in the Indexed Literal Offset mode should note the changes to assembler syntax for this mode. This is described in more detail in **Section 27.2.1 "Extended Instruction Syntax"**.

NOTES:

NOTES:

### 13.7 Resetting Timer1 Using the ECCP Special Event Trigger

If ECCP1 or ECCP2 is configured to use Timer1 and to generate a Special Event Trigger in Compare mode (CCPxM<3:0> = 1011), this signal will reset Timer3. The trigger from ECCP2 will also start an A/D conversion if the A/D module is enabled (see **Section 18.3.4** "**Special Event Trigger**" for more information).

The module must be configured as either a timer or a synchronous counter to take advantage of this feature. When used this way, the CCPRxH:CCPRxL register pair effectively becomes a Period register for Timer1.

If Timer1 is running in Asynchronous Counter mode, this Reset operation may not work.

In the event that a write to Timer1 coincides with a Special Event Trigger, the write operation will take precedence.

**Note:** The Special Event Trigger from the ECCPx module will not set the TMR1IF interrupt flag bit (PIR1<0>).

#### 13.8 Timer1 Gate

Timer1 can be configured to count freely or the count can be enabled and disabled using the Timer1 gate circuitry. This is also referred to as Timer1 gate count enable.

The Timer1 gate can also be driven by multiple selectable sources.

#### 13.8.1 TIMER1 GATE COUNT ENABLE

The Timer1 Gate Enable mode is enabled by setting the TMR1GE bit of the T1GCON register. The polarity of the Timer1 Gate Enable mode is configured using the T1GPOL bit of the T1GCON register.

When Timer1 Gate Enable mode is enabled, Timer1 will increment on the rising edge of the Timer1 clock source. When Timer1 Gate Enable mode is disabled, no incrementing will occur and Timer1 will hold the current count. See Figure 13-4 for timing details.

TABLE 13-3: TIMER1 GATE ENABLE SELECTIONS

| T1CLK    | T1GPOL | T1G | Timer1 Operation |

|----------|--------|-----|------------------|

| <b>↑</b> | 0      | 0   | Counts           |

| <b>↑</b> | 0      | 1   | Holds Count      |

| <b>↑</b> | 1      | 0   | Holds Count      |

| <b>↑</b> | 1      | 1   | Counts           |

### 15.1 Timer3 Gate Control Register

The Timer3 Gate Control register (T3GCON), provided in Register 14-2, is used to control the Timer3 gate.

### REGISTER 15-2: T3GCON: TIMER3 GATE CONTROL REGISTER (ACCESS F97h)(1)

| R/W-0  | R/W-0  | R/W-0 | R/W-0  | R/W-0        | R-x    | R/W-0  | R/W-0  |

|--------|--------|-------|--------|--------------|--------|--------|--------|

| TMR3GE | T3GPOL | T3GTM | T3GSPM | T3GGO/T3DONE | T3GVAL | T3GSS1 | T3GSS0 |

| bit 7  |        |       |        |              |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 TMR3GE: Timer3 Gate Enable bit

If TMR3ON = 0: This bit is ignored. If TMR3ON = 1:

1 = Timer3 counting is controlled by the Timer3 gate function

0 = Timer3 counts regardless of Timer3 gate function

bit 6 T3GPOL: Timer3 Gate Polarity bit

1 = Timer3 gate is active-high (Timer3 counts when gate is high)

0 = Timer3 gate is active-low (Timer3 counts when gate is low)

bit 5 T3GTM: Timer3 Gate Toggle Mode bit

1 = Timer3 Gate Toggle mode is enabled

0 = Timer3 Gate Toggle mode is disabled and toggle flip-flop is cleared

Timer3 gate flip-flop toggles on every rising edge.

bit 4 T3GSPM: Timer3 Gate Single Pulse Mode bit

1 = Timer3 Gate Single Pulse mode is enabled and is controlling Timer3 gate

0 = Timer3 Gate Single Pulse mode is disabled

bit 3 T3GGO/T3DONE: Timer3 Gate Single Pulse Acquisition Status bit

1 = Timer3 gate single pulse acquisition is ready, waiting for an edge

0 = Timer3 gate single pulse acquisition has completed or has not been started

This bit is automatically cleared when T3GSPM is cleared.

bit 2 T3GVAL: Timer3 Gate Current State bit

Indicates the current state of the Timer3 gate that could be provided to TMR3H:TMR3L. Unaffected by

Timer3 Gate Enable bit (TMR3GE).

bit 1-0 T3GSS<1:0>: Timer3 Gate Source Select bits

10 = TMR2 to match PR2 output

01 = Timer0 overflow output

00 = Timer3 gate pin (T3G)

Note 1: Programming the T3GCON prior to T3CON is recommended.

### 15.3 Timer3 16-Bit Read/Write Mode

Timer3 can be configured for 16-bit reads and writes (see Section 15.3 "Timer3 16-Bit Read/Write Mode"). When the RD16 control bit (T3CON<1>) is set, the address for TMR3H is mapped to a buffer register for the high byte of Timer3. A read from TMR3L will load the contents of the high byte of Timer3 into the Timer3 High Byte Buffer register. This provides the user with the ability to accurately read all 16 bits of Timer3 without having to determine whether a read of the high byte, followed by a read of the low byte, has become invalid due to a rollover between reads.

A write to the high byte of Timer3 must also take place through the TMR3H Buffer register. The Timer3 high byte is updated with the contents of TMR3H when a write occurs to TMR3L. This allows a user to write all 16 bits to both the high and low bytes of Timer3 at once.

The high byte of Timer3 is not directly readable or writable in this mode. All reads and writes must take place through the Timer3 High Byte Buffer register.

Writes to TMR3H do not clear the Timer3 prescaler. The prescaler is only cleared on writes to TMR3L.

## 15.4 Using the Timer1 Oscillator as the Timer3 Clock Source

The Timer1 internal oscillator may be used as the clock source for Timer3. The Timer1 oscillator is enabled by setting the T1OSCEN (T1CON<3>) bit. To use it as the Timer3 clock source, the TMR3CS bit must also be set. As previously noted, this also configures Timer3 to increment on every rising edge of the oscillator source.

The Timer1 oscillator is described in **Section 13.0** "Timer1 Module".

### 15.5 Timer3 Gate

Timer3 can be configured to count freely, or the count can be enabled and disabled using Timer3 gate circuitry. This is also referred to as Timer3 gate count enable.

Timer3 gate can also be driven by multiple selectable sources.

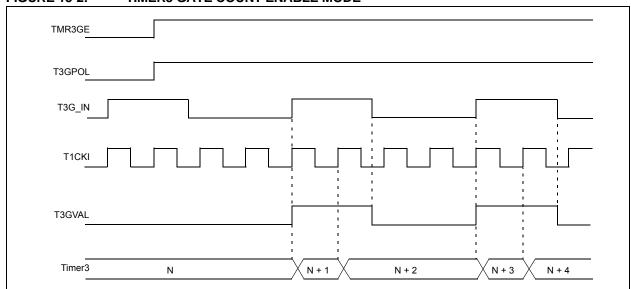

### 15.5.1 TIMER3 GATE COUNT ENABLE

The Timer3 Gate Enable mode is enabled by setting the TMR3GE bit of the T3GCON register. The polarity of the Timer3 Gate Enable mode is configured using the T3GPOL bit of the T3GCON register.

When Timer3 Gate Enable mode is enabled, Timer3 will increment on the rising edge of the Timer3 clock source. When Timer3 Gate Enable mode is disabled, no incrementing will occur and Timer3 will hold the current count. See Figure 15-2 for timing details.

TABLE 15-1: TIMER3 GATE ENABLE SELECTIONS

| T3CLK    | T3GPOL | T3G | Timer3 Operation |

|----------|--------|-----|------------------|

| <b>↑</b> | 0      | 0   | Counts           |

| <b>↑</b> | 0      | 1   | Holds Count      |

| <b>↑</b> | 1      | 0   | Holds Count      |

| <b>↑</b> | 1      | 1   | Counts           |

### REGISTER 17-16: ALRMWD: ALARM WEEKDAY VALUE REGISTER (ACCESS F8Fh, PTR 01b)<sup>(1)</sup>

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-x | R/W-x | R/W-x |

|-------|-----|-----|-----|-----|-------|-------|-------|

| _     | _   | _   | _   | _   | WDAY2 | WDAY1 | WDAY0 |

| bit 7 |     |     |     |     |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-3 **Unimplemented:** Read as '0'

bit 2-0 WDAY<2:0>: Binary Coded Decimal Value of Weekday Digit bits

Contains a value from 0 to 6.

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

### REGISTER 17-17: ALRMHR: ALARM HOURS VALUE REGISTER (ACCESS F8Eh, PTR 01b)(1)

| U-0   | U-0 | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| _     | _   | HRTEN1 | HRTEN0 | HRONE3 | HRONE2 | HRONE1 | HRONE0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-6 **Unimplemented:** Read as '0'

bit 5-4 HRTEN<1:0>: Binary Coded Decimal Value of Hour's Tens Digit bits

Contains a value from 0 to 2.

bit 3-0 **HRONE3:HRONE0:** Binary Coded Decimal Value of Hour's Ones Digit bits

Contains a value from 0 to 9.

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

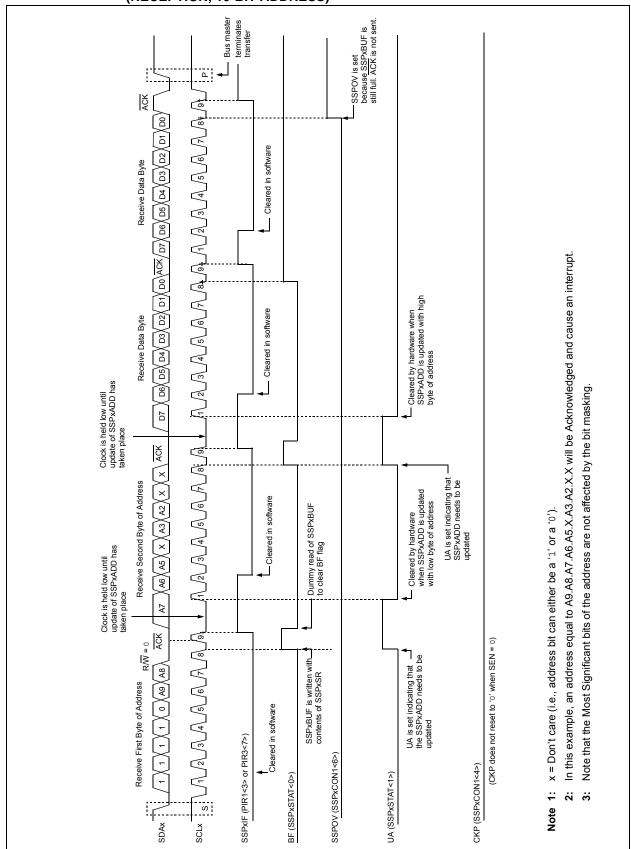

FIGURE 19-11:  $I^2C^{TM}$  SLAVE MODE TIMING WITH SEN = 0 AND ADMSK<5:1> = 01001 (RECEPTION, 10-BIT ADDRESS)

### 21.7 A/D Converter Calibration

The A/D Converter in the PIC18F46J11 family of devices includes a self-calibration feature, which compensates for any offset generated within the module. The calibration process is automated and is initiated by setting the ADCAL bit (ADCON1<6>). The next time the GO/DONE bit is set, the module will perform a "dummy" conversion (that is, with reading none of the input channels) and store the resulting value internally to compensate for the offset. Thus, subsequent offsets will be compensated.

Example 21-1 provides an example of a calibration routine.

The calibration process assumes that the device is in a relatively steady-state operating condition. If A/D calibration is used, it should be performed after each device Reset or if there are other major changes in operating conditions.

## 21.8 Operation in Power-Managed Modes

The selection of the automatic acquisition time and A/D conversion clock is determined in part by the clock source and frequency while in a power-managed mode.

If the A/D is expected to operate while the device is in a power-managed mode, the ACQT<2:0> and ADCS<2:0> bits in ADCON1 should be updated in accordance with the power-managed mode clock that will be used. After the power-managed mode is entered (either of the power-managed Run modes), an A/D acquisition or conversion may be started. Once an acquisition or conversion is started, the device should continue to be clocked by the same power-managed mode clock source until the conversion has been completed. If desired, the device may be placed into the corresponding power-managed Idle mode during the conversion.

If the power-managed mode clock frequency is less than 1 MHz, the A/D RC clock source should be selected

Operation in the Sleep mode requires the A/D RC clock to be selected. If bits, ACQT<2:0>, are set to '000' and a conversion is started, the conversion will be delayed one instruction cycle to allow execution of the SLEEP instruction and entry to Sleep mode. The IDLEN and SCS bits in the OSCCON register must have already been cleared prior to starting the conversion.

#### **EXAMPLE 21-1:** SAMPLE A/D CALIBRATION ROUTINE

```

ANCONO PCFGO

; Make Channel 0 analog

BCF

BSF

ADCON0, ADON

;Enable A/D module

BSF

ADCON1, ADCAL

; Enable Calibration

;Start a dummy A/D conversion

BSF

ADCON0,GO

CALIBRATION

BTFSC

ADCON0,GO

; Wait for the dummy conversion to finish

CALIBRATION

BRA

ADCON1, ADCAL

;Calibration done, turn off calibration enable

BCF

;Proceed with the actual A/D conversion

```

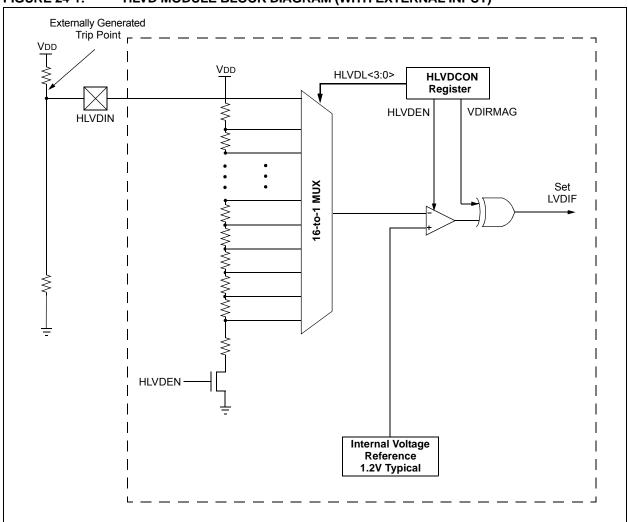

# 24.0 HIGH/LOW VOLTAGE DETECT (HLVD)

PIC18F46J11 family devices (including PIC18LF46J11 family devices) have a High/Low Voltage Detect (HLVD) module for monitoring the absolute voltage on VDD or the HLVDIN pin. This is a programmable circuit that allows the user to specify both a device voltage trip point and the direction of change from that point.

If the module detects an excursion past the trip point in that direction, an interrupt flag is set. If the interrupt is enabled, the program execution will branch to the interrupt vector address and the software can then respond to the interrupt.

W = Writable bit

Legend:

R = Readable bit

The High/Low-Voltage Detect Control register (Register 24-1) completely controls the operation of the HLVD module. This allows the circuitry to be "turned off" by the user under software control, which minimizes the current consumption for the device.

Figure 24-1 provides a block diagram for the HLVD module.

### REGISTER 24-1: HLVDCON: HIGH/LOW-VOLTAGE DETECT CONTROL REGISTER (ACCESS F85h)

| R/W-0   | R-0   | R-0   | R/W-0  | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|---------|-------|-------|--------|-----------------------|-----------------------|-----------------------|-----------------------|

| VDIRMAG | BGVST | IRVST | HLVDEN | HLVDL3 <sup>(1)</sup> | HLVDL2 <sup>(1)</sup> | HLVDL1 <sup>(1)</sup> | HLVDL0 <sup>(1)</sup> |

| bit 7   |       |       |        |                       |                       |                       | bit 0                 |

U = Unimplemented bit, read as '0'

| -n = Value a | at POR                                    | '1' = Bit is set                                                                                                           | '0' = Bit is cleared                                                                          | x = Bit is unknown                                                       |

|--------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| bit 7        | 1 = Ever                                  | •                                                                                                                          | als or exceeds trip point (HLVD                                                               | •                                                                        |

| bit 6        | BGVST:<br>1 = Indic                       | nt occurs when voltage equal<br>Band Gap Reference Volta<br>cates internal band gap volta<br>cates internal band gap volta | age references is stable                                                                      | /DL<3:0>)                                                                |

| bit 5        | <b>IRVST:</b> I<br>1 = Indic<br>0 = Indic | nternal Reference Voltage Scates that the voltage detect                                                                   | Stable Flag bit<br>t logic will generate the interrupt<br>ct logic will not generate the into | flag at the specified voltage range errupt flag at the specified voltage |

| bit 4        | 1 = HLV                                   | <b>I:</b> High/Low-Voltage Detect<br>'D enabled<br>'D disabled                                                             | Power Enable bit                                                                              |                                                                          |

| bit 3-0      | 1111 = I<br>1110 = I<br>•                 | Maximum setting                                                                                                            | nit bits <sup>(1)</sup><br>d (input comes from the HLVDI                                      | N pin)                                                                   |

|              |                                           | Minimum setting<br>Reserved                                                                                                |                                                                                               |                                                                          |

Note 1: See Table 29-8 in Section 29.0 "Electrical Characteristics" for specifications.

The module is enabled by setting the HLVDEN bit. Each time the module is enabled, the circuitry requires some time to stabilize. The IRVST bit is a read-only bit that indicates when the circuit is stable. The module can generate an interrupt only after the circuit is stable and IRVST is set.

The VDIRMAG bit determines the overall operation of the module. When VDIRMAG is cleared, the module monitors for drops in VDD below a predetermined set point. When the bit is set, the module monitors for rises in VDD above the set point.

### 24.1 Operation

When the HLVD module is enabled, a comparator uses an internally generated reference voltage as the set point. The set point is compared with the trip point, where each node in the resistor divider represents a trip point voltage. The "trip point" voltage is the voltage level at which the device detects a high or low-voltage event, depending on the configuration of the module.

When the supply voltage is equal to the trip point, the voltage tapped off of the resistor array is equal to the internal reference voltage generated by the voltage reference module. The comparator then generates an interrupt signal by setting the LVDIF bit.

The trip point voltage is software programmable to any one of 8 values. The trip point is selected by programming the HLVDL<3:0> bits (HLVDCON<3:0>).

Additionally, the HLVD module allows the user to supply the trip voltage to the module from an external source. This mode is enabled when bits, HLVDL<3:0>, are set to '1111'. In this state, the comparator input is multiplexed from the external input pin, HLVDIN. This gives users flexibility because it allows them to configure the HLVD interrupt to occur at any voltage in the valid operating range.

FIGURE 24-1: HLVD MODULE BLOCK DIAGRAM (WITH EXTERNAL INPUT)

CALLW Subroutine Call using WREG

Syntax: CALLW Operands: None

Operation:  $\begin{aligned} (\text{PC} + 2) &\rightarrow \text{TOS}, \\ (\text{W}) &\rightarrow \text{PCL}, \\ (\text{PCLATH}) &\rightarrow \text{PCH}, \\ (\text{PCLATU}) &\rightarrow \text{PCU} \end{aligned}$

Status Affected: None

Encoding: 0000 0000 0001 0100

Description

First, the return address (PC + 2) is pushed onto the return stack. Next, the contents of W are written to PCL; the existing value is discarded. Then, the contents of PCLATH and PCLATU are latched into PCH and PCU, respectively. The second cycle is executed as

a NOP instruction while the new next instruction is fetched.

Unlike CALL, there is no option to update W, STATUS or BSR.

Words: 1 Cycles: 2

Q Cycle Activity:

| Q1        | Q2        | Q3         | Q4        |

|-----------|-----------|------------|-----------|

| Decode    | Read      | Push PC to | No        |

|           | WREG      | stack      | operation |

| No        | No        | No         | No        |

| operation | operation | operation  | operation |

Example: HERE CALLW

Before Instruction

PC = address (HERE)

PCLATH = 10h PCLATU = 00h W = 06h

After Instruction

PC = 001006h

TOS = address (HERE + 2)

PCLATH = 10h

PCLATU = 00h

W = 06h

MOVSF Move Indexed to f

Syntax: MOVSF  $[z_s]$ ,  $f_d$ Operands:  $0 \le z_s \le 127$

$0 \le f_d \le 4095$

Operation:  $((FSR2) + z_s) \rightarrow f_d$

Status Affected: None

Encoding: 1st word (source) 2nd word (destin.)

Description:

1110 1011 0zzz zzzz<sub>s</sub> 1111 ffff ffff ffff<sub>d</sub>

The contents of the source register are moved to destination register 'f<sub>d</sub>'. The actual address of the source register is determined by adding the 7-bit literal offset 'z<sub>s</sub>', in the first word, to the value of FSR2. The address of the destination register is specified by the 12-bit literal 'f<sub>d</sub>' in the second word. Both addresses can be anywhere in the

4096-byte data space (000h to FFFh). The MOVSF instruction cannot use the PCL, TOSU, TOSH or TOSL as the

destination register.

If the resultant source address points to an Indirect Addressing register, the

value returned will be 00h.

Words: 2 Cycles: 2

Q Cycle Activity:

| Q1     | Q2                                  | Q3                    | Q4                              |

|--------|-------------------------------------|-----------------------|---------------------------------|

| Decode | Determine source addr               | Determine source addr | Read source reg                 |

| Decode | No<br>operation<br>No dummy<br>read | No<br>operation       | Write<br>register 'f'<br>(dest) |

Example: MOVSF [0x05], REG2

Before Instruction

FSR2 = 80h Contents of 85h = 33h REG2 = 11h

After Instruction

FSR2 = 80h Contents of 85h = 33h REG2 = 33h

SSx SCKx (CKP = 0)SCKx (CKP = 1)79 SDOx <del>→</del> <del>←</del> 75, 76 SDIx

FIGURE 29-13: **EXAMPLE SPI MASTER MODE TIMING (CKE = 0)**

TABLE 29-20: EXAMPLE SPI MODE REQUIREMENTS (MASTER MODE, CKE = 0)

|              |                       | `                                          |     |     |       | <u> </u>                      |

|--------------|-----------------------|--------------------------------------------|-----|-----|-------|-------------------------------|

| Param<br>No. | Symbol                | Characteristic                             | Min | Max | Units | Conditions                    |

| 73           | TDIV2SCH,<br>TDIV2SCL | Setup Time of SDIx Data Input to SCKx Edge | 35  | _   | ns    | VDD = 3.3V,<br>VDDCORE = 2.5V |

|              | TDIVZSCL              |                                            | 100 | _   | ns    | VDD = 2.15V,<br>VDD = 2.15V   |

| 74           | TscH2DIL,             | Hold Time of SDIx Data Input to SCKx Edge  | 30  | _   | ns    | VDD = 3.3V,                   |

|              | TscL2DIL              |                                            |     |     |       | VDDCORE = 2.5V                |

|              |                       |                                            | 83  |     | ns    | VDD = 2.15V                   |

| 75           | TDOR                  | SDOx Data Output Rise Time                 |     | 25  | ns    | PORTB or PORTC                |

| 76           | TDOF                  | SDOx Data Output Fall Time                 | _   | 25  | ns    | PORTB or PORTC                |

| 78           | TscR                  | SCKx Output Rise Time (Master mode)        | _   | 25  | ns    | PORTB or PORTC                |

| 79           | TscF                  | SCKx Output Fall Time (Master mode)        | _   | 25  | ns    | PORTB or PORTC                |

### **INDEX**

| A                                                |     | CTMU                                              | . 379 |

|--------------------------------------------------|-----|---------------------------------------------------|-------|

| A/D                                              | 351 | CTMU Current Source Calibration Circuit           | . 382 |

| A/D Converter Interrupt, Configuring             |     | CTMU Typical Connections and Internal             |       |

| Acquisition Requirements                         |     | Configuration for Pulse Delay Generation          | . 390 |

| ADCAL Bit                                        |     | CTMU Typical Connections and Internal             |       |

| ADRESH Register                                  |     | Configuration for Time Measurement                |       |

| Analog Port Pins, Configuring                    |     | Demultiplexed Addressing Mode                     |       |

| Associated Registers                             |     | Device Clock                                      | 38    |

| Automatic Acquisition Time                       |     | EUSART Transmit                                   | . 337 |

| Calibration                                      |     | EUSARTx Receive                                   | . 339 |

| Configuring the Module                           |     | Fail-Safe Clock Monitor                           | . 410 |

| Conversion Clock (TAD)                           |     | Fully Multiplexed Addressing Mode                 | . 186 |

| Conversion Requirements                          |     | Generic I/O Port Operation                        | . 131 |

| Conversion Status (GO/DONE Bit)                  |     | High/Low-Voltage Detect with External Input       |       |

| Conversions                                      |     | Interrupt Logic                                   | . 116 |

| Converter Characteristics                        |     | LCD Control                                       | . 194 |

|                                                  |     | Legacy Parallel Slave Port                        | . 180 |

| Operation in Power-Managed Modes                 |     | MSSPx (I <sup>2</sup> C Master Mode)              |       |

| Special Event Trigger (ECCPx)                    |     | MSSPx (I <sup>2</sup> C Mode)                     |       |

| Use of the ECCP2 Trigger                         |     | MSSPx (SPI Mode)                                  |       |

| Absolute Maximum Ratings                         |     | Multiplexed Addressing Application                |       |

| AC (Timing) Characteristics                      |     | On-Chip Reset Circuit                             |       |

| Load Conditions for Device Timing Specifications |     | Parallel EEPROM (Up to 15-Bit Address, 16-Bit     |       |

| Parameter Symbology                              |     | Data)                                             | . 194 |

| Temperature and Voltage Specifications           |     | Parallel EEPROM (Up to 15-Bit Address, 8-Bit      |       |

| Timing Conditions                                |     | Data)                                             | . 194 |

| ACKSTAT                                          |     | Parallel Master/Slave Connection Addressed Buffer |       |

| ACKSTAT Status Flag                              |     | Parallel Master/Slave Connection Buffered         | . 182 |

| ADCAL Bit                                        | 359 | Partially Multiplexed Addressing Application      |       |

| ADCON0 Register                                  |     | Partially Multiplexed Addressing Mode             |       |

| GO/DONE Bit                                      |     | PIC18F2XJ11 (28-Pin)                              |       |

| ADDFSR                                           |     | PIC18F4XJ11 (44-Pin)                              |       |

| ADDLW                                            |     | PMP Module                                        |       |

| ADDULNK                                          |     | PWM (Enhanced)                                    |       |

| ADDWF                                            |     | PWM Operation (Simplified)                        |       |

| ADDWFC                                           |     | Reads From Flash Program Memory                   |       |

| ADRESL Register                                  | 354 | RTCC                                              |       |

| Analog-to-Digital Converter. See A/D.            | 400 | Simplified Steering                               |       |

| ANDLW                                            |     | Single Comparator                                 |       |

| ANDWF                                            | 421 | Table Read Operation                              |       |

| Assembler                                        |     | Table Write Operation                             |       |

| MPASM Assembler                                  |     | Table Writes to Flash Program Memory              |       |

| Auto-Wake-up on Sync Break Character             | 340 | Timer0 in 16-Bit Mode                             |       |

| В                                                |     | Timer0 in 8-Bit Mode                              |       |

|                                                  | 0.4 | Timer1                                            |       |

| Bank Select Register                             |     | Timer2                                            |       |

| Baud Rate Generator                              |     | Timer3                                            |       |

| BC                                               |     | Timer4                                            |       |

| BCF                                              |     | Using the Open-Drain Output                       |       |

| BF Otatus Flag                                   |     | Watchdog Timer                                    |       |

| BF Status Flag                                   | 316 | BN                                                |       |

| Block Diagrams                                   | 400 | BNC                                               |       |

| +5V System Hardware Interface                    |     | BNN                                               |       |

| 8-Bit Multiplexed Address and Data Application   |     | BNOV                                              |       |

| A/D                                              |     | BNZ                                               |       |

| Analog Input Model                               |     | BOR. See Brown-out Reset.                         |       |

| Baud Rate Generator                              |     | BOV                                               | 427   |

| Capture Mode Operation                           |     | BRA                                               |       |

| Comparator Analog Input Model                    |     | Break Character (12-Bit) Transmit and Receive     |       |

| Comparator Configurations                        |     | BRG. See Baud Rate Generator.                     | . 072 |

| Comparator Output                                |     | Brown-out Reset (BOR)                             | 65    |

| Comparator Voltage Reference                     | 369 | and On-Chip Voltage Regulator                     |       |

| Comparator Voltage Reference Output Buffer       | 071 | Detecting                                         |       |

| Example                                          | 3/1 |                                                   | 50    |

| Power-up Timer (PWRT)                      | . 46, 66 | ALRMCFG (Alarm Configuration)                                                     | 23 <sup>-</sup> |

|--------------------------------------------|----------|-----------------------------------------------------------------------------------|-----------------|

| Time-out Sequence                          |          | ALRMDAY (Alarm Day Value)                                                         |                 |

| Prescaler, Timer0                          |          | ALRMHR (Alarm Hours Value)                                                        |                 |

| Prescaler, Timer2 (Timer4)                 |          | ALRMMIN (Alarm Minutes Value)                                                     |                 |

| PRI_IDLE Mode                              |          | ALRMMNTH (Alarm Month Value)                                                      |                 |

| PRI_RUN Mode                               |          | ALRMRPT (Alarm Calibration)                                                       |                 |

| Product Identification System              |          | ALRMSEC (Alarm Seconds Value)                                                     |                 |

| Program Counter                            |          | ALRMWD (Alarm Weekday Value)                                                      |                 |

| PCL, PCH and PCU Registers                 |          | ANCON0 (A/D Port Configuration 2)                                                 |                 |

| PCLATH and PCLATU Registers                |          | ANCON1 (A/D Port Configuration 1)                                                 |                 |

| Program Memory                             |          | Associated with Comparator                                                        |                 |

| ALU Status                                 | 96       | Associated with Watchdog Timer                                                    |                 |

| Extended Instruction Set                   |          | BAUDCONx (Baud Rate Control)                                                      |                 |

| Flash Configuration Words                  |          | CCPxCON (Enhanced Capture/Compare/PWM                                             | 001             |

| Hard Memory Vectors                        |          | x Control)                                                                        | 249             |

| Instructions                               |          | CMSTAT (Comparator Status)                                                        |                 |

| Two-Word                                   |          | CMxCON (Comparator Control x)                                                     |                 |

| Interrupt Vector                           |          | CONFIG1H (Configuration 1 High)                                                   |                 |

| Look-up Tables                             |          | CONFIG1L (Configuration 1 Low)                                                    |                 |

| Memory Maps                                |          | CONFIG2H (Configuration 2 High)                                                   |                 |

| Hard Vectors and Configuration Words       |          |                                                                                   |                 |

| Reset Vector                               |          | CONFIG2L (Configuration 2 Low)                                                    |                 |

|                                            |          | CONFIG3H (Configuration 3 High)                                                   |                 |

| Program Verification and Code Protection   |          | CONFIGAL (Configuration 3 Low)                                                    |                 |

| Programming, Device Instructions           |          | CONFIGAL (Configuration 4 High)                                                   |                 |

| Pulse Steering                             |          | CONFIG4L (Configuration 4 Low)                                                    |                 |

| PUSH                                       |          | CTMUCONH (CTMU Control High)                                                      |                 |

| PUSH and POP Instructions                  |          | CTMUCONL (CTMU Control Low)                                                       |                 |

| PUSHL                                      | 458      | CTMUICON (CTMU Current Control)                                                   | 39              |

| PWM (CCP Module)                           |          | CVRCON (Comparator Voltage Reference                                              |                 |

| Associated Registers                       |          | Control)                                                                          |                 |

| Duty Cycle                                 |          | DAY (Day Value)                                                                   |                 |

| Example Frequencies/Resolutions            |          | DEVID1 (Device ID 1)                                                              |                 |

| Operation Setup                            | 253      | DEVID2 (Device ID 2)                                                              |                 |

| Period                                     | 252      | DMACON1 (DMA Control 1)                                                           |                 |

| PR2/PR4 Registers                          | 252      | DMACON2 (DMA Control 2)                                                           | 28              |

| TMR2 (TMR4) to PR2 (PR4) Match             | 252      | DSCONH (Deep Sleep Control High Byte)                                             | 58              |

| PWM (ECCP Module)                          |          | DSCONL (Deep Sleep Control Low Byte)                                              | 58              |

| Effects of a Reset                         | 269      | DSGPR0 (Deep Sleep Persistent General                                             |                 |

| Operation in Power-Managed Modes           | 269      | Purpose 0)                                                                        | 59              |

| Operation with Fail-Safe Clock Monitor     | 269      | DSGPR1 (Deep Sleep Persistent General                                             |                 |

| Pulse Steering                             | 266      | Purpose 1)                                                                        | 59              |

| Steering Synchronization                   | 268      | DSWAKEH (Deep Sleep Wake High Byte)                                               | 60              |

| TMR4 to PR4 Match                          | 225      | DSWAKEL (Deep Sleep Wake Low Byte)                                                | 60              |

| PWM Mode. See Enhanced Capture/Compare/PWM | 255      | ECCPxAS (ECCPx Auto-Shutdown Control)                                             | 263             |

|                                            |          | ECCPxDEL (Enhanced PWM Control)                                                   | 266             |

| Q                                          |          | EECON1 (EEPROM Control 1)                                                         | 10              |

| Q Clock                                    | 253      | HLVDCON (High/Low-Voltage Detect Control)                                         | 373             |

| n.                                         |          | HOURS (Hours Value)                                                               |                 |

| R                                          |          | I <sup>2</sup> C Mode (MSSP)                                                      |                 |

| RAM. See Data Memory.                      |          | INTCON (Interrupt Control)                                                        |                 |

| RBIF Bit                                   | 138      | INTCON2 (Interrupt Control 2)                                                     |                 |

| RC_IDLE Mode                               | 54       | INTCON3 (Interrupt Control 3)                                                     |                 |

| RC_RUN Mode                                | 50       | IPR1 (Peripheral Interrupt Priority 1)                                            |                 |

| RCALL                                      | 443      | IPR2 (Peripheral Interrupt Priority 2)                                            |                 |

| RCON Register                              |          | IPR3 (Peripheral Interrupt Priority 3)                                            |                 |

| Bit Status During Initialization           | 68       | MINUTES (Minutes Value)                                                           |                 |

| Reader Response                            |          | MONTH (Month Value)                                                               |                 |

| Real-Time Clock and Calendar (RTCC)        | 227      | ODCON1 (Peripheral Open-Drain Control 1)                                          |                 |

| Operation                                  |          | ODCON1 (Peripheral Open-Drain Control 1) ODCON2 (Peripheral Open-Drain Control 2) |                 |

| Registers                                  |          | , , , , , , , , , , , , , , , , , , , ,                                           |                 |

| Reference Clock Output                     |          | ODCON3 (Peripheral Open-Drain Control 3)                                          |                 |

| Register File                              |          | OSCCON (Oscillator Control)                                                       |                 |

| Register File Summary                      |          | OSCTUNE (Oscillator Tuning)                                                       |                 |

| Registers                                  | . 50 00  | PADCFG1 (Pad Configuration Control 1)                                             |                 |

| ADCON0 (A/D Control 0)                     | 351      | PADCFG1 (Pad Configuration)                                                       |                 |

| ADCON1 (A/D Control 1)                     |          | Parallel Master Port                                                              | 1/2             |

| ADOOINT (A/D COIIIIOI I)                   | 55∠      |                                                                                   |                 |

| ALRMVAL Register Mapping                        | 242   | SUBLW                                              | . 449 |

|-------------------------------------------------|-------|----------------------------------------------------|-------|

| Calibration                                     | 242   | SUBULNK                                            | . 459 |

| Clock Source                                    | 240   | SUBWF                                              | . 449 |

| Digit Carry Rules                               |       | SUBWFB                                             |       |

| General Functionality                           |       | SWAPF                                              |       |

| Leap Year                                       |       | 01711                                              | . 100 |

| Register Mapping                                |       | Т                                                  |       |

| RTCVAL Register Mapping                         |       | Table Pointer Operations with TBLRD, TBLWT (table) | 106   |

|                                                 |       | Table Reads/Table Writes                           |       |

| Safety Window for Register Reads and Write:     |       | Table Reads/Table Writes                           |       |

| Write Lock                                      |       |                                                    |       |

| Peripheral Module Disable (PMD) Register        |       | TBLRD                                              |       |

| Register Interface                              |       | TBLWT                                              |       |

| Register Maps                                   |       | Timer0                                             |       |

| Reset                                           | 244   | Associated Registers                               |       |

| Device                                          | 244   | Operation                                          | 198   |

| Power-on Reset (POR)                            | 244   | Overflow Interrupt                                 | 199   |

| Value Registers (RTCVAL)                        |       | Prescaler                                          | 199   |

| RTCEN Bit Write                                 |       | Switching Assignment                               | . 199 |

|                                                 | 00    | Prescaler Assignment (PSA Bit)                     |       |

| S                                               |       | Prescaler Select (T0PS2:T0PS0 Bits)                |       |

| SCKx                                            | 272   | Reads and Writes in 16-Bit Mode                    |       |

| SDIX                                            |       | Source Edge Select (T0SE Bit)                      |       |

|                                                 |       |                                                    |       |

| SDOx                                            |       | Source Select (T0CS Bit)                           |       |

| SEC_IDLE Mode                                   |       | Timer1                                             |       |

| SEC_RUN Mode                                    |       | 16-Bit Read/Write Mode                             |       |

| Serial Clock, SCKx                              |       | Associated Registers                               |       |

| Serial Data In (SDIx)                           | 272   | Clock Source Selection                             | . 204 |

| Serial Data Out (SDOx)                          | 272   | Gate                                               | . 208 |

| Serial Peripheral Interface. See SPI Mode.      |       | Interrupt                                          | 207   |

| SETF                                            | 447   | Operation                                          | . 204 |

| Shoot-Through Current                           |       | Oscillator 201                                     |       |

| Slave Select (SSx)                              |       | Layout Considerations                              |       |

| SLEEP                                           |       | Resetting, Using the ECCP Special Event Trigger .  |       |

| Software Simulator (MPLAB SIM)                  |       | TMR1H Register                                     |       |

| Special Event Trigger. See Compare (ECCP Mode). | 404   | TMR1L Register                                     |       |

|                                                 | 205   | Use as a Clock Source                              |       |

| Special Features of the CPU                     |       |                                                    |       |

| SPI Mode (MSSP)                                 |       | Timer2                                             |       |

| Associated Registers                            |       | Associated Registers                               |       |

| Bus Mode Compatibility                          |       | Interrupt                                          |       |

| Clock Speed, Interactions                       |       | Operation                                          |       |

| Effects of a Reset                              | 280   | Output                                             | . 214 |

| Enabling SPI I/O                                | 276   | Timer3                                             | . 215 |

| Master Mode                                     | 277   | 16-Bit Read/Write Mode                             | 219   |

| Master/Slave Connection                         | 276   | Associated Registers                               | 223   |

| Operation                                       | 275   | Gate                                               |       |

| Open-Drain Output Option                        |       | Operation                                          |       |

| Operation in Power-Managed Modes                |       | Oscillator                                         |       |

| Registers                                       |       | Overflow Interrupt                                 |       |

|                                                 |       | Special Event Trigger (ECCP)                       |       |

| Serial Clock                                    |       |                                                    |       |

| Serial Data In                                  |       | TMR3H Register                                     |       |

| Serial Data Out                                 |       | TMR3L Register                                     |       |

| Slave Mode                                      |       | Timer4                                             |       |

| Slave Select                                    | 272   | Associated Registers                               |       |

| Slave Select Synchronization                    | 278   | Interrupt                                          | . 226 |

| SPI Clock                                       | 277   | MSSP Clock Shift                                   | . 226 |

| SSPxBUF Register                                | 277   | Operation                                          | . 225 |

| SSPxSR Register                                 |       | Output                                             |       |

| Typical Connection                              |       | Postscaler. See Postscaler, Timer4.                |       |

| SSPOV                                           |       | PR4 Register                                       | 225   |

| SSPOV Status Flag                               |       | Prescaler. See Prescaler, Timer4.                  | . 223 |

|                                                 | 510   |                                                    | 225   |

| SSPxSTAT Register                               | 2 200 | TMR4 to DR4 Metab Interrupt                        |       |

| R/W Bit296                                      | -     | TMR4 to PR4 Match Interrupt                        | , 226 |

| SSx                                             |       | Timing Diagrams                                    |       |

| Stack Full/Underflow Resets                     |       | A/D Conversion                                     |       |

| SUBFSR                                          | 459   | Asynchronous Reception                             |       |

| SUBFWB                                          | 448   | Asynchronous Transmission                          | . 338 |

NOTES: