Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 16                                                                         |

| Program Memory Size        | 16KB (8K x 16)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 3.8K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.15V ~ 3.6V                                                               |

| Data Converters            | A/D 10x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 28-SPDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f24j11-i-sp |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.1.4 EXTENDED INSTRUCTION SET

The PIC18F46J11 family implements the optional extension to the PIC18 instruction set, adding eight new instructions and an Indexed Addressing mode. Enabled as a device configuration option, the extension has been specifically designed to optimize re-entrant application code originally developed in high-level languages, such as C.

## 1.1.5 EASY MIGRATION

Regardless of the memory size, all devices share the same rich set of peripherals, allowing for a smooth migration path as applications grow and evolve.

The consistent pinout scheme used throughout the entire family also aids in migrating to the next larger device.

The PIC18F46J11 family is also pin compatible with other PIC18 families, such as the PIC18F4620, PIC18F4520 and PIC18F45J10. This allows a new dimension to the evolution of applications, allowing developers to select different price points within Microchip's PIC18 portfolio, while maintaining the same feature set.

# 1.2 Other Special Features

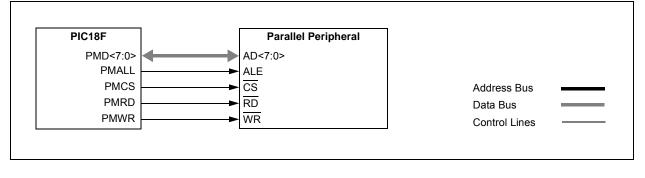

- Communications: The PIC18F46J11 family incorporates a range of serial and parallel communication peripherals. This device also includes two independent Enhanced USARTs and two Master Synchronous Serial Port (MSSP) modules, capable of both Serial Peripheral Interface (SPI) and I<sup>2</sup>C<sup>™</sup> (Master and Slave) modes of operation. The device also has a parallel port and can be configured to serve as either a Parallel Master Port (PMP) or as a Parallel Slave Port (PSP).

- ECCP Modules: All devices in the family incorporate three Enhanced Capture/Compare/PWM (ECCP) modules to maximize flexibility in control applications. Up to four different time bases may be used to perform several different operations at once. Each of the ECCPs offers up to four PWM outputs, allowing for a total of eight PWMs. The ECCPs also offer many beneficial features, including polarity selection, programmable dead time, auto-shutdown and restart and Half-Bridge and Full-Bridge Output modes.

- **10-Bit A/D Converter:** This module incorporates programmable acquisition time, allowing for a channel to be selected and a conversion to be initiated without waiting for a sampling period, and thus, reducing code overhead.

- Extended Watchdog Timer (WDT): This enhanced version incorporates a 16-bit prescaler, allowing an extended time-out range that is stable across operating voltage and temperature. See Section 29.0 "Electrical Characteristics" for time-out periods.

## 1.3 Details on Individual Family Devices

Devices in the PIC18F46J11 family are available in 28-pin and 44-pin packages. Block diagrams for the two groups are shown in Figure 1-1 and Figure 1-2. The devices are differentiated from each other in two ways:

- Flash program memory (three sizes: 16 Kbytes for the PIC18FX4J11, 32 Kbytes for PIC18FX5J11 devices and 64 Kbytes for PIC18FX6J11)

- I/O ports (three bidirectional ports on 28-pin devices, five bidirectional ports on 44-pin devices)

All other features for devices in this family are identical. These are summarized in Table 1-1 and Table 1-2.

The pinouts for the PIC18F2XJ11 devices are listed in Table 1-3 and the pinouts for the PIC18F4XJ11 devices are listed in Table 1-4.

The PIC18F46J11 family of devices provides an on-chip voltage regulator to supply the correct voltage levels to the core. Parts designated with an "F" part number (such as PIC18F46J11) have the voltage regulator enabled.

These parts can run from 2.15V-3.6V on VDD, but should have the VDDCORE pin connected to VSs through a low-ESR capacitor. Parts designated with an "LF" part number (such as PIC18**LF**46J11) do not enable the voltage regulator. For "LF" parts, an external supply of 2.0V-2.7V has to be supplied to the VDDCORE pin with 2.0V-3.6V supplied to VDD (VDDCORE should never exceed VDD).

For more details about the internal voltage regulator, see **Section 26.3 "On-Chip Voltage Regulator"**.

NOTES:

# 10.1.3 INTERFACING TO A 5V SYSTEM

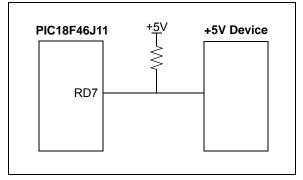

Though the VDDMAX of the PIC18F46J11 family is 3.6V, these devices are still capable of interfacing with 5V systems, even if the VIH of the target system is above 3.6V. This is accomplished by adding a pull-up resistor to the port pin (Figure 10-2), clearing the LAT bit for that pin and manipulating the corresponding TRIS bit (Figure 10-1) to either allow the line to be pulled high or to drive the pin low. Only port pins that are tolerant of voltages up to 5.5V can be used for this type of interface (refer to Section 10.1.2 "Input Pins and Voltage Considerations").

FIGURE 10-2: +5V SYSTEM HARDWARE INTERFACE

### EXAMPLE 10-1: COMMUNICATING WITH THE +5V SYSTEM

| BCF LATD, | 7 | ; set up LAT register so<br>; changing TRIS bit will<br>; drive line low |

|-----------|---|--------------------------------------------------------------------------|

|           |   | ; send a 0 to the 5V system<br>; send a 1 to the 5V system               |

## 10.1.4 OPEN-DRAIN OUTPUTS

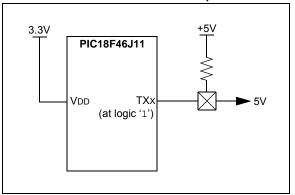

The output pins for several peripherals are also equipped with a configurable open-drain output option. This allows the peripherals to communicate with external digital logic operating at a higher voltage level, without the use of level translators. The open-drain option is implemented on port pins specifically associated with the data and clock outputs of the EUSARTs, the MSSP modules (in SPI mode) and the ECCP modules. It is selectively enabled by setting the open-drain control bit for the corresponding module in the ODCON registers (Register 10-1, Register 10-2 and Register 10-3). Their configuration is discussed in more detail with the individual port where these peripherals are multiplexed.

When the open-drain option is required, the output pin must also be tied through an external pull-up resistor provided by the user to a higher voltage level, up to 5.5V (Figure 10-3). When a digital logic high signal is output, it is pulled up to the higher voltage level.

### FIGURE 10-3: USING THE OPEN-DRAIN OUTPUT (USART SHOWN AS EXAMPLE)

## 10.1.5 TTL INPUT BUFFER OPTION

Many of the digital I/O ports use Schmitt Trigger (ST) input buffers. While this form of buffering works well with many types of input, some applications may require TTL level signals to interface with external logic devices. This is particularly true for the Parallel Master Port (PMP), which is likely to be interfaced to TTL level logic or memory devices.

The inputs for the PMP can be optionally configured for TTL buffers with the PMPTTL bit in the PADCFG1 register (Register 10-4). Setting this bit configures all data and control input pins for the PMP to use TTL buffers. By default, these PMP inputs use the port's ST buffers.

## 10.6 PORTE, TRISE and LATE Registers

| Note: | PORTE    | is | available | only | in | 44-pin |

|-------|----------|----|-----------|------|----|--------|

|       | devices. |    |           |      |    |        |

Depending on the particular PIC18F46J11 family device selected, PORTE is implemented in two different ways.

For 44-pin devices, PORTE is a 3-bit wide port. Three pins (RE0/AN5/PMRD, RE1/AN6/PMWR and RE2/ AN7/PMCS) are individually configurable as inputs or outputs. These pins have Schmitt Trigger input buffers. When selected as analog inputs, these pins will read as '0's.

The corresponding Data Direction register is TRISE. Setting a TRISE bit (= 1) will make the corresponding PORTE pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISE bit (= 0) will make the corresponding PORTE pin an output (i.e., put the contents of the output latch on the selected pin).

TRISE controls the direction of the RE pins, even when they are being used as analog inputs. The user must make sure to keep the pins configured as inputs when using them as analog inputs.

**Note:** On a POR, RE<2:0> are configured as analog inputs.

The Data Latch register (LATE) is also memory mapped. Read-modify-write operations on the LATE register read and write the latched output value for PORTE.

| CLRF  | LATE   | ; | Initialize LATE     |

|-------|--------|---|---------------------|

|       |        | ; | to clear output     |

|       |        | ; | data latches        |

| MOVLW | 0xE0   | ; | Configure REx       |

| MOVWF | ANCON0 | ; | for digital inputs  |

| MOVLW | 0x03   | ; | Value used to       |

|       |        | ; | initialize data     |

|       |        | ; | direction           |

| MOVWF | TRISE  | ; | Set RE<0> as inputs |

|       |        | ; | RE<1> as outputs    |

|       |        | ; | RE<2> as inputs     |

|       |        |   |                     |

Each of the PORTE pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by setting bit, REPU (PORTE<6>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a POR.

Note that the pull-ups can be used for any set of features, similar to the pull-ups found on PORTB.

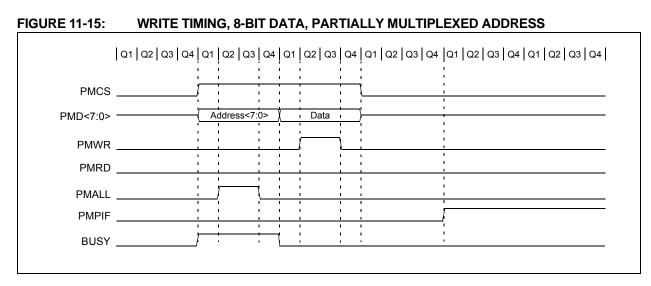

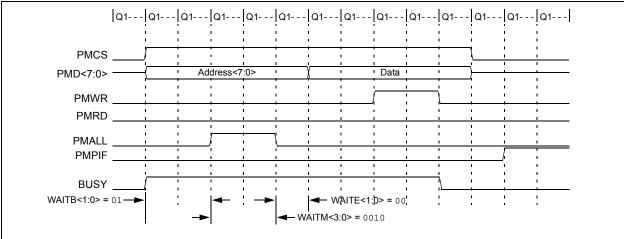

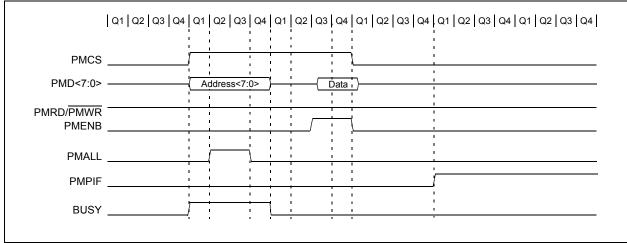

# FIGURE 11-16: WRITE TIMING, 8-BIT DATA, WAIT STATES ENABLED, PARTIALLY MULTIPLEXED ADDRESS

# FIGURE 11-17: READ TIMING, 8-BIT DATA, PARTIALLY MULTIPLEXED ADDRESS, ENABLE STROBE

# **11.4** Application Examples

This section introduces some potential applications for the PMP module.

## 11.4.1 MULTIPLEXED MEMORY OR PERIPHERAL

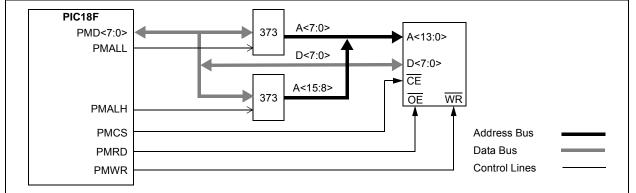

Figure 11-27 demonstrates the hookup of a memory or another addressable peripheral in Full Multiplex mode. Consequently, this mode achieves the best pin saving from the microcontroller perspective. However, for this configuration, there needs to be some external latches to maintain the address.

## 11.4.2 PARTIALLY MULTIPLEXED MEMORY OR PERIPHERAL

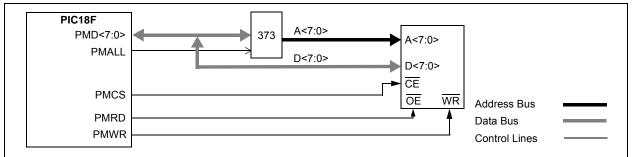

Partial multiplexing implies using more pins; however, for a few extra pins, some extra performance can be achieved. Figure 11-28 provides an example of a memory or peripheral that is partially multiplexed with an external latch. If the peripheral has internal latches, as displayed in Figure 11-29, then no extra circuitry is required except for the peripheral itself.

## FIGURE 11-28: EXAMPLE OF A PARTIALLY MULTIPLEXED ADDRESSING APPLICATION

## FIGURE 11-29: EXAMPLE OF AN 8-BIT MULTIPLEXED ADDRESS AND DATA APPLICATION

# 15.2 Timer3 Operation

Timer3 can operate in one of three modes:

- Timer

- Synchronous Counter

- · Asynchronous Counter

- · Timer with Gated Control

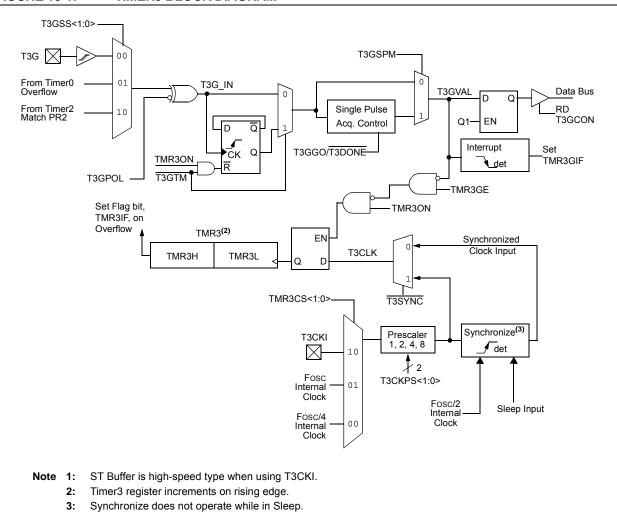

# FIGURE 15-1: TIMER3 BLOCK DIAGRAM

DS39932D-page 218

The operating mode is determined by the clock select

bits, TMR3CSx (T3CON<7:6>). When the TMR3CSx bits

are cleared (= 00), Timer3 increments on every internal

instruction cycle (Fosc/4). When TMR3CSx = 01, the Timer3 clock source is the system clock (Fosc), and

when it is '10', Timer3 works as a counter from the

external clock from the T3CKI pin (on the rising edge

after the first falling edge) or the Timer1 oscillator.

The CCPRxH register and a 2-bit internal latch are used to double-buffer the PWM duty cycle. This double-buffering is essential for glitchless PWM operation.

When the CCPRxH and 2-bit latch match TMR2 (TMR4), concatenated with an internal 2-bit Q clock or 2 bits of the TMR2 (TMR4) prescaler, the CCPx pin is cleared.

The maximum PWM resolution (bits) for a given PWM frequency is given by Equation 18-3:

## EQUATION 18-3:

PWM Resolution (max) =

$$\frac{\log(\frac{FOSC}{FPWM})}{\log(2)}$$

bits

**Note:** If the PWM duty cycle value is longer than the PWM period, the CCPx pin will not be cleared.

## 18.4.3 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Set the PWM period by writing to the PR2 (PR4) register.

- 2. Set the PWM duty cycle by writing to the CCPRxL register and CCPxCON<5:4> bits.

- 3. Make the CCPx pin an output by clearing the appropriate TRIS bit.

- 4. Set the TMR2 (TMR4) prescale value, then enable Timer2 (Timer4) by writing to T2CON (T4CON).

- 5. Configure the CCPx module for PWM operation.

## TABLE 18-2: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 40 MHz

| PWM Frequency              | 2.44 kHz | 9.77 kHz | 39.06 kHz | 156.25 kHz | 312.50 kHz | 416.67 kHz |

|----------------------------|----------|----------|-----------|------------|------------|------------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1          | 1          | 1          |

| PR2 Value                  | FFh      | FFh      | FFh       | 3Fh        | 1Fh        | 17h        |

| Maximum Resolution (bits)  | 10       | 10       | 10        | 8          | 7          | 6.58       |

#### 18.5.8 **OPERATION IN POWER-MANAGED** MODES

In Sleep mode, all clock sources are disabled. Timer2 will not increment and the state of the module will not change. If the ECCPx pin is driving a value, it will continue to drive that value. When the device wakes up, it will continue from this state. If Two-Speed Start-ups are enabled, the initial start-up frequency from HFINTOSC and the postscaler may not be stable immediately.

In PRI IDLE mode, the primary clock will continue to clock the ECCPx module without change.

#### 18.5.8.1 Operation with Fail-Safe Clock Monitor (FSCM)

If the Fail-Safe Clock Monitor (FSCM) is enabled, a clock failure will force the device into the power-managed RC RUN mode and the OSCFIF bit of the PIR2 register will be set. The ECCPx will then be clocked from the internal oscillator clock source, which may have a different clock frequency than the primary clock.

#### EFFECTS OF A RESET 18.5.9

Both Power-on Reset and subsequent Resets will force all ports to Input mode and the ECCP registers to their Reset states.

This forces the ECCP module to reset to a state compatible with previous, non-enhanced ECCP modules used on other PIC18 and PIC16 devices.

| Name     | Bit 7                    | Bit 6          | Bit 5          | Bit 4    | Bit 3    | Bit 2   | Bit 1   | Bit 0   | Reset<br>Values<br>on page: |

|----------|--------------------------|----------------|----------------|----------|----------|---------|---------|---------|-----------------------------|

| INTCON   | GIE/GIEH                 | PEIE/GIEL      | TMR0IE         | INT0IE   | RABIE    | TMR0IF  | INT0IF  | RABIF   | 69                          |

| RCON     | IPEN                     |                | _              | RI       | TO       | PD      | POR     | BOR     | 70                          |

| PIR1     | PMPIF <sup>(1)</sup>     | ADIF           | RCIF           | TXIF     | SSPIF    | CCP1IF  | TMR2IF  | TMR1IF  | 72                          |

| PIE1     | PMPIE <sup>(1)</sup>     | ADIE           | RCIE           | TXIE     | SSPIE    | CCP1IE  | TMR2IE  | TMR1IE  | 72                          |

| IPR1     | PMPIP <sup>(1)</sup>     | ADIP           | RCIP           | TXIP     | SSPIP    | CCP1IP  | TMR2IP  | TMR1IP  | 72                          |

| PIR2     | OSCFIF                   | CM2IF          | CM1IF          | _        | BCL1IF   | LVDIF   | TMR3IF  | CCP2IF  | 72                          |

| PIE2     | OSCFIE                   | CM2IE          | CM1IE          | _        | BCL1IE   | LVDIE   | TMR3IE  | CCP2IE  | 72                          |

| IPR2     | OSCFIP                   | CM2IP          | CM1IP          | _        | BCL1IP   | LVDIP   | TMR3IP  | CCP2IP  | 72                          |

| TRISC    | TRISC7                   | TRISC6         | TRISC5         | TRISC4   | TRISC3   | TRISC2  | TRISC1  | TRISC0  | 72                          |

| TMR1L    | Timer1 Register Low Byte |                |                |          |          |         |         |         |                             |

| TMR1H    | Timer1 Regi              | ster High Byte | 9              |          |          |         |         |         | 70                          |

| TCLKCON  | _                        |                |                | T1RUN    | _        | _       | T3CCP2  | T3CCP1  | 94                          |

| T1CON    | TMR1CS1                  | TMR1CS0        | T1CKPS1        | T1CKPS0  | T10SCEN  | T1SYNC  | RD16    | TMR10N  | 70                          |

| TMR2     | Timer2 Regi              | ster           |                |          |          |         |         |         | 70                          |

| T2CON    | _                        | T2OUTPS3       | T2OUTPS2       | T2OUTPS1 | T2OUTPS0 | TMR2ON  | T2CKPS1 | T2CKPS0 | 70                          |

| PR2      | Timer2 Peric             | d Register     |                |          |          |         |         |         | 70                          |

| TMR3L    | Timer3 Regi              | ster Low Byte  |                |          |          |         |         |         | 73                          |

| TMR3H    | Timer3 Regi              | ster High Byte | 9              |          |          |         |         |         | 73                          |

| T3CON    | TMR3CS1                  | TMR3CS0        | T3CKPS1        | T3CKPS0  | _        | T3SYNC  | RD16    | TMR3ON  | 73                          |

| CCPR1L   | Capture/Cor              | npare/PWM F    | Register 1 Lov | v Byte   |          |         |         |         | 72                          |

| CCPR1H   | Capture/Cor              | npare/PWM F    | Register 1 Hig | h Byte   |          |         |         |         | 72                          |

| CCP1CON  | P1M1                     | P1M0           | DC1B1          | DC1B0    | CCP1M3   | CCP1M2  | CCP1M1  | CCP1M0  | 72                          |

| ECCP1AS  | ECCP1ASE                 | ECCP1AS2       | ECCP1AS1       | ECCP1AS0 | PSS1AC1  | PSS1AC0 | PSS1BD1 | PSS1BD0 | 70                          |

| ECCP1DEL | P1RSEN                   | P1DC6          | P1DC5          | P1DC4    | P1DC3    | P1DC2   | P1DC1   | P1DC0   | 72                          |

# TABLE 18-5: REGISTERS ASSOCIATED WITH ECCP1 MODULE AND TIMER1 TO TIMER3

nimplemented, read as '0'. Shaded cells are not used during ECCP operation.

Note 1: These bits are only available on 44-pin devices.

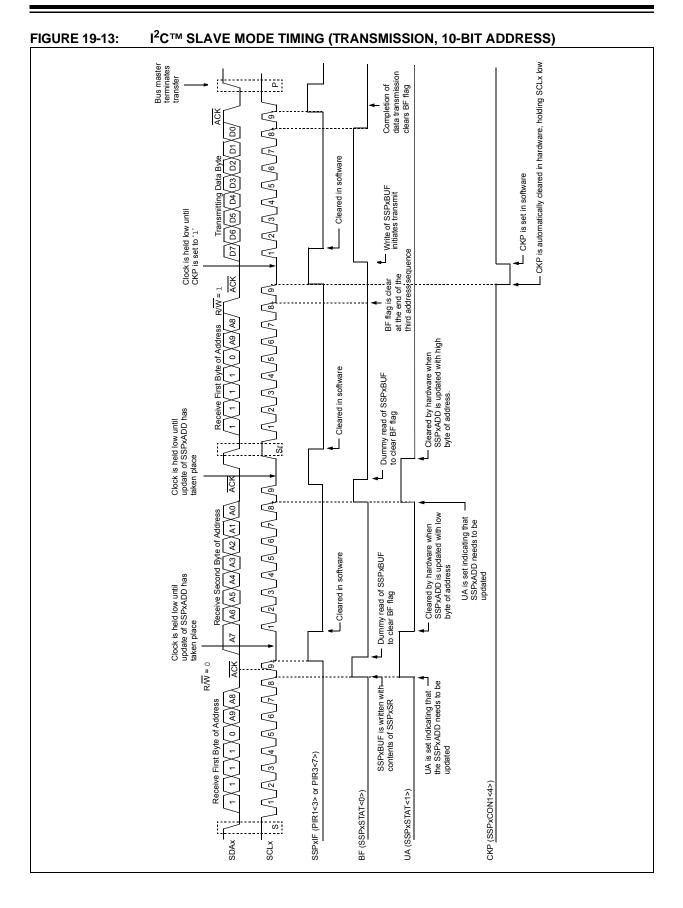

## 19.5.3.5 Reception

When the  $R/\overline{W}$  bit of the address byte is clear and an address match occurs, the  $R/\overline{W}$  bit of the SSPxSTAT register is cleared. The received address is loaded into the SSPxBUF register and the SDAx line is held low (ACK).

When the address byte overflow condition exists, then the no Acknowledge (ACK) pulse is given. An overflow condition is defined as either bit, BF (SSPxSTAT<0>), is set or bit, SSPOV (SSPxCON1<6>), is set.

An MSSP interrupt is generated for each data transfer byte. The interrupt flag bit, SSPxIF, must be cleared in software. The SSPxSTAT register is used to determine the status of the byte.

If SEN is enabled (SSPxCON2<0> = 1), SCLx will be held low (clock stretch) following each data transfer. The clock must be released by setting bit, CKP (SSPxCON1<4>). See **Section 19.5.4** "Clock **Stretching**" for more details.

# 19.5.3.6 Transmission

When the R/W bit of the incoming address byte is set and an address match occurs, the R/W bit of the SSPxSTAT register is set. The received address is loaded into the SSPxBUF register. The ACK pulse will be sent on the ninth bit and pin SCLx is held low regardless of SEN (see Section 19.5.4 "Clock Stretching" for more details). By stretching the clock, the master will be unable to assert another clock pulse until the slave is done preparing the transmit data. The transmit data must be loaded into the SSPxBUF register, which also loads the SSPxSR register. Then, the SCLx pin be enabled by setting bit, should CKP (SSPxCON1<4>). The eight data bits are shifted out on the falling edge of the SCLx input. This ensures that the SDAx signal is valid during the SCLx high time (Figure 19-10).

The  $\overline{ACK}$  pulse from the master-receiver is latched on the rising edge of the ninth SCLx input pulse. If the SDAx line is high (not  $\overline{ACK}$ ), then the data transfer is complete. In this case, when the  $\overline{ACK}$  is latched by the slave, the slave monitors for another occurrence of the Start bit. If the SDAx line was low ( $\overline{ACK}$ ), the next transmit data must be loaded into the SSPxBUF register. Again, the SCLx pin must be enabled by setting bit, CKP.

An MSSP interrupt is generated for each data transfer byte. The SSPxIF bit must be cleared in software and the SSPxSTAT register is used to determine the status of the byte. The SSPxIF bit is set on the falling edge of the ninth clock pulse.

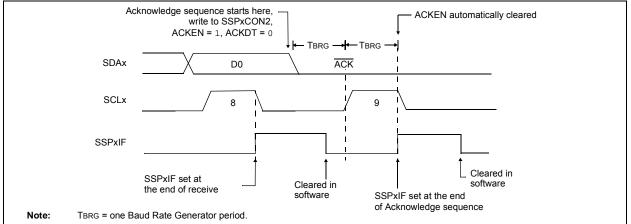

## 19.5.12 ACKNOWLEDGE SEQUENCE TIMING

An Acknowledge sequence is enabled by setting the Acknowledge Sequence Enable bit. ACKEN (SSPxCON2<4>). When this bit is set, the SCLx pin is pulled low and the contents of the Acknowledge data bit are presented on the SDAx pin. If the user wishes to generate an Acknowledge, then the ACKDT bit should be cleared. If not, the user should set the ACKDT bit before starting an Acknowledge sequence. The BRG then counts for one rollover period (TBRG) and the SCLx pin is deasserted (pulled high). When the SCLx pin is sampled high (clock arbitration), the BRG counts for TBRG; the SCLx pin is then pulled low. Following this, the ACKEN bit is automatically cleared, the BRG is turned off and the MSSP module then goes into an inactive state (Figure 19-25).

## 19.5.12.1 WCOL Status Flag

If the user writes the SSPxBUF when an Acknowledge sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write does not occur).

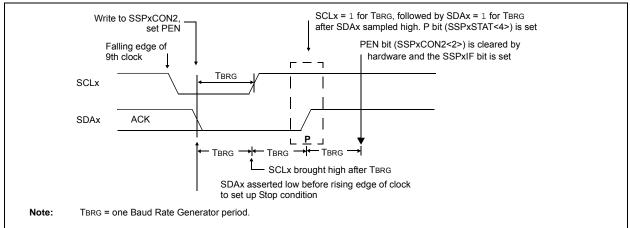

## 19.5.13 STOP CONDITION TIMING

A Stop bit is asserted on the SDAx pin at the end of a receive/transmit by setting the Stop Sequence Enable bit, PEN (SSPxCON2<2>). At the end of a receive/transmit, the SCLx line is held low after the falling edge of the ninth clock. When the PEN bit is set, the master will assert the SDAx line low. When the SDAx line is sampled low, the BRG is reloaded and counts down to 0. When the BRG times out, the SCLx pin will be brought high and one Baud Rate Generator rollover count (TBRG) later, the SDAx pin will be deasserted. When the SDAx pin is sampled high while SCLx is high, the Stop bit (SSPxSTAT<4>) is set. A TBRG later, the PEN bit is cleared and the SSPxIF bit is set (Figure 19-26).

## 19.5.13.1 WCOL Status Flag

If the user writes the SSPxBUF when a Stop sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

# FIGURE 19-25: ACKNOWLEDGE SEQUENCE WAVEFORM

## FIGURE 19-26: STOP CONDITION RECEIVE OR TRANSMIT MODE

|                       |                                                                                                                                           |                                             |                  |                   | •              |                 | ,               |  |  |  |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|------------------|-------------------|----------------|-----------------|-----------------|--|--|--|

| R/W-0                 | R/W-0                                                                                                                                     | R/W-0                                       | R/W-1            | R/W-1             | R/W-1          | R/W-1           | R/W-1           |  |  |  |

| CON                   | COE                                                                                                                                       | CPOL                                        | EVPOL1           | EVPOL0            | CREF           | CCH1            | CCH0            |  |  |  |

| bit 7                 |                                                                                                                                           |                                             |                  |                   |                | •               | bit             |  |  |  |

| Logondi               |                                                                                                                                           |                                             |                  |                   |                |                 |                 |  |  |  |

| Legend:<br>R = Readab | la hit                                                                                                                                    | W = Writable                                | h it             |                   | opted bit read | d oo 'O'        |                 |  |  |  |

|                       |                                                                                                                                           |                                             |                  | U = Unimplem      |                |                 |                 |  |  |  |

| -n = Value a          | IT POR                                                                                                                                    | '1' = Bit is set                            |                  | '0' = Bit is clea | ared           | x = Bit is unkr | nown            |  |  |  |

| bit 7                 | CON: Compa                                                                                                                                | arator Enable b                             | it               |                   |                |                 |                 |  |  |  |

|                       | 1 = Compara                                                                                                                               | tor is enabled tor is disabled              |                  |                   |                |                 |                 |  |  |  |

| bit 6                 | COE: Compa                                                                                                                                | COE: Comparator Output Enable bit           |                  |                   |                |                 |                 |  |  |  |

|                       | 1 = Compara                                                                                                                               | tor output is pr                            | esent on the C   | xOUT pin (assig   | gned in PPS m  | odule)          |                 |  |  |  |

|                       | 0 = Compara                                                                                                                               | tor output is int                           | ernal only       |                   |                |                 |                 |  |  |  |

| bit 5                 | CPOL: Comp                                                                                                                                | CPOL: Comparator Output Polarity Select bit |                  |                   |                |                 |                 |  |  |  |

|                       | 1 = Comparator output is inverted                                                                                                         |                                             |                  |                   |                |                 |                 |  |  |  |

|                       | 0 = Compara                                                                                                                               | tor output is no                            | t inverted       |                   |                |                 |                 |  |  |  |

| bit 4-3               | EVPOL<1:0>: Interrupt Polarity Select bits                                                                                                |                                             |                  |                   |                |                 |                 |  |  |  |

|                       | 11 = Interrupt generation on any change of the output <sup>(1)</sup>                                                                      |                                             |                  |                   |                |                 |                 |  |  |  |

|                       | 10 = Interrupt generation only on high-to-low transition of the output                                                                    |                                             |                  |                   |                |                 |                 |  |  |  |

|                       | <ul> <li>01 = Interrupt generation only on low-to-high transition of the output</li> <li>00 = Interrupt generation is disabled</li> </ul> |                                             |                  |                   |                |                 |                 |  |  |  |

| bit 2                 | •                                                                                                                                         | •                                           |                  | on-invertina inr  | out)           |                 |                 |  |  |  |

|                       | <b>CREF:</b> Comparator Reference Select bit (non-inverting input)<br>1 = Non-inverting input connects to internal CVREF voltage          |                                             |                  |                   |                |                 |                 |  |  |  |

|                       |                                                                                                                                           | rting input conr                            |                  | 0                 |                |                 |                 |  |  |  |

| bit 1-0               | CCH<1:0>: (                                                                                                                               | Comparator Cha                              | annel Select bi  | ts                |                |                 |                 |  |  |  |

|                       | 11 = Invertir                                                                                                                             | ng input of com                             | parator connec   | ts to VIRV        |                |                 |                 |  |  |  |

|                       |                                                                                                                                           |                                             | ng input of com  | parator connec    | ts to C2INB pi | n; for CM2CON   | I, reserved     |  |  |  |

|                       | 01 = Reserv                                                                                                                               |                                             | norator connor   | to to CVIND nin   |                |                 |                 |  |  |  |

|                       |                                                                                                                                           | ig input of com                             | parator connec   | ts to CxINB pin   |                |                 |                 |  |  |  |

| Note 1: T             | he CMxIF is aut                                                                                                                           | omatically set a                            | any time this mo | ode is selected a | and must be cl | eared by the ap | oplication afte |  |  |  |

|                       | 1                                                                                                                                         | 1 <sup>4</sup>                              |                  |                   |                |                 |                 |  |  |  |

# REGISTER 22-1: CMxCON: COMPARATOR CONTROL x REGISTER (ACCESS FD2h/FD1h)

the initial configuration.

# 24.6 Operation During Sleep

When enabled, the HLVD circuitry continues to operate during Sleep. If the device voltage crosses the trip point, the LVDIF bit will be set and the device will wakeup from Sleep. Device execution will continue from the interrupt vector address if interrupts have been globally enabled.

# 24.7 Effects of a Reset

A device Reset forces all registers to their Reset state. This forces the HLVD module to be turned off.

| Name    | Bit 7    | Bit 6     | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|---------|----------|-----------|--------|--------|--------|--------|--------|--------|----------------------------|

| HLVDCON | VDIRMAG  | BGVST     | IRVST  | HLVDEN | HLVDL3 | HLVDL2 | HLVDL1 | HLVDL0 | 72                         |

| INTCON  | GIE/GIEH | PEIE/GIEL | TMR0IE | INT0IE | RBIE   | TMR0IF | INT0IF | RBIF   | 69                         |

| PIR2    | OSCFIF   | CM1IF     | CM2IF  | —      | BCLIF  | LVDIF  | TMR3IF | CCP2IF | 71                         |

| PIE2    | OSCFIE   | CM1IE     | CM2IE  | —      | BCLIE  | LVDIE  | TMR3IE | CCP2IE | 71                         |

| IPR2    | OSCFIP   | CM1IP     | CM2IP  | _      | BCLIP  | LVDIP  | TMR3IP | CCP2IP | 71                         |

## TABLE 24-1: REGISTERS ASSOCIATED WITH HIGH/LOW-VOLTAGE DETECT MODULE

Legend: — = unimplemented, read as '0'. Shaded cells are unused by the HLVD module.

NOTES:

# PIC18F46J11 FAMILY

| INCF                                                                                                                                                                                                                                                                          | SZ                     | Increment                                                                          | Increment f, Skip if 0                                                                                                                                               |                         |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--|--|--|--|--|

| Synta                                                                                                                                                                                                                                                                         | ax:                    | INCFSZ f                                                                           | {,d {,a}}                                                                                                                                                            |                         |  |  |  |  |  |

| Oper                                                                                                                                                                                                                                                                          | ands:                  | $\begin{array}{l} 0 \leq f \leq 255 \\ d  \in  [0,1] \\ a  \in  [0,1] \end{array}$ | d ∈ [0,1]                                                                                                                                                            |                         |  |  |  |  |  |

| Oper                                                                                                                                                                                                                                                                          | ation:                 | .,                                                                                 | (f) + 1 $\rightarrow$ dest,<br>skip if result = 0                                                                                                                    |                         |  |  |  |  |  |

| Statu                                                                                                                                                                                                                                                                         | s Affected:            | None                                                                               | None                                                                                                                                                                 |                         |  |  |  |  |  |

| Enco                                                                                                                                                                                                                                                                          | ding:                  | 0011                                                                               | 11da fff                                                                                                                                                             | f ffff                  |  |  |  |  |  |

| Desc                                                                                                                                                                                                                                                                          | ription:               | incremented placed in W                                                            | The contents of register 'f' are<br>incremented. If 'd' is '0', the result is<br>placed in W. If 'd' is '1', the result is<br>placed back in register 'f'. (default) |                         |  |  |  |  |  |

|                                                                                                                                                                                                                                                                               |                        | which is alread                                                                    | If the result is '0', the next instruction which is already fetched is discarded and a $NOP$ is executed instead, making it a two-cycle instruction.                 |                         |  |  |  |  |  |

|                                                                                                                                                                                                                                                                               |                        | -                                                                                  | ne Access Ban<br>ne BSR is useo<br>(default).                                                                                                                        |                         |  |  |  |  |  |

| If 'a' is '0' and the extended instructi<br>set is enabled, this instruction opera<br>in Indexed Literal Offset Addressing<br>mode whenever f ≤ 95 (5Fh). See<br>Section 27.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Index<br>Literal Offset Mode" for details. |                        |                                                                                    |                                                                                                                                                                      |                         |  |  |  |  |  |

| Word                                                                                                                                                                                                                                                                          | ls:                    | 1                                                                                  |                                                                                                                                                                      |                         |  |  |  |  |  |

| Cycle                                                                                                                                                                                                                                                                         | es:                    |                                                                                    | ycles if skip a<br>a 2-word instr                                                                                                                                    |                         |  |  |  |  |  |

| QC                                                                                                                                                                                                                                                                            | ycle Activity:         |                                                                                    |                                                                                                                                                                      |                         |  |  |  |  |  |

| i                                                                                                                                                                                                                                                                             | Q1                     | Q2                                                                                 | Q3                                                                                                                                                                   | Q4                      |  |  |  |  |  |

|                                                                                                                                                                                                                                                                               | Decode                 | Read<br>register 'f'                                                               | Process<br>Data                                                                                                                                                      | Write to<br>destination |  |  |  |  |  |

| lf sk                                                                                                                                                                                                                                                                         | ip:                    |                                                                                    | Data                                                                                                                                                                 | destination             |  |  |  |  |  |

|                                                                                                                                                                                                                                                                               | Q1                     | Q2                                                                                 | Q3                                                                                                                                                                   | Q4                      |  |  |  |  |  |

|                                                                                                                                                                                                                                                                               | No                     | No                                                                                 | No                                                                                                                                                                   | No                      |  |  |  |  |  |

| lf ek                                                                                                                                                                                                                                                                         | operation              | operation<br>d by 2-word ins                                                       | operation                                                                                                                                                            | operation               |  |  |  |  |  |

| 11 31                                                                                                                                                                                                                                                                         | Q1                     | Q2                                                                                 | Q3                                                                                                                                                                   | Q4                      |  |  |  |  |  |

|                                                                                                                                                                                                                                                                               | No                     | No                                                                                 | No                                                                                                                                                                   | No                      |  |  |  |  |  |

|                                                                                                                                                                                                                                                                               | operation              | operation                                                                          | operation                                                                                                                                                            | operation               |  |  |  |  |  |

|                                                                                                                                                                                                                                                                               | No                     | No                                                                                 | No                                                                                                                                                                   | No                      |  |  |  |  |  |

|                                                                                                                                                                                                                                                                               | operation              | operation                                                                          | operation                                                                                                                                                            | operation               |  |  |  |  |  |

| <u>Exan</u>                                                                                                                                                                                                                                                                   | nple:                  | HERE I<br>NZERO :<br>ZERO :                                                        |                                                                                                                                                                      | T, 1, 0                 |  |  |  |  |  |

|                                                                                                                                                                                                                                                                               | Before Instruc         | tion                                                                               |                                                                                                                                                                      |                         |  |  |  |  |  |

|                                                                                                                                                                                                                                                                               | PC<br>After Instructio |                                                                                    |                                                                                                                                                                      |                         |  |  |  |  |  |

|                                                                                                                                                                                                                                                                               | CNT<br>If CNT          | = CNT + 1<br>= 0;                                                                  | l                                                                                                                                                                    |                         |  |  |  |  |  |

|                                                                                                                                                                                                                                                                               | PC                     | <ul> <li>Address</li> </ul>                                                        | (ZERO)                                                                                                                                                               |                         |  |  |  |  |  |

|                                                                                                                                                                                                                                                                               | If CNT<br>PC           | <ul><li>≠ 0;</li><li>= Address</li></ul>                                           | (NZERO)                                                                                                                                                              |                         |  |  |  |  |  |

|                                                                                                                                                                                                                                                                               |                        |                                                                                    |                                                                                                                                                                      |                         |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description: | INFSNZ f<br>$0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$<br>(f) + 1 $\rightarrow$ de<br>skip if result<br>None<br>0100<br>The content<br>incremented                                                                                                                          | est,<br>t≠0                                                               |                          |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--------------------------|--|--|--|--|--|--|

| Operation:<br>Status Affected:<br>Encoding:                                         | $d \in [0,1]$<br>$a \in [0,1]$<br>(f) + 1 → deskip if result<br>None<br>0100<br>The content                                                                                                                                                                                          | t≠0                                                                       |                          |  |  |  |  |  |  |

| Status Affected:<br>Encoding:                                                       | a ∈ [0,1]<br>(f) + 1 → de<br>skip if result<br>None<br>0100<br>The content                                                                                                                                                                                                           | t≠0                                                                       |                          |  |  |  |  |  |  |

| Status Affected:<br>Encoding:                                                       | (f) + 1 $\rightarrow$ deskip if result<br>None<br>0100<br>The content                                                                                                                                                                                                                | t≠0                                                                       |                          |  |  |  |  |  |  |

| Status Affected:<br>Encoding:                                                       | skip if result<br>None<br>0100<br>The content                                                                                                                                                                                                                                        | t≠0                                                                       |                          |  |  |  |  |  |  |

| Encoding:                                                                           | None<br>0100<br>The content                                                                                                                                                                                                                                                          |                                                                           |                          |  |  |  |  |  |  |

| Encoding:                                                                           | 0100<br>The content                                                                                                                                                                                                                                                                  | 10da fff                                                                  |                          |  |  |  |  |  |  |

| 8                                                                                   | The content                                                                                                                                                                                                                                                                          | 10da fff                                                                  |                          |  |  |  |  |  |  |

| Description:                                                                        |                                                                                                                                                                                                                                                                                      |                                                                           |                          |  |  |  |  |  |  |

|                                                                                     | incremented. If 'd' is '0', the result is<br>placed in W. If 'd' is '1', the result is<br>placed back in register 'f' (default).                                                                                                                                                     |                                                                           |                          |  |  |  |  |  |  |

|                                                                                     | instruction v<br>discarded a                                                                                                                                                                                                                                                         | is not '0', the i<br>which is alread<br>nd a NOP is ex<br>king it a two-c | ly fetched is<br>kecuted |  |  |  |  |  |  |

|                                                                                     | If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank (default).                                                                                                                                                                   |                                                                           |                          |  |  |  |  |  |  |

|                                                                                     | If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever f ≤ 95 (5Fh). See<br>Section 27.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |                                                                           |                          |  |  |  |  |  |  |

| Words:                                                                              | 1                                                                                                                                                                                                                                                                                    |                                                                           |                          |  |  |  |  |  |  |

| Cycles:                                                                             | 1(2)<br><b>Note:</b> 3 cycles if skip and followed<br>by a 2-word instruction.                                                                                                                                                                                                       |                                                                           |                          |  |  |  |  |  |  |

| Q Cycle Activity:                                                                   |                                                                                                                                                                                                                                                                                      |                                                                           |                          |  |  |  |  |  |  |

| Q1                                                                                  | Q2                                                                                                                                                                                                                                                                                   | Q3                                                                        | Q4                       |  |  |  |  |  |  |

| Decode                                                                              | Read                                                                                                                                                                                                                                                                                 | Process                                                                   | Write to                 |  |  |  |  |  |  |

|                                                                                     | register 'f'                                                                                                                                                                                                                                                                         | Data                                                                      | destination              |  |  |  |  |  |  |

| If skip:                                                                            | 00                                                                                                                                                                                                                                                                                   | 00                                                                        | 04                       |  |  |  |  |  |  |

| Q1                                                                                  | Q2                                                                                                                                                                                                                                                                                   | Q3                                                                        | Q4                       |  |  |  |  |  |  |

| No<br>operation                                                                     | No<br>operation                                                                                                                                                                                                                                                                      | No<br>operation                                                           | No<br>operation          |  |  |  |  |  |  |

| If skip and followed b                                                              |                                                                                                                                                                                                                                                                                      |                                                                           | operation                |  |  |  |  |  |  |

| Q1                                                                                  | Q2                                                                                                                                                                                                                                                                                   | Q3                                                                        | Q4                       |  |  |  |  |  |  |

| No                                                                                  | No                                                                                                                                                                                                                                                                                   | No                                                                        | No                       |  |  |  |  |  |  |

|                                                                                     | operation                                                                                                                                                                                                                                                                            | operation                                                                 | operation                |  |  |  |  |  |  |

| No                                                                                  | No                                                                                                                                                                                                                                                                                   | No                                                                        | No                       |  |  |  |  |  |  |

| operation                                                                           | operation                                                                                                                                                                                                                                                                            | operation                                                                 | operation                |  |  |  |  |  |  |

|                                                                                     | HERE INFSNZ REG, 1, 0<br>ZERO<br>NZERO                                                                                                                                                                                                                                               |                                                                           |                          |  |  |  |  |  |  |

| Example:                                                                            |                                                                                                                                                                                                                                                                                      |                                                                           |                          |  |  |  |  |  |  |

| Example:<br>Before Instructio<br>PC =                                               | zero<br>nzero<br>n                                                                                                                                                                                                                                                                   | G (HERE)                                                                  |                          |  |  |  |  |  |  |

| Before Instructio<br>PC =<br>After Instruction<br>REG =                             | ZERO<br>NZERO<br>n<br>Address<br>REG + 1                                                                                                                                                                                                                                             |                                                                           |                          |  |  |  |  |  |  |

| Before Instructio<br>PC =<br>After Instruction                                      | ZERO<br>NZERO<br>n<br>Address<br>REG + 7<br>0;                                                                                                                                                                                                                                       | 1                                                                         |                          |  |  |  |  |  |  |

# PIC18F46J11 FAMILY

| IORI        | w                             | Inclusive           | Inclusive OR Literal with W                                                           |     |    |               |  |  |

|-------------|-------------------------------|---------------------|---------------------------------------------------------------------------------------|-----|----|---------------|--|--|

| Synt        | ax:                           |                     |                                                                                       |     |    |               |  |  |

| Oper        | rands:                        | $0 \le k \le 25$    | 5                                                                                     |     |    |               |  |  |

| Oper        | ration:                       | (W) .OR. k          | $x \to W$                                                                             |     |    |               |  |  |

| Statu       | is Affected:                  | N, Z                | N, Z                                                                                  |     |    |               |  |  |

| Enco        | oding:                        | 0000                | 1001                                                                                  | kkk | k  | kkkk          |  |  |

| Desc        | cription:                     |                     | The contents of W are ORed with the eight-bit literal 'k'. The result is placed in W. |     |    |               |  |  |

| Word        | ds:                           | 1                   |                                                                                       |     |    |               |  |  |

| Cycle       | es:                           | 1                   |                                                                                       |     |    |               |  |  |

| QC          | ycle Activity:                |                     |                                                                                       |     |    |               |  |  |

|             | Q1                            | Q2                  | Q                                                                                     | 3   | Q4 |               |  |  |

|             | Decode                        | Read<br>literal 'k' | Proce<br>Dat                                                                          |     | V  | /rite to<br>W |  |  |

|             |                               |                     |                                                                                       |     |    |               |  |  |

| <u>Exar</u> | <u>nple:</u>                  | IORLW               | 35h                                                                                   |     |    |               |  |  |

|             | Before Instruction<br>W = 9Ah |                     |                                                                                       |     |    |               |  |  |

After Instruction W = BFh

| IORWF                                                                                                                        | Inclusive C                                                                                                                                                                                                                                                                          | DR W wi                                                                                                            | th f |                      |  |

|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|------|----------------------|--|

| Syntax:                                                                                                                      | IORWF f                                                                                                                                                                                                                                                                              | IORWF f {,d {,a}}                                                                                                  |      |                      |  |

| Operands:                                                                                                                    | $\begin{array}{l} 0 \leq f \leq 255 \\ d  \in  [0,1] \\ a  \in  [0,1] \end{array}$                                                                                                                                                                                                   | d ∈ [0,1]                                                                                                          |      |                      |  |