Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 16                                                                         |

| Program Memory Size        | 16KB (8K x 16)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 3.8K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.15V ~ 3.6V                                                               |

| Data Converters            | A/D 10x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 28-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f24j11-i-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 28/44-Pin, Low-Power, High-Performance Microcontrollers

### Power Management Features with nanoWatt XLP for Extreme Low Power:

- Deep Sleep mode: CPU off, Peripherals off, Currents Down to 13 nA and 850 nA with RTCC

- Able to wake-up on external triggers, programmable WDT or RTCC alarm

- Ultra Low-Power Wake-up (ULPWU)

- Sleep mode: CPU off, Peripherals off, SRAM on, Fast Wake-up, Currents Down to 105 nA Typical

- Idle: CPU off, Peripherals on, Currents Down to 2.3 μA Typical

- Run: CPU on, Peripherals on, Currents Down to 6.2 μA Typical

- Timer1 Oscillator/w RTCC: 1 μA, 32 kHz Typical

- Watchdog Timer: 813 nA, 2V Typical

#### **Special Microcontroller Features:**

- 5.5V Tolerant Inputs (digital only pins)

- · Low-Power, High-Speed CMOS Flash Technology

- C Compiler Optimized Architecture for Re-Entrant Code

- · Priority Levels for Interrupts

- Self-Programmable under Software Control

- 8 x 8 Single-Cycle Hardware Multiplier

- Extended Watchdog Timer (WDT):

- Programmable period from 4 ms to 131s

- Single-Supply In-Circuit Serial Programming™ (ICSP™) via Two Pins

- In-Circuit Debug (ICD) with Three Breakpoints via Two Pins

- Operating Voltage Range of 2.0V to 3.6V

- On-Chip 2.5V Regulator

- Flash Program Memory of 10,000 Erase/Write Cycles Minimum and 20-Year Data Retention

### **Peripheral Highlights:**

- Peripheral Pin Select:

- Allows independent I/O mapping of many peripherals

- Continuous hardware integrity checking and safety interlocks prevent unintentional configuration changes

- · Hardware Real-Time Clock and Calendar (RTCC):

- Provides clock, calendar and alarm functions

- High-Current Sink/Source 25 mA/25 mA (PORTB and PORTC)

#### Peripheral Highlights (Continued):

- · Four Programmable External Interrupts

- Four Input Change Interrupts

- Two Enhanced Capture/Compare/PWM (ECCP) modules:

- One, two or four PWM outputs

- Selectable polarity

- Programmable dead time

- Auto-shutdown and auto-restart

- Pulse steering control

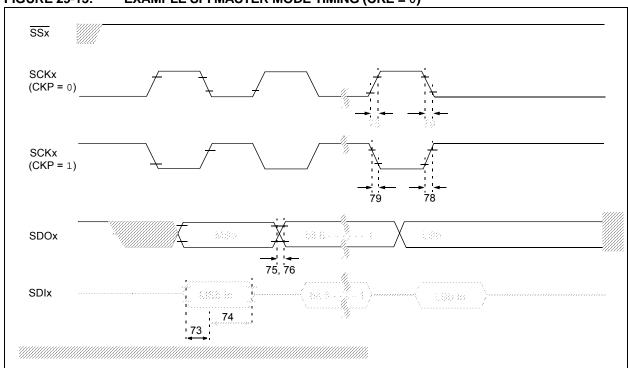

- Two Master Synchronous Serial Port (MSSP) modules featuring:

- 3-wire SPI (all 4 modes)

- 1024-byte SPI Direct Memory Access (DMA) channel

- I<sup>2</sup>C<sup>™</sup> Master and Slave modes

- 8-Bit Parallel Master Port/Enhanced Parallel Slave Port

- Two-Rail Rail Analog Comparators with Input Multiplexing

- 10-Bit, up to 13-Channel Analog-to-Digital (A/D) Converter module:

- Auto-acquisition capability

- Conversion available during Sleep

- Self-Calibration

- High/Low-Voltage Detect module

- Charge Time Measurement Unit (CTMU):

- Supports capacitive touch sensing for touch screens and capacitive switches

- Provides a Precise Resolution Time Measurement for Both Flow Measurement and Simple Temperature Sensing

- Two Enhanced USART modules:

- Supports RS-485, RS-232 and LIN/J2602

- Auto-wake-up on Start bit

- Auto-Baud Detect

#### **Flexible Oscillator Structure:**

- 1% Accurate High-Precision Internal Oscillator

- Two External Clock modes, up to 48 MHz (12 MIPS)

- · Low-Power 31 kHz Internal RC Oscillator

- Tunable Internal Oscillator (31 kHz to 8 MHz, ±0.15% Typical, ±1% Max).

- 4x PLL Option

- Secondary Oscillator using Timer1 @ 32 kHz

- Fail-Safe Clock Monitor:

- Allows for safe shutdown if any clock stops

- Two-Speed Oscillator Start-up

- Programmable Reference Clock Output Generator

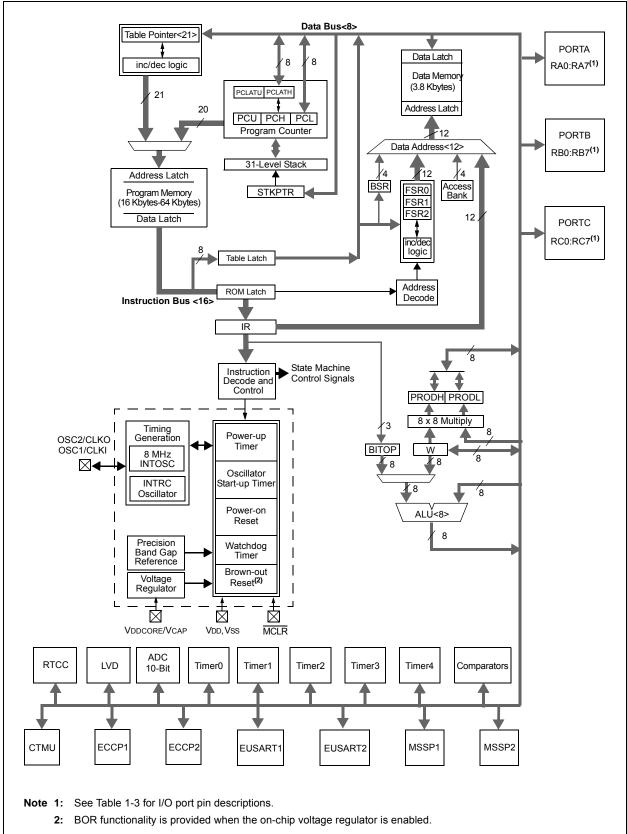

FIGURE 1-1: PIC18F2XJ11 (28-PIN) BLOCK DIAGRAM

| R/W-0         | U-0                                          | R/W-1                                                                                                                                                      | R/W-1                       | R-1               | R-1               | R/W-0             | R/W-0         |  |

|---------------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-------------------|-------------------|-------------------|---------------|--|

| IPEN          | _                                            | CM                                                                                                                                                         | RI                          | TO                | PD                | POR               | BOR           |  |

| bit 7         |                                              |                                                                                                                                                            |                             |                   |                   |                   | bit (         |  |

|               |                                              |                                                                                                                                                            |                             |                   |                   |                   |               |  |

| Legend:       |                                              |                                                                                                                                                            |                             |                   |                   |                   |               |  |

| R = Reada     |                                              | W = Writable                                                                                                                                               |                             | -                 | mented bit, rea   |                   |               |  |

| -n = Value    | at POR                                       | '1' = Bit is se                                                                                                                                            | t                           | '0' = Bit is cle  | eared             | x = Bit is unkr   | IOWN          |  |

| bit 7         | IPEN: Intern                                 | upt Priority Ena                                                                                                                                           | hle hit                     |                   |                   |                   |               |  |

|               |                                              | priority levels of                                                                                                                                         |                             |                   |                   |                   |               |  |

|               |                                              | priority levels o                                                                                                                                          |                             | PIC16CXXX Co      | ompatibility mo   | de)               |               |  |

| bit 6         | Unimpleme                                    | nted: Read as                                                                                                                                              | '0'                         |                   |                   |                   |               |  |

| bit 5         | CM: Configu                                  | ration Mismatc                                                                                                                                             | h Flag bit                  |                   |                   |                   |               |  |

|               |                                              | guration Misma                                                                                                                                             |                             |                   |                   |                   |               |  |

|               |                                              | guration Misma                                                                                                                                             |                             | is occurred (m    | lust be set in s  | software after a  | Configuratio  |  |

| bit 4         |                                              | nstruction Flag                                                                                                                                            |                             |                   |                   |                   |               |  |

|               |                                              | SET instruction                                                                                                                                            |                             | uted (set by firr | nware onlv)       |                   |               |  |

|               | 0 = The RE                                   | SET instruction                                                                                                                                            | was execute                 |                   |                   | iust be set in so | oftware after |  |

| <b>h</b> :+ 0 |                                              | out Reset occur                                                                                                                                            | ,                           |                   |                   |                   |               |  |

| bit 3         |                                              | og Time-out Fla<br>bower-up, CLRW                                                                                                                          | •                           | or GIEED inct     | ruction           |                   |               |  |

|               | • •                                          | time-out occurr                                                                                                                                            |                             | OI SLEEP IIISI    | ruction           |                   |               |  |

| bit 2         | PD: Power-[                                  | Down Detection                                                                                                                                             | Flag bit                    |                   |                   |                   |               |  |

|               | 1 = Set by p                                 | ower-up or by                                                                                                                                              | the CLRWDT in               | struction         |                   |                   |               |  |

|               | 0 = Set by e                                 | execution of the                                                                                                                                           | SLEEP instru                | ction             |                   |                   |               |  |

| bit 1         |                                              | -on Reset Statu                                                                                                                                            |                             |                   |                   |                   |               |  |

|               |                                              | r-on Reset has                                                                                                                                             |                             |                   |                   | r-on Reset occu   | re)           |  |

| bit 0         |                                              | n-out Reset Stat                                                                                                                                           |                             | e sel in sollwar  |                   | I-OII Resel Occu  | 15)           |  |

| DILO          |                                              | n-out Reset ha                                                                                                                                             |                             | l (set by firmwa  | are only)         |                   |               |  |

|               |                                              |                                                                                                                                                            |                             |                   | • •               | n-out Reset occ   | curs)         |  |

|               |                                              |                                                                                                                                                            |                             |                   |                   |                   |               |  |

| Note 1:       | It is recommende<br>Power-on Reset           |                                                                                                                                                            |                             | er a Power-on I   | Reset has beer    | detected, so the  | at subsequen  |  |

| 2:            | If the on-chip vo<br><b>BOR</b> " for more i |                                                                                                                                                            | is disabled, $\overline{B}$ | OR remains '0     | ' at all times. S | See Section 5.4   | 1 "Detecting  |  |

| 3:            |                                              | Brown-out Reset is said to have occurred when BOR is '0' and POR is '1' (assuming that POR was set to '1' by software immediately after a Power-on Reset). |                             |                   |                   |                   |               |  |

#### REGISTER 5-1: RCON: RESET CONTROL REGISTER (ACCESS FD0h)

#### 6.2 PIC18 Instruction Cycle

#### 6.2.1 CLOCKING SCHEME

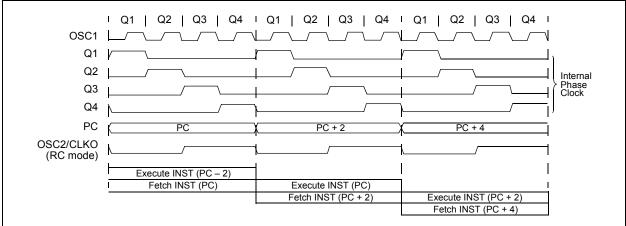

The microcontroller clock input, whether from an internal or external source, is internally divided by '4' to generate four non-overlapping quadrature clocks (Q1, Q2, Q3 and Q4). Internally, the PC is incremented on every Q1; the instruction is fetched from the program memory and latched into the Instruction Register (IR) during Q4. The instruction is decoded and executed during the following Q1 through Q4. Figure 6-4 illustrates the clocks and instruction execution flow.

#### 6.2.2 INSTRUCTION FLOW/PIPELINING

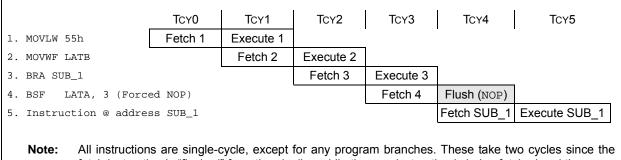

An "Instruction Cycle" consists of four Q cycles, Q1 through Q4. The instruction fetch and execute are pipelined in such a manner that a fetch takes one instruction cycle, while the decode and execute take another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the PC to change (e.g., GOTO), then two cycles are required to complete the instruction (Example 6-3).

A fetch cycle begins with the PC incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the IR in cycle Q1. This instruction is then decoded and executed during the Q2, Q3 and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

#### EXAMPLE 6-3: INSTRUCTION PIPELINE FLOW

**Note:** All instructions are single-cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline while the new instruction is being fetched and then executed.

#### FIGURE 6-4: CLOCK/INSTRUCTION CYCLE

| TABLE 10-9: PORTD I/O SUMMARY |          |                 |                            |                          |                                                                                                 |  |

|-------------------------------|----------|-----------------|----------------------------|--------------------------|-------------------------------------------------------------------------------------------------|--|

| Pin                           | Function | TRIS<br>Setting | I/O                        | l/O<br>Type              | Description                                                                                     |  |

| RD0/PMD0/                     | RD0      | 1               | I                          | ST                       | PORTD<0> data input.                                                                            |  |

| SCL2                          |          | 0               | 0                          | DIG                      | LATD<0> data output.                                                                            |  |

|                               | PMD0     | 1               | Ι                          | ST/TTL                   |                                                                                                 |  |

|                               |          | 0               | 0                          | DIG                      | Parallel Master Port data out.                                                                  |  |

|                               | SCL2     | 1               | I                          | I <sup>2</sup> C/<br>SMB | I <sup>2</sup> C <sup>™</sup> clock input (MSSP2 module); input type depends on module setting. |  |

|                               |          | 0               | 0                          | DIG                      | I <sup>2</sup> C <sup>™</sup> clock output (MSSP2 module); takes priority over port data.       |  |

| RD1/PMD1/                     | RD1      | 1               | I                          | ST                       | PORTD<1> data input.                                                                            |  |

| SDA2                          |          | 0               | 0                          | DIG                      | LATD<1> data output.                                                                            |  |

|                               | PMD1     | 1               | Ι                          | ST/TTL                   | Parallel Master Port data in.                                                                   |  |

|                               |          | 0               | 0                          | DIG                      | Parallel Master Port data out.                                                                  |  |

|                               | SDA2     | 1               | Ι                          | I <sup>2</sup> C/<br>SMB | I <sup>2</sup> C data input (MSSP2 module); input type depends on module setting.               |  |

|                               |          | 0               | 0                          | DIG                      | I <sup>2</sup> C data output (MSSP2 module); takes priority over port data.                     |  |

| RD2/PMD2/                     | RD2      | 1               | Ι                          | ST                       | PORTD<2> data input.                                                                            |  |

| RP19                          |          | 0               | O DIG LATD<2> data output. |                          | LATD<2> data output.                                                                            |  |

| PMD2                          |          | 1               | Ι                          | ST/TTL                   | Parallel Master Port data in.                                                                   |  |

|                               |          | 0               | 0                          | DIG                      | Parallel Master Port data out.                                                                  |  |

|                               | RP19     | 1               | Ι                          | ST                       | Remappable peripheral pin 19 input.                                                             |  |

|                               |          | 0               | 0                          | DIG                      | Remappable peripheral pin 19 output.                                                            |  |

| RD3/PMD3/                     | RD3      | 1               | Ι                          | DIG                      | PORTD<3> data input.                                                                            |  |

| RP20                          |          | 0               | 0                          | DIG                      | LATD<3> data output.                                                                            |  |

|                               | PMD3     | 1               | Ι                          | ST/TTL                   | Parallel Master Port data in.                                                                   |  |

|                               |          | 0               | 0                          | DIG                      | Parallel Master Port data out.                                                                  |  |

|                               | RP20     | 1               | Ι                          | ST                       | Remappable peripheral pin 20 input.                                                             |  |

|                               |          | 0               | 0                          | DIG                      | Remappable peripheral pin 20 output.                                                            |  |

| RD4/PMD4/                     | RD4      | 1               | Ι                          | ST                       | PORTD<4> data input.                                                                            |  |

| RP21                          |          | 0               | 0                          | DIG                      | LATD<4> data output.                                                                            |  |

|                               | PMD4     | 1               | Ι                          | ST/TTL                   | Parallel Master Port data in.                                                                   |  |

|                               |          | 0               | 0                          | DIG                      | Parallel Master Port data out.                                                                  |  |

|                               | RP21     | 1               | Ι                          | ST                       | Remappable peripheral pin 21 input.                                                             |  |

|                               |          | 0               | 0                          | DIG                      | Remappable peripheral pin 21 output.                                                            |  |

| RD5/PMD5/                     | RD5      | 1               | Ι                          | ST                       | PORTD<5> data input.                                                                            |  |

| RP22                          |          | 0               | 0                          | DIG                      | LATD<5> data output.                                                                            |  |

|                               | PMD5     | 1               | I                          | ST/TTL                   | Parallel Master Port data in.                                                                   |  |

|                               |          | 0               | 0                          | DIG                      | Parallel Master Port data out.                                                                  |  |

|                               | RP22     | 1               | Ι                          | ST                       | Remappable peripheral pin 22 input.                                                             |  |

|                               |          | 0               | 0                          | DIG                      | Remappable peripheral pin 22 output.                                                            |  |

#### TABLE 10-9: PORTD I/O SUMMARY

0

0

DIG

Remappable peripheral pin 22 output.

Legend:

DIG = Digital level output; TTL = TTL input buffer; ST = Schmitt Trigger input buffer; I<sup>2</sup>C/SMB = I<sup>2</sup>C/SMBus input buffer; x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

Choosing the configuration requires the review of all PPSs and their pin assignments, especially those that will not be used in the application. In all cases, unused pin selectable peripherals should be disabled completely. Unused peripherals should have their inputs assigned to an unused RPn pin function. I/O pins with unused RPn functions should be configured with the null peripheral output.

The assignment of a peripheral to a particular pin does not automatically perform any other configuration of the pin's I/O circuitry. In theory, this means adding a pin selectable output to a pin may mean inadvertently driving an existing peripheral input when the output is driven. Users must be familiar with the behavior of other fixed peripherals that share a remappable pin and know when to enable or disable them. To be safe, fixed digital peripherals that share the same pin should be disabled when not in use.

Along these lines, configuring a remappable pin for a specific peripheral does not automatically turn that feature on. The peripheral must be specifically configured for operation and enabled, as if it were tied to a fixed pin. Where this happens in the application code (immediately following device Reset and peripheral configuration or inside the main application routine) depends on the peripheral and its use in the application.

A final consideration is that the PPS functions neither override analog inputs nor reconfigure pins with analog functions for digital I/O. If a pin is configured as an analog input on device Reset, it must be explicitly reconfigured as digital I/O when used with a PPS.

Example 10-7 provides a configuration for bidirectional communication with flow control using EUSART2. The following input and output functions are used:

- Input Function RX2

- Output Function TX2

#### EXAMPLE 10-7: CONFIGURING EUSART2 INPUT AND OUTPUT FUNCTIONS

```

;*******

; Unlock Registers

; PPS registers are in BANK 14

MOVLB

0 \times 0 E

BCF

INTCON, GIE ; Disable interrupts

MOVLW

0x55

MOVWF

EECON2, 0

MOVLW

0xAA

MOVWF

EECON2, 0

; Turn off PPS Write Protect

PPSCON, IOLOCK, BANKED

BCF

********

; Configure Input Functions

; (See Table 9-13)

;************************

; Assign RX2 To Pin RP0

MOVLW

0x00

MOVWF

RPINR16, BANKED

********

; Configure Output Functions

; (See Table 9-14)

; Assign TX2 To Pin RP1

MOVLW

0 \times 05

MOVWF

RPOR1, BANKED

; Lock Registers

MOVLW

0x55

MOVWF

EECON2. 0

MOVLW

0xAA

MOVWF

EECON2, 0

; Write Protect PPS

BSF PPSCON, IOLOCK, BANKED

```

Note: If the Configuration bit, IOL1WAY = 1, once the IOLOCK bit is set, it cannot be cleared, preventing any future RP register changes. The IOLOCK bit is cleared back to '0' on any device Reset.

| REGISTER 10-6: | <b>RPINR1: PERIPHERAL</b> | <b>PIN SELECT INPUT</b> | <b>REGISTER 1</b> | (BANKED EE7h) |

|----------------|---------------------------|-------------------------|-------------------|---------------|

|----------------|---------------------------|-------------------------|-------------------|---------------|

| U-0   | U-0 | U-0 | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   |

|-------|-----|-----|---------|---------|---------|---------|---------|

| —     | —   | —   | INTR1R4 | INTR1R3 | INTR1R2 | INTR1R1 | INTR1R0 |

| bit 7 |     |     |         |         |         |         | bit 0   |

| Legend:           | R/W = Readable, Writable | $R/\overline{W}$ = Readable, Writable if IOLOCK = 0 |                    |  |  |  |  |

|-------------------|--------------------------|-----------------------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit         | U = Unimplemented bit, read as '0'                  |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set         | '0' = Bit is cleared                                | x = Bit is unknown |  |  |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 INTR1R<4:0>: Assign External Interrupt 1 (INT1) to the Corresponding RPn Pin bits

#### REGISTER 10-7: RPINR2: PERIPHERAL PIN SELECT INPUT REGISTER 2 (BANKED EE8h)

| U-0   | U-0 | U-0 | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   |

|-------|-----|-----|---------|---------|---------|---------|---------|

| —     | —   | —   | INTR2R4 | INTR2R3 | INTR2R2 | INTR2R1 | INTR2R0 |

| bit 7 |     |     |         |         |         |         | bit 0   |

| Legend:           | $R/\overline{W}$ = Readable, Writable if IOLOCK = 0 |                                    |                    |  |  |  |

|-------------------|-----------------------------------------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit                                    | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 INTR2R<4:0>: Assign External Interrupt 2 (INT2) to the Corresponding RPn pin bits

#### REGISTER 10-8: RPINR3: PERIPHERAL PIN SELECT INPUT REGISTER 3 (BANKED EE9h)

| U-0   | U-0 | U-0 | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   |

|-------|-----|-----|---------|---------|---------|---------|---------|

| —     | —   | —   | INTR3R4 | INTR3R3 | INTR3R2 | INTR3R1 | INTR3R0 |

| bit 7 |     |     |         |         |         |         | bit 0   |

| Legend:           | $R/\overline{W}$ = Readable, Writable if IOLOCK = 0 |                                    |                    |  |  |  |

|-------------------|-----------------------------------------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit                                    | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 INTR3R<4:0>: Assign External Interrupt 3 (INT3) to the Corresponding RPn Pin bits

#### REGISTER 10-15: RPINR16: PERIPHERAL PIN SELECT INPUT REGISTER 16 (BANKED EF6h)

| U-0   | U-0 | U-0 | R/W-1    | R/W-1    | R/W-1    | R/W-1    | R/W-1    |

|-------|-----|-----|----------|----------|----------|----------|----------|

| —     |     | _   | RX2DT2R4 | RX2DT2R3 | RX2DT2R2 | RX2DT2R1 | RX2DT2R0 |

| bit 7 |     |     |          |          |          |          | bit 0    |

| Legend:           | R/W = Readable, Wri | $R/\overline{W}$ = Readable, Writable if IOLOCK = 0 |                                    |  |  |  |  |

|-------------------|---------------------|-----------------------------------------------------|------------------------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit    | U = Unimplemented bit                               | U = Unimplemented bit, read as '0' |  |  |  |  |

| -n = Value at POR | '1' = Bit is set    | '0' = Bit is cleared                                | x = Bit is unknown                 |  |  |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RX2DT2R<4:0>:** EUSART2 Synchronous/Asynchronous Receive (RX2/DT2) to the Corresponding RPn Pin bits

#### REGISTER 10-16: RPINR17: PERIPHERAL PIN SELECT INPUT REGISTER 17 (BANKED EF7h)

| U-0   | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-----|-------|-------|-------|-------|-------|

| —     | —   |     | CK2R4 | CK2R3 | CK2R2 | CK2R1 | CK2R0 |

| bit 7 |     |     |       |       |       |       | bit 0 |

| Legend:           | $R/\overline{W}$ = Readable, Writable if IOLOCK = 0 |                                    |                    |  |  |

|-------------------|-----------------------------------------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                                    | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 CK2R<4:0>: EUSART2 Clock Input (CK2) to the Corresponding RPn Pin bits

#### REGISTER 10-17: RPINR21: PERIPHERAL PIN SELECT INPUT REGISTER 21 (BANKED EFBh)

| U-0   | U-0 | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|-----|--------|--------|--------|--------|--------|

| —     | —   | —   | SDI2R4 | SDI2R3 | SDI2R2 | SDI2R1 | SDI2R0 |

| bit 7 |     |     |        |        |        |        | bit 0  |

| Legend:           | $R/\overline{W}$ = Readable, Writable if IOLOCK = 0 |                                                   |                    |  |  |

|-------------------|-----------------------------------------------------|---------------------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                                    | = Writable bit U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared                              | x = Bit is unknown |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 SDI2R<4:0>: Assign SPI2 Data Input (SDI2) to the Corresponding RPn Pin bits

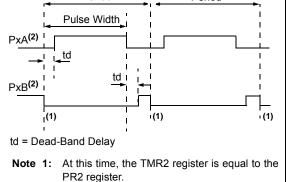

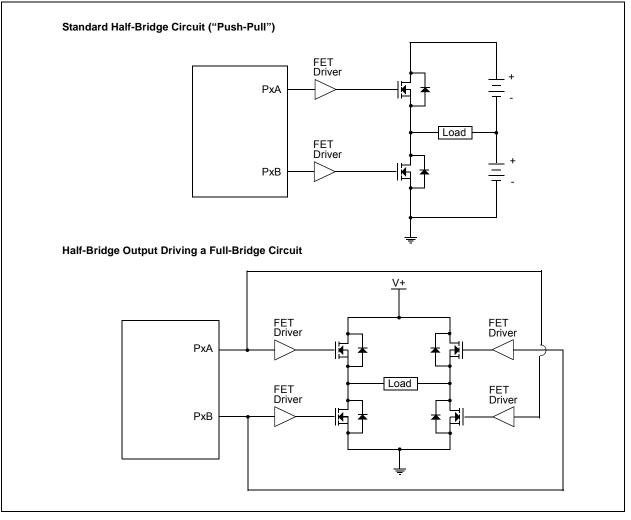

#### 18.5.1 HALF-BRIDGE MODE

In Half-Bridge mode, two pins are used as outputs to drive push-pull loads. The PWM output signal is output on the PxA pin, while the complementary PWM output signal is output on the PxB pin (see Figure 18-8). This mode can be used for half-bridge applications, as shown in Figure 18-9, or for full-bridge applications, where four power switches are being modulated with two PWM signals.

In Half-Bridge mode, the programmable dead-band delay can be used to prevent shoot-through current in half-bridge power devices. The value of the PxDC<6:0> bits of the ECCPxDEL register sets the number of instruction cycles before the output is driven active. If the value is greater than the duty cycle, the corresponding output remains inactive during the entire cycle. See **Section 18.5.6 "Programmable Dead-Band Delay Mode"** for more details of the dead-band delay operations. Since the PxA and PxB outputs are multiplexed with the PORT data latches, the associated TRIS bits must be cleared to configure PxA and PxB as outputs.

**2:** Output signals are shown as active-high.

#### FIGURE 18-9: EXAMPLE OF HALF-BRIDGE APPLICATIONS

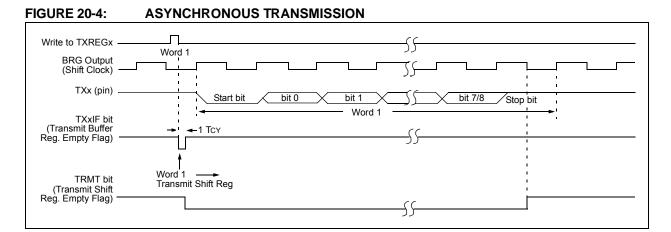

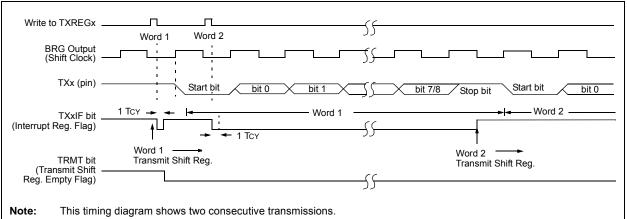

#### FIGURE 20-5: ASYNCHRONOUS TRANSMISSION (BACK-TO-BACK)

#### TABLE 20-5: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Name     | Bit 7                                          | Bit 6       | Bit 5       | Bit 4       | Bit 3  | Bit 2  | Bit 1   | Bit 0  | Reset<br>Values<br>on Page: |

|----------|------------------------------------------------|-------------|-------------|-------------|--------|--------|---------|--------|-----------------------------|

| INTCON   | GIE/GIEH                                       | PEIE/GIEL   | TMR0IE      | INT0IE      | RBIE   | TMR0IF | INT0IF  | RBIF   | 69                          |

| PIR1     | PMPIF <sup>(1)</sup>                           | ADIF        | RC1IF       | TX1IF       | SSP1IF | CCP1IF | TMR2IF  | TMR1IF | 72                          |

| PIE1     | PMPIE <sup>(1)</sup>                           | ADIE        | RC1IE       | TX1IE       | SSP1IE | CCP1IE | TMR2IE  | TMR1IE | 72                          |

| IPR1     | PMPIP <sup>(1)</sup>                           | ADIP        | RC1IP       | TX1IP       | SSP1IP | CCP1IP | TMR2IP  | TMR1IP | 72                          |

| PIR3     | SSP2IF                                         | BCL2IF      | RC2IF       | TX2IF       | TMR4IF | CTMUIF | TMR3GIF | RTCCIF | 72                          |

| PIE3     | SSP2IE                                         | BCL2IE      | RC2IE       | TX2IE       | TMR4IE | CTMUIE | TMR3GIE | RTCCIE | 72                          |

| IPR3     | SSP2IP                                         | BCL2IP      | RC2IP       | TX2IP       | TMR4IP | CTMUIP | TMR3GIP | RTCCIP | 72                          |

| RCSTAx   | SPEN                                           | RX9         | SREN        | CREN        | ADDEN  | FERR   | OERR    | RX9D   | 72                          |

| TXREGx   | EUSARTx                                        | Transmit Re | gister      |             |        |        |         |        | 72                          |

| TXSTAx   | CSRC                                           | TX9         | TXEN        | SYNC        | SENDB  | BRGH   | TRMT    | TX9D   | 72                          |

| BAUDCONx | ABDOVF                                         | RCIDL       | RXDTP       | TXDTP       | BRG16  | —      | WUE     | ABDEN  | 73                          |

| SPBRGHx  | EUSARTx Baud Rate Generator Register High Byte |             |             |             |        |        |         |        | 72                          |

| SPBRGx   | EUSARTx                                        | Baud Rate C | Generator R | egister Low | Byte   |        |         |        | 72                          |

| ODCON2   |                                                | _           |             |             |        |        | U2OD    | U10D   | 74                          |

Legend: -= unimplemented locations read as '0'. Shaded cells are not used for asynchronous transmission.

**Note 1:** These bits are only available on 44-pin devices.

### 21.0 10-BIT ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

The Analog-to-Digital (A/D) Converter module has 10 inputs for the 28-pin devices and 13 for the 44-pin devices. Additionally, two internal channels are available for sampling the VDDCORE and VBG absolute reference voltage. This module allows conversion of an analog input signal to a corresponding 10-bit digital number.

The module has six registers:

A/D Control Register 0 (ADCON0)

- A/D Control Register 1 (ADCON1)

- A/D Port Configuration Register 2 (ANCON0)

- A/D Port Configuration Register 1 (ANCON1)

- A/D Result Registers (ADRESH and ADRESL)

The ADCON0 register, in Register 21-1, controls the operation of the A/D module. The ADCON1 register, in Register 21-2, configures the A/D clock source, programmed acquisition time and justification.

The ANCON0 and ANCON1 registers, in Register 21-3 and Register 21-4, configure the functions of the port pins.

#### REGISTER 21-1: ADCON0: A/D CONTROL REGISTER 0 (ACCESS FC2h)

| R/W-0               | R/W-0                                                                                                                                                                                                                                                      | R/W-0                                          | R/W-0                      | R/W-0               | R/W-0               | R/W-0               | R/W-0            |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|----------------------------|---------------------|---------------------|---------------------|------------------|

| VCFG1               | I VCFG0                                                                                                                                                                                                                                                    | CHS3 <sup>(2)</sup>                            | CHS2 <sup>(2)</sup>        | CHS1 <sup>(2)</sup> | CHS0 <sup>(2)</sup> | GO/DONE             | ADON             |

| bit 7               |                                                                                                                                                                                                                                                            |                                                |                            |                     |                     |                     | bit 0            |

| Legend:             |                                                                                                                                                                                                                                                            |                                                |                            |                     |                     |                     |                  |

| R = Reada           | able bit                                                                                                                                                                                                                                                   | W = Writable b                                 | oit                        | U = Unimpler        | nented bit, read    | 1 as '0'            |                  |

| -n = Value          |                                                                                                                                                                                                                                                            | '1' = Bit is set                               |                            | '0' = Bit is clea   |                     | x = Bit is unkno    | wn               |

|                     |                                                                                                                                                                                                                                                            |                                                |                            |                     |                     |                     |                  |

| bit 7               | <b>VCFG1:</b> Volt<br>1 = VREF- (A<br>0 = AVss <sup>(4)</sup>                                                                                                                                                                                              | age Reference (<br>N2)                         | Configuration I            | bit (VREF- sourc    | e)                  |                     |                  |

| bit 6               | <b>VCFG0:</b> Volt<br>1 = VREF+ (A<br>0 = AVDD <sup>(4)</sup>                                                                                                                                                                                              | age Reference (<br>AN3)                        | Configuration I            | bit (VREF+ sourc    | ce)                 |                     |                  |

| bit 5-2             | 0000 = Char<br>0001 = Char<br>0010 = Char<br>0011 = Char<br>0100 = Char<br>0101 = Char<br>0110 = Char<br>0111 = Char<br>1000 = Char<br>1001 = Char<br>1010 = Char<br>1011 = Char<br>1001 = Char<br>1011 = Char<br>1100 = Char<br>1101 = VDD0<br>1111 = VBG | CORE<br>Absolute Refere                        | nce (~1.2V) <sup>(3)</sup> | )                   |                     |                     |                  |

| bit 1               | When ADON                                                                                                                                                                                                                                                  | version in progre                              |                            |                     |                     |                     |                  |

| bit 0               |                                                                                                                                                                                                                                                            | On bit<br>verter module is<br>verter module is |                            |                     |                     |                     |                  |

| Note 1:<br>2:<br>3: | These channels are<br>Performing a conver<br>For best accuracy, th<br>on this channel.                                                                                                                                                                     | sion on unimplement                            | ed channels will r         |                     | <7>=1) at least 1   | 0 ms before perform | ing a conversion |

4: On 44-pin QFN devices, AVDD and AVSS reference sources are intended to be externally connected to VDD and VSS levels. Other package types tie AVDD and AVSS to VDD and VSS internally.

#### EXAMPLE 25-2: CURRENT CALIBRATION ROUTINE

```

#include <pl8cxxx.h>

#define COUNT 500

//@ 8MHz = 125uS.

#define DELAY for(i=0;i<COUNT;i++)</pre>

#define RCAL .027

//R value is 4200000 (4.2M)

//scaled so that result is in

//1/100th of uA

#define ADSCALE 1023

//for unsigned conversion 10 sig bits

#define ADREF 3.3

//Vdd connected to A/D Vr+

int main(void)

{

int i;

int j = 0;

//index for loop

unsigned int Vread = 0;

double VTot = 0;

//assume CTMU and A/D have been setup correctly

//see Example 25-1 for CTMU & A/D setup

setup();

CTMUCONHbits.CTMUEN = 1;

//Enable the CTMU

CTMUCONLbits.EDG1STAT = 0;

// Set Edge status bits to zero

CTMUCONLbits.EDG2STAT = 0;

for(j=0;j<10;j++)</pre>

{

CTMUCONHbits.IDISSEN = 1;

//drain charge on the circuit

//wait 125us

DELAY;

CTMUCONHbits.IDISSEN = 0;

//end drain of circuit

CTMUCONLbits.EDG1STAT = 1;

//Begin charging the circuit

//using CTMU current source

DELAY;

//wait for 125us

CTMUCONLbits.EDG1STAT = 0;

//Stop charging circuit

PIR1bits.ADIF = 0;

//make sure A/D Int not set

ADCON0bits.GO=1;

//and begin A/D conv.

while(!PIR1bits.ADIF);

//Wait for A/D convert complete

Vread = ADRES;

//Get the value from the A/D

PIR1bits.ADIF = 0;

//Clear A/D Interrupt Flag

VTot += Vread;

//Add the reading to the total

}

Vavg = (float)(VTot/10.000);

//Average of 10 readings

Vcal = (float)(Vavg/ADSCALE*ADREF);

CTMUISrc = Vcal/RCAL;

//CTMUISrc is in 1/100ths of uA

```

#### EXAMPLE 25-3: CAPACITANCE CALIBRATION ROUTINE

```

#include <pl8cxxx.h>

#define COUNT 25

//@ 8MHz INTFRC = 62.5 us.

#define ETIME COUNT*2.5

//time in uS

#define DELAY for(i=0;i<COUNT;i++)</pre>

#define ADSCALE 1023

//for unsigned conversion 10 sig bits

#define ADREF 3.3

//Vdd connected to A/D Vr+

#define RCAL .027

//R value is 4200000 (4.2M)

//scaled so that result is in

//1/100th of uA

int main(void)

{

int i;

int j = 0;

//index for loop

unsigned int Vread = 0;

float CTMUISrc, CTMUCap, Vavg, VTot, Vcal;

//assume CTMU and A/D have been setup correctly

//see Example 25-1 for CTMU & A/D setup

setup();

CTMUCONHbits.CTMUEN = 1;

//Enable the CTMU

CTMUCONLbits.EDG1STAT = 0;

// Set Edge status bits to zero

CTMUCONLbits.EDG2STAT = 0;

for(j=0;j<10;j++)</pre>

{

CTMUCONHbits.IDISSEN = 1;

//drain charge on the circuit

DELAY;

//wait 125us

CTMUCONHbits.IDISSEN = 0;

//end drain of circuit

CTMUCONLbits.EDG1STAT = 1;

//Begin charging the circuit

//using CTMU current source

DELAY;

//wait for 125us

CTMUCONLbits.EDG1STAT = 0;

//Stop charging circuit

PIR1bits.ADIF = 0;

//make sure A/D Int not set

ADCON0bits.GO=1;

//and begin A/D conv.

while(!PIR1bits.ADIF);

//Wait for A/D convert complete

Vread = ADRES;

//Get the value from the A/D

PIR1bits.ADIF = 0;

//Clear A/D Interrupt Flag

VTot += Vread;

//Add the reading to the total

}

Vavg = (float)(VTot/10.000);

//Average of 10 readings

Vcal = (float)(Vavg/ADSCALE*ADREF);

CTMUISrc = Vcal/RCAL;

//CTMUISrc is in 1/100ths of uA

CTMUCap = (CTMUISrc*ETIME/Vcal)/100;

}

```

#### 25.9 Registers

There are three control registers for the CTMU:

- CTMUCONH

- CTMUCONL

- CTMUICON

The CTMUCONH and CTMUCONL registers (Register 25-1 and Register 25-2) contain control bits for configuring the CTMU module edge source selection, edge source polarity selection, edge sequencing, A/D trigger, analog circuit capacitor discharge and enables. The CTMUICON register (Register 25-3) has bits for selecting the current source range and current source trim.

#### REGISTER 25-1: CTMUCONH: CTMU CONTROL REGISTER HIGH (ACCESS FB3h)

| R/W-0  | U-0 | R/W-0    | R/W-0 | R/W-0 | R/W-0    | R/W-0   | U-0   |

|--------|-----|----------|-------|-------|----------|---------|-------|

| CTMUEN | —   | CTMUSIDL | TGEN  | EDGEN | EDGSEQEN | IDISSEN | —     |

| bit 7  |     |          |       |       |          |         | bit 0 |

|        |     |          |       |       |          |         |       |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7 | CTMUEN: CTMU Enable bit                                                                                                            |

|-------|------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul><li>1 = Module is enabled</li><li>0 = Module is disabled</li></ul>                                                             |

| bit 6 | Unimplemented: Read as '0'                                                                                                         |

| bit 5 | CTMUSIDL: Stop in Idle Mode bit                                                                                                    |

|       | <ul><li>1 = Discontinue module operation when device enters Idle mode</li><li>0 = Continue module operation in Idle mode</li></ul> |

| bit 4 | TGEN: Time Generation Enable bit                                                                                                   |

|       | <ul><li>1 = Enables edge delay generation</li><li>0 = Disables edge delay generation</li></ul>                                     |

| bit 3 | EDGEN: Edge Enable bit                                                                                                             |

|       | 1 = Edges are not blocked<br>0 = Edges are blocked                                                                                 |

| bit 2 | EDGSEQEN: Edge Sequence Enable bit                                                                                                 |

|       | <ul><li>1 = Edge 1 event must occur before Edge 2 event can occur</li><li>0 = No edge sequence is needed</li></ul>                 |

| bit 1 | IDISSEN: Analog Current Source Control bit                                                                                         |

|       | <ul><li>1 = Analog current source output is grounded</li><li>0 = Analog current source output is not grounded</li></ul>            |

| bit 0 | Reserved: Write as '0'                                                                                                             |

|       |                                                                                                                                    |

#### REGISTER 26-3: CONFIG2L: CONFIGURATION REGISTER 2 LOW (BYTE ADDRESS 300002h)

| R/WO-1          | R/WO-1                    | U-0                                                 | R/WO-1           | R/WO-1           | R/WO-1           | R/WO-1          | R/WO-1         |  |  |

|-----------------|---------------------------|-----------------------------------------------------|------------------|------------------|------------------|-----------------|----------------|--|--|

| IESO            | FCMEN                     | _                                                   | LPT10SC          | T1DIG            | FOSC2            | FOSC1           | FOSC0          |  |  |

| bit 7           | •                         |                                                     |                  |                  |                  |                 | bit (          |  |  |

| <u> </u>        |                           |                                                     |                  |                  |                  |                 |                |  |  |

| Legend:         |                           |                                                     |                  |                  |                  |                 |                |  |  |

| R = Readable    |                           | WO = Write-C                                        |                  | •                | mented bit, read |                 |                |  |  |

| -n = Value at I | Reset                     | '1' = Bit is set                                    |                  | '0' = Bit is cle | ared             | x = Bit is unkr | nown           |  |  |

| bit 7           |                           | peed Start-up (                                     | Intornal/Extor   | aal Oacillator S | witchovor) Cor   | stral hit       |                |  |  |

| JIL 7           |                           | ed Start-up (                                       |                  |                  | switchover) Cor  |                 |                |  |  |

|                 |                           | ed Start-up ena                                     |                  |                  |                  |                 |                |  |  |

| bit 6           | FCMEN: Fail               | -Safe Clock Mc                                      | nitor Enable b   | bit              |                  |                 |                |  |  |

|                 | 1 = Fail-Safe             | Clock Monitor                                       | enabled          |                  |                  |                 |                |  |  |

|                 | 0 = Fail-Safe             | Clock Monitor                                       | disabled         |                  |                  |                 |                |  |  |

| bit 5           | Unimplemen                | ted: Read as '                                      | כ'               |                  |                  |                 |                |  |  |

| bit 4           |                           | ow-Power Time                                       |                  |                  |                  |                 |                |  |  |

|                 |                           | scillator configu<br>scillator configu              | • •              | •                | 1                |                 |                |  |  |

| bit 3           | T1DIG: Seco               | DIG: Secondary Clock Source T1OSCEN Enforcement bit |                  |                  |                  |                 |                |  |  |

|                 |                           | ary oscillator cl<br>N (T1CON<3>                    |                  | ay be selecte    | d (OSCCON<1      | :0> = 01) reg   | ardless of the |  |  |

|                 |                           | ary oscillator clo                                  |                  | y not be select  | ed unless T1C    | ON<3> = 1       |                |  |  |

| bit 2-0         | FOSC<2:0>:                | Oscillator Sele                                     | ction bits       |                  |                  |                 |                |  |  |

|                 |                           | L oscillator with                                   |                  | e controlled, Cl | KO on RA6        |                 |                |  |  |

|                 |                           | cillator with CL                                    |                  |                  |                  |                 |                |  |  |

|                 | 101 = HSPL<br>100 = HS os | L oscillator with<br>cillator                       | PLL SOTTWARE     | e controlled     |                  |                 |                |  |  |

|                 |                           | SCPLLO, intern                                      | al oscillator w  | ith PLL softwa   | re controlled, C | LKO on RA6, p   | ort function o |  |  |

|                 |                           | SCPLL, interna                                      |                  |                  |                  |                 |                |  |  |

|                 |                           | SCO internal os                                     |                  | •                | ,                |                 |                |  |  |

|                 | 000 = INTOS               | SC internal osc                                     | liator block (IN | NIRC/INTOSC      | ), port function | on RA6 and R    | 47             |  |  |

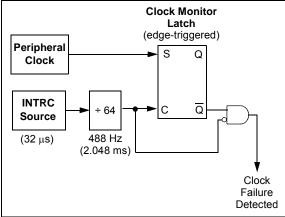

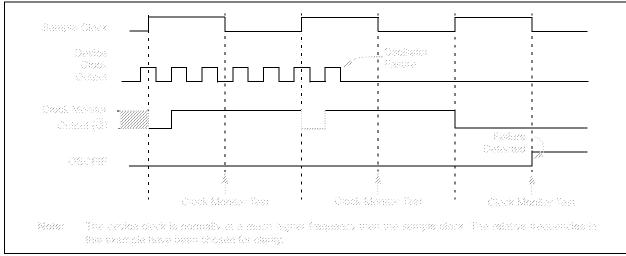

#### FIGURE 26-4: FSCM BLOCK DIAGRAM

Clock failure is tested for on the falling edge of the sample clock. If a sample clock falling edge occurs while the clock monitor is still set, and a clock failure has been detected (Figure 26-5), the following results:

- The FSCM generates an oscillator fail interrupt by setting bit, OSCFIF (PIR2<7>);

- The device clock source is switched to the internal oscillator block (OSCCON is not updated to show the current clock source – this is the Fail-safe condition); and

- The WDT is reset.

During switchover, the postscaler frequency from the internal oscillator block may not be sufficiently stable for timing-sensitive applications. In these cases, it may be desirable to select another clock configuration and enter an alternate power-managed mode. This can be done to attempt a partial recovery or execute a controlled shutdown. See Section 4.1.4 "Multiple Sleep Commands" and Section 26.4.1 "Special Considerations for Using Two-Speed Start-up" for more details.

The FSCM will detect failures of the primary or secondary clock sources only. If the internal oscillator block fails, no failure would be detected, nor would any action be possible.

#### 26.5.1 FSCM AND THE WATCHDOG TIMER

Both the FSCM and the WDT are clocked by the INTRC oscillator. Since the WDT operates with a separate divider and counter, disabling the WDT has no effect on the operation of the INTRC oscillator when the FSCM is enabled.

As already noted, the clock source is switched to the INTRC clock when a clock failure is detected; this may mean a substantial change in the speed of code execution. If the WDT is enabled with a small prescale value, a decrease in clock speed allows a WDT time-out to occur and a subsequent device Reset. For this reason, Fail-Safe Clock Monitor events also reset the WDT and postscaler, allowing it to start timing from when execution speed was changed and decreasing the likelihood of an erroneous time-out.

#### FIGURE 26-5: FSCM TIMING DIAGRAM

| COMF                    | Compleme                        | ent f                                                                                |                                 | CPF         | SEQ             | Compare f                    | with W, Skip                                                                | if f = W                     |

|-------------------------|---------------------------------|--------------------------------------------------------------------------------------|---------------------------------|-------------|-----------------|------------------------------|-----------------------------------------------------------------------------|------------------------------|

| Syntax:                 | COMF f                          | {,d {,a}}                                                                            |                                 | Synta       | ax:             | CPFSEQ                       | f {,a}                                                                      |                              |

| Operands:               | 0 ≤ f ≤ 255                     |                                                                                      |                                 | Oper        | ands:           | $0 \leq f \leq 255$          |                                                                             |                              |

| oporaniaon              | d ∈ [0,1]                       |                                                                                      |                                 |             |                 | a ∈ [0,1]                    |                                                                             |                              |

|                         | a ∈ [0,1]                       |                                                                                      |                                 | Oper        | ation:          | (f) – (W),                   |                                                                             |                              |

| Operation:              | $\overline{f} \rightarrow dest$ |                                                                                      |                                 |             |                 | skip if (f) =<br>(unsigned c | (W)<br>comparison)                                                          |                              |

| Status Affected:        | N, Z                            |                                                                                      |                                 | Statu       | s Affected:     | None                         | • /                                                                         |                              |

| Encoding:               | 0001                            | 11da ff:                                                                             | ff ffff                         | Enco        |                 | 0110                         | 001a fff                                                                    | f ffff                       |

| Description:            | complemer<br>stored in W        | nts of register "<br>nted. If 'd' is '0<br>/. If 'd' is '1', th<br>k in register 'f' | ', the result is<br>e result is |             | ription:        | Compares to ory location     | f to the contents of<br>f to the contents<br>an unsigned s                  | f data mem-<br>ents of W by  |

|                         | lf 'a' is '0', t                | he Access Bar<br>he BSR is use                                                       | nk is selected.                 |             |                 | discarded a                  | en the fetched<br>ind a NOP is ex<br>king this a two                        | xecuted                      |

|                         | set is enabl<br>in Indexed      | Ind the extend<br>led, this instruct<br>Literal Offset                               | ction operates<br>Addressing    |             |                 |                              | ne Access Bar<br>ne BSR is useo<br>(default).                               |                              |

|                         | Section 27<br>Bit-Oriente       | never f ≤ 95 (5<br>7.2.3 "Byte-Or<br>ed Instruction<br>set Mode" for                 | iented and<br>s in Indexed      |             |                 | set is enabl<br>in Indexed   | nd the extended, this instruct<br>Literal Offset A<br>vever f $\leq$ 95 (5) | ction operates<br>Addressing |

| Words:                  | 1                               |                                                                                      |                                 |             |                 |                              | .2.3 "Byte-Or                                                               |                              |

| Cycles:                 | 1                               |                                                                                      |                                 |             |                 | Bit-Oriente                  | ed Instruction<br>set Mode" for                                             | s in Indexed                 |

| Q Cycle Activity:       |                                 |                                                                                      |                                 | Word        | e.              | 1                            |                                                                             | detailo.                     |

| Q1                      | Q2                              | Q3                                                                                   | Q4                              | Cycle       |                 | 1(2)                         |                                                                             |                              |

| Decode                  | Read<br>register 'f'            | Process<br>Data                                                                      | Write to destination            | Cycle       |                 | Note: 3 cy                   | cles if skip and<br>2-word instrue                                          |                              |

|                         |                                 |                                                                                      |                                 | QC          | ycle Activity:  | ,                            |                                                                             |                              |

| Example:                | COMF                            | REG, 0, 0                                                                            |                                 |             | Q1              | Q2                           | Q3                                                                          | Q4                           |

| Before Instruc          |                                 |                                                                                      |                                 |             | Decode          | Read                         | Process                                                                     | No                           |

| REG<br>After Instructio | = 13h                           |                                                                                      |                                 |             |                 | register 'f'                 | Data                                                                        | operation                    |

| REG                     | = 13h                           |                                                                                      |                                 | lf sk       | •               |                              |                                                                             |                              |

| W                       | = ECh                           |                                                                                      |                                 |             | Q1              | Q2                           | Q3                                                                          | Q4                           |

|                         |                                 |                                                                                      |                                 |             | No<br>operation | No<br>operation              | No<br>operation                                                             | No<br>operation              |

|                         |                                 |                                                                                      |                                 | lfsk        |                 | d by 2-word in               |                                                                             | operation                    |

|                         |                                 |                                                                                      |                                 | 1 30        | Q1              | Q2                           | Q3                                                                          | Q4                           |

|                         |                                 |                                                                                      |                                 |             | No              | No                           | No                                                                          | No                           |

|                         |                                 |                                                                                      |                                 |             | operation       | operation                    | operation                                                                   | operation                    |

|                         |                                 |                                                                                      |                                 |             | No              | No                           | No                                                                          | No                           |

|                         |                                 |                                                                                      |                                 |             | operation       | operation                    | operation                                                                   | operation                    |

|                         |                                 |                                                                                      |                                 | <u>Exan</u> | <u>nple:</u>    | HERE<br>NEQUAL<br>EQUAL      | CPFSEQ REG<br>:<br>:                                                        | B, O                         |

|                         |                                 |                                                                                      |                                 |             | Before Instruc  |                              |                                                                             |                              |

|                         |                                 |                                                                                      |                                 |             | PC Addr         |                              | RE                                                                          |                              |

| Before Instruction<br>PC Address<br>W<br>REG | =<br>=<br>= | HERE<br>?<br>? |          |

|----------------------------------------------|-------------|----------------|----------|

| After Instruction                            |             |                |          |

| If REG                                       | =           | W;             |          |

| PC                                           | =           | Address        | (EQUAL)  |

| If REG                                       | ≠           | W;             |          |

| PC                                           | =           | Address        | (NEQUAL) |

|                                              |             |                |          |

| XORWF              | Exclusive OR W with f                                                                                                                                                                                                                                                                |                   |    |                       |  |  |