Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 48MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 16                                                                          |

| Program Memory Size        | 16KB (8K x 16)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 3.8K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.15V ~ 3.6V                                                                |

| Data Converters            | A/D 10x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 28-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f24j11t-i-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Features                             | PIC18F24J11                                                                     | PIC18F25J11              | PIC18F26J11      |  |  |

|--------------------------------------|---------------------------------------------------------------------------------|--------------------------|------------------|--|--|

| Operating Frequency                  | DC – 48 MHz                                                                     | DC – 48 MHz              | DC – 48 MHz      |  |  |

| Program Memory (Bytes)               | 16K                                                                             | 32K                      | 64K              |  |  |

| Program Memory (Instructions)        | 8,192                                                                           | 16,384                   | 32,768           |  |  |

| Data Memory (Bytes)                  | 3.8K                                                                            | 3.8K                     | 3.8K             |  |  |

| Interrupt Sources                    |                                                                                 | 30                       | ·                |  |  |

| I/O Ports                            | Ports A, B, C                                                                   |                          |                  |  |  |

| Timers                               | 5                                                                               |                          |                  |  |  |

| Enhanced Capture/Compare/PWM Modules |                                                                                 | 2                        |                  |  |  |

| Serial Communications                | MS                                                                              | SP (2), Enhanced USAR    | T (2)            |  |  |

| Parallel Communications (PMP/PSP)    |                                                                                 | No                       |                  |  |  |

| 10-Bit Analog-to-Digital Module      |                                                                                 | 10 Input Channels        |                  |  |  |

| Resets (and Delays)                  | POR, BOR, RESET Instruction, Stack Full, Stack Underflow, MCLR, WDT (PWRT, OST) |                          |                  |  |  |

| Instruction Set                      | 75 Instructions,                                                                | 83 with Extended Instruc | tion Set Enabled |  |  |

| Packages                             | 28-Pin QFN                                                                      | I, SOIC, SSOP and SPE    | 0IP (300 mil)    |  |  |

# TABLE 1-1:DEVICE FEATURES FOR THE PIC18F2XJ11 (28-PIN DEVICES)

#### TABLE 1-2: DEVICE FEATURES FOR THE PIC18F4XJ11 (44-PIN DEVICES)

| Features                             | PIC18F44J11                                                                     | PIC18F45J11               | PIC18F46J11     |  |  |

|--------------------------------------|---------------------------------------------------------------------------------|---------------------------|-----------------|--|--|

| Operating Frequency                  | DC – 48 MHz                                                                     | DC – 48 MHz               | DC – 48 MHz     |  |  |

| Program Memory (Bytes)               | 16K                                                                             | 32K                       | 64K             |  |  |

|                                      | -                                                                               | -                         | -               |  |  |

| Program Memory (Instructions)        | 8,192                                                                           | 16,384                    | 32,768          |  |  |

| Data Memory (Bytes)                  | 3.8K                                                                            | 3.8K                      | 3.8K            |  |  |

| Interrupt Sources                    | 30                                                                              |                           |                 |  |  |

| I/O Ports                            | Ports A, B, C, D, E                                                             |                           |                 |  |  |

| Timers                               | 5                                                                               |                           |                 |  |  |

| Enhanced Capture/Compare/PWM Modules |                                                                                 | 2                         |                 |  |  |

| Serial Communications                | MS                                                                              | SP (2), Enhanced USART    | (2)             |  |  |

| Parallel Communications (PMP/PSP)    |                                                                                 | Yes                       |                 |  |  |

| 10-Bit Analog-to-Digital Module      |                                                                                 | 13 Input Channels         |                 |  |  |

| Resets (and Delays)                  | POR, BOR, RESET Instruction, Stack Full, Stack Underflow, MCLR, WDT (PWRT, OST) |                           |                 |  |  |

| Instruction Set                      | 75 Instructions,                                                                | 83 with Extended Instruct | ion Set Enabled |  |  |

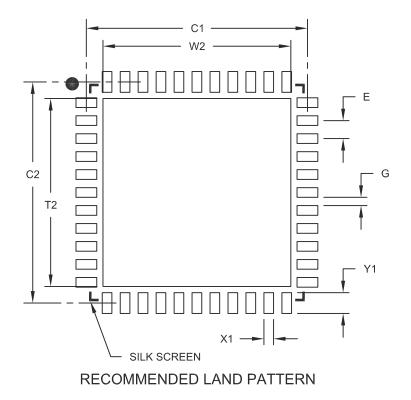

| Packages                             |                                                                                 | 44-Pin QFN and TQFP       |                 |  |  |

|                                                                                                              | Pin N      | umber       | Dia                       | Duffer                                   |                                                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------|------------|-------------|---------------------------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                                                                                                     | 44-<br>QFN | 44-<br>TQFP | Pin<br>Type               | Buffer<br>Type                           | Description                                                                                                                                       |

|                                                                                                              |            |             |                           |                                          | PORTB is a bidirectional I/O port. PORTB can be<br>software programmed for internal weak pull-ups on<br>all inputs.                               |

| RB0/AN12/INT0/RP3<br>RB0<br>AN12<br>INT0<br>RP3                                                              | 9          | 8           | I/O<br>I<br>I<br>I/O      | DIG<br>Analog<br>ST<br>DIG               | Digital I/O.<br>Analog input 12.<br>External interrupt 0.<br>Remappable peripheral pin 3.                                                         |

| RB1/AN10/PMBE/RTCC/RP4<br>RB1<br>AN10<br>PMBE<br>RTCC<br>RP4                                                 | 10         | 9           | I/O<br>I<br>O<br>I/O      | DIG<br>Analog<br>DIG<br>DIG<br>DIG       | Digital I/O.<br>Analog input 10.<br>Parallel Master Port byte enable.<br>Real Time Clock Calendar output.<br>Remappable peripheral pin 4.         |

| RB2/AN8/CTED1/PMA3/REFO/<br>RP5<br>RB2<br>AN8<br>CTED1<br>PMA3<br>REFO<br>RP5                                | 11         | 10          | I/O<br>I<br>I<br>O<br>I/O | DIG<br>Analog<br>ST<br>DIG<br>DIG<br>DIG | Digital I/O.<br>Analog input 8.<br>CTMU edge 1 input.<br>Parallel Master Port address.<br>Reference output clock.<br>Remappable peripheral pin 5. |

| RB3/AN9/CTED2/PMA2/RP6<br>RB3<br>AN9<br>CTED2<br>PMA2<br>RP6                                                 | 12         | 11          | I/O<br>I<br>I<br>O<br>I/O | DIG<br>Analog<br>ST<br>DIG<br>DIG        | Digital I/O.<br>Analog input 9.<br>CTMU edge 2 input.<br>Parallel Master Port address.<br>Remappable peripheral pin 6.                            |

| Legend: TTL = TTL compatible in<br>ST = Schmitt Trigger in<br>I = Input<br>P = Power<br>DIG = Digital output |            | n CMOS      | levels                    | A<br>(                                   | CMOS= CMOS compatible input or outputAnalog= Analog inputO= OutputOD= Open-Drain (no P diode to VDD)                                              |

# TABLE 1-4: PIC18F4XJ11 PINOUT I/O DESCRIPTIONS (CONTINUED)

**Note 1:** RA7 and RA6 will be disabled if OSC1 and OSC2 are used for the clock function.

#### 3.2.5.1 OSCTUNE Register

The internal oscillator's output has been calibrated at the factory but can be adjusted in the user's application. This is done by writing to the OSCTUNE register (Register 3-1).

When the OSCTUNE register is modified, the INTOSC frequency will begin shifting to the new frequency. Code execution continues during this shift. There is no indication that the shift has completed.

The OSCTUNE register also contains the INTSRC bit. The INTSRC bit allows users to select which internal oscillator provides the clock source when the 31 kHz frequency option is selected. This is covered in more detail in **Section 3.3.1 "Oscillator Control Register"**.

The 4x Phase Locked Loop (PLL) can be used with the internal oscillator block to produce faster device clock speeds than are normally possible with the internal oscillator sources. When enabled, the PLL produces a clock speed up to 32 MHz.

PLL operation is controlled through software. The control bit, PLLEN (OSCTUNE<6>), is used to enable or disable its operation. The PLL is available only to INTOSC when the device is configured to use one of the INTPLL modes as the primary clock source, SCS<1:0> = 00 (FOSC<2:0> = 011 or 010). Additionally, the PLL will only function when the selected output frequency is either 4 MHz or 8 MHz (OSCCON<6:4> = 111 or 110).

When configured for one of the PLL enabled modes, setting the PLLEN bit does not immediately switch the device clock to the PLL output. The PLL requires up to two milliseconds to start-up and lock, during which time, the device continues to be clocked. Once the PLL output is ready, the microcontroller core will automatically switch to the PLL derived frequency.

#### 3.2.5.2 Internal Oscillator Output Frequency and Drift

The internal oscillator block is calibrated at the factory to produce an INTOSC output frequency of 8.0 MHz. However, this frequency may drift as VDD or temperature changes, which can affect the controller operation in a variety of ways.

The low-frequency INTRC oscillator operates independently of the INTOSC source. Any changes in INTOSC across voltage and temperature are not necessarily reflected by changes in INTRC and vice versa.

### 3.2.5.3 Compensating for INTOSC Drift

It is possible to adjust the INTOSC frequency by modifying the value in the OSCTUNE register. This has no effect on the INTRC clock source frequency.

Tuning the INTOSC source requires knowing when to make the adjustment, in which direction it should be made, and in some cases, how large a change is needed. When using the EUSART, for example, an adjustment may be required when it begins to generate framing errors or receives data with errors while in Asynchronous mode. Framing errors indicate that the device clock frequency is too high; to adjust for this, decrement the value in OSCTUNE to reduce the clock frequency. On the other hand, errors in data may suggest that the clock speed is too low; to compensate, increment OSCTUNE to increase the clock frequency.

It is also possible to verify device clock speed against a reference clock. Two timers may be used: one timer is clocked by the peripheral clock, while the other is clocked by a fixed reference source, such as the Timer1 oscillator. Both timers are cleared, but the timer clocked by the reference generates interrupts. When an interrupt occurs, the internally clocked timer is read and both timers are cleared. If the internally clocked timer value is greater than expected, then the internal oscillator block is running too fast. To adjust for this, decrement the OSCTUNE register.

Finally, an ECCP module can use free-running Timer1 (or Timer3), clocked by the internal oscillator block and an external event with a known period (i.e., AC power frequency). The time of the first event is captured in the CCPRxH:CCPRxL registers and is recorded for use later. When the second event causes a capture, the time of the first event is subtracted from the time of the second event. Since the period of the external event is known, the time difference between events can be calculated.

If the measured time is greater than the calculated time, the internal oscillator block is running too fast; to compensate, decrement the OSCTUNE register. If the measured time is less than the calculated time, the internal oscillator block is running too slow; to compensate, increment the OSCTUNE register.

| REGISTER 10-24: | : RPOR3: PERIPHERAL PIN SELECT OUTPUT REC | GISTER 3 (BANKED EC9h) |

|-----------------|-------------------------------------------|------------------------|

|-----------------|-------------------------------------------|------------------------|

| U-0             | U-0                                       | U-0              | R/W-0 | R/W-0                                  | R/W-0 | R/W-0 | R/W-0 |

|-----------------|-------------------------------------------|------------------|-------|----------------------------------------|-------|-------|-------|

| _               | _                                         | —                | RP3R4 | RP3R3                                  | RP3R2 | RP3R1 | RP3R0 |

| bit 7           |                                           |                  |       |                                        |       |       | bit 0 |

|                 |                                           |                  |       |                                        |       |       |       |

| Legend:         | d: R/W = Readable, Writable if IOLOCK = 0 |                  |       |                                        |       |       |       |

| R = Readable    | bit                                       | W = Writable     | bit   | U = Unimplemented bit, read as '0'     |       |       |       |

| -n = Value at P | OR                                        | '1' = Bit is set | ł     | '0' = Bit is cleared x = Bit is unknow |       |       | nown  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP3R<4:0>:** Peripheral Output Function is Assigned to RP3 Output Pin bits (see Table 10-14 for peripheral function numbers)

#### REGISTER 10-25: RPOR4: PERIPHERAL PIN SELECT OUTPUT REGISTER 4 (BANKED ECAh)

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-------|-------|-------|

| —     | _   |     | RP4R4 | RP4R3 | RP4R2 | RP4R1 | RP4R0 |

| bit 7 |     |     |       |       |       |       | bit 0 |

| Legend:           | $R/\overline{W}$ = Readable, Writable if IOLOCK = 0 |                                    |                    |  |  |  |

|-------------------|-----------------------------------------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit                                    | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP4R<4:0>:** Peripheral Output Function is Assigned to RP4 Output Pin bits (see Table 10-14 for peripheral function numbers)

#### REGISTER 10-26: RPOR5: PERIPHERAL PIN SELECT OUTPUT REGISTER 5 (BANKED ECBh)

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-------|-------|-------|

| —     | —   | —   | RP5R4 | RP5R3 | RP5R2 | RP5R1 | RP5R0 |

| bit 7 |     |     |       |       |       |       | bit 0 |

| Legend:           | $R/\overline{W}$ = Readable, Writable if IOLOCK = 0 |                                    |                    |  |  |

|-------------------|-----------------------------------------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                                    | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP5R<4:0>:** Peripheral Output Function is Assigned to RP5 Output Pin bits (see Table 10-14 for peripheral function numbers)

# **11.4 Application Examples**

This section introduces some potential applications for the PMP module.

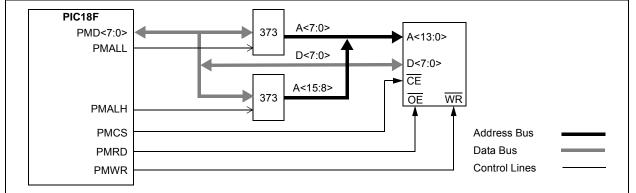

#### 11.4.1 MULTIPLEXED MEMORY OR PERIPHERAL

Figure 11-27 demonstrates the hookup of a memory or another addressable peripheral in Full Multiplex mode. Consequently, this mode achieves the best pin saving from the microcontroller perspective. However, for this configuration, there needs to be some external latches to maintain the address.

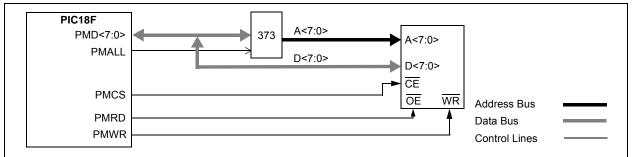

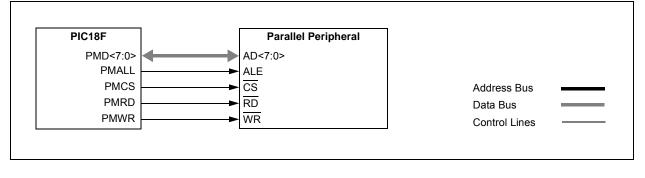

#### 11.4.2 PARTIALLY MULTIPLEXED MEMORY OR PERIPHERAL

Partial multiplexing implies using more pins; however, for a few extra pins, some extra performance can be achieved. Figure 11-28 provides an example of a memory or peripheral that is partially multiplexed with an external latch. If the peripheral has internal latches, as displayed in Figure 11-29, then no extra circuitry is required except for the peripheral itself.

#### FIGURE 11-28: EXAMPLE OF A PARTIALLY MULTIPLEXED ADDRESSING APPLICATION

#### FIGURE 11-29: EXAMPLE OF AN 8-BIT MULTIPLEXED ADDRESS AND DATA APPLICATION

# REGISTER 15-3: TCLKCON: TIMER CLOCK CONTROL REGISTER (BANKED F52h)

| U-0   | U-0 | U-0 | R-0   | U-0 | U-0 | R/W-0  | R/W-0  |

|-------|-----|-----|-------|-----|-----|--------|--------|

| _     |     | —   | T1RUN | —   | —   | T3CCP2 | T3CCP1 |

| bit 7 |     |     |       |     |     |        | bit 0  |

| Legend:           |                  |                        |                                    |  |  |

|-------------------|------------------|------------------------|------------------------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | U = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown                 |  |  |

| bit 7-5<br>bit 4 | Unimplemented: Read as '0'<br>T1RUN: Timer1 Run Status bit<br>1 = Device is currently clocked by T1OSC/T1CKI<br>0 = System clock comes from an oscillator other than T1OSC/T1CKI                                                                                                                                                                            |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3-2          | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                  |

| bit 1-0          | <ul> <li>T3CCP&lt;2:1&gt;: ECCP Timer Assignment bits</li> <li>10 = ECCP1 and ECCP2 both use Timer3 (capture/compare) and Timer4 (PWM)</li> <li>01 = ECCP1 uses Timer1 (compare/capture) and Timer2 (PWM); ECCP2 uses Timer3 (capture/compare) and Timer4 (PWM)</li> <li>00 = ECCP1 and ECCP2 both use Timer1 (capture/compare) and Timer2 (PWM)</li> </ul> |

# 15.6 Timer3 Interrupt

The TMR3 register pair (TMR3H:TMR3L) increments from 0000h to FFFFh and overflows to 0000h. The Timer3 interrupt, if enabled, is generated on overflow and is latched in interrupt flag bit, TMR3IF (PIR2<1>). This interrupt can be enabled or disabled by setting or clearing the Timer3 Interrupt Enable bit, TMR3IE (PIE2<1>).

### 15.7 Resetting Timer3 Using the ECCP Special Event Trigger

If ECCP1 or ECCP2 is configured to use Timer3 and to generate a Special Event Trigger in Compare mode (CCPxM<3:0> = 1011), this signal will reset Timer3.

The trigger from ECCP2 will also start an A/D conversion if the A/D module is enabled (see **Section 18.3.4** "**Special Event Trigger**" for more information).

The module must be configured as either a timer or synchronous counter to take advantage of this feature. When used this way, the CCPRxH:CCPRxL register pair effectively becomes a Period register for Timer3.

If Timer3 is running in Asynchronous Counter mode, the Reset operation may not work.

In the event that a write to Timer3 coincides with a Special Event Trigger from an ECCP module, the write will take precedence.

Note: The Special Event Triggers from the ECCPx module will not set the TMR3IF interrupt flag bit (PIR1<0>).

| Name    | Bit 7                     | Bit 6     | Bit 5   | Bit 4   | Bit 3            | Bit 2  | Bit 1   | Bit 0  | Reset<br>Values<br>on Page: |

|---------|---------------------------|-----------|---------|---------|------------------|--------|---------|--------|-----------------------------|

| INTCON  | GIE/GIEH                  | PEIE/GIEL | TMR0IE  | INT0IE  | RBIE             | TMR0IF | INT0IF  | RBIF   | 90                          |

| PIR2    | OSCFIF                    | CM2IF     | CM1IF   | _       | BCL1IF           | LVDIF  | TMR3IF  | CCP2IF | 92                          |

| PIE2    | OSCFIE                    | CM2IE     | CM1IE   | _       | BCL1IE           | LVDIE  | TMR3IE  | CCP2IE | 92                          |

| IPR2    | OSCFIP                    | CM2IP     | CM1IP   | _       | BCL1IP           | LVDIP  | TMR3IP  | CCP2IP | 92                          |

| TMR3L   | Timer3 Register Low Byte  |           |         |         |                  |        |         |        | 93                          |

| TMR3H   | Timer3 Register High Byte |           |         |         |                  |        |         | 93     |                             |

| T1CON   | TMR1CS1                   | TMR1CS0   | T1CKPS1 | T1CKPS0 | T1OSCEN          | T1SYNC | RD16    | TMR10N | 91                          |

| T3CON   | TMR3CS1                   | TMR3CS0   | T3CKPS1 | T3CKPS0 | _                | T3SYNC | RD16    | TMR3ON | 93                          |

| T3GCON  | TMR3GE                    | T3GPOL    | T3GTM   | T3GSPM  | T3GGO/<br>T3DONE | T3GVAL | T3GSS1  | T3GSS0 | 92                          |

| TCLKCON | —                         | —         | —       | T1RUN   | —                | _      | T3CCP2  | T3CCP1 | 94                          |

| PIR3    | SSP2IF                    | BCL2IF    | RC2IF   | TX2IF   | TMR4IF           | CTMUIF | TMR3GIF | RTCCIF | 92                          |

| PIE3    | SSP2IE                    | BCL2IE    | RC2IE   | TX2IE   | TMR4IE           | CTMUIE | TMR3GIE | RTCCIE | 92                          |

| IPR3    | SSP2IP                    | BCL2IP    | RC2IP   | TX2IP   | TMR4IP           | CTMUIP | TMR3GIP | RTCCIP | 92                          |

### TABLE 15-3: REGISTERS ASSOCIATED WITH TIMER3 AS A TIMER/COUNTER

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the Timer3 module.

| R/W-0           | R/W-0                                                                                                              | R/W-0                                                       | R/W-0                                                        | R/W-0                                         | R/W-0                                             | R/W-0                                  | R/W-0       |

|-----------------|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--------------------------------------------------------------|-----------------------------------------------|---------------------------------------------------|----------------------------------------|-------------|

| SSCON1          | SSCON0                                                                                                             | TXINC                                                       | RXINC                                                        | DUPLEX1                                       | DUPLEX0                                           | DLYINTEN                               | DMAEN       |

| bit 7           |                                                                                                                    |                                                             |                                                              |                                               |                                                   |                                        | bit         |

| Legend:         |                                                                                                                    |                                                             |                                                              |                                               |                                                   |                                        |             |

| R = Readable    | bit                                                                                                                | W = Writable                                                | bit                                                          | U = Unimpler                                  | mented bit, read                                  | d as '0'                               |             |

| -n = Value at F | POR                                                                                                                | '1' = Bit is set                                            | t                                                            | '0' = Bit is cle                              | ared                                              | x = Bit is unkn                        | iown        |

| bit 7-6         | $11 = \frac{\text{SSDMA}}{\text{O1} = \frac{\text{SSDMA}}{\text{SSDMA}}}$ $10 = \frac{\text{SSDMA}}{\text{SSDMA}}$ | is asserted for<br>is asserted for<br>is asserted for       | the duration<br>the duration<br>the duration                 | of 2 bytes; DLY<br>of 1 byte; DLYI            | INTEN is alway<br>INTEN is alway<br>NTEN is alway | ys reset low<br>s reset low            |             |

| bit 5           | <b>TXINC:</b> Trans<br>Allows the tra<br>1 = The trans                                                             | smit Address Ir<br>Insmit address<br>mit address is         | to increment Enal<br>to increment to<br>to be increme        | ble bit<br>as the transfer<br>nted from the i | progresses.                                       | tware programr<br>XADDR<11:0><br> 1:0> | napie       |

| bit 4           | Allows the recei                                                                                                   | ved address is                                              | to increment a to be increme                                 | s the transfer p<br>ented from the            | -                                                 | RXADDR<11:0><br>11:0>                  |             |

| bit 3-2         | <b>DUPLEX&lt;1:0</b><br>10 = SPI DM.<br>01 = DMA op                                                                | I>: Transmit/Read<br>A operates in F<br>erates in Half-     | eceive Operat<br>Full-Duplex mo<br>Duplex mode,              | ing Mode Seled                                | ct bits<br>nultaneously tra<br>itted only         | nsmitted and re                        | ceived      |

| bit 1           | <b>DLYINTEN:</b> DEnables the i<br>elapsed from<br>1 = The intern                                                  | Delay Interrupt<br>nterrupt to be<br>the latest com         | Enable bit<br>invoked after<br>pleted transfe<br>, SSCON<1:0 | the number of                                 | SCK cycles sp                                     | ecified in DLYC                        | YC<2:0≻ ha  |

| bit 0           | <b>DMAEN:</b> DM<br>This bit is set                                                                                | A Operation St<br>by the users'<br>the DMA opera<br>session | art/Stop bit<br>software to st                               | art the DMA op<br>eted or aborted             |                                                   | eset back to zer                       | o by the DM |

# REGISTER 19-3: DMACON1: DMA CONTROL REGISTER 1 (ACCESS F88h)

# 19.5.2 OPERATION

The MSSP module functions are enabled by setting the MSSP Enable bit, SSPEN (SSPxCON1<5>).

The SSPxCON1 register allows control of the  $I^2C$  operation. Four mode selection bits (SSPxCON1<3:0>) allow one of the following  $I^2C$  modes to be selected:

- I<sup>2</sup>C Master mode, clock

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address) with Start and Stop bit interrupts enabled

- I<sup>2</sup>C Slave mode (10-bit address) with Start and Stop bit interrupts enabled

- I<sup>2</sup>C Firmware Controlled Master mode, slave is Idle

Selection of any I<sup>2</sup>C mode with the SSPEN bit set forces the SCLx and SDAx pins to be open-drain, provided these pins are programmed as inputs by setting the appropriate TRISB or TRISD bits. To ensure proper operation of the module, pull-up resistors must be provided externally to the SCLx and SDAx pins.

#### 19.5.3 SLAVE MODE

In Slave mode, the SCLx and SDAx pins must be configured as inputs (TRISB<5:4> set). The MSSP module will override the input state with the output data when required (slave-transmitter).

The  $l^2C$  Slave mode hardware will always generate an interrupt on an address match. Address masking will allow the hardware to generate an interrupt for more than one address (up to 31 in 7-bit addressing and up to 63 in 10-bit addressing). Through the mode select bits, the user can also choose to interrupt on Start and Stop bits.

When an address is matched, or the data transfer after an address match is received, the hardware automatically will generate the Acknowledge (ACK) pulse and load the SSPxBUF register with the received value currently in the SSPxSR register.

Any combination of the following conditions will cause the MSSP module not to give this ACK pulse:

- The Buffer Full bit, BF (SSPxSTAT<0>), was set before the transfer was received.

- The overflow bit, SSPOV (SSPxCON1<6>), was set before the transfer was received.

In this case, the SSPxSR register value is not loaded into the SSPxBUF, but bit, SSPxIF, is set. The BF bit is cleared by reading the SSPxBUF register, while bit, SSPOV, is cleared through software. The SCLx clock input must have a minimum high and low for proper operation. The high and low times of the  $I^2C$  specification, as well as the requirement of the MSSP module, are shown in timing parameter 100 and parameter 101.

### 19.5.3.1 Addressing

Once the MSSP module has been enabled, it waits for a Start condition to occur. Following the Start condition, the 8 bits are shifted into the SSPxSR register. All incoming bits are sampled with the rising edge of the clock (SCLx) line. The value of register, SSPxSR<7:1>, is compared to the value of the SSPxADD register. The address is compared on the falling edge of the eighth clock (SCLx) pulse. If the addresses match and the BF and SSPOV bits are clear, the following events occur:

- 1. The SSPxSR register value is loaded into the SSPxBUF register.

- 2. The Buffer Full bit, BF, is set.

- 3. An ACK pulse is generated.

- 4. The MSSPx Interrupt Flag bit, SSPxIF, is set (and interrupt is generated, if enabled) on the falling edge of the ninth SCLx pulse.

In 10-Bit Addressing mode, two address bytes need to be received by the slave. The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. Bit  $R/\overline{W}$  (SSPxSTAT<2>) must specify a write so the slave device will receive the second address byte. For a 10-bit address, the first byte would equal '11110 A9 A8 0', where 'A9' and 'A8' are the two MSbs of the address. The sequence of events for 10-bit addressing is as follows, with steps 7 through 9 for the slave-transmitter:

- 1. Receive first (high) byte of address (bits, SSPxIF, BF and UA, are set on address match).

- 2. Update the SSPxADD register with second (low) byte of address (clears bit, UA, and releases the SCLx line).

- 3. Read the SSPxBUF register (clears bit, BF) and clear flag bit, SSPxIF.

- 4. Receive second (low) byte of address (bits, SSPxIF, BF and UA, are set).

- 5. Update the SSPxADD register with the first (high) byte of address. If match releases SCLx line, this will clear bit, UA.

- 6. Read the SSPxBUF register (clears bit, BF) and clear flag bit, SSPxIF.

- 7. Receive Repeated Start condition.

- 8. Receive first (high) byte of address (bits, SSPxIF and BF, are set).

- 9. Read the SSPxBUF register (clears bit, BF) and clear flag bit, SSPxIF.

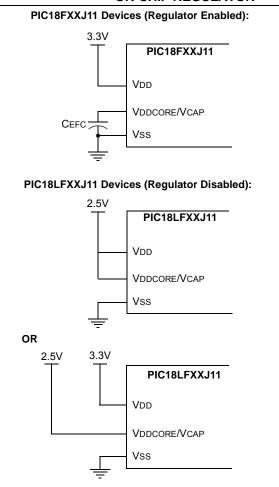

# FIGURE 26-2: CONNECTIONS FOR THE ON-CHIP REGULATOR

# 26.3.2 ON-CHIP REGULATOR AND BOR

When the on-chip regulator is enabled, PIC18F46J11 family devices also have a simple brown-out capability. If the voltage supplied to the regulator is inadequate to maintain a minimum output level; the regulator Reset circuitry will generate a Brown-out Reset (BOR). This event is captured by the BOR flag bit (RCON<0>).

The operation of the BOR is described in more detail in Section 5.4 "Brown-out Reset (BOR)" and Section 5.4.1 "Detecting BOR". The brown-out voltage levels are specific in Section 29.1 "DC Characteristics: Supply Voltage PIC18F46J11 Family (Industrial)".

# 26.3.3 POWER-UP REQUIREMENTS

The on-chip regulator is designed to meet the power-up requirements for the device. If the application does not use the regulator, then strict power-up conditions must be adhered to. While powering up, VDDCORE should not exceed VDD by 0.3 volts.

# 26.3.4 OPERATION IN SLEEP MODE

When enabled, the on-chip regulator always consumes a small incremental amount of current over IDD. This includes when the device is in Sleep mode, even though the core digital logic does not require much power. To provide additional savings in applications where power resources are critical, the regulator can be configured to automatically enter a lower quiescent draw standby mode whenever the device goes into Sleep mode. This feature is controlled by the REGSLP bit (WDTCON<7>, Register 26-11). If this bit is set upon entry into Sleep mode, the regulator will transition into a lower power state. In this state, the regulator still provides a regulated output voltage necessary to maintain SRAM state information, but consumes less quiescent current.

Substantial Sleep mode power savings can be obtained by setting the REGSLP bit, but device wake-up time will increase in order to insure the regulator has enough time to stabilize.

# 27.0 INSTRUCTION SET SUMMARY

The PIC18F46J11 family of devices incorporates the standard set of 75 PIC18 core instructions, and an extended set of eight new instructions for the optimization of code that is recursive or that utilizes a software stack. The extended set is discussed later in this section.

# 27.1 Standard Instruction Set

The standard PIC18 instruction set adds many enhancements to the previous PIC<sup>®</sup> MCU instruction sets, while maintaining an easy migration from these PIC MCU instruction sets. Most instructions are a single program memory word (16 bits), but there are four instructions that require two program memory locations.

Each single-word instruction is a 16-bit word divided into an opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction.

The instruction set is highly orthogonal and is grouped into four basic categories:

- Byte-oriented operations

- Bit-oriented operations

- · Literal operations

- Control operations

The PIC18 instruction set summary in Table 27-2 lists the **byte-oriented**, **bit-oriented**, **literal** and **control** operations.

Table 27-1 provides the opcode field descriptions.

Most Byte-oriented instructions have three operands:

- 1. The file register (specified by 'f')

- 2. The destination of the result (specified by 'd')

- 3. The accessed memory (specified by 'a')

The file register designator, 'f', specifies which file register is to be used by the instruction. The destination designator, 'd', specifies where the result of the operation is to be placed. If 'd' is '0', the result is placed in the WREG register. If 'd' is '1', the result is placed in the file register specified in the instruction.

All **Bit-oriented** instructions have three operands:

- 1. The file register (specified by 'f')

- 2. The bit in the file register (specified by 'b')

- 3. The accessed memory (specified by 'a')

The bit field designator 'b' selects the number of the bit affected by the operation, while the file register designator, 'f', represents the number of the file in which the bit is located. The **Literal** instructions may use some of the following operands:

- A literal value to be loaded into a file register (specified by 'k')

- The desired FSR register to load the literal value into (specified by 'f')

- No operand required (specified by '—')

The **Control** instructions may use some of the following operands:

- A program memory address (specified by 'n')

- The mode of the CALL or RETURN instructions (specified by 's')

- The mode of the table read and table write instructions (specified by 'm')

- No operand required (specified by '---')

All instructions are a single word, except for four double-word instructions. These instructions were made double-word to contain the required information in 32 bits. In the second word, the 4 MSbs are '1's. If this second word is executed as an instruction (by itself), it will execute as a NOP.

All single-word instructions are executed in a single instruction cycle, unless a conditional test is true or the Program Counter (PC) is changed as a result of the instruction. In these cases, the execution takes two instruction cycles with the additional instruction cycle(s) executed as a NOP.

The double-word instructions execute in two instruction cycles.

One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true, or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s. Two-word branch instructions (if true) would take 3  $\mu$ s.

Figure 27-1 provides the general formats that the instructions can have. All examples use the convention 'nnh' to represent a hexadecimal number.

The instruction set summary, provided in Table 27-2, lists the standard instructions recognized by the Microchip MPASM<sup>™</sup> Assembler.

Section 27.1.1 "Standard Instruction Set" provides a description of each instruction.

| BTFS        | SC                    | Bit Test File                                                                | , Skip if Clear                                                                                                                   |                                                               |  |  |  |  |  |  |

|-------------|-----------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|--|--|--|--|--|--|

| Synta       | IX:                   | BTFSC f, b                                                                   | BTFSC f, b {,a}                                                                                                                   |                                                               |  |  |  |  |  |  |

| Opera       |                       | 0 ≤ f ≤ 255                                                                  |                                                                                                                                   |                                                               |  |  |  |  |  |  |

|             |                       | $0 \leq b \leq 7$                                                            |                                                                                                                                   |                                                               |  |  |  |  |  |  |

|             |                       | a ∈ [0,1]                                                                    | a ∈ [0,1]                                                                                                                         |                                                               |  |  |  |  |  |  |

| Opera       | ation:                | skip if (f <b>)</b>                                                          | = 0                                                                                                                               |                                                               |  |  |  |  |  |  |

| Statu       | s Affected:           | None                                                                         |                                                                                                                                   |                                                               |  |  |  |  |  |  |

| Enco        | ding:                 | 1011                                                                         | bbba fff:                                                                                                                         | f ffff                                                        |  |  |  |  |  |  |

| Desci       | ription:              | instruction is<br>then the next<br>the current in<br>carded and a            | skipped. If bit<br>skipped. If bit<br>instruction fet<br>astruction exect<br>NOP is execu<br>a two-cycle ins                      | 'b' is '0',<br>ched during<br>ution is dis-<br>ted instead,   |  |  |  |  |  |  |

|             |                       |                                                                              | e Access Bank<br>e BSR is used t<br>lefault).                                                                                     |                                                               |  |  |  |  |  |  |

|             |                       | set is enable<br>in Indexed Li<br>mode whene<br>Section 27.2<br>Bit-Oriented | d the extended<br>d, this instructi<br>iteral Offset Ad<br>ever f ≤ 95 (5FH<br>2.3 "Byte-Orie<br>I Instructions<br>et Mode" for d | on operates<br>Idressing<br>n). See<br>nted and<br>in Indexed |  |  |  |  |  |  |

| Word        | s:                    | 1                                                                            |                                                                                                                                   |                                                               |  |  |  |  |  |  |

| Cycle       |                       | 1(2)                                                                         |                                                                                                                                   |                                                               |  |  |  |  |  |  |

| 0,010       |                       | . ,                                                                          | cles if skip and                                                                                                                  | followed                                                      |  |  |  |  |  |  |

|             |                       | by a                                                                         | 2-word instruc                                                                                                                    | tion.                                                         |  |  |  |  |  |  |

| QC          | cle Activity:         |                                                                              |                                                                                                                                   |                                                               |  |  |  |  |  |  |

|             | Q1                    | Q2                                                                           | Q3                                                                                                                                | Q4                                                            |  |  |  |  |  |  |

|             | Decode                | Read<br>register 'f'                                                         | Process<br>Data                                                                                                                   | No<br>operation                                               |  |  |  |  |  |  |

| lf ski      | p:                    | regiotor r                                                                   | Dula                                                                                                                              | oporation                                                     |  |  |  |  |  |  |

|             | Q1                    | Q2                                                                           | Q3                                                                                                                                | Q4                                                            |  |  |  |  |  |  |

|             | No                    | No                                                                           | No                                                                                                                                | No                                                            |  |  |  |  |  |  |

|             | operation             | operation                                                                    | operation                                                                                                                         | operation                                                     |  |  |  |  |  |  |

| IT SKI      | p and followed<br>Q1  | by 2-word inst<br>Q2                                                         | Q3                                                                                                                                | Q4                                                            |  |  |  |  |  |  |

|             | No                    | No                                                                           | No                                                                                                                                | No                                                            |  |  |  |  |  |  |

|             | operation             | operation                                                                    | operation                                                                                                                         | operation                                                     |  |  |  |  |  |  |

|             | No                    | No                                                                           | No                                                                                                                                | No                                                            |  |  |  |  |  |  |

|             | operation             | operation                                                                    | operation                                                                                                                         | operation                                                     |  |  |  |  |  |  |

| <u>Exam</u> | iple:                 | HERE BI<br>FALSE :<br>TRUE :                                                 | FSC FLAG                                                                                                                          | , 1, O                                                        |  |  |  |  |  |  |

| I           | Before Instruct<br>PC |                                                                              | ress (HERE)                                                                                                                       |                                                               |  |  |  |  |  |  |

|             | After Instruction     | n                                                                            |                                                                                                                                   |                                                               |  |  |  |  |  |  |

|             | If FLAG<<br>PC        | - /                                                                          | ress (TRUE)                                                                                                                       |                                                               |  |  |  |  |  |  |

|             | If FLAG<              | l> = 1;                                                                      |                                                                                                                                   |                                                               |  |  |  |  |  |  |

|             | PC                    | = add                                                                        | ress (false)                                                                                                                      | )                                                             |  |  |  |  |  |  |

| BTFSS                                          | Bit Test File                                                                | , Skip if Set                                                                                                                     |                                                                             |  |  |  |  |  |

|------------------------------------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:                                        | BTFSS f, b {                                                                 | ,a}                                                                                                                               |                                                                             |  |  |  |  |  |

| Operands:                                      | $0 \leq f \leq 255$                                                          |                                                                                                                                   |                                                                             |  |  |  |  |  |

|                                                | $0 \le b < 7$                                                                |                                                                                                                                   |                                                                             |  |  |  |  |  |

| <b>o</b> <i>i</i> :                            | a ∈ [0,1]                                                                    | _                                                                                                                                 |                                                                             |  |  |  |  |  |

| Operation:                                     | skip if (f <b>)</b>                                                          | = 1                                                                                                                               |                                                                             |  |  |  |  |  |

| Status Affected:                               | None                                                                         |                                                                                                                                   |                                                                             |  |  |  |  |  |

| Encoding:                                      |                                                                              | bbba fff:                                                                                                                         |                                                                             |  |  |  |  |  |

| Description:                                   | instruction is<br>then the next<br>the current in<br>carded and a            | gister 'f' is '1', tl<br>skipped. If bit<br>t instruction fet<br>nstruction exect<br>a NOP is execu<br>a two-cycle ins            | 'b' is '1',<br>ched during<br>ution is dis-<br>ted instead,                 |  |  |  |  |  |

|                                                |                                                                              | e Access Bank<br>e BSR is used<br>default).                                                                                       |                                                                             |  |  |  |  |  |

|                                                | set is enable<br>in Indexed Li<br>mode whene<br>Section 27.2<br>Bit-Oriented | d the extended<br>d, this instructi<br>iteral Offset Ad<br>ever f ≤ 95 (5FH<br>2.3 "Byte-Orie<br>I Instructions<br>et Mode" for d | on operates<br>Idressing<br>n). See<br><b>nted and</b><br><b>in Indexed</b> |  |  |  |  |  |

| Words:                                         | 1                                                                            |                                                                                                                                   |                                                                             |  |  |  |  |  |

| Cycles:                                        |                                                                              | vcles if skip an<br>a 2-word instru                                                                                               |                                                                             |  |  |  |  |  |

| Q Cycle Activity:                              | 00                                                                           | 00                                                                                                                                | 0.1                                                                         |  |  |  |  |  |

| Q1<br>Decode                                   | Q2<br>Read                                                                   | Q3<br>Process                                                                                                                     | Q4<br>No                                                                    |  |  |  |  |  |

| Decode                                         | register 'f'                                                                 | Data                                                                                                                              | operation                                                                   |  |  |  |  |  |

| lf skip:                                       | 0                                                                            |                                                                                                                                   |                                                                             |  |  |  |  |  |

| Q1                                             | Q2                                                                           | Q3                                                                                                                                | Q4                                                                          |  |  |  |  |  |

| No                                             | No                                                                           | No                                                                                                                                | No                                                                          |  |  |  |  |  |

| operation                                      | operation                                                                    | operation                                                                                                                         | operation                                                                   |  |  |  |  |  |

| If skip and followed<br>Q1                     | Q2                                                                           | Q3                                                                                                                                | Q4                                                                          |  |  |  |  |  |

| No                                             | No                                                                           | No                                                                                                                                | No                                                                          |  |  |  |  |  |

| operation                                      | operation                                                                    | operation                                                                                                                         | operation                                                                   |  |  |  |  |  |

| No                                             | No                                                                           | No                                                                                                                                | No                                                                          |  |  |  |  |  |

| operation                                      | operation                                                                    | operation                                                                                                                         | operation                                                                   |  |  |  |  |  |

| Example:                                       | HERE BI<br>FALSE :<br>TRUE :                                                 | TFSS FLAG                                                                                                                         | , 1, 0                                                                      |  |  |  |  |  |

| Before Instruct<br>PC                          |                                                                              | ress (HERE)                                                                                                                       |                                                                             |  |  |  |  |  |

| After Instruction                              | n                                                                            |                                                                                                                                   |                                                                             |  |  |  |  |  |

| After Instructio<br>If FLAG<<br>PC<br>If FLAG< | 1> = 0;<br>= add                                                             | ress (False)                                                                                                                      | )                                                                           |  |  |  |  |  |

#### 27.2.2 EXTENDED INSTRUCTION SET

| ADD   | FSR               | Add Liter        | Add Literal to FSR                    |        |               |  |  |  |  |

|-------|-------------------|------------------|---------------------------------------|--------|---------------|--|--|--|--|

| Synta | ax:               | ADDFSR           | ADDFSR f, k                           |        |               |  |  |  |  |

| Oper  | ands:             | $0 \le k \le 63$ | $0 \le k \le 63$                      |        |               |  |  |  |  |

|       |                   | f ∈ [ 0, 1,      | 2]                                    |        |               |  |  |  |  |

| Oper  | ation:            | FSR(f) + I       | $s \rightarrow FSR($                  | (f)    |               |  |  |  |  |

| Statu | us Affected: None |                  |                                       |        |               |  |  |  |  |

| Enco  | oding:            | 1110             | 1000                                  | ffkk   | kkkk          |  |  |  |  |

| Desc  | ription:          | The 6-bit        | The 6-bit literal 'k' is added to the |        |               |  |  |  |  |

|       |                   | contents of      | of the FSF                            | R spec | ified by 'f'. |  |  |  |  |

| Word  | ls:               | 1                |                                       |        |               |  |  |  |  |

| Cycle | es:               | 1                |                                       |        |               |  |  |  |  |

| QC    | ycle Activity:    |                  |                                       |        |               |  |  |  |  |

|       | Q1                | Q2               | Q3                                    |        | Q4            |  |  |  |  |

|       | Decode            | Read             | Proces                                | SS     | Write to      |  |  |  |  |

|       |                   | literal 'k'      | Data                                  | 1      | FSR           |  |  |  |  |

|       |                   |                  |                                       |        |               |  |  |  |  |

ADDFSR 2, 0x23

03FFh

0422h

Example:

Before Instruction FSR2

After Instruction

FSR2

=

=

| ADDULNK          | Add Literal to FSR2 and Return                                                                                             |                      |                                            |      |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------|----------------------|--------------------------------------------|------|--|--|--|--|

| Syntax:          | ADDULN                                                                                                                     | ADDULNK k            |                                            |      |  |  |  |  |

| Operands:        | $0 \le k \le 63$                                                                                                           |                      |                                            |      |  |  |  |  |

| Operation:       | FSR2 + k                                                                                                                   | $x \rightarrow FSR2$ | ,                                          |      |  |  |  |  |

|                  | $(TOS) \rightarrow$                                                                                                        | PC                   |                                            |      |  |  |  |  |

| Status Affected: | None                                                                                                                       |                      | -                                          |      |  |  |  |  |

| Encoding:        | 1110                                                                                                                       | 1000                 | 11kk                                       | kkkk |  |  |  |  |

| Description:     | The 6-bit literal 'k' is added to the<br>contents of FSR2. A RETURN is then<br>executed by loading the PC with the<br>TOS. |                      |                                            |      |  |  |  |  |

|                  |                                                                                                                            | a nop is p           | es two cyc<br>performed                    |      |  |  |  |  |

|                  | case of th                                                                                                                 | ne ADDFSI            | ht of as a<br>R instructio<br>'11'); it op | on,  |  |  |  |  |

| Words:           | 1                                                                                                                          |                      |                                            |      |  |  |  |  |

| Cycles:          | 2                                                                                                                          |                      |                                            |      |  |  |  |  |

Q Cycle Activity:

| Q1        | Q2          | Q3        | Q4        |

|-----------|-------------|-----------|-----------|

| Decode    | Read        | Process   | Write to  |

|           | literal 'k' | Data      | FSR       |

| No        | No          | No        | No        |

| Operation | Operation   | Operation | Operation |

| Example:          | AD   | DDULNK 0x23 |  |

|-------------------|------|-------------|--|

| Before Instruc    | tion |             |  |

| FSR2              | =    | 03FFh       |  |

| PC                | =    | 0100h       |  |

| After Instruction | n    |             |  |

=

=

0422h

(TOS)

FSR2

PC

Note: All PIC18 instructions may take an optional label argument preceding the instruction mnemonic for use in symbolic addressing. If a label is used, the instruction format then becomes: {label} instruction argument(s).

# 29.2 DC Characteristics: Power-Down and Supply Current PIC18F46J11 Family (Industrial) (Continued)

| PIC18LFX     | XJ11 Family                         |      |      | <b>rating C</b><br>perature |       | <b>c (unless otherwise</b> $C \le TA \le +85^{\circ}C$ for ind |                                                                |

|--------------|-------------------------------------|------|------|-----------------------------|-------|----------------------------------------------------------------|----------------------------------------------------------------|

| PIC18FXX     | J11 Family                          |      |      | rating C<br>perature        |       | <b>c (unless otherwise</b> $C \le TA \le +85^{\circ}C$ for in  |                                                                |

| Param<br>No. | Device                              | Тур  | Max  | Units                       |       | Condi                                                          | tions                                                          |

|              | Supply Current (IDD) <sup>(2)</sup> |      |      |                             |       |                                                                |                                                                |

|              | PIC18LFXXJ11                        | 1.9  | 3.6  | mA                          | -40°C |                                                                |                                                                |

|              |                                     | 2.0  | 3.8  | mA                          | +25°C | VDD = 2.0V,<br>VDDCORE = 2.0V                                  |                                                                |

|              |                                     | 2.0  | 3.8  | mA                          | +85°C | VDDCORE - 2.0V                                                 |                                                                |

|              | PIC18LFXXJ11                        | 2.8  | 4.8  | mA                          | -40°C |                                                                |                                                                |

|              |                                     | 2.8  | 4.8  | mA                          | +25°C | VDD = 2.5V,<br>VDDCORE = 2.5V                                  |                                                                |

|              |                                     | 2.8  | 4.9  | mA                          | +85°C | VDDCORE - 2.3V                                                 | Fosc = 8 MHz, RC_RUN                                           |

|              | PIC18FXXJ11                         | 2.3  | 4.2  | mA                          | -40°C | VDD = 2.15V,                                                   | mode, Internal RC Oscillator                                   |

|              |                                     | 2.3  | 4.2  | mA                          | +25°C | VDDCORE = 10 $\mu$ F                                           |                                                                |

|              |                                     | 2.4  | 4.5  | mA                          | +85°C | Capacitor                                                      | -                                                              |

|              | PIC18FXXJ11                         | 2.8  | 5.1  | mA                          | -40°C | VDD = 3.3V,                                                    |                                                                |

|              |                                     | 2.8  | 5.1  | mA                          | +25°C | VDDCORE = 10 $\mu$ F                                           |                                                                |

|              |                                     | 2.8  | 5.4  | mA                          | +85°C | Capacitor                                                      |                                                                |

|              | PIC18LFXXJ11                        | 1.9  | 9.4  | μA                          | -40°C |                                                                |                                                                |

|              |                                     | 2.3  | 9.4  | μA                          | +25°C | VDD = 2.0V,<br>VDDCORE = 2.0V                                  |                                                                |

|              |                                     | 4.5  | 17.2 | μA                          | +85°C |                                                                |                                                                |

|              | PIC18LFXXJ11                        | 2.4  | 10.5 | μA                          | -40°C | VDD = 2.5V,                                                    |                                                                |

|              |                                     | 2.8  | 10.5 | μA                          | +25°C | VDD = 2.5V,<br>VDDCORE = 2.5V                                  |                                                                |

|              |                                     | 5.4  | 19.5 | μA                          | +85°C |                                                                | Fosc = 31 kHz, <b>RC_IDLE</b><br>mode, Internal RC Oscillator, |

|              | PIC18FXXJ11                         | 33.3 | 75   | μA                          | -40°C | VDD = 2.15V,                                                   | INTSRC = 0                                                     |