Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

EXF

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 48MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 16                                                                          |

| Program Memory Size        | 32KB (16K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 3.8K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.15V ~ 3.6V                                                                |

| Data Converters            | A/D 10x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 28-QFN (6x6)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f25j11t-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC18F46J11 FAMILY

## 28/44-Pin, Low-Power, High-Performance Microcontrollers

## Power Management Features with nanoWatt XLP for Extreme Low Power:

- Deep Sleep mode: CPU off, Peripherals off, Currents Down to 13 nA and 850 nA with RTCC

- Able to wake-up on external triggers, programmable WDT or RTCC alarm

- Ultra Low-Power Wake-up (ULPWU)

- Sleep mode: CPU off, Peripherals off, SRAM on, Fast Wake-up, Currents Down to 105 nA Typical

- Idle: CPU off, Peripherals on, Currents Down to 2.3 μA Typical

- Run: CPU on, Peripherals on, Currents Down to 6.2 μA Typical

- Timer1 Oscillator/w RTCC: 1 μA, 32 kHz Typical

- Watchdog Timer: 813 nA, 2V Typical

## **Special Microcontroller Features:**

- 5.5V Tolerant Inputs (digital only pins)

- · Low-Power, High-Speed CMOS Flash Technology

- C Compiler Optimized Architecture for Re-Entrant Code

- · Priority Levels for Interrupts

- Self-Programmable under Software Control

- 8 x 8 Single-Cycle Hardware Multiplier

- Extended Watchdog Timer (WDT):

- Programmable period from 4 ms to 131s

- Single-Supply In-Circuit Serial Programming™ (ICSP™) via Two Pins

- In-Circuit Debug (ICD) with Three Breakpoints via Two Pins

- Operating Voltage Range of 2.0V to 3.6V

- On-Chip 2.5V Regulator

- Flash Program Memory of 10,000 Erase/Write Cycles Minimum and 20-Year Data Retention

## **Peripheral Highlights:**

- Peripheral Pin Select:

- Allows independent I/O mapping of many peripherals

- Continuous hardware integrity checking and safety interlocks prevent unintentional configuration changes

- · Hardware Real-Time Clock and Calendar (RTCC):

- Provides clock, calendar and alarm functions

- High-Current Sink/Source 25 mA/25 mA (PORTB and PORTC)

### Peripheral Highlights (Continued):

- · Four Programmable External Interrupts

- Four Input Change Interrupts

- Two Enhanced Capture/Compare/PWM (ECCP) modules:

- One, two or four PWM outputs

- Selectable polarity

- Programmable dead time

- Auto-shutdown and auto-restart

- Pulse steering control

- Two Master Synchronous Serial Port (MSSP) modules featuring:

- 3-wire SPI (all 4 modes)

- 1024-byte SPI Direct Memory Access (DMA) channel

- I<sup>2</sup>C<sup>™</sup> Master and Slave modes

- 8-Bit Parallel Master Port/Enhanced Parallel Slave Port

- Two-Rail Rail Analog Comparators with Input Multiplexing

- 10-Bit, up to 13-Channel Analog-to-Digital (A/D) Converter module:

- Auto-acquisition capability

- Conversion available during Sleep

- Self-Calibration

- High/Low-Voltage Detect module

- Charge Time Measurement Unit (CTMU):

- Supports capacitive touch sensing for touch screens and capacitive switches

- Provides a Precise Resolution Time Measurement for Both Flow Measurement and Simple Temperature Sensing

- Two Enhanced USART modules:

- Supports RS-485, RS-232 and LIN/J2602

- Auto-wake-up on Start bit

- Auto-Baud Detect

### **Flexible Oscillator Structure:**

- 1% Accurate High-Precision Internal Oscillator

- Two External Clock modes, up to 48 MHz (12 MIPS)

- · Low-Power 31 kHz Internal RC Oscillator

- Tunable Internal Oscillator (31 kHz to 8 MHz, ±0.15% Typical, ±1% Max).

- 4x PLL Option

- Secondary Oscillator using Timer1 @ 32 kHz

- Fail-Safe Clock Monitor:

- Allows for safe shutdown if any clock stops

- Two-Speed Oscillator Start-up

- Programmable Reference Clock Output Generator

|                                                                                                 | Pin Nu                     | umber    |             |                |                                                                                                                                                                     |

|-------------------------------------------------------------------------------------------------|----------------------------|----------|-------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                                                                                        | 28-SPDIP/<br>SSOP/<br>SOIC | 28-QFN   | Pin<br>Type | Buffer<br>Type | Description                                                                                                                                                         |

| MCLR                                                                                            | 1                          | 26       | I           | ST             | Master Clear (Reset) input. This pin is an active-low Reset to the device.                                                                                          |

| OSC1/CLKI/RA7<br>OSC1                                                                           | 9                          | 6        | I           | ST             | Oscillator crystal input or external clock source<br>input. ST buffer when configured in RC mode;<br>CMOS otherwise. Main oscillator input<br>connection.           |

|                                                                                                 |                            |          | 1           | CMOS           | External clock source input; always associated with pin function OSC1 (see related OSC1/CLKI pins).                                                                 |

| RA7 <sup>(1)</sup><br>OSC2/CLKO/RA6                                                             | 10                         | 7        | I/O         | TTL            | Digital I/O.<br>Oscillator crystal or clock output.                                                                                                                 |

| OSC2                                                                                            |                            |          | 0           | —              | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode.                                                                             |

| CLKO                                                                                            |                            |          | 0           | _              | Main oscillator feedback output connection.<br>In RC mode, OSC2 pin outputs CLKO, which<br>has 1/4 the frequency of OSC1 and denotes<br>the instruction cycle rate. |

| RA6 <sup>(1)</sup>                                                                              |                            |          | I/O         | TTL            | Digital I/O.                                                                                                                                                        |

| Legend: TTL = TTL compar<br>ST = Schmitt Trig<br>I = Input<br>P = Power<br>DIG = Digital output | iger input w               | ith CMOS | levels      | A<br>C         | MOS = CMOS compatible input or output<br>nalog = Analog input<br>= Output<br>D = Open-Drain (no P diode to VDD)                                                     |

## TABLE 1-3:PIC18F2XJ11 PINOUT I/O DESCRIPTIONS

Note 1: RA7 and RA6 will be disabled if OSC1 and OSC2 are used for the clock function.

## 5.5 Configuration Mismatch (CM)

The Configuration Mismatch (CM) Reset is designed to detect, and attempt to recover from, random memory corrupting events. These include Electrostatic Discharge (ESD) events, which can cause widespread single bit changes throughout the device and result in catastrophic failure.

In PIC18FXXJ Flash devices, the device Configuration registers (located in the configuration memory space) are continuously monitored during operation by comparing their values to complimentary shadow registers. If a mismatch is detected between the two sets of registers, a CM Reset automatically occurs. These events are captured by the CM bit (RCON<5>). The state of the bit is set to '0' whenever a CM event occurs; it does not change for any other Reset event.

A CM Reset behaves similarly to a MCLR, RESET instruction, WDT time-out or Stack Event Resets. As with all hard and power Reset events, the device Configuration Words are reloaded from the Flash Configuration Words in program memory as the device restarts.

## 5.6 Power-up Timer (PWRT)

PIC18F46J11 family devices incorporate an on-chip PWRT to help regulate the POR process. The PWRT is always enabled. The main function is to ensure that the device voltage is stable before code is executed.

The Power-up Timer (PWRT) of the PIC18F46J11 family devices is a 5-bit counter which uses the INTRC source as the clock input. This yields an approximate time interval of  $32 \times 32 \ \mu s = 1 \ ms$ . While the PWRT is counting, the device is held in Reset.

The power-up time delay depends on the INTRC clock and will vary from chip-to-chip due to temperature and process variation. See DC parameter 33 (TPWRT) for details.

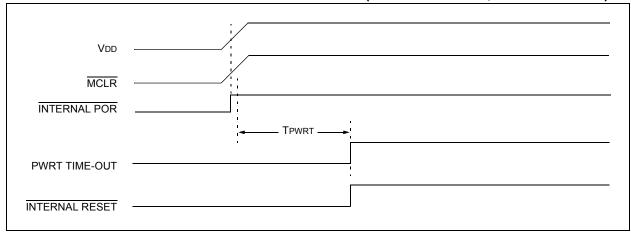

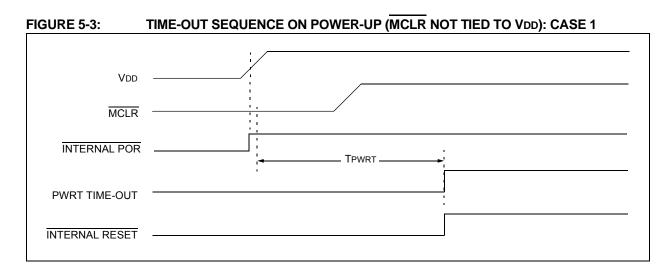

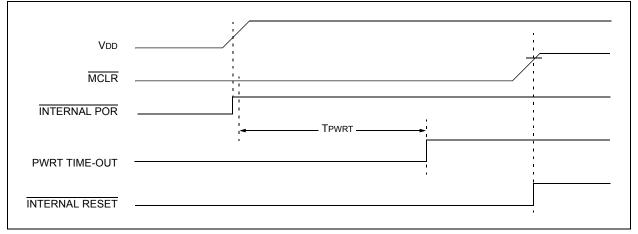

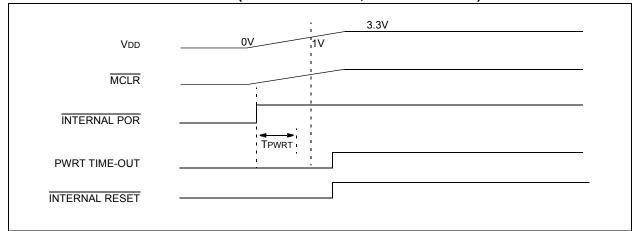

## 5.6.1 TIME-OUT SEQUENCE

The PWRT time-out is invoked after the POR pulse has cleared. The total time-out will vary based on the status of the PWRT. Figure 5-2, Figure 5-3, Figure 5-4 and Figure 5-5 all depict time-out sequences on power-up with the PWRT.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$ is kept low long enough, the PWRT will expire. Bringing  $\overline{\text{MCLR}}$  high will begin execution immediately if a clock source is available (Figure 5-4). This is useful for testing purposes, or to synchronize more than one PIC18FXXXX device operating in parallel.

## FIGURE 5-2: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD, VDD RISE < TPWRT)

## FIGURE 5-4: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

FIGURE 5-5:

## SLOW RISE TIME (MCLR TIED TO VDD, VDD RISE > TPWRT)

## 6.1.1 HARD MEMORY VECTORS

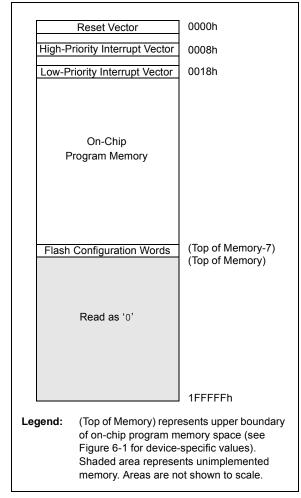

All PIC18 devices have a total of three hard-coded return vectors in their program memory space. The Reset vector address is the default value to which the program counter returns on all device Resets; it is located at 0000h.

PIC18 devices also have two interrupt vector addresses for handling high-priority and low-priority interrupts. The high-priority interrupt vector is located at 0008h and the low-priority interrupt vector at 0018h. Figure 6-2 provides their locations in relation to the program memory map.

### FIGURE 6-2: HARD VECTOR AND CONFIGURATION WORD LOCATIONS FOR PIC18F46J11 FAMILY DEVICES

## 6.1.2 FLASH CONFIGURATION WORDS

Because PIC18F46J11 family devices do not have persistent configuration memory, the top four words of on-chip program memory are reserved for configuration information. On Reset, the configuration information is copied into the Configuration registers.

The Configuration Words are stored in their program memory location in numerical order, starting with the lower byte of CONFIG1 at the lowest address and ending with the upper byte of CONFIG4.

Table 6-1 provides the actual addresses of the Flash Configuration Word for devices in the PIC18F46J11 family. Figure 6-2 displays their location in the memory map with other memory vectors.

Additional details on the device Configuration Words are provided in **Section 26.1** "**Configuration Bits**".

| TABLE 6-1: | FLASH CONFIGURATION<br>WORD FOR PIC18F46J11<br>FAMILY DEVICES |

|------------|---------------------------------------------------------------|

|            |                                                               |

| Device      | Program<br>Memory<br>(Kbytes) | Configuration<br>Word<br>Addresses |  |

|-------------|-------------------------------|------------------------------------|--|

| PIC18F24J11 | 16                            | 3FF8h to 3FFFh                     |  |

| PIC18F44J11 | 10                            |                                    |  |

| PIC18F25J11 | 32                            | 7FF8h to 7FFFh                     |  |

| PIC18F45J11 | 32                            |                                    |  |

| PIC18F26J11 | 64                            | FFF8h to FFFFh                     |  |

| PIC18F46J11 | 04                            |                                    |  |

| Name    | Bit 7    | Bit 6     | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|---------|----------|-----------|---------|---------|---------|--------|--------|--------|----------------------------|

| PORTB   | RB7      | RB6       | RB5     | RB4     | RB3     | RB2    | RB1    | RB0    | 87                         |

| LATB    | LATB7    | LATB6     | LATB5   | LATB4   | LATB3   | LATB2  | LATB1  | LATB0  | 87                         |

| TRISB   | TRISB7   | TRISB6    | TRISB5  | TRISB4  | TRISB3  | TRISB2 | TRISB1 | TRISB0 | 87                         |

| INTCON  | GIE/GIEH | PEIE/GIEL | TMR0IE  | INT0IE  | RBIE    | TMR0IF | INT0IF | RBIF   | 87                         |

| INTCON2 | RBPU     | INTEDG0   | INTEDG1 | INTEDG2 | INTEDG3 | TMR0IP | INT3IP | RBIP   | 87                         |

| INTCON3 | INT2IP   | INT1IP    | INT3IE  | INT2IE  | INT1IE  | INT3IF | INT2IF | INT1IF | 87                         |

| ANCON0  | PCFG7    | PCFG6     | PCFG5   | PCFG4   | PCFG3   | PCFG2  | PCFG1  | PCFG0  | 87                         |

TABLE 10-6: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by PORTB.

## 10.7.6 PERIPHERAL PIN SELECT REGISTERS

The PIC18F46J11 family of devices implements a total of 37 registers for remappable peripheral configuration of 44-pin devices. The 28-pin devices have 31 registers for remappable peripheral configuration.

**Note:** Input and output register values can only be changed if PPS<IOLOCK> = 0. See Example 10-7 for a specific command sequence.

## REGISTER 10-5: PPSCON: PERIPHERAL PIN SELECT INPUT REGISTER 0 (BANKED EFFh)<sup>(1)</sup>

| U-0         | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  |  |

|-------------|-----|-----|-----|-----|-----|-----|--------|--|

| _           | —   |     |     | —   | —   | _   | IOLOCK |  |

| bit 7 bit 0 |     |     |     |     |     |     |        |  |

| Legend:           |                  |                             |                    |  |

|-------------------|------------------|-----------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | 1 as '0'           |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |  |

## bit 7-1 Unimplemented: Read as '0'

bit 0

IOLOCK: I/O Lock Enable bit

1 = I/O lock active, RPORx and RPINRx registers are write-protected

0 = I/O lock not active, pin configurations can be changed

Note 1: Register values can only be changed if PPSCON<IOLOCK> = 0.

## 15.3 Timer3 16-Bit Read/Write Mode

Timer3 can be configured for 16-bit reads and writes (see Section 15.3 "Timer3 16-Bit Read/Write Mode"). When the RD16 control bit (T3CON<1>) is set, the address for TMR3H is mapped to a buffer register for the high byte of Timer3. A read from TMR3L will load the contents of the high byte of Timer3 into the Timer3 High Byte Buffer register. This provides the user with the ability to accurately read all 16 bits of Timer3 without having to determine whether a read of the high byte, followed by a read of the low byte, has become invalid due to a rollover between reads.

A write to the high byte of Timer3 must also take place through the TMR3H Buffer register. The Timer3 high byte is updated with the contents of TMR3H when a write occurs to TMR3L. This allows a user to write all 16 bits to both the high and low bytes of Timer3 at once.

The high byte of Timer3 is not directly readable or writable in this mode. All reads and writes must take place through the Timer3 High Byte Buffer register.

Writes to TMR3H do not clear the Timer3 prescaler. The prescaler is only cleared on writes to TMR3L.

## 15.4 Using the Timer1 Oscillator as the Timer3 Clock Source

The Timer1 internal oscillator may be used as the clock source for Timer3. The Timer1 oscillator is enabled by setting the T1OSCEN (T1CON<3>) bit. To use it as the Timer3 clock source, the TMR3CS bit must also be set. As previously noted, this also configures Timer3 to increment on every rising edge of the oscillator source. The Timer1 oscillator is described in Section 13.0 "Timer1 Module".

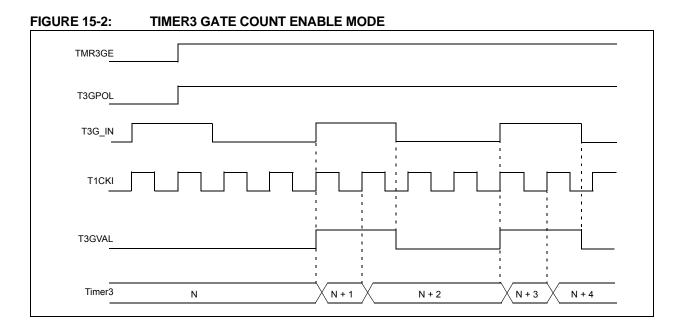

## 15.5 Timer3 Gate

Timer3 can be configured to count freely, or the count can be enabled and disabled using Timer3 gate circuitry. This is also referred to as Timer3 gate count enable.

Timer3 gate can also be driven by multiple selectable sources.

## 15.5.1 TIMER3 GATE COUNT ENABLE

The Timer3 Gate Enable mode is enabled by setting the TMR3GE bit of the T3GCON register. The polarity of the Timer3 Gate Enable mode is configured using the T3GPOL bit of the T3GCON register.

When Timer3 Gate Enable mode is enabled, Timer3 will increment on the rising edge of the Timer3 clock source. When Timer3 Gate Enable mode is disabled, no incrementing will occur and Timer3 will hold the current count. See Figure 15-2 for timing details.

## TABLE 15-1: TIMER3 GATE ENABLE SELECTIONS

| T3CLK      | T3GPOL | T3G | Timer3 Operation |

|------------|--------|-----|------------------|

| $\uparrow$ | 0      | 0   | Counts           |

| $\uparrow$ | 0      | 1   | Holds Count      |

| $\uparrow$ | 1      | 0   | Holds Count      |

| $\uparrow$ | 1      | 1   | Counts           |

## REGISTER 17-11: HOURS: HOURS VALUE REGISTER (ACCESS F98h, PTR 01b)<sup>(1)</sup>

| U-0   | U-0 | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | HRTEN1 | HRTEN0 | HRONE3 | HRONE2 | HRONE1 | HRONE0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 7-6 | Unimplemented: Read as '0'                                                                                  |

|---------|-------------------------------------------------------------------------------------------------------------|

| bit 5-4 | HRTEN<1:0>: Binary Coded Decimal Value of Hour's Tens Digit bits<br>Contains a value from 0 to 2.           |

| bit 3-0 | <b>HRONE&lt;3:0&gt;:</b> Binary Coded Decimal Value of Hour's Ones Digit bits Contains a value from 0 to 9. |

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

### REGISTER 17-12: MINUTES: MINUTES VALUE REGISTER (ACCESS F99h, PTR 00b)

| U-0   | R/W-x   |

|-------|---------|---------|---------|---------|---------|---------|---------|

| —     | MINTEN2 | MINTEN1 | MINTEN0 | MINONE3 | MINONE2 | MINONE1 | MINONE0 |

| bit 7 |         |         |         |         |         |         | bit 0   |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7   | Unimplemented: Read as '0'                                                                                     |

|---------|----------------------------------------------------------------------------------------------------------------|

| bit 6-4 | <b>MINTEN&lt;2:0&gt;:</b> Binary Coded Decimal Value of Minute's Tens Digit bits Contains a value from 0 to 5. |

| bit 3-0 | MINONE<3:0>: Binary Coded Decimal Value of Minute's Ones Digit bits<br>Contains a value from 0 to 9.           |

## REGISTER 17-13: SECONDS: SECONDS VALUE REGISTER (ACCESS F98h, PTR 00b)

| U-0   | R/W-x   |

|-------|---------|---------|---------|---------|---------|---------|---------|

| —     | SECTEN2 | SECTEN1 | SECTEN0 | SECONE3 | SECONE2 | SECONE1 | SECONE0 |

| bit 7 |         |         |         |         |         |         | bit 0   |

| Legend:    |         |                                                                                                                                                        |                        |                    |  |  |  |

|------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--------------------|--|--|--|

| R = Reada  | ble bit | W = Writable bit                                                                                                                                       | U = Unimplemented bit, | read as '0'        |  |  |  |

| -n = Value | at POR  | '1' = Bit is set                                                                                                                                       | '0' = Bit is cleared   | x = Bit is unknown |  |  |  |

| bit 7      | Unimple | mented: Read as '0'                                                                                                                                    |                        |                    |  |  |  |

| bit 6-4    | SECTEN  | <b>Unimplemented:</b> Read as '0'<br><b>SECTEN&lt;2:0&gt;:</b> Binary Coded Decimal Value of Second's Tens Digit bits<br>Contains a value from 0 to 5. |                        |                    |  |  |  |

|            |         |                                                                                                                                                        |                        |                    |  |  |  |

bit 3-0 SECONE<3:0>: Binary Coded Decimal Value of Second's Ones Digit bits Contains a value from 0 to 9.

## REGISTER 17-16: ALRMWD: ALARM WEEKDAY VALUE REGISTER (ACCESS F8Fh, PTR 01b)<sup>(1)</sup>

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-x | R/W-x | R/W-x |

|-------|-----|-----|-----|-----|-------|-------|-------|

| —     | —   | —   | —   | —   | WDAY2 | WDAY1 | WDAY0 |

| bit 7 |     |     |     |     |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-3 Unimplemented: Read as '0'

bit 2-0 **WDAY<2:0>:** Binary Coded Decimal Value of Weekday Digit bits Contains a value from 0 to 6.

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

## REGISTER 17-17: ALRMHR: ALARM HOURS VALUE REGISTER (ACCESS F8Eh, PTR 01b)<sup>(1)</sup>

| U-0   | U-0 | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | HRTEN1 | HRTEN0 | HRONE3 | HRONE2 | HRONE1 | HRONE0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7-6 | Unimplemented: Read as '0'                                                                                  |

|---------|-------------------------------------------------------------------------------------------------------------|

| bit 5-4 | <b>HRTEN&lt;1:0&gt;:</b> Binary Coded Decimal Value of Hour's Tens Digit bits Contains a value from 0 to 2. |

| bit 3-0 | <b>HRONE3:HRONE0:</b> Binary Coded Decimal Value of Hour's Ones Digit bits Contains a value from 0 to 9.    |

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

## TABLE 17-2:DAY TO MONTH ROLLOVER<br/>SCHEDULE

| Month          | Maximum Day Field       |  |  |  |

|----------------|-------------------------|--|--|--|

| 01 (January)   | 31                      |  |  |  |

| 02 (February)  | 28 or 29 <sup>(1)</sup> |  |  |  |

| 03 (March)     | 31                      |  |  |  |

| 04 (April)     | 30                      |  |  |  |

| 05 (May)       | 31                      |  |  |  |

| 06 (June)      | 30                      |  |  |  |

| 07 (July)      | 31                      |  |  |  |

| 08 (August)    | 31                      |  |  |  |

| 09 (September) | 30                      |  |  |  |

| 10 (October)   | 31                      |  |  |  |

| 11 (November)  | 30                      |  |  |  |

| 12 (December)  | 31                      |  |  |  |

Note 1: See Section 17.2.4 "Leap Year".

## 17.2.4 LEAP YEAR

Since the year range on the RTCC module is 2000 to 2099, the leap year calculation is determined by any year divisible by '4' in the above range. Only February is effected in a leap year.

February will have 29 days in a leap year and 28 days in any other year.

## 17.2.5 GENERAL FUNCTIONALITY

All Timer registers containing a time value of seconds or greater are writable. The user configures the time by writing the required year, month, day, hour, minutes and seconds to the Timer registers, via Register Pointers (see Section 17.2.8 "Register Mapping").

The timer uses the newly written values and proceeds with the count from the required starting point.

The RTCC is enabled by setting the RTCEN bit (RTCCFG<7>). If enabled, while adjusting these registers, the timer still continues to increment. However, any time the MINSEC register is written to, both of the timer prescalers are reset to '0'. This allows fraction of a second synchronization.

The Timer registers are updated in the same cycle as the write instruction's execution by the CPU. The user must ensure that when RTCEN = 1, the updated registers will not be incremented at the same time. This can be accomplished in several ways:

- By checking the RTCSYNC bit (RTCCFG<4>)

- By checking the preceding digits from which a carry can occur

- By updating the registers immediately following the seconds pulse (or alarm interrupt)

The user has visibility to the half-second field of the counter. This value is read-only and can be reset only by writing to the lower half of the SECONDS register.

## 17.2.6 SAFETY WINDOW FOR REGISTER READS AND WRITES

The RTCSYNC bit indicates a time window during which the RTCC Clock Domain registers can be safely read and written without concern about a rollover. When RTCSYNC = 0, the registers can be safely accessed by the CPU.

Whether RTCSYNC = 1 or 0, the user should employ a firmware solution to ensure that the data read did not fall on a rollover boundary, resulting in an invalid or partial read. This firmware solution would consist of reading each register twice and then comparing the two values. If the two values matched, then, a rollover did not occur.

## 17.2.7 WRITE LOCK

In order to perform a write to any of the RTCC Timer registers, the RTCWREN bit (RTCCFG<5>) must be set.

To avoid accidental writes to the RTCC Timer register, it is recommended that the RTCWREN bit (RTCCFG<5>) be kept clear at any time other than while writing to. For the RTCWREN bit to be set, there is only one instruction cycle time window allowed between the 55h/AA sequence and the setting of RTCWREN. For that reason, it is recommended that users follow the code example in Example 17-1.

## EXAMPLE 17-1: SETTING THE RTCWREN BIT

| movlb | 0x0f       |

|-------|------------|

| movlw | 0x55       |

| movwf | EECON2,0   |

| movlw | 0xAA       |

| movwf | EECON2,0   |

| bsf   | RTCCFG,5,1 |

### 17.2.8 REGISTER MAPPING

To limit the register interface, the RTCC Timer and Alarm Timer registers are accessed through corresponding register pointers. The RTCC Value register window (RTCVALH and RTCVALL) uses the RTCPTR bits (RTCCFG<1:0>) to select the required Timer register pair.

By reading or writing to the RTCVALH register, the RTCC Pointer value (RTCPTR<1:0>) decrements by 1 until it reaches '00'. Once it reaches '00', the MINUTES and SECONDS value will be accessible through RTCVALH and RTCVALL until the pointer value is manually changed.

## REGISTER 19-6: SSPxCON1: MSSPx CONTROL REGISTER 1 – I<sup>2</sup>C<sup>™</sup> MODE (ACCESS FC6h/F72h)

| R/W-0 | R/W-0 | R/W-0                | R/W-0 | R/W-0                | R/W-0                | R/W-0                | R/W-0                |

|-------|-------|----------------------|-------|----------------------|----------------------|----------------------|----------------------|

| WCOL  | SSPOV | SSPEN <sup>(1)</sup> | CKP   | SSPM3 <sup>(2)</sup> | SSPM2 <sup>(2)</sup> | SSPM1 <sup>(2)</sup> | SSPM0 <sup>(2)</sup> |

| bit 7 |       |                      |       |                      |                      |                      | bit 0                |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7   | WCOL: Write Collision Detect bit                                                                                                                                                 |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | In Master Transmit mode:                                                                                                                                                         |

|         | 1 = A write to the SSPxBUF register was attempted while the I <sup>2</sup> C conditions were not valid for a                                                                     |

|         | transmission to be started (must be cleared in software)                                                                                                                         |

|         | 0 = No collision                                                                                                                                                                 |

|         | In Slave Transmit mode:<br>1 = The SSPxBUF register is written while it is still transmitting the previous word (must be cleared in                                              |

|         | software)                                                                                                                                                                        |

|         | 0 = No collision                                                                                                                                                                 |

|         | In Receive mode (Master or Slave modes):                                                                                                                                         |

|         | This is a "don't care" bit.                                                                                                                                                      |

| bit 6   | SSPOV: Receive Overflow Indicator bit                                                                                                                                            |

|         | In Receive mode:                                                                                                                                                                 |

|         | 1 = A byte is received while the SSPxBUF register is still holding the previous byte (must be cleared in                                                                         |

|         | software)<br>0 = No overflow                                                                                                                                                     |

|         | In Transmit mode:                                                                                                                                                                |

|         | This is a "don't care" bit in Transmit mode.                                                                                                                                     |

| bit 5   | SSPEN: Master Synchronous Serial Port Enable bit <sup>(1)</sup>                                                                                                                  |

| bit o   | 1 = Enables the serial port and configures the SDAx and SCLx pins as the serial port pins                                                                                        |

|         | 0 = Disables serial port and configures these pins as I/O port pins                                                                                                              |

| bit 4   | CKP: SCKx Release Control bit                                                                                                                                                    |

|         | In Slave mode:                                                                                                                                                                   |

|         | 1 = Releases clock                                                                                                                                                               |

|         | 0 = Holds clock low (clock stretch); used to ensure data setup time                                                                                                              |

|         | In Master mode:                                                                                                                                                                  |

|         | Unused in this mode.                                                                                                                                                             |

| bit 3-0 | <b>SSPM&lt;3:0&gt;:</b> Master Synchronous Serial Port Mode Select bits <sup>(2)</sup>                                                                                           |

|         | 1111 = I <sup>2</sup> C Slave mode, 10-bit address with Start and Stop bit interrupts enabled $1110 = I^2C$ Slave mode, 7-bit address with Start and Stop bit interrupts enabled |

|         | $1011 = I^2C$ Firmware Controlled Master mode (slave Idle)                                                                                                                       |

|         | 1001 = Load SSPxMSK register at SSPxADD SFR address(3,4)                                                                                                                         |

|         | 1000 = I <sup>2</sup> C Master mode, clock = Fosc/(4 * (SSPxADD + 1))                                                                                                            |

|         | $0111 = I^2C$ Slave mode, 10-bit address                                                                                                                                         |

|         | 0110 = I <sup>2</sup> C Slave mode, 7-bit address                                                                                                                                |

| Note 1: | When enabled, the SDAx and SCLx pins must be configured as inputs.                                                                                                               |

| 2:      | Bit combinations not specifically listed here are either reserved or implemented in SPI mode only.                                                                               |

| 3:      | When SSPM<3:0> = 1001, any reads or writes to the SSPxADD SFR address actually accesses the                                                                                      |

|         | SSPxMSK register.                                                                                                                                                                |

| 4.      | This mode is only available when 7-Bit Address Masking mode is selected (MSSPMSK Configuration bit is '1')                                                                       |

4: This mode is only available when 7-Bit Address Masking mode is selected (MSSPMSK Configuration bit is '1').

## 19.5.14 SLEEP OPERATION

While in Sleep mode, the  $I^2C$  module can receive addresses or data and when an address match or complete byte transfer occurs, wake the processor from Sleep (if the MSSP interrupt is enabled).

## 19.5.15 EFFECTS OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

## 19.5.16 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the Start and Stop conditions allows the determination of when the bus is free. The Start and Stop bits are cleared from a Reset or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit (SSPxSTAT<4>) is set, or the bus is Idle, with both the Start and Stop bits clear. When the bus is busy, enabling the MSSP interrupt will generate the interrupt when the Stop condition occurs.

In multi-master operation, the SDAx line must be monitored for arbitration to see if the signal level is the expected output level. This check is performed in hardware with the result placed in the BCLxIF bit.

The states where arbitration can be lost are:

- · Address Transfer

- Data Transfer

- · A Start Condition

- · A Repeated Start Condition

- An Acknowledge Condition

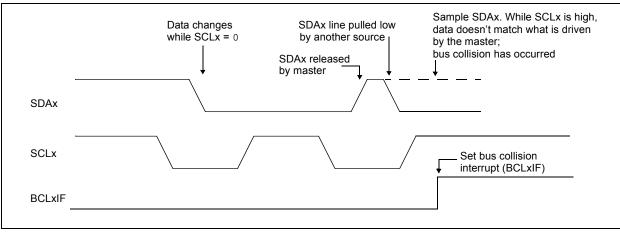

### 19.5.17 MULTI -MASTER COMMUNICATION, BUS COLLISION AND BUS ARBITRATION

Multi-Master mode support is achieved by bus arbitration. When the master outputs address/data bits onto the SDAx pin, arbitration takes place when the master outputs a '1' on SDAx, by letting SDAx float high and another master asserts a '0'. When the SCLx pin floats high, data should be stable. If the expected data on SDAx is a '1' and the data sampled on the SDAx pin = 0, then a bus collision has taken place. The master will set the Bus Collision Interrupt Flag, BCLxIF, and reset the  $I^2C$  port to its Idle state (Figure 19-27).

If a transmit was in progress when the bus collision occurred, the transmission is halted, the BF flag is cleared, the SDAx and SCLx lines are deasserted and the SSPxBUF can be written to. When the user services the bus collision Interrupt Service Routine and if the  $I^2C$  bus is free, the user can resume communication by asserting a Start condition.

If a Start, Repeated Start, Stop or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDAx and SCLx lines are deasserted and the respective control bits in the SSPxCON2 register are cleared. When the user services the bus collision Interrupt Service Routine (ISR), and if the  $I^2C$  bus is free, the user can resume communication by asserting a Start condition.

The master will continue to monitor the SDAx and SCLx pins. If a Stop condition occurs, the SSPxIF bit will be set.

A write to the SSPxBUF will start the transmission of data at the first data bit regardless of where the transmitter left off when the bus collision occurred.

In Multi-Master mode, the interrupt generation on the detection of Start and Stop conditions allows the determination of when the bus is free. Control of the  $I^2C$  bus can be taken when the Stop bit is set in the SSPxSTAT register, or the bus is Idle and the Start and Stop bits are cleared.

### FIGURE 19-27: BUS COLLISION TIMING FOR TRANSMIT AND ACKNOWLEDGE

|             |                       | SYNC = 0, BRGH = 0, BRG16 = 0 |                             |                       |            |                             |                       |            |                             |                       |            |                             |  |  |

|-------------|-----------------------|-------------------------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|--|--|

| BAUD        | Fosc = 40.000 MHz     |                               |                             | Fosc = 20.000 MHz     |            |                             | Fosc = 10.000 MHz     |            |                             | Fosc = 8.000 MHz      |            |                             |  |  |

| RATE<br>(K) | Actual<br>Rate<br>(K) | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |

| 0.3         | _                     |                               |                             |                       |            |                             |                       |            | _                           | _                     | _          | _                           |  |  |

| 1.2         | —                     | —                             | —                           | 1.221                 | 1.73       | 255                         | 1.202                 | 0.16       | 129                         | 1.201                 | -0.16      | 103                         |  |  |

| 2.4         | 2.441                 | 1.73                          | 255                         | 2.404                 | 0.16       | 129                         | 2.404                 | 0.16       | 64                          | 2.403                 | -0.16      | 51                          |  |  |

| 9.6         | 9.615                 | 0.16                          | 64                          | 9.766                 | 1.73       | 31                          | 9.766                 | 1.73       | 15                          | 9.615                 | -0.16      | 12                          |  |  |

| 19.2        | 19.531                | 1.73                          | 31                          | 19.531                | 1.73       | 15                          | 19.531                | 1.73       | 7                           | _                     | _          | _                           |  |  |

| 57.6        | 56.818                | -1.36                         | 10                          | 62.500                | 8.51       | 4                           | 52.083                | -9.58      | 2                           | —                     | _          | _                           |  |  |

| 115.2       | 125.000               | 8.51                          | 4                           | 104.167               | -9.58      | 2                           | 78.125                | -32.18     | 1                           | —                     | _          | _                           |  |  |

## TABLE 20-3: BAUD RATES FOR ASYNCHRONOUS MODES

|              | SYNC = 0, BRGH = 0, BRG16 = 0 |            |                             |                       |            |                             |                       |            |                             |  |  |

|--------------|-------------------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|--|--|

| BAUD<br>RATE | Fos                           | c = 4.000  | MHz                         | Fos                   | c = 2.000  | MHz                         | Fosc = 1.000 MHz      |            |                             |  |  |

| (K)          | Actual<br>Rate<br>(K)         | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |

| 0.3          | 0.300                         | 0.16       | 207                         | 0.300                 | -0.16      | 103                         | 0.300                 | -0.16      | 51                          |  |  |

| 1.2          | 1.202                         | 0.16       | 51                          | 1.201                 | -0.16      | 25                          | 1.201                 | -0.16      | 12                          |  |  |

| 2.4          | 2.404                         | 0.16       | 25                          | 2.403                 | -0.16      | 12                          | _                     | _          | _                           |  |  |

| 9.6          | 8.929                         | -6.99      | 6                           | _                     | _          | _                           | _                     | _          | _                           |  |  |

| 19.2         | 20.833                        | 8.51       | 2                           | —                     | _          | _                           | —                     | _          | _                           |  |  |

| 57.6         | 62.500                        | 8.51       | 0                           | —                     | _          | _                           | —                     | _          | _                           |  |  |

| 115.2        | 62.500                        | -45.75     | 0                           | _                     | _          | —                           | _                     | —          | —                           |  |  |

|              |                   | SYNC = 0, BRGH = 1, BRG16 = 0 |                             |                       |                   |                             |                       |                  |                             |                       |            |                             |  |  |

|--------------|-------------------|-------------------------------|-----------------------------|-----------------------|-------------------|-----------------------------|-----------------------|------------------|-----------------------------|-----------------------|------------|-----------------------------|--|--|

| BAUD<br>RATE | FOSC = 40.000 MHZ |                               | Fosc = 20.000 MHz           |                       | Fosc = 10.000 MHz |                             |                       | Fosc = 8.000 MHz |                             |                       |            |                             |  |  |

| (K)          | Actual            |                               | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error        | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error       | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |

| 0.3          | —                 | _                             | _                           | —                     | _                 | _                           | _                     | _                | _                           | _                     | _          | _                           |  |  |

| 1.2          | —                 | —                             | —                           | —                     | —                 | —                           | —                     | —                | —                           | —                     | —          | —                           |  |  |

| 2.4          | —                 | _                             | _                           | —                     | _                 | _                           | 2.441                 | 1.73             | 255                         | 2.403                 | -0.16      | 207                         |  |  |

| 9.6          | 9.766             | 1.73                          | 255                         | 9.615                 | 0.16              | 129                         | 9.615                 | 0.16             | 64                          | 9615.                 | -0.16      | 51                          |  |  |

| 19.2         | 19.231            | 0.16                          | 129                         | 19.231                | 0.16              | 64                          | 19.531                | 1.73             | 31                          | 19.230                | -0.16      | 25                          |  |  |

| 57.6         | 58.140            | 0.94                          | 42                          | 56.818                | -1.36             | 21                          | 56.818                | -1.36            | 10                          | 55.555                | 3.55       | 8                           |  |  |

| 115.2        | 113.636           | -1.36                         | 21                          | 113.636               | -1.36             | 10                          | 125.000               | 8.51             | 4                           | —                     | _          | _                           |  |  |

|       | SYNC = 0, BRGH = 1, BRG16 = 0 |                         |     |                                            |           |                       |                  |                             |     |  |  |  |

|-------|-------------------------------|-------------------------|-----|--------------------------------------------|-----------|-----------------------|------------------|-----------------------------|-----|--|--|--|

| BAUD  | Foso                          | c = 4.000               | MHz | Fos                                        | c = 2.000 | MHz                   | Fosc = 1.000 MHz |                             |     |  |  |  |

| (K)   | Actual<br>Rate<br>(K)         | Rate <sup>%</sup> value |     | Actual % SPBRG<br>Rate Error (K) (decimal) |           | Actual<br>Rate<br>(K) | %<br>Error       | SPBRG<br>value<br>(decimal) |     |  |  |  |

| 0.3   |                               |                         | _   |                                            |           | _                     | 0.300            | -0.16                       | 207 |  |  |  |

| 1.2   | 1.202                         | 0.16                    | 207 | 1.201                                      | -0.16     | 103                   | 1.201            | -0.16                       | 51  |  |  |  |

| 2.4   | 2.404                         | 0.16                    | 103 | 2.403                                      | -0.16     | 51                    | 2.403            | -0.16                       | 25  |  |  |  |

| 9.6   | 9.615                         | 0.16                    | 25  | 9.615                                      | -0.16     | 12                    | _                | _                           | _   |  |  |  |

| 19.2  | 19.231                        | 0.16                    | 12  | _                                          | _         | _                     | _                | _                           | _   |  |  |  |

| 57.6  | 62.500                        | 8.51                    | 3   | _                                          | _         | _                     | _                | _                           | _   |  |  |  |

| 115.2 | 125.000                       | 8.51                    | 1   | _                                          | _         | —                     | _                | _                           | _   |  |  |  |

© 2011 Microchip Technology Inc.

|                       |                                                                                                                                           |                                |                  |                   | •              |                 | ,               |  |  |  |  |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|------------------|-------------------|----------------|-----------------|-----------------|--|--|--|--|

| R/W-0                 | R/W-0                                                                                                                                     | R/W-0                          | R/W-1            | R/W-1             | R/W-1          | R/W-1           | R/W-1           |  |  |  |  |

| CON                   | COE                                                                                                                                       | CPOL                           | EVPOL1           | EVPOL0            | CREF           | CCH1            | CCH0            |  |  |  |  |

| bit 7                 |                                                                                                                                           |                                |                  |                   |                | •               | bit             |  |  |  |  |

| Logondi               |                                                                                                                                           |                                |                  |                   |                |                 |                 |  |  |  |  |

| Legend:<br>R = Readab | la hit                                                                                                                                    | W = Writable                   | h it             |                   | opted bit read | d oo 'O'        |                 |  |  |  |  |

|                       |                                                                                                                                           |                                |                  | U = Unimplem      |                |                 |                 |  |  |  |  |

| -n = Value a          | IT POR                                                                                                                                    | '1' = Bit is set               |                  | '0' = Bit is clea | ared           | x = Bit is unkr | nown            |  |  |  |  |

| bit 7                 | CON: Compa                                                                                                                                | arator Enable b                | it               |                   |                |                 |                 |  |  |  |  |

|                       | 1 = Compara                                                                                                                               | tor is enabled tor is disabled |                  |                   |                |                 |                 |  |  |  |  |

| bit 6                 | COE: Comparator Output Enable bit                                                                                                         |                                |                  |                   |                |                 |                 |  |  |  |  |

|                       | 1 = Comparator output is present on the CxOUT pin (assigned in PPS module)                                                                |                                |                  |                   |                |                 |                 |  |  |  |  |

|                       | 0 = Compara                                                                                                                               | tor output is int              | ernal only       |                   |                |                 |                 |  |  |  |  |

| bit 5                 | CPOL: Comparator Output Polarity Select bit                                                                                               |                                |                  |                   |                |                 |                 |  |  |  |  |

|                       | 1 = Comparator output is inverted                                                                                                         |                                |                  |                   |                |                 |                 |  |  |  |  |

|                       | 0 = Compara                                                                                                                               | tor output is no               | t inverted       |                   |                |                 |                 |  |  |  |  |

| bit 4-3               | EVPOL<1:0>: Interrupt Polarity Select bits                                                                                                |                                |                  |                   |                |                 |                 |  |  |  |  |

|                       | 11 = Interrupt generation on any change of the output <sup>(1)</sup>                                                                      |                                |                  |                   |                |                 |                 |  |  |  |  |

|                       | 10 = Interrupt generation only on high-to-low transition of the output                                                                    |                                |                  |                   |                |                 |                 |  |  |  |  |

|                       | <ul> <li>01 = Interrupt generation only on low-to-high transition of the output</li> <li>00 = Interrupt generation is disabled</li> </ul> |                                |                  |                   |                |                 |                 |  |  |  |  |

| bit 2                 | •                                                                                                                                         | •                              |                  | non-invertina inr | out)           |                 |                 |  |  |  |  |

|                       | <b>CREF:</b> Comparator Reference Select bit (non-inverting input)<br>1 = Non-inverting input connects to internal CVREF voltage          |                                |                  |                   |                |                 |                 |  |  |  |  |

|                       |                                                                                                                                           | rting input conr               |                  | 0                 |                |                 |                 |  |  |  |  |

| bit 1-0               | CCH<1:0>: (                                                                                                                               | Comparator Cha                 | annel Select bi  | ts                |                |                 |                 |  |  |  |  |

|                       | 11 = Invertir                                                                                                                             | ng input of com                | parator connec   | ts to VIRV        |                |                 |                 |  |  |  |  |

|                       |                                                                                                                                           |                                | ng input of com  | parator connec    | ts to C2INB pi | n; for CM2CON   | I, reserved     |  |  |  |  |

|                       | 01 = Reserv                                                                                                                               |                                | norator connor   | to to CVIND nin   |                |                 |                 |  |  |  |  |

|                       |                                                                                                                                           | ig input of com                | parator connec   | ts to CxINB pin   |                |                 |                 |  |  |  |  |

| Note 1: T             | he CMxIF is aut                                                                                                                           | omatically set a               | any time this mo | ode is selected a | and must be cl | eared by the ap | oplication afte |  |  |  |  |

|                       | 1                                                                                                                                         | 1 <sup>4</sup>                 |                  |                   |                |                 |                 |  |  |  |  |

## REGISTER 22-1: CMxCON: COMPARATOR CONTROL x REGISTER (ACCESS FD2h/FD1h)

the initial configuration.

## PIC18F46J11 FAMILY

| RCA                                                                                                                                                                                                                                                                                                                                                                | LL              | all                                        |               |     |     |                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------------------------------|---------------|-----|-----|------------------------------------------------------------------|

| Synta                                                                                                                                                                                                                                                                                                                                                              | ax:             | RCALL n                                    |               |     |     |                                                                  |

| Oper                                                                                                                                                                                                                                                                                                                                                               | ands:           | -1024 ≤ n ≤                                | 1023          |     |     |                                                                  |

| Oper                                                                                                                                                                                                                                                                                                                                                               | ation:          | (PC) + 2 →<br>(PC) + 2 + 2                 | -             | ;   |     |                                                                  |

| Statu                                                                                                                                                                                                                                                                                                                                                              | s Affected:     | None                                       |               |     |     |                                                                  |

| Enco                                                                                                                                                                                                                                                                                                                                                               | ding:           | 1101                                       | 1nnn          | nnn | n   | nnnn                                                             |

| Description: Subroutine call with a jump up to 1K<br>from the current location. First, return<br>address (PC + 2) is pushed onto the<br>stack. Then, add the 2's complemen<br>number '2n' to the PC. Since the PC<br>will have incremented to fetch the ne<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is a<br>two-cycle instruction. |                 |                                            |               |     |     | t, return<br>nto the<br>blement<br>the PC<br>the next<br>vill be |

| Word                                                                                                                                                                                                                                                                                                                                                               | ls:             | 1                                          |               |     |     |                                                                  |

| Cycle                                                                                                                                                                                                                                                                                                                                                              | es:             | 2                                          |               |     |     |                                                                  |

| QC                                                                                                                                                                                                                                                                                                                                                                 | ycle Activity:  |                                            |               |     |     |                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                    | Q1              | Q2                                         | Q3            | 3   |     | Q4                                                               |

|                                                                                                                                                                                                                                                                                                                                                                    | Decode          | Read literal<br>'n'<br>PUSH PC<br>to stack | Proce<br>Data |     | Wri | te to PC                                                         |

|                                                                                                                                                                                                                                                                                                                                                                    | No<br>operation | No<br>operation                            | No<br>operat  |     | ор  | No<br>eration                                                    |

Example: HERE RCALL Jump

Before Instruction

PC = Address (HERE) After Instruction PC = Address (Jump) TOS = Address (HERE + 2)

| RESET          |       | Reset          |                                                                         |       |                 |      |  |  |  |

|----------------|-------|----------------|-------------------------------------------------------------------------|-------|-----------------|------|--|--|--|

| Syntax:        |       | RESET          |                                                                         |       |                 |      |  |  |  |

| Operands:      |       | None           |                                                                         |       |                 |      |  |  |  |

| Operation:     |       |                | Reset all registers and flags that are affected by a MCLR Reset.        |       |                 |      |  |  |  |

| Status Affecte | ed:   | All            |                                                                         |       |                 |      |  |  |  |

| Encoding:      |       | 0000           | 0000                                                                    | 111   | 1               | 1111 |  |  |  |

| Description:   |       |                | This instruction provides a way to<br>execute a MCLR Reset in software. |       |                 |      |  |  |  |

| Words:         |       | 1              |                                                                         |       |                 |      |  |  |  |

| Cycles:        |       | 1              |                                                                         |       |                 |      |  |  |  |

| Q Cycle Acti   | vity: |                |                                                                         |       |                 |      |  |  |  |

| Q1             | l     | Q2             | Q                                                                       | 3     |                 | Q4   |  |  |  |

| Deco           | de    | Start<br>reset | No<br>opera                                                             | ,<br> | No<br>operation |      |  |  |  |

| Example:       |       | RESET          |                                                                         |       |                 |      |  |  |  |

| Instru | uctior | 1 |

|--------|--------|---|

| After Instruction |             |

|-------------------|-------------|

| Registers =       | Reset Value |

| Flags* =          | Reset Value |

#### 27.2.2 EXTENDED INSTRUCTION SET

| ADD   | FSR            | Add Liter        | Add Literal to FSR                    |        |          |  |  |  |  |  |

|-------|----------------|------------------|---------------------------------------|--------|----------|--|--|--|--|--|

| Synta | ax:            | ADDFSR           | f, k                                  |        |          |  |  |  |  |  |

| Oper  | ands:          | $0 \le k \le 63$ | $0 \leq k \leq 63$                    |        |          |  |  |  |  |  |

|       |                | f ∈ [ 0, 1,      | 2]                                    |        |          |  |  |  |  |  |

| Oper  | ation:         | FSR(f) + I       | $s \rightarrow FSR($                  | (f)    |          |  |  |  |  |  |

| Statu | s Affected:    | None             | None                                  |        |          |  |  |  |  |  |

| Enco  | oding:         | 1110             | 1000                                  | ffkk   | kkkk     |  |  |  |  |  |

| Desc  | ription:       | The 6-bit        | iteral 'k' i                          | s adde | d to the |  |  |  |  |  |

|       |                | contents of      | contents of the FSR specified by 'f'. |        |          |  |  |  |  |  |

| Word  | ls:            | 1                |                                       |        |          |  |  |  |  |  |

| Cycle | es:            | 1                | 1                                     |        |          |  |  |  |  |  |

| QC    | ycle Activity: |                  |                                       |        |          |  |  |  |  |  |

|       | Q1             | Q2               | Q3                                    |        | Q4       |  |  |  |  |  |

|       | Decode         | Read             | Proces                                | SS     | Write to |  |  |  |  |  |

|       |                | literal 'k'      | Data                                  | 1      | FSR      |  |  |  |  |  |

|       |                |                  |                                       |        |          |  |  |  |  |  |

ADDFSR 2, 0x23

03FFh

0422h

Example:

Before Instruction FSR2

After Instruction

FSR2

=

=

| ADDULNK                                                                                                                       | Add Literal to FSR2 and Return                                                                                           |                      |      |      |  |  |  |