Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 48MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 16                                                                          |

| Program Memory Size        | 32KB (16K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 3.8K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.15V ~ 3.6V                                                                |

| Data Converters            | A/D 10x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 28-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f25j11t-i-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                                                                                                                                                                                                                                                                                                                                                                          | Pin Nu                     | umber  |             |                |                                                                                                                                                                     |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--------|-------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin Name                                                                                                                                                                                                                                                                                                                                                                 | 28-SPDIP/<br>SSOP/<br>SOIC | 28-QFN | Pin<br>Type | Buffer<br>Type | Description                                                                                                                                                         |  |

| MCLR                                                                                                                                                                                                                                                                                                                                                                     | 1                          | 26     | I           | ST             | Master Clear (Reset) input. This pin is an active-low Reset to the device.                                                                                          |  |

| OSC1/CLKI/RA7<br>OSC1                                                                                                                                                                                                                                                                                                                                                    | 9                          | 6      | I           | ST             | Oscillator crystal input or external clock source<br>input. ST buffer when configured in RC mode;<br>CMOS otherwise. Main oscillator input<br>connection.           |  |

|                                                                                                                                                                                                                                                                                                                                                                          |                            |        | 1           | CMOS           | External clock source input; always associated with pin function OSC1 (see related OSC1/CLKI pins).                                                                 |  |

| RA7 <sup>(1)</sup><br>OSC2/CLKO/RA6                                                                                                                                                                                                                                                                                                                                      | 10                         | 7      | I/O         | TTL            | Digital I/O.<br>Oscillator crystal or clock output.                                                                                                                 |  |

| OSC2                                                                                                                                                                                                                                                                                                                                                                     |                            |        | 0           | —              | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode.                                                                             |  |

| CLKO                                                                                                                                                                                                                                                                                                                                                                     |                            |        | 0           | _              | Main oscillator feedback output connection.<br>In RC mode, OSC2 pin outputs CLKO, which<br>has 1/4 the frequency of OSC1 and denotes<br>the instruction cycle rate. |  |

| RA6 <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                       |                            |        | I/O         | TTL            | Digital I/O.                                                                                                                                                        |  |

| Legend:       TTL = TTL compatible input       CMOS       = CMOS compatible input or output         ST = Schmitt Trigger input with CMOS levels       Analog       = Analog input         I = Input       O       = Output         P = Power       OD       = Open-Drain (no P diode to VDD)         DIG = Digital output       O       = Open-Drain (no P diode to VDD) |                            |        |             |                |                                                                                                                                                                     |  |

#### TABLE 1-3:PIC18F2XJ11 PINOUT I/O DESCRIPTIONS

Note 1: RA7 and RA6 will be disabled if OSC1 and OSC2 are used for the clock function.

### 7.5 Writing to Flash Program Memory

The programming block is 32 words or 64 bytes. Programming one word or 2 bytes at a time is also supported.

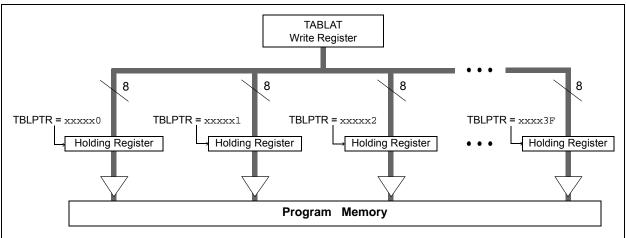

Table writes are used internally to load the holding registers needed to program the Flash memory. There are 64 holding registers used by the table writes for programming.

Since the Table Latch (TABLAT) is only a single byte, the TBLWT instruction may need to be executed 64 times for each programming operation (if WPROG = 0). All of the table write operations will essentially be short writes because only the holding registers are written. At the end of updating the 64 holding registers, the EECON1 register must be written to in order to start the programming operation with a long write.

The long write is necessary for programming the internal Flash. Instruction execution is halted while in a long write cycle. The long write will be terminated by the internal programming timer.

The on-chip timer controls the write time. The write/erase voltages are generated by an on-chip charge pump, rated to operate over the voltage range of the device.

- Note 1: Unlike previous PIC<sup>®</sup> devices, devices of the PIC18F46J11 family do not reset the holding registers after a write occurs. The holding registers must be cleared or overwritten before a programming sequence.

- 2: To maintain the endurance of the program memory cells, each Flash byte should not be programmed more than once between erase operations. Before attempting to modify the contents of the target cell a second time, an erase of the target page, or a bulk erase of the entire memory, must be performed.

#### 7.5.1 FLASH PROGRAM MEMORY WRITE SEQUENCE

The sequence of events for programming an internal program memory location should be:

- 1. Read 1024 bytes into RAM.

- 2. Update data values in RAM as necessary.

- 3. Load Table Pointer register with address being erased.

- 4. Execute the erase procedure.

- 5. Load Table Pointer register with address of first byte being written, minus 1.

- 6. Write the 64 bytes into the holding registers with auto-increment.

- Set the WREN bit (EECON1<2>) to enable byte writes.

- 8. Disable interrupts.

- 9. Write 55h to EECON2.

- 10. Write 0AAh to EECON2.

- 11. Set the WR bit. This will begin the write cycle.

- 12. The CPU will stall for the duration of the write for TIW (see parameter D133A).

- 13. Re-enable interrupts.

- 14. Repeat steps 6 through 13 until all 1024 bytes are written to program memory.

- 15. Verify the memory (table read).

An example of the required code is provided in Example 7-3 on the following page.

Note: Before setting the WR bit, the Table Pointer address needs to be within the intended address range of the 64 bytes in the holding register.

### REGISTER 9-3: INTCON3: INTERRUPT CONTROL REGISTER 3 (ACCESS FF0h)

| R/W-1      | R/W-1                                                            | R/W-0                                                 | R/W-0            | R/W-0                  | R/W-0           | R/W-0             | R/W-0  |

|------------|------------------------------------------------------------------|-------------------------------------------------------|------------------|------------------------|-----------------|-------------------|--------|

| INT2IP     | INT1IP                                                           | INT3IE                                                | INT2IE           | INT1IE                 | INT3IF          | INT2IF            | INT1IF |

| bit 7      |                                                                  |                                                       |                  |                        |                 |                   | bit (  |

| Legend:    |                                                                  |                                                       |                  |                        |                 |                   |        |

| R = Reada  | ıble bit                                                         | W = Writable                                          | bit              | U = Unimplen           | nented bit, rea | d as '0'          |        |

| -n = Value |                                                                  | '1' = Bit is set                                      |                  | '0' = Bit is cle       |                 | x = Bit is unkr   | nown   |

| bit 7      | 1 = High prio                                                    | •                                                     | upt Priority bit |                        |                 |                   |        |

| bit 6      | 0 = Low prior<br>INT1IP: INT1<br>1 = High prior<br>0 = Low prior | External Interr                                       | upt Priority bit |                        |                 |                   |        |

| bit 5      | INT3IE: INT3<br>1 = Enables                                      | External Interr<br>the INT3 extern<br>the INT3 extern | nal interrupt    |                        |                 |                   |        |

| bit 4      | 1 = Enables                                                      | External Interr<br>the INT2 extern<br>the INT2 exter  | nal interrupt    |                        |                 |                   |        |

| bit 3      | 1 = Enables                                                      | External Interr<br>the INT1 extern<br>the INT1 exter  | nal interrupt    |                        |                 |                   |        |

| bit 2      | 1 = The INT3                                                     | External Interr<br>external interr<br>external interr | upt occurred (   | must be cleared        | d in software)  |                   |        |

| bit 1      | 1 = The INT2                                                     | External Interr<br>external interr<br>external interr | upt occurred (   | must be cleared        | d in software)  |                   |        |

| bit 0      | 1 = The INT1                                                     | External Interr<br>external interr<br>external interr | rupt occurred (  | must be cleared<br>cur | d in software)  |                   |        |

|            | Interrupt flag bits<br>enable bit or the 0<br>are clear prior to | Global Interrupt                                      | Enable bit. Us   | ser software sho       | ould ensure the | e appropriate int |        |

| Pin        | Function | TRIS<br>Setting | I/O                          | I/O<br>Type                | Description                                                                             |  |

|------------|----------|-----------------|------------------------------|----------------------------|-----------------------------------------------------------------------------------------|--|

| RC0/T1OSO/ | RC0      | 1               | I                            | ST                         | PORTC<0> data input.                                                                    |  |

| T1CKI/RP11 |          | 0               | 0 O DIG LATC<0> data output. |                            | LATC<0> data output.                                                                    |  |

|            | T10S0    | x               | 0                            | ANA                        | Timer1 oscillator output; enabled when Timer1 oscillator enabled. Disables digital I/O. |  |

|            | T1CKI    | 1               | Ι                            | ST                         | Timer1 counter input.                                                                   |  |

|            | RP11     | 1               | Ι                            | ST                         | Remappable peripheral pin 11 input.                                                     |  |

|            |          | 0               | 0                            | DIG                        | Remappable peripheral pin 11 output.                                                    |  |

| RC1/T1OSI/ | RC1      | 1               | Ι                            | ST                         | PORTC<1> data input.                                                                    |  |

| RP12       |          | 0               | 0                            | DIG                        | LATC<1> data output.                                                                    |  |

|            | T10SI    | x               | I                            | ANA                        | Timer1 oscillator input; enabled when Timer1 oscillator enabled. Disables digital I/O.  |  |

|            | RP12     | 1               | Ι                            | ST                         | Remappable peripheral pin 12 input.                                                     |  |

|            |          | 0               | 0                            | DIG                        | Remappable peripheral pin 12 output.                                                    |  |

| RC2/AN11/  | RC2      | 1               | Ι                            | ST                         | PORTC<2> data input.                                                                    |  |

| CTPLS/RP13 |          | 0               | 0                            | DIG                        | LATC<2> data output.                                                                    |  |

| _          | AN11     | 1               | Ι                            | ANA                        | A/D input channel 11.                                                                   |  |

|            | CTPLS    | 0               | 0                            | DIG                        |                                                                                         |  |

|            | RP13     | 1               | Ι                            | ST                         | Remappable peripheral pin 13 input.                                                     |  |

|            |          | 0               | 0                            | DIG                        | Remappable peripheral pin 13 output.                                                    |  |

| RC3/SCK1/  | RC3      | 1               | Ι                            | ST                         | PORTC<3> data input.                                                                    |  |

| SCL1/RP14  |          | 0               | 0                            | DIG                        | LATC<3> data output.                                                                    |  |

|            | SCK1     | 1               | Ι                            | ST                         | SPI clock input (MSSP1 module).                                                         |  |

|            |          | 0               | 0                            | DIG                        | SPI clock output (MSSP1 module).                                                        |  |

|            | SCL1     | 1               | I                            | I <sup>2</sup> C/<br>SMBus | I <sup>2</sup> C™ clock input (MSSP1 module).                                           |  |

|            |          | 0               | 0                            | DIG                        | I <sup>2</sup> C clock output (MSSP1 module).                                           |  |

|            | RP14     | 1               | Ι                            | ST                         | Remappable peripheral pin 14 input.                                                     |  |

|            |          | 0               | 0                            | DIG                        | Remappable peripheral pin 14 output.                                                    |  |

| RC4/SDI1/  | RC4      | 1               | Ι                            | ST                         | PORTC<4> data input.                                                                    |  |

| SDA1/RP15  |          | 0               | 0                            | DIG                        | LATC<4> data output.                                                                    |  |

|            | SDI1     | 1               | Ι                            | ST                         | SPI data input (MSSP1 module).                                                          |  |

|            | SDA1     | 1               | I                            | l <sup>2</sup> C/<br>SMBus | I <sup>2</sup> C data input (MSSP1 module).                                             |  |

|            |          | 0               | 0                            | DIG                        | I <sup>2</sup> C/SMBus.                                                                 |  |

|            | RP15     | 1               | Ι                            | ST                         | Remappable peripheral pin 15 input.                                                     |  |

|            |          | 0               | 0                            | DIG                        | Remappable peripheral pin 15 output.                                                    |  |

TABLE 10-7: PORTC I/O SUMMARY

**Legend:** DIG = Digital level output; TTL = TTL input buffer; ST = Schmitt Trigger input buffer; ANA = Analog level input/output; I<sup>2</sup>C/SMB = I<sup>2</sup>C/SMBus input buffer; x = Don't care (TRIS bit does not affect port direction or is overridden for this option)

Note 1: This bit is only available on 44-pin devices.

| REGISTER 10-6: | <b>RPINR1: PERIPHERAL</b> | <b>PIN SELECT INPUT</b> | <b>REGISTER 1</b> | (BANKED EE7h) |

|----------------|---------------------------|-------------------------|-------------------|---------------|

|----------------|---------------------------|-------------------------|-------------------|---------------|

| U-0   | U-0 | U-0 | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   |

|-------|-----|-----|---------|---------|---------|---------|---------|

| —     | —   | —   | INTR1R4 | INTR1R3 | INTR1R2 | INTR1R1 | INTR1R0 |

| bit 7 |     |     |         |         |         |         | bit 0   |

| Legend:           | R/W = Readable, Writable | $R/\overline{W}$ = Readable, Writable if IOLOCK = 0 |                    |  |  |  |  |

|-------------------|--------------------------|-----------------------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit         | U = Unimplemented bit, read as '0'                  |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set         | '0' = Bit is cleared                                | x = Bit is unknown |  |  |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 INTR1R<4:0>: Assign External Interrupt 1 (INT1) to the Corresponding RPn Pin bits

#### REGISTER 10-7: RPINR2: PERIPHERAL PIN SELECT INPUT REGISTER 2 (BANKED EE8h)

| U-0   | U-0 | U-0 | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   |

|-------|-----|-----|---------|---------|---------|---------|---------|

| —     | —   | —   | INTR2R4 | INTR2R3 | INTR2R2 | INTR2R1 | INTR2R0 |

| bit 7 |     |     |         |         |         |         | bit 0   |

| Legend:           | R/W = Readable, Writable | R/W = Readable, Writable if IOLOCK = 0 |                    |  |  |  |  |

|-------------------|--------------------------|----------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit         | U = Unimplemented bit, read as '0'     |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set         | '0' = Bit is cleared                   | x = Bit is unknown |  |  |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 INTR2R<4:0>: Assign External Interrupt 2 (INT2) to the Corresponding RPn pin bits

#### REGISTER 10-8: RPINR3: PERIPHERAL PIN SELECT INPUT REGISTER 3 (BANKED EE9h)

| U-0   | U-0 | U-0 | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   |

|-------|-----|-----|---------|---------|---------|---------|---------|

| —     | —   | —   | INTR3R4 | INTR3R3 | INTR3R2 | INTR3R1 | INTR3R0 |

| bit 7 |     |     |         |         |         |         | bit 0   |

| Legend:           | $R/\overline{W}$ = Readable, Writable i | $R/\overline{W}$ = Readable, Writable if IOLOCK = 0 |                    |  |  |  |  |

|-------------------|-----------------------------------------|-----------------------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit                        | U = Unimplemented bit, read as '0'                  |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set                        | '0' = Bit is cleared                                | x = Bit is unknown |  |  |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 INTR3R<4:0>: Assign External Interrupt 3 (INT3) to the Corresponding RPn Pin bits

### REGISTER 10-21: RPOR0: PERIPHERAL PIN SELECT OUTPUT REGISTER 0 (BANKED EC6h)<sup>(1)</sup>

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-------|-------|-------|

| —     | _   |     | RP0R4 | RP0R3 | RP0R2 | RP0R1 | RP0R0 |

| bit 7 |     |     |       |       |       |       | bit 0 |

| Legend:           | $R/\overline{W}$ = Readable, Writable if IOLOCK = 0 |                                    |                    |  |  |

|-------------------|-----------------------------------------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                                    | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP0R<4:0>:** Peripheral Output Function is Assigned to RP0 Output Pin bits (see Table 10-14 for peripheral function numbers)

**Note 1:** Register values can be changed only if PPSCON<IOLOCK> = 0.

#### REGISTER 10-22: RPOR1: PERIPHERAL PIN SELECT OUTPUT REGISTER 1 (BANKED EC7h)

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-------|-------|-------|

| —     | —   | —   | RP1R4 | RP1R3 | RP1R2 | RP1R1 | RP1R0 |

| bit 7 |     |     |       |       |       |       | bit 0 |

| Legend:           | $R/\overline{W}$ = Readable, Writable if IOLOCK = 0 |                                    |                    |  |  |

|-------------------|-----------------------------------------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                                    | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP1R<4:0>:** Peripheral Output Function is Assigned to RP1 Output Pin bits (see Table 10-14 for peripheral function numbers)

#### REGISTER 10-23: RPOR2: PERIPHERAL PIN SELECT OUTPUT REGISTER 2 (BANKED EC8h)

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-------|-------|-------|

| —     | _   |     | RP2R4 | RP2R3 | RP2R2 | RP2R1 | RP2R0 |

| bit 7 |     |     |       |       |       |       | bit 0 |

| Legend:           | $R/\overline{W}$ = Readable, Writable if IOLOCK = 0 |                                    |                    |  |  |

|-------------------|-----------------------------------------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                                    | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP2R<4:0>:** Peripheral Output Function is Assigned to RP2 Output Pin bits (see Table 10-14 for peripheral function numbers)

# REGISTER 11-5: PMEH: PARALLEL PORT ENABLE REGISTER HIGH BYTE (BANKED F57h)<sup>(1)</sup>

| U-0                             | R/W-0                     | U-0                | U-0                                | U-0                  | U-0 | U-0                | U-0   |  |

|---------------------------------|---------------------------|--------------------|------------------------------------|----------------------|-----|--------------------|-------|--|

| _                               | PTEN14                    | —                  |                                    | —                    | —   | _                  | —     |  |

| bit 7                           |                           |                    |                                    |                      |     |                    | bit 0 |  |

|                                 |                           |                    |                                    |                      |     |                    |       |  |

| Legend:                         |                           |                    |                                    |                      |     |                    |       |  |

| R = Readable bit W = Writable b |                           | oit                | U = Unimplemented bit, read as '0' |                      |     |                    |       |  |

| -n = Value a                    | it POR                    | '1' = Bit is set   |                                    | '0' = Bit is cleared |     | x = Bit is unknown |       |  |

|                                 |                           |                    |                                    |                      |     |                    |       |  |

| bit 7                           | Unimpleme                 | nted: Read as '0   | ,                                  |                      |     |                    |       |  |

| bit 6                           | PTEN14: PN                | ICS Port Enable    | bit                                |                      |     |                    |       |  |

|                                 | 1 = PMCS chip select line |                    |                                    |                      |     |                    |       |  |

|                                 | 0 = PMCS f                | unctions as port l | I/O                                |                      |     |                    |       |  |

| bit 5-0                         | Unimpleme                 | nted: Read as '0   | ,                                  |                      |     |                    |       |  |

Note 1: This register is only available in 44-pin devices.

## REGISTER 11-6: PMEL: PARALLEL PORT ENABLE REGISTER LOW BYTE (BANKED F56h)<sup>(1)</sup>

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| PTEN7 | PTEN6 | PTEN5 | PTEN4 | PTEN3 | PTEN2 | PTEN1 | PTEN0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 7-2 | PTEN<7:2>: PMP Address Port Enable bits                                                                                                            |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = PMA<7:2> function as PMP address lines                                                                                                         |

|         | 0 = PMA<7:2> function as port I/O                                                                                                                  |

| bit 1-0 | PTEN<1:0>: PMALH/PMALL Strobe Enable bits                                                                                                          |

|         | <ul> <li>1 = PMA&lt;1:0&gt; function as either PMA&lt;1:0&gt; or PMALH and PMALL</li> <li>0 = PMA&lt;1:0&gt; pads functions as port I/O</li> </ul> |

Note 1: This register is only available in 44-pin devices.

#### 18.5.3 START-UP CONSIDERATIONS

When any PWM mode is used, the application hardware must use the proper external pull-up and/or pull-down resistors on the PWM output pins.

| Note: | When the microcontroller is released from |  |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|--|

|       | Reset, all of the I/O pins are in the     |  |  |  |  |  |  |

|       | high-impedance state. The external        |  |  |  |  |  |  |

|       | circuits must keep the power switch       |  |  |  |  |  |  |

|       | devices in the OFF state until the micro- |  |  |  |  |  |  |

|       | controller drives the I/O pins with the   |  |  |  |  |  |  |

|       | proper signal levels or activates the PWM |  |  |  |  |  |  |

|       | output(s).                                |  |  |  |  |  |  |

The CCPxM<1:0> bits of the CCPxCON register allow the user to choose whether the PWM output signals are active-high or active-low for each pair of PWM output pins (PxA/PxC and PxB/PxD). The PWM output polarities must be selected before the PWM pin output drivers are enabled. Changing the polarity configuration while the PWM pin output drivers are enabled is not recommended since it may result in damage to the application circuits.

The PxA, PxB, PxC and PxD output latches may not be in the proper states when the PWM module is initialized. Enabling the PWM pin output drivers at the same time as the Enhanced PWM modes may cause damage to the application circuit. The Enhanced PWM modes must be enabled in the proper Output mode and complete a full PWM cycle before enabling the PWM pin output drivers. The completion of a full PWM cycle is indicated by the TMR2IF or TMR4IF bit of the PIR1 or PIR3 register being set as the second PWM period begins.

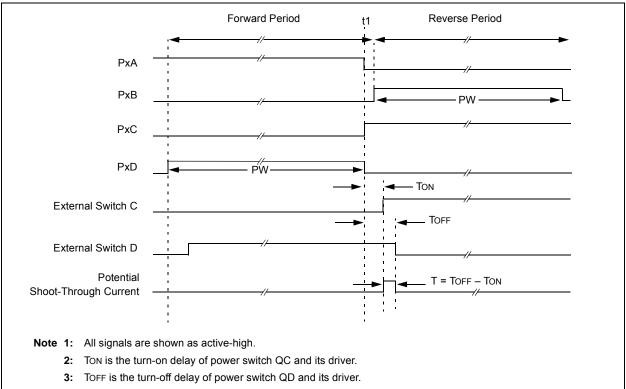

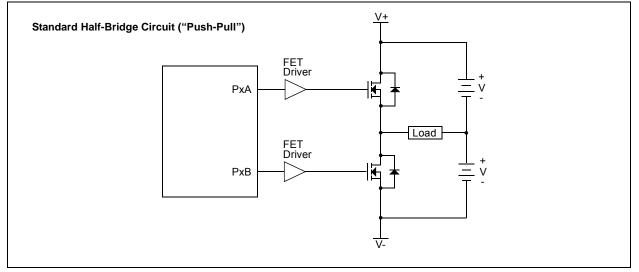

#### 18.5.6 PROGRAMMABLE DEAD-BAND DELAY MODE

In half-bridge applications, where all power switches are modulated at the PWM frequency, the power switches normally require more time to turn off than to turn on. If both the upper and lower power switches are switched at the same time (one turned on and the other turned off), both switches may be on for a short period until one switch completely turns off. During this brief interval, a very high current (shoot-through current) will flow through both power switches, shorting the bridge supply. To avoid this potentially destructive shoot-through current from flowing during switching, turning on either of the power switches is normally delayed to allow the other switch to completely turn off.

In Half-Bridge mode, a digitally programmable dead-band delay is available to avoid shoot-through current from destroying the bridge power switches. The delay occurs at the signal transition from the non-active state to the active state. See Figure 18-16 for illustration. The lower seven bits of the associated ECCPxDEL register (Register 18-3) sets the delay period in terms of microcontroller instruction cycles (TcY or 4 Tosc).

#### **EXAMPLE OF FIGURE 18-16:** HALF-BRIDGE PWM OUTPUT Period Period Pulse Width PxA(2) td I PxB(2) (1) ·(1) (1) td = Dead-Band Delay Note 1: At this time, the TMR2 register is equal to the PR2 register. 2: Output signals are shown as active-high.

#### FIGURE 18-17: EXAMPLE OF HALF-BRIDGE APPLICATIONS

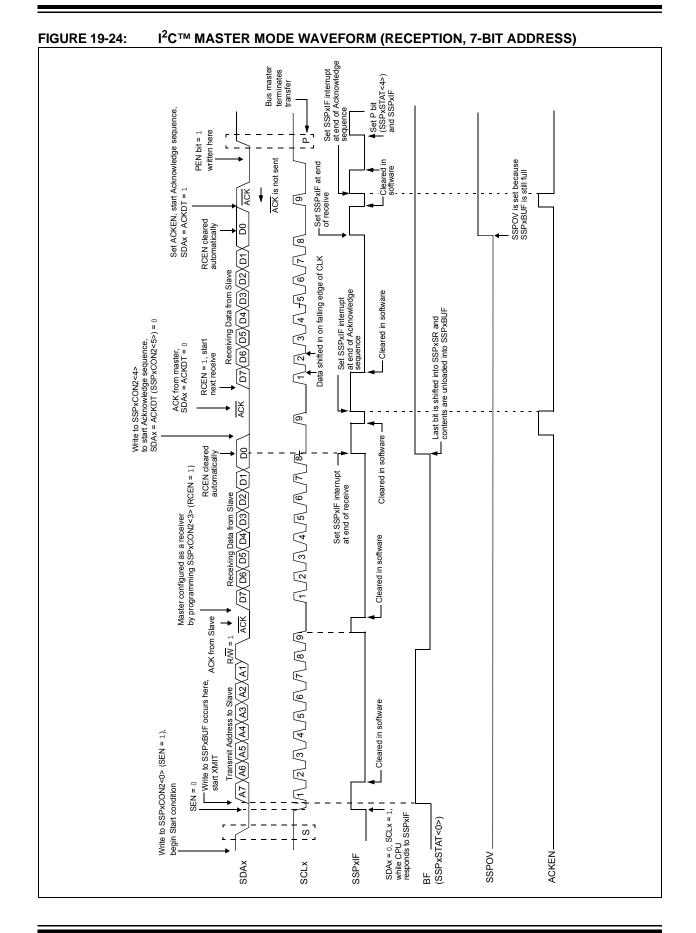

### 19.2 Control Registers

Each MSSP module has three associated control registers. These include a status register (SSPxSTAT) and two control registers (SSPxCON1 and SSPxCON2). The use of these registers and their individual Configuration bits differ significantly depending on whether the MSSP module is operated in SPI or I<sup>2</sup>C mode.

Additional details are provided under the individual sections.

Note: In devices with more than one MSSP module, it is very important to pay close attention to the SSPxCON register names. SSP1CON1 and SSP1CON2 control different operational aspects of the same module, while SSP1CON1 and SSP2CON1 control the same features for two different modules.

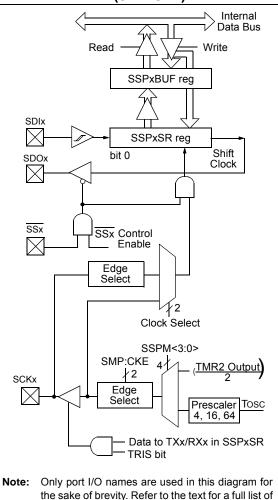

### 19.3 SPI Mode

The SPI mode allows 8 bits of data to be synchronously transmitted and received simultaneously. All four modes of SPI are supported.

When MSSP2 is used in SPI mode, it can optionally be configured to work with the SPI DMA submodule described in **Section 19.4 "SPI DMA Module"**.

To accomplish communication, typically three pins are used:

- Serial Data Out (SDOx) RC5/SDO1/RP16 or SDO2/Remappable

- Serial Data In (SDIx) RC4/SDI1/SDA1/RP15 or SDI2/Remappable

- Serial Clock (SCKx) RC3/SCK1/SCL1/RP14 or SCK2/Remappable

Additionally, a fourth pin may be used when in a Slave mode of operation:

Slave Select (SSx) – RA5/AN4/SS1/ HLVDIN/RP2 or SS2/Remappable

Figure 19-1 depicts the block diagram of the MSSP module when operating in SPI mode.

#### FIGURE 19-1: MSSPx BLOCK DIAGRAM (SPI MODE)

multiplexed functions.

#### 19.3.1 REGISTERS

Each MSSP module has four registers for SPI mode operation. These are:

- MSSPx Control Register 1 (SSPxCON1)

- MSSPx Status Register (SSPxSTAT)

- Serial Receive/Transmit Buffer Register (SSPxBUF)

- MSSPx Shift Register (SSPxSR) Not directly accessible

SSPxCON1 and SSPxSTAT are the control and status registers in SPI mode operation. The SSPxCON1 register is readable and writable. The lower six bits of the SSPxSTAT are read-only. The upper two bits of the SSPxSTAT are read/write.

SSPxSR is the shift register used for shifting data in or out. SSPxBUF is the buffer register to which data bytes are written to or read from.

In receive operations, SSPxSR and SSPxBUF together create a double-buffered receiver. When SSPxSR receives a complete byte, it is transferred to SSPxBUF and the SSPxIF interrupt is set.

transmission, the SSPxBUF During is not double-buffered. A write to SSPxBUF will write to both SSPxBUF and SSPxSR.

Because the SSPxBUF register is dou-Note: ble-buffered, using read-modify-write instructions such as BCF, COMF, etc., will not work. Similarly, when debugging under an in-circuit debugger, performing actions that cause reads of SSPxBUF (mouse hovering, watch, etc.) can consume data that the application code was expecting to receive.

| REGISTER 19-1: | SSPxSTAT: MSSPx STATUS REGISTER – SPI MODE (ACCESS FC7h/F73h) |  |

|----------------|---------------------------------------------------------------|--|

|----------------|---------------------------------------------------------------|--|

| R/W-0 | R/W-0              | R-0 | R-0 | R-0 | R-0 | R-0 | R-0   |

|-------|--------------------|-----|-----|-----|-----|-----|-------|

| SMP   | CKE <sup>(1)</sup> | D/A | Р   | S   | R/W | UA  | BF    |

| bit 7 |                    |     |     |     |     |     | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7   | SMP: Sample bit                                                                                             |

|---------|-------------------------------------------------------------------------------------------------------------|

|         | SPI Master mode:                                                                                            |

|         | 1 = Input data sampled at end of data output time                                                           |

|         | 0 = Input data sampled at middle of data output time                                                        |

|         | SPI Slave mode:                                                                                             |

|         | SMP must be cleared when SPI is used in Slave mode.                                                         |

| bit 6   | CKE: SPI Clock Select bit <sup>(1)</sup>                                                                    |

|         | 1 = Transmit occurs on transition from active to Idle clock state                                           |

|         | 0 = Transmit occurs on transition from Idle to active clock state                                           |

| bit 5   | D/A: Data/Address bit                                                                                       |

|         | Used in I <sup>2</sup> C™ mode only.                                                                        |

| bit 4   | P: Stop bit                                                                                                 |

|         | Used in I <sup>2</sup> C mode only; this bit is cleared when the MSSP module is disabled, SSPEN is cleared. |

| bit 3   | S: Start bit                                                                                                |

|         | Used in I <sup>2</sup> C mode only.                                                                         |

| bit 2   | R/W: Read/Write Information bit                                                                             |

|         | Used in I <sup>2</sup> C mode only.                                                                         |

| bit 1   | UA: Update Address bit                                                                                      |

|         | Used in I <sup>2</sup> C mode only.                                                                         |

| bit 0   | BF: Buffer Full Status bit                                                                                  |

|         | 1 = Receive complete, SSPxBUF is full                                                                       |

|         | 0 = Receive not complete, SSPxBUF is empty                                                                  |

| Note 1: | Polarity of clock state is set by the CKP bit (SSPxCON1<4>).                                                |

olarity of clock state is set by the CKP bit (SSPxCON1<4>).

| R/W-0         | R/W-0                             | R/W-0                                                 | R/W-0            | R/W-0                                 | R-0              | R-0               | R-x            |

|---------------|-----------------------------------|-------------------------------------------------------|------------------|---------------------------------------|------------------|-------------------|----------------|

| SPEN          | RX9                               | SREN                                                  | CREN             | ADDEN                                 | FERR             | OERR              | RX9D           |

| oit 7         |                                   |                                                       |                  |                                       |                  |                   | bit            |

| Legend:       |                                   |                                                       |                  |                                       |                  |                   |                |

| R = Readabl   | le bit                            | W = Writable I                                        | oit              | U = Unimplem                          | ented bit, read  | l as '0'          |                |

| -n = Value at | t POR                             | '1' = Bit is set                                      |                  | '0' = Bit is clea                     | ared             | x = Bit is unkn   | iown           |

| bit 7         | SPEN: Serial                      | Port Enable bit                                       | :                |                                       |                  |                   |                |

|               | 1 = Serial po                     | rt enabled                                            |                  |                                       |                  |                   |                |

|               | 0 = Serial po                     | rt disabled (hel                                      | d in Reset)      |                                       |                  |                   |                |

| bit 6         |                                   | eceive Enable b                                       | it               |                                       |                  |                   |                |

|               |                                   | <ul><li>bit reception</li><li>bit reception</li></ul> |                  |                                       |                  |                   |                |

| bit 5         | SREN: Single                      | e Receive Enab                                        | le bit           |                                       |                  |                   |                |

|               | <u>Asynchronou</u><br>Don't care. | <u>s mode</u> :                                       |                  |                                       |                  |                   |                |

|               |                                   | mode – Master                                         |                  |                                       |                  |                   |                |

|               | 0 = Disables                      | single receive<br>single receive<br>ared after recep  | ntion is comple  | ate                                   |                  |                   |                |

|               |                                   | mode – Slave:                                         |                  |                                       |                  |                   |                |

| bit 4         | CREN: Conti                       | nuous Receive                                         | Enable bit       |                                       |                  |                   |                |

|               | <u>Asynchronou</u><br>1 = Enables |                                                       |                  |                                       |                  |                   |                |

|               | 0 = Disables                      | receiver                                              |                  |                                       |                  |                   |                |

|               | Synchronous                       |                                                       |                  |                                       |                  |                   |                |

|               |                                   | continuous rece<br>continuous rec                     |                  | le bit, CREN, is                      | cleared (CREN    | N overrides SR    | EN)            |

| bit 3         | ADDEN: Add                        | ress Detect Ena                                       | able bit         |                                       |                  |                   |                |

|               |                                   | <u>s mode 9-Bit (R</u>                                |                  |                                       | la tha maasiya k |                   |                |

|               | 0 = Disables                      | address detect                                        | ion, all bytes a | nterrupt and load<br>are received and |                  |                   |                |

|               | <u>Asynchronou</u><br>Don't care. | <u>s mode 8-Bit (R</u>                                | <u>X9 = 0)</u> : |                                       |                  |                   |                |

| bit 2         | FERR: Frami                       | ng Error bit                                          |                  |                                       |                  |                   |                |

|               | 1 = Framing<br>0 = No frami       |                                                       | eared by read    | ling RCREGx re                        | gister and rece  | eiving next valio | d byte)        |

| bit 1         | OERR: Over                        | un Error bit                                          |                  |                                       |                  |                   |                |

|               |                                   | rror is cleared.                                      | leared by clea   | aring bit CREN).                      | UART reception   | on will be disca  | arded until th |

| bit 0         |                                   | of Received Da                                        | ata              |                                       |                  |                   |                |

|               |                                   |                                                       |                  |                                       |                  |                   |                |

|              |                       | SYNC = 0, BRGH = 0, BRG16 = 1 |                             |                       |            |                             |                       |            |                             |                       |            |                             |

|--------------|-----------------------|-------------------------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD<br>RATE | Fosc                  | = 40.000                      | ) MHz                       | Fosc                  | = 20.000   | ) MHz                       | Fosc                  | = 10.000   | ) MHz                       | Fosc = 8.000 MHz      |            |                             |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3          | 0.300                 | 0.00                          | 8332                        | 0.300                 | 0.02       | 4165                        | 0.300                 | 0.02       | 2082                        | 0.300                 | -0.04      | 1665                        |

| 1.2          | 1.200                 | 0.02                          | 2082                        | 1.200                 | -0.03      | 1041                        | 1.200                 | -0.03      | 520                         | 1.201                 | -0.16      | 415                         |

| 2.4          | 2.402                 | 0.06                          | 1040                        | 2.399                 | -0.03      | 520                         | 2.404                 | 0.16       | 259                         | 2.403                 | -0.16      | 207                         |

| 9.6          | 9.615                 | 0.16                          | 259                         | 9.615                 | 0.16       | 129                         | 9.615                 | 0.16       | 64                          | 9.615                 | -0.16      | 51                          |

| 19.2         | 19.231                | 0.16                          | 129                         | 19.231                | 0.16       | 64                          | 19.531                | 1.73       | 31                          | 19.230                | -0.16      | 25                          |

| 57.6         | 58.140                | 0.94                          | 42                          | 56.818                | -1.36      | 21                          | 56.818                | -1.36      | 10                          | 55.555                | 3.55       | 8                           |

| 115.2        | 113.636               | -1.36                         | 21                          | 113.636               | -1.36      | 10                          | 125.000               | 8.51       | 4                           | _                     | —          | —                           |

### TABLE 20-3: BAUD RATES FOR ASYNCHRONOUS MODES (CONTINUED)

|       |                       |            | S                           | YNC = 0, E            | = 0, BRGH = 0, BRG16 = 1 |                             |                       |                  |                             |  |  |

|-------|-----------------------|------------|-----------------------------|-----------------------|--------------------------|-----------------------------|-----------------------|------------------|-----------------------------|--|--|

| BAUD  | FOSC = 4.000  MHz     |            |                             | Fos                   | c = 2.000                | MHz                         | Fos                   | Fosc = 1.000 MHz |                             |  |  |

| (K)   | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error               | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error       | SPBRG<br>value<br>(decimal) |  |  |

| 0.3   | 0.300                 | 0.04       | 832                         | 0.300                 | -0.16                    | 415                         | 0.300                 | -0.16            | 207                         |  |  |

| 1.2   | 1.202                 | 0.16       | 207                         | 1.201                 | -0.16                    | 103                         | 1.201                 | -0.16            | 51                          |  |  |

| 2.4   | 2.404                 | 0.16       | 103                         | 2.403                 | -0.16                    | 51                          | 2.403                 | -0.16            | 25                          |  |  |

| 9.6   | 9.615                 | 0.16       | 25                          | 9.615                 | -0.16                    | 12                          | —                     | _                | _                           |  |  |

| 19.2  | 19.231                | 0.16       | 12                          | —                     | _                        | _                           | —                     | _                | _                           |  |  |

| 57.6  | 62.500                | 8.51       | 3                           | —                     | _                        | _                           | —                     | _                | _                           |  |  |

| 115.2 | 125.000               | 8.51       | 1                           | _                     | _                        | —                           | _                     | _                | _                           |  |  |

|              |                       | SYNC = 0, BRGH = 1, BRG16 = 1 or SYNC = 1, BRG16 = 1 |                             |                       |            |                             |                       |            |                             |                       |            |                             |

|--------------|-----------------------|------------------------------------------------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD<br>RATE | FOSC = 40.000 MHZ     |                                                      | ) MHz                       | Fosc = 20.000 MHz     |            |                             | Fosc = 10.000 MHz     |            |                             | Fosc = 8.000 MHz      |            |                             |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error                                           | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3          | 0.300                 | 0.00                                                 | 33332                       | 0.300                 | 0.00       | 16665                       | 0.300                 | 0.00       | 8332                        | 0.300                 | -0.01      | 6665                        |

| 1.2          | 1.200                 | 0.00                                                 | 8332                        | 1.200                 | 0.02       | 4165                        | 1.200                 | 0.02       | 2082                        | 1.200                 | -0.04      | 1665                        |

| 2.4          | 2.400                 | 0.02                                                 | 4165                        | 2.400                 | 0.02       | 2082                        | 2.402                 | 0.06       | 1040                        | 2.400                 | -0.04      | 832                         |

| 9.6          | 9.606                 | 0.06                                                 | 1040                        | 9.596                 | -0.03      | 520                         | 9.615                 | 0.16       | 259                         | 9.615                 | -0.16      | 207                         |

| 19.2         | 19.193                | -0.03                                                | 520                         | 19.231                | 0.16       | 259                         | 19.231                | 0.16       | 129                         | 19.230                | -0.16      | 103                         |

| 57.6         | 57.803                | 0.35                                                 | 172                         | 57.471                | -0.22      | 86                          | 58.140                | 0.94       | 42                          | 57.142                | 0.79       | 34                          |

| 115.2        | 114.943               | -0.22                                                | 86                          | 116.279               | 0.94       | 42                          | 113.636               | -1.36      | 21                          | 117.647               | -2.12      | 16                          |

|              |                       | SYNC = 0, BRGH = 1, BRG16 = 1 or SYNC = 1, BRG16 = 1 |                             |                       |            |                             |                       |                  |                             |  |

|--------------|-----------------------|------------------------------------------------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------------|-----------------------------|--|

| BAUD<br>RATE | Fosc = 4.000 MHz      |                                                      |                             | Fos                   | c = 2.000  | MHz                         | Fos                   | Fosc = 1.000 MHz |                             |  |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error                                           | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error       | SPBRG<br>value<br>(decimal) |  |

| 0.3          | 0.300                 | 0.01                                                 | 3332                        | 0.300                 | -0.04      | 1665                        | 0.300                 | -0.04            | 832                         |  |

| 1.2          | 1.200                 | 0.04                                                 | 832                         | 1.201                 | -0.16      | 415                         | 1.201                 | -0.16            | 207                         |  |

| 2.4          | 2.404                 | 0.16                                                 | 415                         | 2.403                 | -0.16      | 207                         | 2.403                 | -0.16            | 103                         |  |

| 9.6          | 9.615                 | 0.16                                                 | 103                         | 9.615                 | -0.16      | 51                          | 9.615                 | -0.16            | 25                          |  |

| 19.2         | 19.231                | 0.16                                                 | 51                          | 19.230                | -0.16      | 25                          | 19.230                | -0.16            | 12                          |  |

| 57.6         | 58.824                | 2.12                                                 | 16                          | 55.555                | 3.55       | 8                           | —                     | _                | —                           |  |

| 115.2        | 111.111               | -3.55                                                | 8                           | —                     | _          | —                           | —                     | _                | —                           |  |

# 22.5 Comparator Control and Configuration

Each comparator has up to eight possible combinations of inputs: up to four external analog inputs, and one of two internal voltage references.

Both comparators allow a selection of the signal from pin, CxINA, or the voltage from the comparator reference (CVREF) on the non-inverting channel. This is compared to either CxINB, CTMU or the microcontroller's fixed internal reference voltage (VIRV, 0.6V nominal) on the inverting channel.

Table 22-1 provides the comparator inputs and outputs tied to fixed I/O pins.

Figure 22-4 illustrates the available comparator configurations and their corresponding bit settings.

| TABLE 22-1: | COMPARATOR INPUTS AND |

|-------------|-----------------------|

|             | OUTPUTS               |

| Comparator | Input or Output | I/O Pin         |

|------------|-----------------|-----------------|

|            | C1INA (VIN+)    | RA0             |

| 1          | C1INB (VIN-)    | RA3             |

| I          | C1OUT           | Remapped<br>RPn |

|            | C2INA(VIN+)     | RA1             |

| 2          | C2INB(VIN-)     | RA2             |

| 2          | C2OUT           | Remapped<br>RPn |

# 22.5.1 COMPARATOR ENABLE AND INPUT SELECTION

Setting the CON bit of the CMxCON register (CMxCON<7>) enables the comparator for operation. Clearing the CON bit disables the comparator, resulting in minimum current consumption.

The CCH<1:0> bits in the CMxCON register (CMxCON<1:0>) direct either one of three analog input pins, or the Internal Reference Voltage (VIRV), to the comparator VIN-. Depending on the comparator operating mode, either an external or internal voltage reference may be used. The analog signal present at VIN- is compared to the signal at VIN+ and the digital output of the comparator is adjusted accordingly.

The external reference is used when CREF = 0 (CMxCON<2>) and VIN+ is connected to the CxINA pin. When external voltage references are used, the comparator module can be configured to have the reference sources externally. The reference signal must be between VSs and VDD, and can be applied to either pin of the comparator.

The comparator module also allows the selection of an internally generated voltage reference (CVREF) from the comparator voltage reference module. This module is described in more detail in **Section 22.0 "Comparator Module"**. The reference from the comparator voltage reference module is only available when CREF = 1. In this mode, the internal voltage reference is applied to the comparator's VIN+ pin.

| Note: | The comparator input pin selected by    |

|-------|-----------------------------------------|

|       | CCH<1:0> must be configured as an input |

|       | by setting both the corresponding TRIS  |

|       | and PCFG bits in the ANCON1 register.   |

# 22.5.2 COMPARATOR ENABLE AND OUTPUT SELECTION

The comparator outputs are read through the CMSTAT register. The CMSTAT<0> reads the Comparator 1 output and CMSTAT<1> reads the Comparator 2 output. These bits are read-only.

The comparator outputs may also be directly output to the RPn I/O pins by setting the COE bit (CMxCON<6>). When enabled, multiplexers in the output path of the pins switch to the output of the comparator.

By default, the comparator's output is at logic high whenever the voltage on VIN+ is greater than on VIN-. The polarity of the comparator outputs can be inverted using the CPOL bit (CMxCON<5>).

The uncertainty of each of the comparators is related to the input offset voltage and the response time given in the specifications, as discussed in **Section 22.2 "Comparator Operation"**.

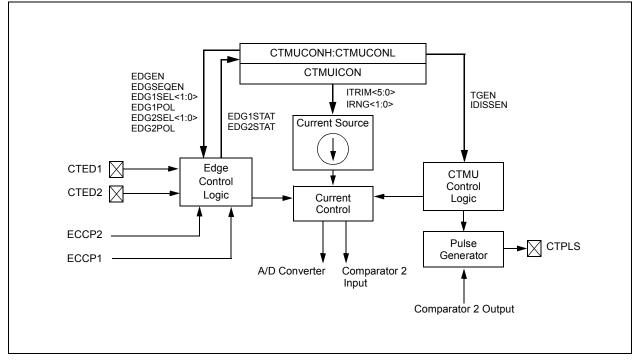

### 25.0 CHARGE TIME MEASUREMENT UNIT (CTMU)

The Charge Time Measurement Unit (CTMU) is a flexible analog module that provides accurate differential time measurement between pulse sources, as well as asynchronous pulse generation. By working with other on-chip analog modules, the CTMU can be used to precisely measure time, measure capacitance, measure relative changes in capacitance or generate output pulses with a specific time delay. The CTMU is ideal for interfacing with capacitive-based sensors.

The module includes the following key features:

- Up to 13 channels available for capacitive or time measurement input

- · On-chip precision current source

- Four-edge input trigger sources

- Polarity control for each edge source

- Control of edge sequence

- Control of response to edges

- · Time measurement resolution of 1 nanosecond

- · High precision time measurement

- Time delay of external or internal signal asynchronous to system clock

- Accurate current source suitable for capacitive measurement

The CTMU works in conjunction with the A/D Converter to provide up to 13 channels for time or charge measurement, depending on the specific device and the number of A/D channels available. When configured for time delay, the CTMU is connected to one of the analog comparators. The level-sensitive input edge sources can be selected from four sources: two external inputs or ECCP1/ECCP2 Special Event Triggers.

Figure 25-1 provides a block diagram of the CTMU.

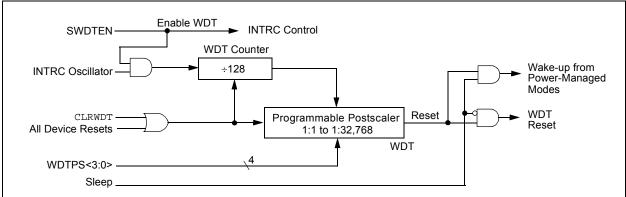

### 26.2 Watchdog Timer (WDT)

PIC18F46J11 family devices have both a conventional WDT circuit and a dedicated, Deep Sleep capable Watchdog Timer. When enabled, the conventional WDT operates in normal Run, Idle and Sleep modes. This data sheet section describes the conventional WDT circuit.

The dedicated, Deep Sleep capable WDT can only be enabled in Deep Sleep mode. This timer is described in Section 4.6.4 "Deep Sleep Watchdog Timer (DSWDT)".

The conventional WDT is driven by the INTRC oscillator. When the WDT is enabled, the clock source is also enabled. The nominal WDT period is 4 ms and has the same stability as the INTRC oscillator.

The 4 ms period of the WDT is multiplied by a 16-bit postscaler. Any output of the WDT postscaler is selected by a multiplexer, controlled by the WDTPS bits in Configuration Register 2H. Available periods range from about 4 ms to 135 seconds (2.25 minutes depending on voltage, temperature and WDT postscaler). The WDT and postscaler are cleared

#### FIGURE 26-1: WDT BLOCK DIAGRAM

whenever a SLEEP or CLRWDT instruction is executed, or a clock failure (primary or Timer1 oscillator) has occurred.

- Note 1: The CLRWDT and SLEEP instructions clear the WDT and postscaler counts when executed.

- 2: When a CLRWDT instruction is executed, the postscaler count will be cleared.

#### 26.2.1 CONTROL REGISTER

The WDTCON register (Register 26-11) is a readable and writable register. The SWDTEN bit enables or disables WDT operation. This allows software to override the WDTEN Configuration bit and enable the WDT only if it has been disabled by the Configuration bit.

LVDSTAT is a read-only status bit that is continuously updated and provides information about the current level of VDDCORE. This bit is only valid when the on-chip voltage regulator is enabled.

| BTFS        | SC                    | Bit Test File                                                                | Bit Test File, Skip if Clear                                                                                                      |                                                               |  |  |  |

|-------------|-----------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|--|--|--|

| Synta       | IX:                   | BTFSC f, b                                                                   | {,a}                                                                                                                              |                                                               |  |  |  |

| Opera       |                       | 0 ≤ f ≤ 255                                                                  |                                                                                                                                   |                                                               |  |  |  |

|             |                       | $0 \leq b \leq 7$                                                            |                                                                                                                                   |                                                               |  |  |  |

|             |                       | a ∈ [0,1]                                                                    |                                                                                                                                   |                                                               |  |  |  |

| Opera       | ation:                | skip if (f <b>)</b>                                                          | = 0                                                                                                                               |                                                               |  |  |  |

| Statu       | s Affected:           | None                                                                         |                                                                                                                                   |                                                               |  |  |  |

| Enco        | ding:                 | 1011                                                                         | bbba fff:                                                                                                                         | f ffff                                                        |  |  |  |

| Desci       | ription:              | instruction is<br>then the next<br>the current in<br>carded and a            | skipped. If bit<br>skipped. If bit<br>instruction fet<br>astruction exect<br>NOP is execu<br>a two-cycle ins                      | 'b' is '0',<br>ched during<br>ution is dis-<br>ted instead,   |  |  |  |

|             |                       |                                                                              | e Access Bank<br>e BSR is used t<br>lefault).                                                                                     |                                                               |  |  |  |

|             |                       | set is enable<br>in Indexed Li<br>mode whene<br>Section 27.2<br>Bit-Oriented | d the extended<br>d, this instructi<br>iteral Offset Ad<br>ever f ≤ 95 (5FH<br>2.3 "Byte-Orie<br>I Instructions<br>et Mode" for d | on operates<br>Idressing<br>n). See<br>nted and<br>in Indexed |  |  |  |

| Word        | s:                    | 1                                                                            |                                                                                                                                   |                                                               |  |  |  |

| Cycle       |                       | 1(2)                                                                         |                                                                                                                                   |                                                               |  |  |  |

| 0,010       |                       | . ,                                                                          | cles if skip and                                                                                                                  | followed                                                      |  |  |  |

|             |                       | by a                                                                         | 2-word instruc                                                                                                                    | tion.                                                         |  |  |  |

| QC          | cle Activity:         |                                                                              |                                                                                                                                   |                                                               |  |  |  |

|             | Q1                    | Q2                                                                           | Q3                                                                                                                                | Q4                                                            |  |  |  |

|             | Decode                | Read<br>register 'f'                                                         | Process<br>Data                                                                                                                   | No<br>operation                                               |  |  |  |