Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 48MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 16                                                                          |

| Program Memory Size        | 32KB (16K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 3.8K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.15V ~ 3.6V                                                                |

| Data Converters            | A/D 10x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 28-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f25j11t-i-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 4.7 Ultra Low-Power Wake-up

The Ultra Low-Power Wake-up (ULPWU) on RA0 allows a slow falling voltage to generate an interrupt without excess current consumption.

Follow these steps to use this feature:

- 1. Configure a remappable output pin to output the ULPOUT signal.

- Map an INTx interrupt-on-change input function to the same pin as used for the ULPOUT output function. Alternatively, in step 1, configure ULPOUT to output onto a PORTB interrupt-on-change pin.

- 3. Charge the capacitor on RA0 by configuring the RA0 pin to an output and setting it to '1'.

- 4. Enable interrupt for the corresponding pin selected in step 2.

- 5. Stop charging the capacitor by configuring RA0 as an input.

- 6. Discharge the capacitor by setting the ULPEN and ULPSINK bits in the WDTCON register.

- 7. Configure Sleep mode.

- 8. Enter Sleep mode.

When the voltage on RA0 drops below VIL, an interrupt will be generated, which will cause the device to wake-up and execute the next instruction.

This feature provides a low-power technique for periodically waking up the device from Sleep mode. The time-out is dependent on the discharge time of the RC circuit on RA0.

When the ULPWU module causes the device to wake-up from Sleep mode, the WDTCON<ULPLVL> bit is set. When the ULPWU module causes the device to wake-up from Deep Sleep, the DSULP (DSWAKEL<5>) bit is set. Software can check these bits upon wake-up to determine the wake-up source. Also in Sleep mode, only the remappable output function, ULPWU, will output this bit value to an RPn pin for externally detecting wake-up events.

See Example 4-1 for initializing the ULPWU module.

| Note: | For module-related bit definitions, see the |  |  |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|--|--|

|       | WDTCON register in Section 26.2             |  |  |  |  |  |  |  |

|       | "Watchdog Timer (WDT)" and the              |  |  |  |  |  |  |  |

|       | DSWAKEL register (Register 4-6).            |  |  |  |  |  |  |  |

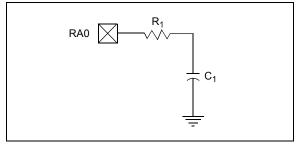

A series resistor between RA0 and the external capacitor provides overcurrent protection for the RA0/AN0/C1INA/ULPWU/RP0 pin and can allow for software calibration of the time-out (see Figure 4-9).

#### FIGURE 4-9: SERIAL RESISTOR

A timer can be used to measure the charge time and discharge time of the capacitor. The charge time can then be adjusted to provide the desired interrupt delay. This technique will compensate for the affects of temperature, voltage and component accuracy. The peripheral can also be configured as a simple Programmable Low-Voltage Detect (LVD) or temperature sensor.

Note: For more information, refer to AN879, "Using the Microchip Ultra Low-Power Wake-up Module" application note (DS00879).

#### EXAMPLE 4-1: ULTRA LOW-POWER WAKE-UP INITIALIZATION

```

//Configure a remappable output pin with interrupt capability

//for ULPWU function (RP21 => RD4/INT1 in this example)

RPOR21 = 13;// ULPWU function mapped to RP21/RD4

RPINR1 = 21;// INT1 mapped to RP21 (RD4)

//*********

//Charge the capacitor on RAO

TRISAbits.TRISA0 = 0;

LATAbits.LATA0 = 1;

for(i = 0; i < 10000; i++) Nop();</pre>

//Stop Charging the capacitor on RAO

TRISAbits.TRISA0 = 1;

//Enable the Ultra Low Power Wakeup module

//and allow capacitor discharge

WDTCONbits.ULPEN = 1;

WDTCONbits.ULPSINK = 1;

//For Sleep, Enable Interrupt for ULPW.

INTCON3bits.INT1IF = 0;

INTCON3bits.INT1IE = 1;

//***************

//Configure Sleep Mode

//********************

//For Sleep

OSCCONbits.IDLEN = 0;

//For Deep Sleep

OSCCONDits.IDLEN = 0i// enable deep sleep

DSCONHbits.DSEN = 1;// Note: must be set just before executing Sleep();

/ / * * * * * * * * * * * * * * * *

//Enter Sleep Mode

/ / * * * * * * * * * * * * * * * *

Sleep();

// for sleep, execution will resume here

// for deep sleep, execution will restart at reset vector (use WDTCONbits.DS to detect)

```

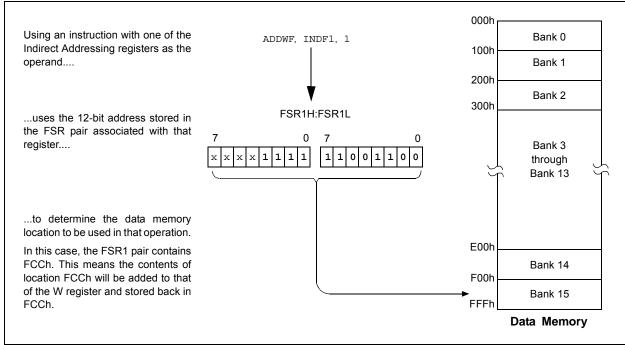

## 6.4.3.1 FSR Registers and the INDF Operand (INDF)

At the core of Indirect Addressing are three sets of registers: FSR0, FSR1 and FSR2. Each represents a pair of 8-bit registers, FSRnH and FSRnL. The four upper bits of the FSRnH register are not used, so each FSR pair holds a 12-bit value. This represents a value that can address the entire range of the data memory in a linear fashion. The FSR register pairs, then, serve as pointers to data memory locations.

Indirect Addressing is accomplished with a set of INDF operands, INDF0 through INDF2. These can be presumed to be "virtual" registers: they are mapped in the

FIGURE 6-8: INDIRECT ADDRESSING

SFR space but are not physically implemented. Reading or writing to a particular INDF register actually accesses its corresponding FSR register pair. A read from INDF1, for example, reads the data at the address indicated by FSR1H:FSR1L. Instructions that use the INDF registers as operands actually use the contents of their corresponding FSR as a pointer to the instruction's target. The INDF operand is just a convenient way of using the pointer.

Because Indirect Addressing uses a full 12-bit address, data RAM banking is not necessary. Thus, the current contents of the BSR and the Access RAM bit have no effect on determining the target address.

## REGISTER 7-1: EECON1: EEPROM CONTROL REGISTER 1 (ACCESS FA6h)

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-x | R/W-0 | R/S-0 | U-0   |

|-------|-----|-------|-------|-------|-------|-------|-------|

| —     | —   | WPROG | FREE  | WRERR | WREN  | WR    | —     |

| bit 7 |     |       |       |       |       |       | bit 0 |

| Legend:           | S = Settable bit (cannot b | S = Settable bit (cannot be cleared in software) |                                    |  |  |  |  |

|-------------------|----------------------------|--------------------------------------------------|------------------------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bi                             | U = Unimplemented bit, read as '0' |  |  |  |  |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared x = Bit is unknown          |                                    |  |  |  |  |

| bit 7-6 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5   | WPROG: One Word-Wide Program bit                                                                                                                                                                                                                                          |

|         | <ul><li>1 = Program 2 bytes on the next WR command</li><li>0 = Program 64 bytes on the next WR command</li></ul>                                                                                                                                                          |

| bit 4   | FREE: Flash Erase Enable bit                                                                                                                                                                                                                                              |

|         | <ul> <li>1 = Perform an erase operation on the next WR command (cleared by hardware after completion of erase)</li> <li>0 = Perform write only</li> </ul>                                                                                                                 |

| bit 3   | WRERR: Flash Program Error Flag bit                                                                                                                                                                                                                                       |

|         | <ul> <li>1 = A write operation is prematurely terminated (any Reset during self-timed programming in normal operation, or an improper write attempt)</li> <li>0 = The write operation completed</li> </ul>                                                                |

| bit 2   | WREN: Flash Program Write Enable bit                                                                                                                                                                                                                                      |

|         | <ul><li>1 = Allows write cycles to Flash program memory</li><li>0 = Inhibits write cycles to Flash program memory</li></ul>                                                                                                                                               |

| bit 1   | WR: Write Control bit                                                                                                                                                                                                                                                     |

|         | <ul> <li>1 = Initiates a program memory erase cycle or write cycle<br/>(The operation is self-timed and the bit is cleared by hardware once write is complete. The WR bit<br/>can only be set (not cleared) in software.)</li> <li>0 = Write cycle is complete</li> </ul> |

| bit 0   | Unimplemented: Read as '0'                                                                                                                                                                                                                                                |

## 7.4 Erasing Flash Program Memory

The minimum erase block is 512 words or 1024 bytes. Only through the use of an external programmer, or through ICSP control, can larger blocks of program memory be bulk erased. Word erase in the Flash array is not supported.

When initiating an erase sequence from the microcontroller itself, a block of 1024 bytes of program memory is erased. The Most Significant 12 bits of the TBLPTR<21:10> point to the block being erased. TBLPTR<9:0> are ignored.

The EECON1 register commands the erase operation. The WREN bit must be set to enable write operations. The FREE bit is set to select an erase operation. For protection, the write initiate sequence for EECON2 must be used.

A long write is necessary for erasing the internal Flash. Instruction execution is halted while in a long write cycle. The long write will be terminated by the internal programming timer.

## 7.4.1 FLASH PROGRAM MEMORY ERASE SEQUENCE

The sequence of events for erasing a block of internal program memory location is:

- 1. Load Table Pointer register with address of row being erased.

- 2. Set the WREN and FREE bits (EECON1<2,4>) to enable the erase operation.

- 3. Disable interrupts.

- 4. Write 55h to EECON2.

- 5. Write 0AAh to EECON2.

- 6. Set the WR bit; this will begin the erase cycle.

- The CPU will stall for the duration of the erase for TIE (see parameter D133B).

- 8. Re-enable interrupts.

## EXAMPLE 7-2: ERASING FLASH PROGRAM MEMORY

|           | MOVLW<br>MOVWF<br>MOVLW<br>MOVWF<br>MOVLW | CODE_ADDR_UPPER<br>TBLPTRU<br>CODE_ADDR_HIGH<br>TBLPTRH<br>CODE ADDR LOW | ; load TBLPTR with the base<br>; address of the memory block |

|-----------|-------------------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------|

|           | MOVWF                                     | TBLPTRL                                                                  |                                                              |

| ERASE_ROW |                                           |                                                                          |                                                              |

|           | BSF                                       | EECON1, WREN                                                             | ; enable write to memory                                     |

|           | BSF                                       | EECON1, FREE                                                             | ; enable Erase operation                                     |

|           | BCF                                       | INTCON, GIE                                                              | ; disable interrupts                                         |

| Required  | MOVLW                                     | 0x55                                                                     |                                                              |

| Sequence  | MOVWF                                     | EECON2                                                                   | ; write 55h                                                  |

|           | MOVLW                                     | 0xAA                                                                     |                                                              |

|           | MOVWF                                     | EECON2                                                                   | ; write OAAh                                                 |

|           | BSF                                       | EECON1, WR                                                               | ; start erase (CPU stall)                                    |

|           | BSF                                       | INTCON, GIE                                                              | ; re-enable interrupts                                       |

| Pin           | Function                                                     | TRIS<br>Setting | I/O | I/О<br>Туре                             | Description                                                       |  |  |  |  |  |

|---------------|--------------------------------------------------------------|-----------------|-----|-----------------------------------------|-------------------------------------------------------------------|--|--|--|--|--|

| RA5/AN4/SS1/  | RA5                                                          | 0               | 0   | DIG                                     | LATA<5> data output; not affected by analog input.                |  |  |  |  |  |

| HLVDIN/RP2    |                                                              |                 |     |                                         | PORTA<5> data input; disabled when analog input enabled.          |  |  |  |  |  |

|               | AN4                                                          | 1               |     | ANA                                     | A/D input channel 4. Default configuration on POR.                |  |  |  |  |  |

|               | SS1                                                          | 1               | Ι   | TTL                                     | Slave select input for MSSP1.                                     |  |  |  |  |  |

|               | HLVDIN                                                       | 1               | I   | ANA                                     | High/Low-Voltage Detect external trip point reference input.      |  |  |  |  |  |

|               | RP2                                                          | 1               | I   | ST                                      | Remappable Peripheral pin 2 input.                                |  |  |  |  |  |

|               |                                                              | 0               | 0   | DIG Remappable Peripheral pin 2 output. |                                                                   |  |  |  |  |  |

| OSC2/CLKO/    | OSC2                                                         | x               | 0   | ANA                                     | Main oscillator feedback output connection (HS mode).             |  |  |  |  |  |

| RA6           |                                                              |                 |     |                                         | System cycle clock output (Fosc/4) in RC and EC Oscillator modes. |  |  |  |  |  |

|               | RA6                                                          | 1               | I   | TTL                                     | PORTA<6> data input.                                              |  |  |  |  |  |

|               |                                                              | 0               | 0   | DIG                                     | LATA<6> data output.                                              |  |  |  |  |  |

| OSC1/CLKI/RA7 | OSC1/CLKI/RA7 OSC1 1 I ANA Main oscillator input connection. |                 |     |                                         | Main oscillator input connection.                                 |  |  |  |  |  |

|               | CLKI                                                         | 1               | Ι   | ANA                                     | Main clock input connection.                                      |  |  |  |  |  |

|               | RA7                                                          | 1               | I   | TTL                                     | PORTA<6> data input.                                              |  |  |  |  |  |

|               |                                                              | 0               | 0   | DIG                                     | LATA<6> data output.                                              |  |  |  |  |  |

TABLE 10-3: PORTA I/O SUMMARY (CONTINUED)

**Legend:** DIG = Digital level output; TTL = TTL input buffer; ST = Schmitt Trigger input buffer; ANA = Analog level input/output; x = Don't care (TRIS bit does not affect port direction or is overridden for this option)

Note 1: This bit is only available on 44-pin devices.

| Name   | Bit 7                | Bit 6                | Bit 5                | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|--------|----------------------|----------------------|----------------------|--------|--------|--------|--------|--------|----------------------------|

| PORTA  | RA7                  | RA6                  | RA5                  | _      | RA3    | RA2    | RA1    | RA0    | 87                         |

| LATA   | LAT7                 | LAT6                 | LAT5                 | _      | LAT3   | LAT2   | LAT1   | LAT0   | 87                         |

| TRISA  | TRIS7                | TRIS6                | TRISA5               | _      | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 87                         |

| ANCON0 | PCFG7 <sup>(1)</sup> | PCFG6 <sup>(1)</sup> | PCFG5 <sup>(1)</sup> | PCFG4  | PCFG3  | PCFG2  | PCFG1  | PCFG0  | 88                         |

| CMxCON | CON                  | COE                  | CPOL                 | EVPOL1 | EVPOL0 | CREF   | CCH1   | CCH0   | 87                         |

| CVRCON | CVREN                | CVROE                | CVRR                 | CVRSS  | CVR3   | CVR2   | CVR1   | CVR0   | 88                         |

TABLE 10-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

Legend: — = unimplemented, read as '0'. Shaded cells are not used by PORTA.

Note 1: These bits are only available in 44-pin devices.

| U-0   | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-----|-------|-------|-------|-------|-------|

|       | _   | _   | IC2R4 | IC2R3 | IC2R2 | IC2R1 | IC2R0 |

| bit 7 |     |     |       |       |       |       | bit 0 |

|       |     |     |       |       |       |       |       |

| Legend:           | $R/\overline{W}$ = Readable, Writable if IOLOCK = 0 |                                    |                    |  |  |  |  |

|-------------------|-----------------------------------------------------|------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit                                    | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 IC2R<4:0>: Assign Input Capture 2 (ECCP2) to the Corresponding RPn Pin bits

### REGISTER 10-13: RPINR12: PERIPHERAL PIN SELECT INPUT REGISTER 12 (BANKED EF2h)

| U-0   | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-----|-------|-------|-------|-------|-------|

| —     | —   | —   | T1GR4 | T1GR3 | T1GR2 | T1GR1 | T1GR0 |

| bit 7 |     |     |       |       |       |       | bit 0 |

| Legend:           | $R/\overline{W}$ = Readable, Writable if IOLOCK = 0 |                                    |                    |  |  |

|-------------------|-----------------------------------------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                                    | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 T1GR<4:0>: Timer1 Gate Input (T1G) to the Corresponding RPn Pin bits

## REGISTER 10-14: RPINR13: PERIPHERAL PIN SELECT INPUT REGISTER 13 (BANKED EF3h)

| U-0         | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |  |

|-------------|-----|-----|-------|-------|-------|-------|-------|--|

| —           | —   | —   | T3GR4 | T3GR3 | T3GR2 | T3GR1 | T3GR0 |  |

| bit 7 bit 0 |     |     |       |       |       |       |       |  |

| Legend:           | $R/\overline{W}$ = Readable, Writable if IOLOCK = 0 |                                    |                    |  |  |

|-------------------|-----------------------------------------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                                    | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 T3GR<4:0>: Timer3 Gate Input (T3G) to the Corresponding RPn Pin bits

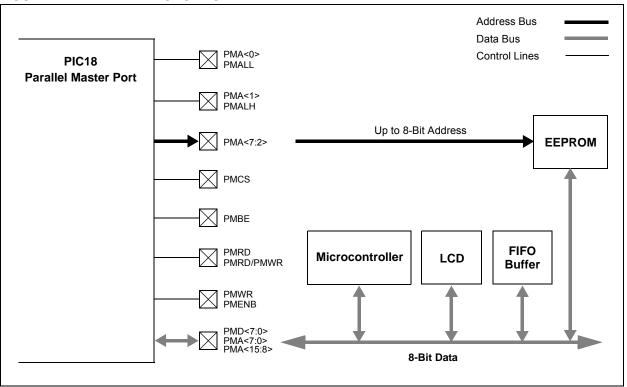

## 11.0 PARALLEL MASTER PORT (PMP)

The Parallel Master Port module (PMP) is an 8-bit parallel I/O module, specifically designed to communicate with a wide variety of parallel devices, such as communication peripherals, LCDs, external memory devices and microcontrollers. Because the interface to parallel peripherals varies significantly, the PMP is highly configurable. The PMP module can be configured to serve as either a PMP or as a Parallel Slave Port (PSP). Key features of the PMP module are:

- Up to 16 bits of Addressing when Using Data/Address Multiplexing

- Up to 8 Programmable Address Lines

- One Chip Select Line

- Programmable Strobe Options:

- Individual Read and Write Strobes or;

Read/Write Strobe with Enable Strobe

- Address Auto-Increment/Auto-Decrement

- Programmable Address/Data Multiplexing

- Programmable Polarity on Control Signals

- Legacy Parallel Slave Port Support

- Enhanced Parallel Slave Support:

- Address Support

- 4-Byte Deep, Auto-Incrementing Buffer

- · Programmable Wait States

- · Selectable Input Voltage Levels

#### FIGURE 11-1: PMP MODULE OVERVIEW

## 12.0 TIMER0 MODULE

The Timer0 module incorporates the following features:

- Software selectable operation as a timer or counter in both 8-bit or 16-bit modes

- · Readable and writable registers

- Dedicated 8-bit, software programmable

prescaler

- Selectable clock source (internal or external)

- · Edge select for external clock

- Interrupt-on-overflow

The T0CON register (Register 12-1) controls all aspects of the module's operation, including the prescale selection. It is both readable and writable.

Figure 12-1 provides a simplified block diagram of the Timer0 module in 8-bit mode. Figure 12-2 provides a simplified block diagram of the Timer0 module in 16-bit mode.

### REGISTER 12-1: T0CON: TIMER0 CONTROL REGISTER (ACCESS FD5h)

| R/W-1       | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------------|--------|-------|-------|-------|-------|-------|-------|

| TMR00N      | T08BIT | TOCS  | TOSE  | PSA   | T0PS2 | T0PS1 | T0PS0 |

| bit 7 bit 0 |        |       |       |       |       |       |       |

| Legend:          |                   |                                                                                   |                               |                    |  |  |  |  |

|------------------|-------------------|-----------------------------------------------------------------------------------|-------------------------------|--------------------|--|--|--|--|

| R = Readable bit |                   | W = Writable bit                                                                  | U = Unimplemented bit         | , read as '0'      |  |  |  |  |

| -n = Value       | at POR            | '1' = Bit is set                                                                  | '0' = Bit is cleared          | x = Bit is unknown |  |  |  |  |

|                  |                   |                                                                                   |                               |                    |  |  |  |  |

| bit 7            |                   | : Timer0 On/Off Control bit                                                       |                               |                    |  |  |  |  |

|                  |                   | les Timer0                                                                        |                               |                    |  |  |  |  |

|                  | 0 = Stops         | 5 Timer0                                                                          |                               |                    |  |  |  |  |

| bit 6            | <b>T08BIT</b> : 1 | Timer0 8-Bit/16-Bit Control bit                                                   | t                             |                    |  |  |  |  |

|                  | 1 = Timer         | 0 is configured as an 8-bit tir                                                   | mer/counter                   |                    |  |  |  |  |

|                  | 0 = Timer         | 0 is configured as a 16-bit tir                                                   | mer/counter                   |                    |  |  |  |  |

| bit 5            | TOCS: Tir         | mer0 Clock Source Select bit                                                      |                               |                    |  |  |  |  |

|                  | 1 = Trans         | ition on T0CKI pin input edge                                                     | e                             |                    |  |  |  |  |

|                  | 0 = Interr        | al clock (Fosc/4)                                                                 |                               |                    |  |  |  |  |

| bit 4            | TOSE: Tir         | <b>FOSE</b> : Timer0 Source Edge Select bit                                       |                               |                    |  |  |  |  |

|                  | 1 = Increi        | ment on high-to-low transitior                                                    | n on T0CKI pin                |                    |  |  |  |  |

|                  | 0 = Increi        | ment on low-to-high transitior                                                    | n on T0CKI pin                |                    |  |  |  |  |

| bit 3            | PSA: Tim          | er0 Prescaler Assignment bi                                                       | t                             |                    |  |  |  |  |

|                  | 1 = Timer         | 0 prescaler is not assigned.                                                      | Timer0 clock input bypasses p | orescaler.         |  |  |  |  |

|                  | 0 = Timer         | 0 = Timer0 prescaler is assigned. Timer0 clock input comes from prescaler output. |                               |                    |  |  |  |  |

| bit 2-0          | T0PS<2:           | 0>: Timer0 Prescaler Select I                                                     | bits                          |                    |  |  |  |  |

|                  | 111 <b>= 1</b> :2 | 111 = 1:256 Prescale value                                                        |                               |                    |  |  |  |  |

|                  | 110 <b>= 1</b> :1 | 28 Prescale value                                                                 |                               |                    |  |  |  |  |

|                  |                   | A Prescale value                                                                  |                               |                    |  |  |  |  |

|                  |                   | 32 Prescale value                                                                 |                               |                    |  |  |  |  |

|                  |                   | 6 Prescale value                                                                  |                               |                    |  |  |  |  |

|                  |                   | B Prescale value                                                                  |                               |                    |  |  |  |  |

|                  | 001 = 1:4         | Prescale value<br>Prescale value                                                  |                               |                    |  |  |  |  |

|                  | 000 - 1.2         |                                                                                   |                               |                    |  |  |  |  |

|                  |                   |                                                                                   |                               |                    |  |  |  |  |

## 17.1 RTCC MODULE REGISTERS

The RTCC module registers are divided into following categories:

## **RTCC Control Registers**

- RTCCFG

- RTCCAL

- PADCFG1

- ALRMCFG

- ALRMRPT

## **RTCC Value Registers**

- RTCVALH and RTCVALL Can access the following registers

- YEAR

- MONTH

- DAY

- WEEKDAY

- HOUR

- MINUTE

- SECOND

## **Alarm Value Registers**

- ALRMVALH and ALRMVALL Can access the following registers:

- ALRMMNTH

- ALRMDAY

- ALRMWD

- ALRMHR

- ALRMMIN

- ALRMSEC

- Note: The RTCVALH and RTCVALL registers can be accessed through RTCRPT<1:0>. ALRMVALH and ALRMVALL can be accessed through ALRMPTR<1:0>.

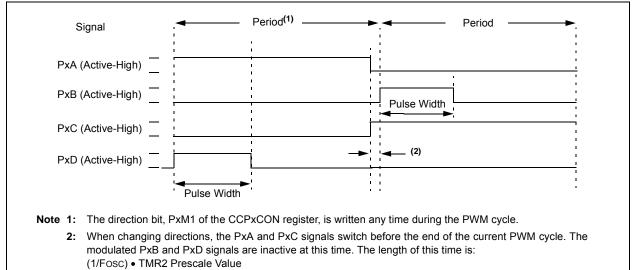

### 18.5.2.1 Direction Change in Full-Bridge Mode

In the Full-Bridge mode, the PxM1 bit in the CCPxCON register allows users to control the forward/reverse direction. When the application firmware changes this direction control bit, the module will change to the new direction on the next PWM cycle.

A direction change is initiated in software by changing the PxM1 bit of the CCPxCON register. The following sequence occurs prior to the end of the current PWM period:

- The modulated outputs (PxB and PxD) are placed in their inactive state.

- The associated unmodulated outputs (PxA and PxC) are switched to drive in the opposite direction.

- PWM modulation resumes at the beginning of the next period.

See Figure 18-12 for an illustration of this sequence.

The Full-Bridge mode does not provide a dead-band delay. As one output is modulated at a time, a dead-band delay is generally not required. There is a situation where a dead-band delay is required. This situation occurs when both of the following conditions are true:

- 1. The direction of the PWM output changes when the duty cycle of the output is at or near 100%.

- 2. The turn-off time of the power switch, including the power device and driver circuit, is greater than the turn-on time.

Figure 18-13 shows an example of the PWM direction changing from forward to reverse, at a near 100% duty cycle. In this example, at time, t1, the PxA and PxD outputs become inactive, while the PxC output becomes active. Since the turn-off time of the power devices is longer than the turn-on time, a shoot-through current will flow through power devices, QC and QD (see Figure 18-10), for the duration of 't'. The same phenomenon will occur to power devices, QA and QB, for PWM direction change from reverse to forward.

If changing PWM direction at high duty cycle is required for an application, two possible solutions for eliminating the shoot-through current are:

- 1. Reduce PWM duty cycle for one PWM period before changing directions.

- 2. Use switch drivers that can drive the switches off faster than they can drive them on.

Other options to prevent shoot-through current may exist.

## FIGURE 18-12: EXAMPLE OF PWM DIRECTION CHANGE

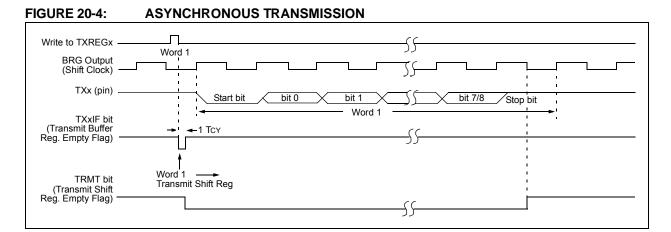

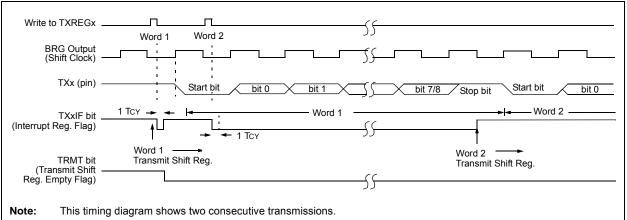

## FIGURE 20-5: ASYNCHRONOUS TRANSMISSION (BACK-TO-BACK)

## TABLE 20-5: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Name     | Bit 7                | Bit 6       | Bit 5       | Bit 4        | Bit 3  | Bit 2  | Bit 1   | Bit 0  | Reset<br>Values<br>on Page: |

|----------|----------------------|-------------|-------------|--------------|--------|--------|---------|--------|-----------------------------|

| INTCON   | GIE/GIEH             | PEIE/GIEL   | TMR0IE      | INT0IE       | RBIE   | TMR0IF | INT0IF  | RBIF   | 69                          |

| PIR1     | PMPIF <sup>(1)</sup> | ADIF        | RC1IF       | TX1IF        | SSP1IF | CCP1IF | TMR2IF  | TMR1IF | 72                          |

| PIE1     | PMPIE <sup>(1)</sup> | ADIE        | RC1IE       | TX1IE        | SSP1IE | CCP1IE | TMR2IE  | TMR1IE | 72                          |

| IPR1     | PMPIP <sup>(1)</sup> | ADIP        | RC1IP       | TX1IP        | SSP1IP | CCP1IP | TMR2IP  | TMR1IP | 72                          |

| PIR3     | SSP2IF               | BCL2IF      | RC2IF       | TX2IF        | TMR4IF | CTMUIF | TMR3GIF | RTCCIF | 72                          |

| PIE3     | SSP2IE               | BCL2IE      | RC2IE       | TX2IE        | TMR4IE | CTMUIE | TMR3GIE | RTCCIE | 72                          |

| IPR3     | SSP2IP               | BCL2IP      | RC2IP       | TX2IP        | TMR4IP | CTMUIP | TMR3GIP | RTCCIP | 72                          |

| RCSTAx   | SPEN                 | RX9         | SREN        | CREN         | ADDEN  | FERR   | OERR    | RX9D   | 72                          |

| TXREGx   | EUSARTx              | Transmit Re | gister      |              |        |        |         |        | 72                          |

| TXSTAx   | CSRC                 | TX9         | TXEN        | SYNC         | SENDB  | BRGH   | TRMT    | TX9D   | 72                          |

| BAUDCONx | ABDOVF               | RCIDL       | RXDTP       | TXDTP        | BRG16  | —      | WUE     | ABDEN  | 73                          |

| SPBRGHx  | EUSARTx              | Baud Rate C | Generator R | egister High | n Byte |        |         |        | 72                          |

| SPBRGx   | EUSARTx              | Baud Rate C | Generator R | egister Low  | Byte   |        |         |        | 72                          |

| ODCON2   |                      | _           |             |              |        |        | U2OD    | U10D   | 74                          |

Legend: - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous transmission.

**Note 1:** These bits are only available on 44-pin devices.

## 25.9 Registers

There are three control registers for the CTMU:

- CTMUCONH

- CTMUCONL

- CTMUICON

The CTMUCONH and CTMUCONL registers (Register 25-1 and Register 25-2) contain control bits for configuring the CTMU module edge source selection, edge source polarity selection, edge sequencing, A/D trigger, analog circuit capacitor discharge and enables. The CTMUICON register (Register 25-3) has bits for selecting the current source range and current source trim.

### REGISTER 25-1: CTMUCONH: CTMU CONTROL REGISTER HIGH (ACCESS FB3h)

| R/W-0  | U-0 | R/W-0    | R/W-0 | R/W-0 | R/W-0    | R/W-0   | U-0   |

|--------|-----|----------|-------|-------|----------|---------|-------|

| CTMUEN | —   | CTMUSIDL | TGEN  | EDGEN | EDGSEQEN | IDISSEN | —     |

| bit 7  |     |          |       |       |          |         | bit 0 |

|        |     |          |       |       |          |         |       |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7 | CTMUEN: CTMU Enable bit                                                                                                            |

|-------|------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul><li>1 = Module is enabled</li><li>0 = Module is disabled</li></ul>                                                             |

| bit 6 | Unimplemented: Read as '0'                                                                                                         |

| bit 5 | CTMUSIDL: Stop in Idle Mode bit                                                                                                    |

|       | <ul><li>1 = Discontinue module operation when device enters Idle mode</li><li>0 = Continue module operation in Idle mode</li></ul> |

| bit 4 | TGEN: Time Generation Enable bit                                                                                                   |

|       | <ul><li>1 = Enables edge delay generation</li><li>0 = Disables edge delay generation</li></ul>                                     |

| bit 3 | EDGEN: Edge Enable bit                                                                                                             |

|       | 1 = Edges are not blocked<br>0 = Edges are blocked                                                                                 |

| bit 2 | EDGSEQEN: Edge Sequence Enable bit                                                                                                 |

|       | <ul><li>1 = Edge 1 event must occur before Edge 2 event can occur</li><li>0 = No edge sequence is needed</li></ul>                 |

| bit 1 | IDISSEN: Analog Current Source Control bit                                                                                         |

|       | <ul><li>1 = Analog current source output is grounded</li><li>0 = Analog current source output is not grounded</li></ul>            |

| bit 0 | Reserved: Write as '0'                                                                                                             |

|       |                                                                                                                                    |

| R/W-0         | R/W-0                                                                                                                                                                        | R/W-0                                            | R/W-0          | R/W-0             | R/W-0            | R/W-x           | R/W-x    |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|----------------|-------------------|------------------|-----------------|----------|

| EDG2POL       | EDG2SEL1                                                                                                                                                                     | EDG2SEL0                                         | EDG1POL        | EDG1SEL1          | EDG1SEL0         | EDG2STAT        | EDG1STAT |

| bit 7         | •                                                                                                                                                                            | •                                                |                | •                 | •                | •               | bit C    |

|               |                                                                                                                                                                              |                                                  |                |                   |                  |                 |          |

| Legend:       |                                                                                                                                                                              |                                                  |                |                   |                  |                 |          |

| R = Readable  | e bit                                                                                                                                                                        | W = Writable                                     | bit            | U = Unimplen      | nented bit, read | l as '0'        |          |

| -n = Value at | POR                                                                                                                                                                          | '1' = Bit is set                                 |                | '0' = Bit is clea | ared             | x = Bit is unkr | iown     |

| bit 7         | EDG2POL: E                                                                                                                                                                   | dge 2 Polarity                                   | Select bit     |                   |                  |                 |          |

|               |                                                                                                                                                                              | rogrammed for<br>rogrammed for                   |                |                   |                  |                 |          |

| bit 6-5       | EDG2SEL<1:0>: Edge 2 Source Select bits<br>11 = CTED1 pin<br>10 = CTED2 pin<br>01 = ECCP1 Special Event Trigger<br>00 = ECCP2 Special Event Trigger                          |                                                  |                |                   |                  |                 |          |

| bit 4         | 1 = Edge 1 p                                                                                                                                                                 | dge 1 Polarity<br>rogrammed for<br>rogrammed for | a positive edg |                   |                  |                 |          |

| bit 3-2       | EDG1SEL<1:0>: Edge 1 Source Select bits<br>11 = CTED1 pin<br>10 = CTED2 pin<br>01 = ECCP1 Special Event Trigger<br>00 = ECCP2 Special Event Trigger                          |                                                  |                |                   |                  |                 |          |

| bit 1         | EDG2STAT: Edge 2 Status bit<br>1 = Edge 2 event has occurred                                                                                                                 |                                                  |                |                   |                  |                 |          |

| bit 0         | <ul> <li>0 = Edge 2 event has not occurred</li> <li>EDG1STAT: Edge 1 Status bit</li> <li>1 = Edge 1 event has occurred</li> <li>0 = Edge 1 event has not occurred</li> </ul> |                                                  |                |                   |                  |                 |          |

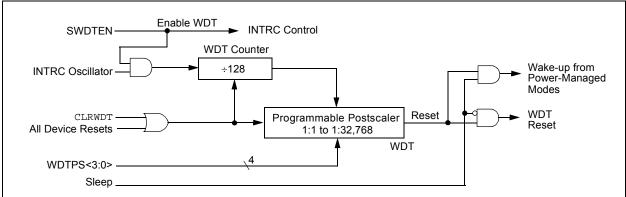

## 26.2 Watchdog Timer (WDT)

PIC18F46J11 family devices have both a conventional WDT circuit and a dedicated, Deep Sleep capable Watchdog Timer. When enabled, the conventional WDT operates in normal Run, Idle and Sleep modes. This data sheet section describes the conventional WDT circuit.

The dedicated, Deep Sleep capable WDT can only be enabled in Deep Sleep mode. This timer is described in Section 4.6.4 "Deep Sleep Watchdog Timer (DSWDT)".

The conventional WDT is driven by the INTRC oscillator. When the WDT is enabled, the clock source is also enabled. The nominal WDT period is 4 ms and has the same stability as the INTRC oscillator.

The 4 ms period of the WDT is multiplied by a 16-bit postscaler. Any output of the WDT postscaler is selected by a multiplexer, controlled by the WDTPS bits in Configuration Register 2H. Available periods range from about 4 ms to 135 seconds (2.25 minutes depending on voltage, temperature and WDT postscaler). The WDT and postscaler are cleared

### FIGURE 26-1: WDT BLOCK DIAGRAM

whenever a SLEEP or CLRWDT instruction is executed, or a clock failure (primary or Timer1 oscillator) has occurred.

- Note 1: The CLRWDT and SLEEP instructions clear the WDT and postscaler counts when executed.

- 2: When a CLRWDT instruction is executed, the postscaler count will be cleared.

### 26.2.1 CONTROL REGISTER

The WDTCON register (Register 26-11) is a readable and writable register. The SWDTEN bit enables or disables WDT operation. This allows software to override the WDTEN Configuration bit and enable the WDT only if it has been disabled by the Configuration bit.

LVDSTAT is a read-only status bit that is continuously updated and provides information about the current level of VDDCORE. This bit is only valid when the on-chip voltage regulator is enabled.

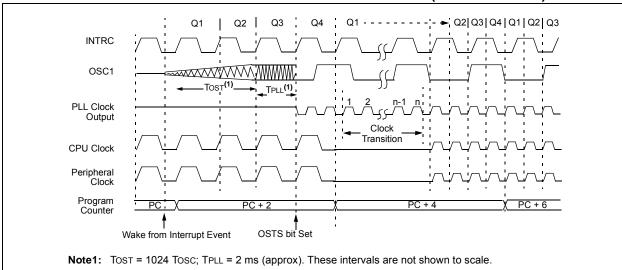

## 26.4 Two-Speed Start-up

The Two-Speed Start-up feature helps to minimize the latency period, from oscillator start-up to code execution, by allowing the microcontroller to use the INTRC oscillator as a clock source until the primary clock source is available. It is enabled by setting the IESO Configuration bit.

Two-Speed Start-up should be enabled only if the primary oscillator mode is HS or HSPLL (Crystal-Based) modes. Since the EC and ECPLL modes do not require an Oscillator Start-up Timer (OST) delay, Two-Speed Start-up should be disabled.

When enabled, Resets and wake-ups from Sleep mode cause the device to configure itself to run from the internal oscillator block as the clock source, following the time-out of the Power-up Timer after a Power-on Reset is enabled. This allows almost immediate code execution while the primary oscillator starts and the OST is running. Once the OST times out, the device automatically switches to PRI\_RUN mode.

In all other power-managed modes, Two-Speed Start-up is not used. The device will be clocked by the currently selected clock source until the primary clock source becomes available. The setting of the IESO bit is ignored.

FIGURE 26-3: TIMING TRANSITION FOR TWO-SPEED START-UP (INTRC TO HSPLL)

## 26.4.1 SPECIAL CONSIDERATIONS FOR USING TWO-SPEED START-UP

While using the INTRC oscillator in Two-Speed Start-up, the device still obeys the normal command sequences for entering power-managed modes, including serial SLEEP instructions (refer to **Section 4.1.4 "Multiple Sleep Commands"**). In practice, this means that user code can change the SCS<1:0> bit settings or issue SLEEP instructions before the OST times out. This would allow an application to briefly wake-up, perform routine "housekeeping" tasks and return to Sleep before the device starts to operate from the primary oscillator.

User code can also check if the primary clock source is currently providing the device clocking by checking the status of the OSTS bit (OSCCON<3>). If the bit is set, the primary oscillator is providing the clock. Otherwise, the internal oscillator block is providing the clock during wake-up from Reset or Sleep mode.

## 26.5 Fail-Safe Clock Monitor

The Fail-Safe Clock Monitor (FSCM) allows the microcontroller to continue operation in the event of an external oscillator failure by automatically switching the device clock to the internal oscillator block. The FSCM function is enabled by setting the FCMEN Configuration bit.

When FSCM is enabled, the INTRC oscillator runs at all times to monitor clocks to peripherals and provide a backup clock in the event of a clock failure. Clock monitoring (shown in Figure 26-4) is accomplished by creating a sample clock signal, which is the INTRC output divided by 64. This allows ample time between FSCM sample clocks for a peripheral clock edge to occur. The peripheral device clock and the sample clock are presented as inputs to the clock monitor latch. The clock monitor is set on the falling edge of the device clock source but cleared on the rising edge of the sample clock.

| <b>TABLE 27-2:</b> | PIC18F46J11 FAMILY INSTRUCTION SET ( | CONTINUED) |  |

|--------------------|--------------------------------------|------------|--|

|                    |                                      |            |  |

| Mnemonic,<br>Operands |                        | Description                     | Cycles | 16-Bit Instruction Word |      |      | Status | Notes           |       |

|-----------------------|------------------------|---------------------------------|--------|-------------------------|------|------|--------|-----------------|-------|

|                       |                        | Description                     | Cycles | MSb                     |      |      | LSb    | Affected        | Notes |

| LITERAL OPERATIONS    |                        |                                 |        |                         |      |      |        |                 |       |

| ADDLW                 | k                      | Add Literal and WREG            | 1      | 0000                    | 1111 | kkkk | kkkk   | C, DC, Z, OV, N |       |

| ANDLW                 | k                      | AND Literal with WREG           | 1      | 0000                    | 1011 | kkkk | kkkk   | Z, N            |       |

| IORLW                 | k                      | Inclusive OR Literal with WREG  | 1      | 0000                    | 1001 | kkkk | kkkk   | Z, N            |       |

| LFSR                  | f, k                   | Move Literal (12-bit) 2nd word  | 2      | 1110                    | 1110 | 00ff | kkkk   | None            |       |

|                       |                        | to FSR(f) 1st word              |        | 1111                    | 0000 | kkkk | kkkk   |                 |       |

| MOVLB                 | k                      | Move Literal to BSR<3:0>        | 1      | 0000                    | 0001 | 0000 | kkkk   | None            |       |

| MOVLW                 | k                      | Move Literal to WREG            | 1      | 0000                    | 1110 | kkkk | kkkk   | None            |       |

| MULLW                 | k                      | Multiply Literal with WREG      | 1      | 0000                    | 1101 | kkkk | kkkk   | None            |       |

| RETLW                 | k                      | Return with Literal in WREG     | 2      | 0000                    | 1100 | kkkk | kkkk   | None            |       |

| SUBLW                 | k                      | Subtract WREG from Literal      | 1      | 0000                    | 1000 | kkkk | kkkk   | C, DC, Z, OV, N |       |

| XORLW                 | k                      | Exclusive OR Literal with WREG  | 1      | 0000                    | 1010 | kkkk | kkkk   | Z, N            |       |

| DATA MEN              | $IORY \leftrightarrow$ | PROGRAM MEMORY OPERATIONS       | 6      |                         |      |      |        |                 |       |

| TBLRD*                |                        | Table Read                      | 2      | 0000                    | 0000 | 0000 | 1000   | None            |       |

| TBLRD*+               |                        | Table Read with Post-Increment  |        | 0000                    | 0000 | 0000 | 1001   | None            |       |

| TBLRD*-               |                        | Table Read with Post-Decrement  |        | 0000                    | 0000 | 0000 | 1010   | None            |       |

| TBLRD+*               |                        | Table Read with Pre-Increment   |        | 0000                    | 0000 | 0000 | 1011   | None            |       |

| TBLWT*                |                        | Table Write                     | 2      | 0000                    | 0000 | 0000 | 1100   | None            |       |

| TBLWT*+               |                        | Table Write with Post-Increment |        | 0000                    | 0000 | 0000 | 1101   | None            |       |

| TBLWT*-               |                        | Table Write with Post-Decrement |        | 0000                    | 0000 | 0000 | 1110   | None            |       |

| TBLWT+*               |                        | Table Write with Pre-Increment  |        | 0000                    | 0000 | 0000 | 1111   | None            |       |

**Note 1:** When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned.

**3:** If the Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are two-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

| GOT                                                                                                                        | GOTO Unconditional Branch              |                                                                |                                     |                                       |                                         |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------|----------------------------------------|----------------------------------------------------------------|-------------------------------------|---------------------------------------|-----------------------------------------|--|--|--|--|

| Synta                                                                                                                      | ax:                                    | GOTO k                                                         | GOTO k                              |                                       |                                         |  |  |  |  |

| Oper                                                                                                                       | ands:                                  | $0 \le k \le 10$                                               | $0 \leq k \leq 1048575$             |                                       |                                         |  |  |  |  |

| Oper                                                                                                                       | ation:                                 | $k \rightarrow PC<2$                                           | $k \rightarrow PC < 20:1 >$         |                                       |                                         |  |  |  |  |

| Statu                                                                                                                      | s Affected:                            | None                                                           | None                                |                                       |                                         |  |  |  |  |

|                                                                                                                            | ding:<br>ord (k<7:0>)<br>vord(k<19:8>) | 1110<br>1111                                                   | 1111<br>k <sub>19</sub> kkk         | k <sub>7</sub> kkk<br>kkkk            | kkkk <sub>0</sub><br>kkkk <sub>8</sub>  |  |  |  |  |

| Desc                                                                                                                       | ription:                               | GOTO allov<br>anywhere<br>ory range.<br>into PC<2<br>two-cycle | within ent<br>The 20-b<br>0:1>. GOT | tire 2-Mb<br>it value 'l<br>o is alwa | yte mem-<br><' is loaded                |  |  |  |  |

| Word                                                                                                                       | ls:                                    | 2                                                              | 2                                   |                                       |                                         |  |  |  |  |

| Cycle                                                                                                                      | es:                                    | 2                                                              | 2                                   |                                       |                                         |  |  |  |  |

| QC                                                                                                                         | ycle Activity:                         |                                                                |                                     |                                       |                                         |  |  |  |  |

|                                                                                                                            | Q1                                     | Q2                                                             | Q3                                  | 3                                     | Q4                                      |  |  |  |  |

|                                                                                                                            | Decode                                 | Read literal<br>'k'<7:0>,                                      | No<br>operat                        | ion 'l                                | ead literal<br>‹'<19:8>,<br>/rite to PC |  |  |  |  |

|                                                                                                                            | No<br>operation                        | No<br>operation                                                |                                     | No<br>operation op                    |                                         |  |  |  |  |

| operation     operation     operation       Example:     GOTO THERE       After Instruction       PC =     Address (THERE) |                                        |                                                                |                                     |                                       |                                         |  |  |  |  |

| INCF                               | Increment                                                                                                       | T                                                                                                                                                                    |                                                                          |                                                                                                      |  |  |  |  |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:                            | INCF f{,                                                                                                        | INCF f {,d {,a}}                                                                                                                                                     |                                                                          |                                                                                                      |  |  |  |  |

| Operands:                          | $\begin{array}{l} 0 \leq f \leq 255 \\ d \in [0,1] \\ a \in [0,1] \end{array}$                                  | $\begin{array}{l} 0 \leq f \leq 255 \\ d \in [0,1] \end{array}$                                                                                                      |                                                                          |                                                                                                      |  |  |  |  |

| Operation:                         | (f) + 1 $\rightarrow$ d                                                                                         | (f) + 1 $\rightarrow$ dest                                                                                                                                           |                                                                          |                                                                                                      |  |  |  |  |

| Status Affected:                   | C, DC, N,                                                                                                       | OV, Z                                                                                                                                                                |                                                                          |                                                                                                      |  |  |  |  |

| Encoding:                          | 0010                                                                                                            | 10da                                                                                                                                                                 | ffff                                                                     | ffff                                                                                                 |  |  |  |  |

| Description:                       | incremente<br>placed in V                                                                                       | The contents of register 'f' are<br>incremented. If 'd' is '0', the result is<br>placed in W. If 'd' is '1', the result is<br>placed back in register 'f' (default). |                                                                          |                                                                                                      |  |  |  |  |

|                                    | lf 'a' is '1', t                                                                                                | If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank (default).                                                   |                                                                          |                                                                                                      |  |  |  |  |

|                                    | lt 'a' is '0' a                                                                                                 | and the e                                                                                                                                                            | xtended                                                                  | instruction                                                                                          |  |  |  |  |

|                                    | set is enab<br>in Indexed<br>mode when<br>Section 27<br>Bit-Oriente                                             | led, this i<br>Literal O<br>never f ≤<br>7.2.3 "By<br>ed Instru                                                                                                      | ffset Add<br>95 (5Fh)<br>t <b>e-Orie</b> r<br>ictions i                  | on operate<br>dressing<br>). See<br><b>nted and</b><br>in Indexee                                    |  |  |  |  |

| Words:                             | set is enab<br>in Indexed<br>mode when<br><b>Section 27</b>                                                     | led, this i<br>Literal O<br>never f ≤<br>7.2.3 "By<br>ed Instru                                                                                                      | nstructio<br>ffset Add<br>95 (5Fh)<br>t <b>e-Orie</b> r<br>ictions i     | on operate<br>dressing<br>). See<br><b>nted and</b><br>in Indexee                                    |  |  |  |  |

| Words:<br>Cycles:                  | set is enab<br>in Indexed<br>mode when<br>Section 27<br>Bit-Oriento<br>Literal Off                              | led, this i<br>Literal O<br>never f ≤<br>7.2.3 "By<br>ed Instru                                                                                                      | nstructio<br>ffset Add<br>95 (5Fh)<br>t <b>e-Orie</b> r<br>ictions i     | on operate<br>dressing<br>). See<br><b>nted and</b><br>in Indexee                                    |  |  |  |  |

| Cycles:                            | set is enab<br>in Indexed<br>mode when<br>Section 27<br>Bit-Oriente<br>Literal Off                              | led, this i<br>Literal O<br>never f ≤<br>7.2.3 "By<br>ed Instru                                                                                                      | nstructio<br>ffset Add<br>95 (5Fh)<br>t <b>e-Orie</b> r<br>ictions i     | on operate<br>dressing<br>). See<br><b>nted and</b><br>in Indexee                                    |  |  |  |  |

|                                    | set is enab<br>in Indexed<br>mode when<br>Section 27<br>Bit-Oriente<br>Literal Off                              | led, this i<br>Literal O<br>never f ≤<br>7.2.3 "By<br>ed Instru                                                                                                      | nstructio<br>ffset Add<br>95 (5Fh<br>ite-Orier<br>ictions i<br>e" for de | on operate<br>dressing<br>). See<br><b>nted and</b><br>in Indexee                                    |  |  |  |  |

| Cycles:<br>Q Cycle Activity:       | set is enab<br>in Indexed<br>mode when<br>Section 27<br>Bit-Oriente<br>Literal Off<br>1                         | led, this i<br>Literal O<br>never f ≤<br>7.2.3 "By<br>ed Instru<br>set Mode                                                                                          | nstructio<br>ffset Add<br>95 (5Fh<br>te-Orier<br>ictions i<br>e" for de  | on operate<br>dressing<br>). See<br><b>nted and</b><br><b>n Indexed</b><br>tails.                    |  |  |  |  |

| Cycles:<br>Q Cycle Activity:<br>Q1 | set is enab<br>in Indexed<br>mode when<br>Section 27<br>Bit-Oriente<br>Literal Off<br>1<br>1<br>2<br>Q2<br>Read | led, this i<br>Literal O<br>never f ≤<br>7.2.3 "By<br>ed Instru<br>set Mode<br>Q3<br>Proce<br>Dat                                                                    | nstructio<br>ffset Add<br>95 (5Fh<br>te-Orier<br>ictions i<br>e" for de  | on operate<br>dressing<br>). See<br><b>nted and n</b><br><b>Indexed</b><br>ttails.<br>Q4<br>Write to |  |  |  |  |

| POP                                     |                | Рор Тор о                                                             | Pop Top of Return Stack                                                                                                                                                                                                                                                                    |                  |           |  |  |  |  |

|-----------------------------------------|----------------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------|--|--|--|--|

| Synta                                   | ax:            | POP                                                                   | POP                                                                                                                                                                                                                                                                                        |                  |           |  |  |  |  |

| Operands:                               |                | None                                                                  | None                                                                                                                                                                                                                                                                                       |                  |           |  |  |  |  |

| Operation:                              |                | $(TOS) \rightarrow b$                                                 | (TOS) $\rightarrow$ bit bucket                                                                                                                                                                                                                                                             |                  |           |  |  |  |  |

| Status Affected:                        |                | None                                                                  | None                                                                                                                                                                                                                                                                                       |                  |           |  |  |  |  |

| Encoding:                               |                | 0000                                                                  | 0000                                                                                                                                                                                                                                                                                       | 000              | 0 0110    |  |  |  |  |

| Description:                            |                | stack and i<br>then becor<br>was pushe<br>This instru-<br>the user to | The TOS value is pulled off the return<br>stack and is discarded. The TOS value<br>then becomes the previous value that<br>was pushed onto the return stack.<br>This instruction is provided to enable<br>the user to properly manage the return<br>stack to incorporate a software stack. |                  |           |  |  |  |  |

| Word                                    | ds:            | 1                                                                     |                                                                                                                                                                                                                                                                                            |                  |           |  |  |  |  |

| Cycle                                   | es:            | 1                                                                     |                                                                                                                                                                                                                                                                                            |                  |           |  |  |  |  |

| QC                                      | ycle Activity: |                                                                       |                                                                                                                                                                                                                                                                                            |                  |           |  |  |  |  |

|                                         | Q1             | Q2                                                                    | Q3                                                                                                                                                                                                                                                                                         |                  | Q4        |  |  |  |  |