#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

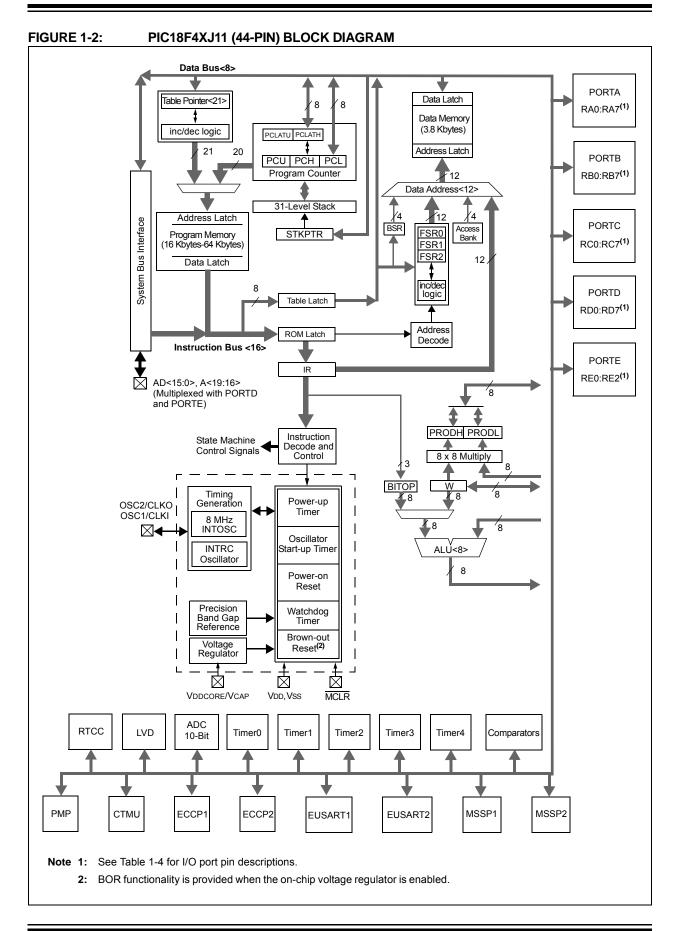

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 16                                                                         |

| Program Memory Size        | 64KB (32K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 3.8K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.15V ~ 3.6V                                                               |

| Data Converters            | A/D 10x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

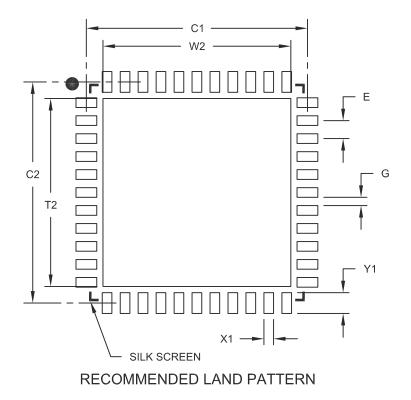

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-QFN (6×6)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f26j11-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 4.0 LOW-POWER MODES

The PIC18F46J11 family devices can manage power consumption through clocking to the CPU and the peripherals. In general, reducing the clock frequency and the amount of circuitry being clocked reduces power consumption.

For managing power in an application, the primary modes of operation are:

- Run Mode

- Idle Mode

- Sleep Mode

- · Deep Sleep Mode

Additionally, there is an Ultra Low-Power Wake-up (ULPWU) mode for generating an interrupt-on-change on RA0.

These modes define which portions of the device are clocked and at what speed.

- The Run and Idle modes can use any of the three available clock sources (primary, secondary or internal oscillator blocks).

- The Sleep mode does not use a clock source.

The ULPWU mode on RA0 allows a slow falling voltage to generate an interrupt-on-change on RA0 without excess current consumption. See **Section 4.7** "**Ultra Low-Power Wake-up**".

The power-managed modes include several power-saving features offered on previous PIC<sup>®</sup> devices, such as clock switching, ULPWU and Sleep mode. In addition, the PIC18F46J11 family devices add a new power-managed Deep Sleep mode.

## 4.1 Selecting Power-Managed Modes

Selecting a power-managed mode requires these decisions:

- Will the CPU be clocked?

- If so, which clock source will be used?

The IDLEN bit (OSCCON<7>) controls CPU clocking and the SCS<1:0> bits (OSCCON<1:0>) select the clock source. The individual modes, bit settings, clock sources and affected modules are summarized in Table 4-1.

# 4.1.1 CLOCK SOURCES

The SCS<1:0> bits allow the selection of one of three clock sources for power-managed modes. They are:

- Primary clock source Defined by the FOSC<2:0> Configuration bits

- Timer1 clock Provided by the secondary oscillator

- Postscaled internal clock Derived from the internal oscillator block

### 4.1.2 ENTERING POWER-MANAGED MODES

Switching from one clock source to another begins by loading the OSCCON register. The SCS<1:0> bits select the clock source.

Changing these bits causes an immediate switch to the new clock source, assuming that it is running. The switch also may be subject to clock transition delays. These delays are discussed in **Section 4.1.3 "Clock Transitions and Status Indicators"** and subsequent sections.

Entry to the power-managed Idle or Sleep modes is triggered by the execution of a SLEEP instruction. The actual mode that results depends on the status of the IDLEN bit.

Depending on the current mode and the mode being switched to, a change to a power-managed mode does not always require setting all of these bits. Many transitions may be done by changing the oscillator select bits, the IDLEN bit or the DSEN bit prior to issuing a SLEEP instruction.

If the IDLEN and DSEN bits are already configured correctly, it may only be necessary to perform a SLEEP instruction to switch to the desired mode.

# 4.4.3 RC\_IDLE MODE

In RC\_IDLE mode, the CPU is disabled but the peripherals continue to be clocked from the internal oscillator block. This mode allows for controllable power conservation during Idle periods.

From RC\_RUN, this mode is entered by setting the IDLEN bit and executing a SLEEP instruction. If the device is in another Run mode, first set IDLEN, then clear the SCS bits and execute SLEEP. When the clock source is switched to the INTOSC block, the primary oscillator is shut down and the OSTS bit is cleared.

When a wake event occurs, the peripherals continue to be clocked from the internal oscillator block. After the wake event, the CPU begins executing code being clocked by the INTRC. The IDLEN and SCS bits are not affected by the wake-up. The INTRC source will continue to run if either the WDT or the FSCM is enabled.

# 4.5 Exiting Idle and Sleep Modes

An exit from Sleep mode, or any of the Idle modes, is triggered by an interrupt, a Reset or a WDT time-out. This section discusses the triggers that cause exits from power-managed modes. The clocking subsystem actions are discussed in each of the power-managed modes sections (see Section 4.2 "Run Modes", Section 4.3 "Sleep Mode" and Section 4.4 "Idle Modes").

## 4.5.1 EXIT BY INTERRUPT

Any of the available interrupt sources can cause the device to exit from an Idle mode, or the Sleep mode, to a Run mode. To enable this functionality, an interrupt source must be enabled by setting its enable bit in one of the INTCON or PIE registers. The exit sequence is initiated when the corresponding interrupt flag bit is set.

On all exits from Idle or Sleep modes by interrupt, code execution branches to the interrupt vector if the GIE/GIEH bit (INTCON<7>) is set. Otherwise, code execution continues or resumes without branching (see Section 9.0 "Interrupts").

# 4.5.2 EXIT BY WDT TIME-OUT

A WDT time-out will cause different actions depending on which power-managed mode the device is in when the time-out occurs. If the device is not executing code (all Idle modes and Sleep mode), the time-out will result in an exit from the power-managed mode (see Section 4.2 "Run Modes" and Section 4.3 "Sleep Mode"). If the device is executing code (all Run modes), the time-out will result in a WDT Reset (see Section 26.2 "Watchdog Timer (WDT)").

The WDT and postscaler are cleared by one of the following events:

- Executing a SLEEP or CLRWDT instruction

- The loss of a currently selected clock source (if the FSCM is enabled)

## 4.5.3 EXIT BY RESET

Exiting an Idle or Sleep mode by Reset automatically forces the device to run from the INTRC.

### 4.5.4 EXIT WITHOUT AN OSCILLATOR START-UP DELAY

Certain exits from power-managed modes do not invoke the OST at all. There are two cases:

- PRI\_IDLE mode (where the primary clock source is not stopped) and the primary clock source is the EC mode

- PRI\_IDLE mode and the primary clock source is the ECPLL mode

In these instances, the primary clock source either does not require an oscillator start-up delay, since it is already running (PRI\_IDLE), or normally does not require an oscillator start-up delay (EC).

# 4.6 Deep Sleep Mode

Deep Sleep mode brings the device into its lowest power consumption state without requiring the use of external switches to remove power from the device. During deep sleep, the on-chip VDDCORE voltage regulator is powered down, effectively disconnecting power to the core logic of the microcontroller.

Note: Since Deep Sleep mode powers down the microcontroller by turning off the on-chip VDDCORE voltage regulator, Deep Sleep capability is available only on PIC18FXXJ members in the device family. The on-chip voltage regulator is not available in PIC18LFXXJ members of the device family, and therefore, they do not support Deep Sleep.

### **REGISTER 4-5:** DSWAKEH: DEEP SLEEP WAKE HIGH BYTE REGISTER (BANKED F4Bh)

| U-0         | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  |  |  |  |

|-------------|-----|-----|-----|-----|-----|-----|--------|--|--|--|

| —           | —   |     | —   | —   | —   |     | DSINT0 |  |  |  |

| bit 7 bit 0 |     |     |     |     |     |     |        |  |  |  |

|             |     |     |     |     |     |     |        |  |  |  |

| Legend:           |                  |                        |                                    |  |  |  |

|-------------------|------------------|------------------------|------------------------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | U = Unimplemented bit, read as '0' |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown                 |  |  |  |

## bit 7-1 Unimplemented: Read as '0'

bit 0

DSINT0: Interrupt-on-Change bit

1 = Interrupt-on-change was asserted during Deep Sleep

0 = Interrupt-on-change was not asserted during Deep Sleep

### REGISTER 4-6: DSWAKEL: DEEP SLEEP WAKE LOW BYTE REGISTER (BANKED F4Ah)

| R/W-0 | U-0 | R/W-0                | R/W-0                | R/W-0                | R/W-0                 | U-0 | R/W-1 |

|-------|-----|----------------------|----------------------|----------------------|-----------------------|-----|-------|

| DSFLT | —   | DSULP <sup>(2)</sup> | DSWDT <sup>(2)</sup> | DSRTC <sup>(2)</sup> | DSMCLR <sup>(2)</sup> |     | DSPOR |

| bit 7 |     |                      |                      |                      |                       |     | bit 0 |

| Legend:           |                                                     |  |                    |  |  |  |

|-------------------|-----------------------------------------------------|--|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0' |  |                    |  |  |  |

| -n = Value at POR | = Value at POR '1' = Bit is set                     |  | x = Bit is unknown |  |  |  |

| bit 7   | DSFLT: Deep Sleep Fault Detected bit                                                                          |

|---------|---------------------------------------------------------------------------------------------------------------|

|         | 1 = A Deep Sleep Fault was detected during Deep Sleep                                                         |

|         | 0 = A Deep Sleep fault was not detected during Deep Sleep                                                     |

| bit 6   | Unimplemented: Read as '0'                                                                                    |

| bit 5   | DSULP: Ultra Low-Power Wake-up status bit <sup>(2)</sup>                                                      |

|         | 1 = An Ultra Low-Power Wake-up event occurred during Deep Sleep                                               |

|         | 0 = An Ultra Low-Power Wake-up event did not occur during Deep Sleep                                          |

| bit 4   | DSWDT: Deep Sleep Watchdog Timer Time-out bit <sup>(2)</sup>                                                  |

|         | 1 = The Deep Sleep Watchdog Timer timed out during Deep Sleep                                                 |

|         | 0 = The Deep Sleep Watchdog Timer did not time out during Deep Sleep                                          |

| bit 3   | DSRTC: Real-Time Clock and Calendar Alarm bit <sup>(2)</sup>                                                  |

|         | 1 = The Real-Time Clock/Calendar triggered an alarm during Deep Sleep                                         |

|         | 0 = The Real-Time Clock /Calendar did not trigger an alarm during Deep Sleep                                  |

| bit 2   | DSMCLR: MCLR Event bit <sup>(2)</sup>                                                                         |

|         | 1 = The MCLR pin was asserted during Deep Sleep                                                               |

|         | 0 = The MCLR pin was not asserted during Deep Sleep                                                           |

| bit 1   | Unimplemented: Read as '0'                                                                                    |

| bit 0   | DSPOR: Power-on Reset Event bit                                                                               |

|         | 1 = The VDD supply POR circuit was active and a POR event was detected <sup>(1)</sup>                         |

|         | 0 = The VDD supply POR circuit was not active, or was active, but did not detect a POR event                  |

| Note 1: | Unlike the other bits in this register, this bit can be set outside of Deep Sleep.                            |

| 2.      | If multiple wake-up triggers are fired around the same time, only the first wake-up event triggered will have |

2: If multiple wake-up triggers are fired around the same time, only the first wake-up event triggered will have its wake-up status bit set.

## 6.4 Data Addressing Modes

| Note: | The execution of some instructions in the  |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|

|       | core PIC18 instruction set is changed      |  |  |  |  |  |  |  |

|       | when the PIC18 extended instruction set is |  |  |  |  |  |  |  |

|       | enabled. See Section 6.6 "Data Memory      |  |  |  |  |  |  |  |

|       | and the Extended Instruction Set" for      |  |  |  |  |  |  |  |

|       | more information.                          |  |  |  |  |  |  |  |

While the program memory can be addressed in only one way, through the PC, information in the data memory space can be addressed in several ways. For most instructions, the addressing mode is fixed. Other instructions may use up to three modes, depending on which operands are used and whether or not the extended instruction set is enabled.

The addressing modes are:

- Inherent

- Literal

- Direct

- Indirect

An additional addressing mode, Indexed Literal Offset, is available when the extended instruction set is enabled (XINST Configuration bit = 1). Its operation is discussed in more detail in **Section 6.6.1 "Indexed Addressing with Literal Offset**".

# 6.4.1 INHERENT AND LITERAL ADDRESSING

Many PIC18 control instructions do not need any argument at all; they either perform an operation that globally affects the device, or they operate implicitly on one register. This addressing mode is known as Inherent Addressing. Examples include SLEEP, RESET and DAW.

Other instructions work in a similar way, but require an additional explicit argument in the opcode. This is known as Literal Addressing mode, because they require some literal value as an argument. Examples include ADDLW and MOVLW, which respectively, add or move a literal value to the W register. Other examples include CALL and GOTO, which include a 20-bit program memory address.

## 6.4.2 DIRECT ADDRESSING

Direct Addressing specifies all or part of the source and/or destination address of the operation within the opcode itself. The options are specified by the arguments accompanying the instruction.

In the core PIC18 instruction set, bit-oriented and byte-oriented instructions use some version of Direct Addressing by default. All of these instructions include some 8-bit Literal Address as their LSB. This address specifies either a register address in one of the banks of data RAM (Section 6.3.3 "General Purpose

**Register File**"), or a location in the Access Bank (Section 6.3.2 "Access Bank") as the data source for the instruction.

The Access RAM bit, 'a', determines how the address is interpreted. When 'a' is '1', the contents of the BSR (Section 6.3.1 "Bank Select Register") are used with the address to determine the complete 12-bit address of the register. When 'a' is '0', the address is interpreted as being a register in the Access Bank. Addressing that uses the Access RAM is sometimes also known as Direct Forced Addressing mode.

A few instructions, such as MOVFF, include the entire 12-bit address (either source or destination) in their opcodes. In these cases, the BSR is ignored entirely.

The destination of the operation's results is determined by the destination bit, 'd'. When 'd' is '1', the results are stored back in the source register, overwriting its original contents. When 'd' is '0', the results are stored in the W register. Instructions without the 'd' argument have a destination that is implicit in the instruction; their destination is either the target register being operated on or the W register.

# 6.4.3 INDIRECT ADDRESSING

Indirect Addressing allows the user to access a location in data memory without giving a fixed address in the instruction. This is done by using File Select Registers (FSRs) as pointers to the locations to be read or written to. Since the FSRs are themselves located in RAM as SFRs, they can also be directly manipulated under program control. This makes FSRs very useful in implementing data structures such as tables and arrays in data memory.

The registers for Indirect Addressing are also implemented with Indirect File Operands (INDFs) that permit automatic manipulation of the pointer value with auto-incrementing, auto-decrementing or offsetting with another value. This allows for efficient code using loops, such as the example of clearing an entire RAM bank in Example 6-5. It also enables users to perform Indexed Addressing and other Stack Pointer operations for program memory in data memory.

### EXAMPLE 6-5: HOW TO CLEAR RAM (BANK 1) USING INDIRECT ADDRESSING

|         | LFSR  | FSR0, 0x100 | ; ( |                |

|---------|-------|-------------|-----|----------------|

| NEXT    | CLRF  | POSTINC0    | ;   | Clear INDF     |

|         |       |             | ;   | register then  |

|         |       |             | ;   | inc pointer    |

|         | BTFSS | FSROH, 1    | ;   | All done with  |

|         |       |             | ;   | Bank1?         |

|         | BRA   | NEXT        | ;   | NO, clear next |

| CONTINU | E     |             | ;   | YES, continue  |

|         |       |             |     |                |

# 9.0 INTERRUPTS

Devices of the PIC18F46J11 family have multiple interrupt sources and an interrupt priority feature that allows most interrupt sources to be assigned a high-priority level or a low-priority level. The high-priority interrupt vector is at 0008h and the low-priority interrupt vector is at 0018h. High-priority interrupt events will interrupt any low-priority interrupts that may be in progress.

There are 13 registers, which are used to control interrupt operation. These registers are:

- RCON

- INTCON

- INTCON2

- INTCON3

- PIR1, PIR2, PIR3

- PIE1, PIE2, PIE3

- IPR1, IPR2, IPR3

It is recommended that the Microchip header files supplied with MPLAB<sup>®</sup> IDE be used for the symbolic bit names in these registers. This allows the assembler/compiler to automatically take care of the placement of these bits within the specified register.

In general, interrupt sources have three bits to control their operation. They are:

- Flag bit to indicate that an interrupt event occurred

- Enable bit that allows program execution to branch to the interrupt vector address when the flag bit is set

- **Priority bit** to select high priority or low priority

The interrupt priority feature is enabled by setting the IPEN bit (RCON<7>). When interrupt priority is enabled, there are two bits which enable interrupts globally. Setting the GIEH bit (INTCON<7>) enables all interrupts that have the priority bit set (high priority). Setting the GIEH and GIEL bits (INTCON<76>) enables interrupts that have the priority bit cleared (low priority). When the interrupt flag, enable bit and appropriate Global Interrupt Enable (GIE) bit are set, the interrupt will vector immediately to address 0008h or 0018h, depending on the priority bit setting. Individual interrupts can be disabled through their corresponding enable bits.

When the IPEN bit is cleared (default state), the interrupt priority feature is disabled and interrupts are compatible with PIC<sup>®</sup> mid-range devices. In Compatibility mode, the interrupt priority bits for each source have no effect. INTCON<6> is the PEIE bit, which enables/disables all peripheral interrupt sources. INTCON<7> is the GIE bit, which enables/disables all interrupt sources. All interrupts branch to address 0008h in Compatibility mode.

When an interrupt is responded to, the Global Interrupt Enable bit is cleared to disable further interrupts. If the IPEN bit is cleared, this is the GIE bit. If interrupt priority levels are used, this will be either the GIEH or GIEL bit. High-priority interrupt sources can interrupt a low-priority interrupt. Low-priority interrupts are not processed while high-priority interrupts are in progress.

The return address is pushed onto the stack and the PC is loaded with the interrupt vector address (0008h or 0018h). Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bits must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine and sets the GIE bit (GIEH or GIEL if priority levels are used), which re-enables interrupts.

For external interrupt events, such as the INTx pins or the PORTB input change interrupt, the interrupt latency will be three to four instruction cycles. The exact latency is the same for one or two-cycle instructions. Individual interrupt flag bits are set regardless of the status of their corresponding enable bit or the GIE bit.

Note: Do not use the MOVFF instruction to modify any of the interrupt control registers while **any** interrupt is enabled. Doing so may cause erratic microcontroller behavior.

| R/W-1      | R/W-1                          | R/W-1                               | R/W-1             | R/W-1              | R/W-1           | R/W-1            | R/W-1         |

|------------|--------------------------------|-------------------------------------|-------------------|--------------------|-----------------|------------------|---------------|

| RBPU       | INTEDG0                        | INTEDG1                             | INTEDG2           | INTEDG3            | TMR0IP          | INT3IP           | RBIP          |

| bit 7      |                                |                                     |                   |                    |                 | ·                | bit 0         |

|            |                                |                                     |                   |                    |                 |                  |               |

| Legend:    |                                |                                     |                   |                    |                 |                  |               |

| R = Reada  |                                | W = Writable                        |                   | U = Unimplem       |                 |                  |               |

| -n = Value | e at POR                       | '1' = Bit is set                    |                   | '0' = Bit is clea  | ared            | x = Bit is unkr  | IOWN          |

| bit 7      | <b>RBPU</b> : PORT             | B Pull-up Enal                      | ole bit           |                    |                 |                  |               |

|            |                                | B pull-ups are                      |                   |                    |                 |                  |               |

|            |                                |                                     |                   | dual port tri-stat | e values        |                  |               |

| bit 6      |                                | ternal Interrupt                    | 0 Edge Select     | t bit              |                 |                  |               |

|            | •                              | on rising edge                      |                   |                    |                 |                  |               |

| bit 5      | •                              | on falling edge<br>ternal Interrupt | 1 Edge Select     | t bit              |                 |                  |               |

| DIL U      |                                | on rising edge                      | I Luge Selec      |                    |                 |                  |               |

|            |                                | on falling edge                     |                   |                    |                 |                  |               |

| bit 4      | INTEDG2: Ex                    | ternal Interrupt                    | 2 Edge Select     | t bit              |                 |                  |               |

|            |                                | on rising edge                      |                   |                    |                 |                  |               |

|            | •                              | on falling edge                     |                   |                    |                 |                  |               |

| bit 3      |                                | ternal Interrupt<br>on rising edge  | 3 Edge Select     | t bit              |                 |                  |               |

|            |                                | on falling edge                     |                   |                    |                 |                  |               |

| bit 2      | •                              | R0 Overflow Int                     | errupt Priority   | bit                |                 |                  |               |

|            | 1 = High prio                  |                                     |                   |                    |                 |                  |               |

|            | 0 = Low prior                  | •                                   |                   |                    |                 |                  |               |

| bit 1      |                                | External Interr                     | upt Priority bit  |                    |                 |                  |               |

|            | 1 = High prio<br>0 = Low prior |                                     |                   |                    |                 |                  |               |

| bit 0      | •                              | t Change Inter                      | rupt Priority bit |                    |                 |                  |               |

|            | 1 = High prio                  | -                                   |                   |                    |                 |                  |               |

|            | 0 = Low prior                  | •                                   |                   |                    |                 |                  |               |

| Note:      | Interrupt flag bits            | are set when                        | an interrupt co   | ndition occurs     | regardless of   | the state of its | corresponding |

|            | enable bit or the C            | Blobal Interrupt                    | Enable bit. Us    | er software sho    | uld ensure the  | appropriate int  |               |

|            | are clear prior to             | enabling an int                     | errupt. This fea  | ature allows for   | software pollir | ng.              |               |

# REGISTER 9-2: INTCON2: INTERRUPT CONTROL REGISTER 2 (ACCESS FF1h)

| R/W-1        | R/W-1                                                                  | R/W-1              | R/W-1            | R/W-1             | R/W-1            | R/W-1           | R/W-1  |  |  |  |  |

|--------------|------------------------------------------------------------------------|--------------------|------------------|-------------------|------------------|-----------------|--------|--|--|--|--|

| SSP2IP       | BCL2IP                                                                 | RC2IP              | TX2IP            | TMR4IP            | CTMUIP           | TMR3GIP         | RTCCIP |  |  |  |  |

| bit 7        | •                                                                      | •                  |                  |                   | •                |                 | bit C  |  |  |  |  |

| <del></del>  |                                                                        |                    |                  |                   |                  |                 |        |  |  |  |  |

| Legend:      |                                                                        |                    |                  |                   |                  |                 |        |  |  |  |  |

| R = Readab   |                                                                        | W = Writable       |                  |                   | nented bit, read |                 |        |  |  |  |  |

| -n = Value a | t POR                                                                  | '1' = Bit is set   |                  | '0' = Bit is clea | ared             | x = Bit is unkn | own    |  |  |  |  |

| bit 7        | SSDOID, Ma                                                             | ster Synchronou    | a Sorial Dort    | 2 Interrunt Drier | ity bit          |                 |        |  |  |  |  |

|              |                                                                        | ,                  |                  |                   |                  |                 |        |  |  |  |  |

|              | 1 = High priority<br>0 = Low priority                                  |                    |                  |                   |                  |                 |        |  |  |  |  |

| bit 6        | BCL2IP: Bus                                                            | s Collision Interr | upt Priority bit | (MSSP2 modu       | le)              |                 |        |  |  |  |  |

|              | 1 = High pri                                                           |                    |                  | ,                 | ,                |                 |        |  |  |  |  |

|              | 0 = Low pric                                                           | ority              |                  |                   |                  |                 |        |  |  |  |  |

| bit 5        | RC2IP: EUSART2 Receive Interrupt Priority bit                          |                    |                  |                   |                  |                 |        |  |  |  |  |

|              | 1 = High priority                                                      |                    |                  |                   |                  |                 |        |  |  |  |  |

|              | 0 = Low price                                                          | •                  |                  |                   |                  |                 |        |  |  |  |  |

| bit 4        |                                                                        | ART2 Transmit      | Interrupt Prior  | ity bit           |                  |                 |        |  |  |  |  |

|              | 1 = High pri-0 = Low price                                             | •                  |                  |                   |                  |                 |        |  |  |  |  |

| bit 3        |                                                                        | •                  | rupt Priority b  | it                |                  |                 |        |  |  |  |  |

|              | <b>TMR4IE:</b> TMR4 to PR4 Interrupt Priority bit<br>1 = High priority |                    |                  |                   |                  |                 |        |  |  |  |  |

|              | 0 = Low price                                                          | •                  |                  |                   |                  |                 |        |  |  |  |  |

| bit 2        | CTMUIP: Ch                                                             | arge Time Mea      | surement Unit    | (CTMU) Interru    | pt Priority bit  |                 |        |  |  |  |  |

|              | 1 = High pri                                                           |                    |                  |                   |                  |                 |        |  |  |  |  |

|              | 0 = Low price                                                          | -                  |                  |                   |                  |                 |        |  |  |  |  |

| bit 1        |                                                                        | ïmer3 Gate Inte    | rrupt Priority b | bit               |                  |                 |        |  |  |  |  |

|              | 1 = High pri-0 = Low price                                             |                    |                  |                   |                  |                 |        |  |  |  |  |

| bit 0        | -                                                                      | CC Interrupt Pri   | ority bit        |                   |                  |                 |        |  |  |  |  |

|              | 1 = High pri                                                           |                    | only bit         |                   |                  |                 |        |  |  |  |  |

|              | 0 = Low price                                                          | •                  |                  |                   |                  |                 |        |  |  |  |  |

# REGISTER 9-12: IPR3: PERIPHERAL INTERRUPT PRIORITY REGISTER 3 (ACCESS FA5h)

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |     |     |       |       |       |       |       |  |  |  |

|----------------------------------------------------------------------|-----|-----|-------|-------|-------|-------|-------|--|--|--|

| <b>Legend:</b> $R/\overline{W}$ = Readable, Writable if IOLOCK = 0   |     |     |       |       |       |       |       |  |  |  |

| bit 7 bit 0                                                          |     |     |       |       |       |       |       |  |  |  |

|                                                                      |     | _   | RP9R4 | RP9R3 | RP9R2 | RP9R1 | RP9R0 |  |  |  |

| U-0                                                                  | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

'0' = Bit is cleared

x = Bit is unknown

### REGISTER 10-30: RPOR9: PERIPHERAL PIN SELECT OUTPUT REGISTER 9 (BANKED ECFh)

bit 7-5 Unimplemented: Read as '0'

-n = Value at POR

bit 4-0 **RP9R<4:0>:** Peripheral Output Function is Assigned to RP9 Output Pin bits (see Table 10-14 for peripheral function numbers)

'1' = Bit is set

### REGISTER 10-31: RPOR10: PERIPHERAL PIN SELECT OUTPUT REGISTER 10 (BANKED ED0h)

| U-0   | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-----|--------|--------|--------|--------|--------|

| —     | —   |     | RP10R4 | RP10R3 | RP10R2 | RP10R1 | RP10R0 |

| bit 7 |     |     |        |        |        |        | bit 0  |

| Legend:           | $R/\overline{W}$ = Readable, Writable if IOLOCK = 0 |                             |                    |  |  |

|-------------------|-----------------------------------------------------|-----------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                                    | U = Unimplemented bit, read | as '0'             |  |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared        | x = Bit is unknown |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP10R<4:0>:** Peripheral Output Function is Assigned to RP10 Output Pin bits (see Table 10-14 for peripheral function numbers)

### REGISTER 10-32: RPOR11: PERIPHERAL PIN SELECT OUTPUT REGISTER 11 (BANKED ED1h)

| U-0   | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-----|--------|--------|--------|--------|--------|

| —     | —   | —   | RP11R4 | RP11R3 | RP11R2 | RP11R1 | RP11R0 |

| bit 7 |     |     |        |        |        |        | bit 0  |

| Legend:           | $R/\overline{W}$ = Readable, Writable if IOLOCK = 0 |                             |                    |  |

|-------------------|-----------------------------------------------------|-----------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit                                    | U = Unimplemented bit, read | d as '0'           |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared        | x = Bit is unknown |  |

### bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP11R<4:0>:** Peripheral Output Function is Assigned to RP11 Output Pin bits (see Table 10-14 for peripheral function numbers)

# REGISTER 11-5: PMEH: PARALLEL PORT ENABLE REGISTER HIGH BYTE (BANKED F57h)<sup>(1)</sup>

| U-0                               | R/W-0      | U-0                | U-0                                | U-0                                    | U-0 | U-0 | U-0   |  |

|-----------------------------------|------------|--------------------|------------------------------------|----------------------------------------|-----|-----|-------|--|

| _                                 | PTEN14     | —                  |                                    | —                                      | —   | _   | —     |  |

| bit 7                             |            |                    |                                    |                                        |     |     | bit 0 |  |

|                                   |            |                    |                                    |                                        |     |     |       |  |

| Legend:                           |            |                    |                                    |                                        |     |     |       |  |

| R = Readable bit W = Writable bit |            | oit                | U = Unimplemented bit, read as '0' |                                        |     |     |       |  |

| -n = Value a                      | it POR     | '1' = Bit is set   |                                    | '0' = Bit is cleared x = Bit is unknow |     |     | nown  |  |

|                                   |            |                    |                                    |                                        |     |     |       |  |

| bit 7                             | Unimpleme  | nted: Read as '0   | ,                                  |                                        |     |     |       |  |

| bit 6                             | PTEN14: PN | ICS Port Enable    | bit                                |                                        |     |     |       |  |

|                                   |            | hip select line    |                                    |                                        |     |     |       |  |

|                                   | 0 = PMCS f | unctions as port l | I/O                                |                                        |     |     |       |  |

| bit 5-0                           | Unimpleme  | nted: Read as '0   | ,                                  |                                        |     |     |       |  |

Note 1: This register is only available in 44-pin devices.

# REGISTER 11-6: PMEL: PARALLEL PORT ENABLE REGISTER LOW BYTE (BANKED F56h)<sup>(1)</sup>

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| PTEN7 | PTEN6 | PTEN5 | PTEN4 | PTEN3 | PTEN2 | PTEN1 | PTEN0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                        |                    |  |

|-------------------|------------------|------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |  |

| bit 7-2 | PTEN<7:2>: PMP Address Port Enable bits                                                                                                            |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = PMA<7:2> function as PMP address lines                                                                                                         |

|         | 0 = PMA<7:2> function as port I/O                                                                                                                  |

| bit 1-0 | PTEN<1:0>: PMALH/PMALL Strobe Enable bits                                                                                                          |

|         | <ul> <li>1 = PMA&lt;1:0&gt; function as either PMA&lt;1:0&gt; or PMALH and PMALL</li> <li>0 = PMA&lt;1:0&gt; pads functions as port I/O</li> </ul> |

Note 1: This register is only available in 44-pin devices.

# 11.3 MASTER PORT MODES

In its Master modes, the PMP module provides an 8-bit data bus, up to 16 bits of address, and all the necessary control signals to operate a variety of external parallel devices, such as memory devices, peripherals and slave microcontrollers. To use the PMP as a master, the module must be enabled (PMPEN = 1) and the mode must be set to one of the two possible Master modes (PMMODEH<1:0> = 10 or 11).

Because there are a number of parallel devices with a variety of control methods, the PMP module is designed to be extremely flexible to accommodate a range of configurations. Some of these features include:

- · 8-Bit and 16-Bit Data modes on an 8-bit data bus

- · Configurable address/data multiplexing

- Up to two chip select lines

- Up to 16 selectable address lines

- · Address auto-increment and auto-decrement

- · Selectable polarity on all control lines

- Configurable Wait states at different stages of the read/write cycle

# 11.3.1 PMP AND I/O PIN CONTROL

Multiple control bits are used to configure the presence or absence of control and address signals in the module. These bits are PTBEEN, PTWREN, PTRDEN and PTEN<15:0>. They give the user the ability to conserve pins for other functions and allow flexibility to control the external address. When any one of these bits is set, the associated function is present on its associated pin; when clear, the associated pin reverts to its defined I/O port function.

Setting a PTENx bit will enable the associated pin as an address pin and drive the corresponding data contained in the PMADDR register. Clearing a PTENx bit will force the pin to revert to its original I/O function.

For the pins configured as chip select (PMCS) with the corresponding PTENx bit set, the PTEN0 and PTEN1 bits will also control the PMALL and PMALH signals. When multiplexing is used, the associated address latch signals should be enabled.

# 11.3.2 READ/WRITE CONTROL

The PMP module supports two distinct read/write signaling methods. In Master Mode 1, read and write strobes are combined into a single control line, PMRD/PMWR. A second control line, PMENB, determines when a read or write action is to be taken. In Master Mode 2, separate read and write strobes (PMRD and PMWR) are supplied on separate pins.

All control signals (PMRD, PMWR, PMBE, PMENB, PMAL and PMCS) can be individually configured as either positive or negative polarity. Configuration is controlled by separate bits in the PMCONL register.

Note that the polarity of control signals that share the same output pin (for example, PMWR and PMENB) are controlled by the same bit; the configuration depends on which Master Port mode is being used.

# 11.3.3 DATA WIDTH

The PMP supports data widths of both 8 bits and 16 bits. The data width is selected by the MODE16 bit (PMMODEH<2>). Because the data path into and out of the module is only 8 bits wide, 16-bit operations are always handled in a multiplexed fashion, with the Least Significant Byte (LSB) of data being presented first. To differentiate data bytes, the byte enable control strobe, PMBE, is used to signal when the Most Significant Byte (MSB) of data is being presented on the data lines.

# 11.3.4 ADDRESS MULTIPLEXING

In either of the Master modes (PMMODEH<1:0> = 1x), the user can configure the address bus to be multiplexed together with the data bus. This is accomplished by using the ADRMUX<1:0> bits (PMCONH<4:3>). There are three address multiplexing modes available; typical pinout configurations for these modes are displayed in Figure 11-9, Figure 11-10 and Figure 11-11.

In Demultiplexed mode (PMCONH<4:3> = 00), data and address information are completely separated. Data bits are presented on PMD<7:0> and address bits are presented on PMADDRH<6:0> and PMADDRL<7:0>.

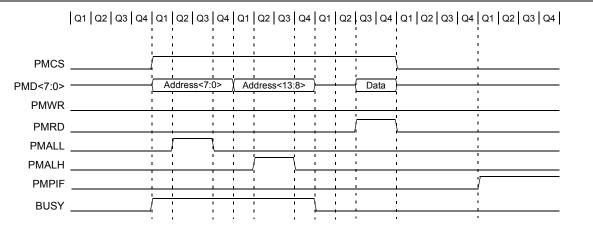

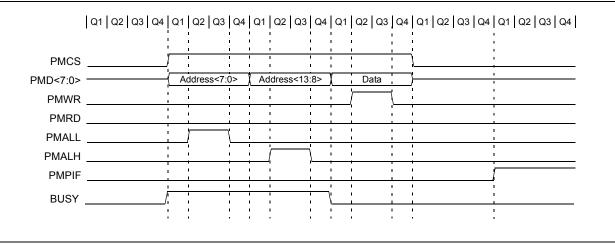

In Partially Multiplexed mode (PMCONH<4:3> = 01), the lower eight bits of the address are multiplexed with the data pins on PMD<7:0>. The upper eight bits of address are unaffected and are presented on PMADDRH<6:0>. The PMA0 pin is used as an address latch, and presents the address latch low enable strobe (PMALL). The read and write sequences are extended by a complete CPU cycle during which the address is presented on the PMD<7:0> pins.

In Fully Multiplexed mode (PMCONH<4:3> = 10), the entire 16 bits of the address are multiplexed with the data pins on PMD<7:0>. The PMA0 and PMA1 pins are used to present address latch low enable (PMALL) and address latch high enable (PMALH) strobes, respectively. The read and write sequences are extended by two complete CPU cycles. During the first cycle, the lower eight bits of the address are presented on the PMD<7:0> pins with the PMALL strobe active. During the second cycle, the upper eight bits of the address are presented on the PMD<7:0> pins with the PMALH strobe active. In the event the upper address bits are configured as chip select pins, the corresponding address bits are automatically forced to '0'.

### FIGURE 11-18: WRITE TIMING, 8-BIT DATA, PARTIALLY MULTIPLEXED ADDRESS, ENABLE **STROBE** Q1 Q2 Q3 Q4 PMCS \_\_\_\_\_ Address<7:0> Data PMD<7:0> ----PMRD/PMWR PMENB \_\_\_\_\_ PMALL 1 1 PMPIF i. ÷ BUSY J

# FIGURE 11-19: READ TIMING, 8-BIT DATA, FULLY MULTIPLEXED 16-BIT ADDRESS

# FIGURE 11-20: WRITE TIMING, 8-BIT DATA, FULLY MULTIPLEXED 16-BIT ADDRESS

# 17.1 RTCC MODULE REGISTERS

The RTCC module registers are divided into following categories:

# **RTCC Control Registers**

- RTCCFG

- RTCCAL

- PADCFG1

- ALRMCFG

- ALRMRPT

# **RTCC Value Registers**

- RTCVALH and RTCVALL Can access the following registers

- YEAR

- MONTH

- DAY

- WEEKDAY

- HOUR

- MINUTE

- SECOND

# **Alarm Value Registers**

- ALRMVALH and ALRMVALL Can access the following registers:

- ALRMMNTH

- ALRMDAY

- ALRMWD

- ALRMHR

- ALRMMIN

- ALRMSEC

- Note: The RTCVALH and RTCVALL registers can be accessed through RTCRPT<1:0>. ALRMVALH and ALRMVALL can be accessed through ALRMPTR<1:0>.

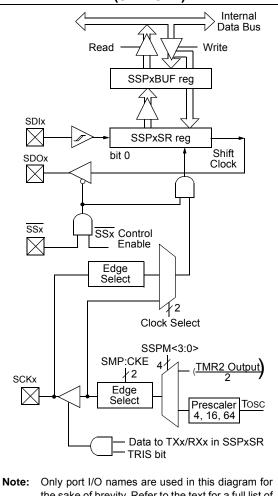

# 19.2 Control Registers

Each MSSP module has three associated control registers. These include a status register (SSPxSTAT) and two control registers (SSPxCON1 and SSPxCON2). The use of these registers and their individual Configuration bits differ significantly depending on whether the MSSP module is operated in SPI or I<sup>2</sup>C mode.

Additional details are provided under the individual sections.

Note: In devices with more than one MSSP module, it is very important to pay close attention to the SSPxCON register names. SSP1CON1 and SSP1CON2 control different operational aspects of the same module, while SSP1CON1 and SSP2CON1 control the same features for two different modules.

# 19.3 SPI Mode

The SPI mode allows 8 bits of data to be synchronously transmitted and received simultaneously. All four modes of SPI are supported.

When MSSP2 is used in SPI mode, it can optionally be configured to work with the SPI DMA submodule described in **Section 19.4 "SPI DMA Module"**.

To accomplish communication, typically three pins are used:

- Serial Data Out (SDOx) RC5/SDO1/RP16 or SDO2/Remappable

- Serial Data In (SDIx) RC4/SDI1/SDA1/RP15 or SDI2/Remappable

- Serial Clock (SCKx) RC3/SCK1/SCL1/RP14 or SCK2/Remappable

Additionally, a fourth pin may be used when in a Slave mode of operation:

Slave Select (SSx) – RA5/AN4/SS1/ HLVDIN/RP2 or SS2/Remappable

Figure 19-1 depicts the block diagram of the MSSP module when operating in SPI mode.

#### FIGURE 19-1: MSSPx BLOCK DIAGRAM (SPI MODE)

ote: Only port I/O names are used in this diagram for the sake of brevity. Refer to the text for a full list of multiplexed functions.

| R/W-0      | R/W-0                             | R/W-0                            | R/W-0         | R/W-0             | R/W-0            | R-1             | R/W-0 |

|------------|-----------------------------------|----------------------------------|---------------|-------------------|------------------|-----------------|-------|

| CSRC       | TX9                               | TXEN <sup>(1)</sup>              | SYNC          | SENDB             | BRGH             | TRMT            | TX9D  |

| bit 7      |                                   |                                  |               |                   |                  |                 | bit   |

| Legend:    |                                   |                                  |               |                   |                  |                 |       |

| R = Reada  | ble bit                           | W = Writable                     | bit           | U = Unimplem      | nented bit. read | d as '0'        |       |

| -n = Value | at POR                            | '1' = Bit is set                 |               | '0' = Bit is clea |                  | x = Bit is unkr | nown  |

|            |                                   |                                  |               |                   |                  |                 |       |

| bit 7      |                                   | Source Select                    | bit           |                   |                  |                 |       |

|            | Asynchronous<br>Don't care.       | <u>s mode:</u>                   |               |                   |                  |                 |       |

|            | Synchronous                       |                                  |               |                   |                  |                 |       |

|            |                                   | ode (clock gen<br>de (clock from |               |                   |                  |                 |       |

| bit 6      |                                   | ansmit Enable I                  |               |                   |                  |                 |       |

|            |                                   | -bit transmissio                 |               |                   |                  |                 |       |

|            |                                   | -bit transmissio                 |               |                   |                  |                 |       |

| bit 5      |                                   | mit Enable bit <sup>(1</sup>     |               |                   |                  |                 |       |

|            | 1 = Transmit<br>0 = Transmit      |                                  | the TXX/CKX   | pin is configure  | d as an output   |                 |       |

| bit 4      | SYNC: EUSA                        | RT Mode Sele                     | ct bit        |                   |                  |                 |       |

|            | 1 = Synchron                      |                                  |               |                   |                  |                 |       |

|            | 0 = Asynchro                      |                                  |               |                   |                  |                 |       |

| bit 3      |                                   | d Break Chara                    | cter bit      |                   |                  |                 |       |

|            |                                   |                                  |               | n (cleared by ha  | rdware upon c    | ompletion)      |       |

|            | <u>Synchronous</u><br>Don't care. |                                  | ľ             |                   |                  |                 |       |

| bit 2      | BRGH: High                        | Baud Rate Sele                   | ect bit       |                   |                  |                 |       |

|            | Asynchronous                      | ed                               |               |                   |                  |                 |       |

|            | 0 = Low spee<br>Synchronous       |                                  |               |                   |                  |                 |       |

|            | Unused in this                    |                                  |               |                   |                  |                 |       |

| bit 1      | TRMT: Transı                      | mit Shift Regist                 | er Status bit |                   |                  |                 |       |

|            | 1 = TSR emp<br>0 = TSR full       | ty                               |               |                   |                  |                 |       |

| bit 0      | TX9D: 9 <sup>th</sup> bit         | of Transmit Da                   | ta            |                   |                  |                 |       |

|            |                                   |                                  | lu            |                   |                  |                 |       |

# 20.2 EUSART Asynchronous Mode

The Asynchronous mode of operation is selected by clearing the SYNC bit (TXSTAx<4>). In this mode, the EUSART uses standard Non-Return-to-Zero (NRZ) format (one Start bit, eight or nine data bits and one Stop bit). The most common data format is 8 bits. An on-chip dedicated 8-bit/16-bit BRG can be used to derive standard baud rate frequencies from the oscillator.

The EUSART transmits and receives the LSb first. The EUSART's transmitter and receiver are functionally independent but use the same data format and baud rate. The BRG produces a clock, either x16 or x64 of the bit shift rate, depending on the BRGH and BRG16 bits (TXSTAx<2> and BAUDCONx<3>). Parity is not supported by the hardware but can be implemented in software and stored as the ninth data bit.

When operating in Asynchronous mode, the EUSART module consists of the following important elements:

- Baud Rate Generator

- Sampling Circuit

- Asynchronous Transmitter

- · Asynchronous Receiver

- Auto-Wake-up on Sync Break Character

- 12-Bit Break Character Transmit

- Auto-Baud Rate Detection

### 20.2.1 EUSART ASYNCHRONOUS TRANSMITTER

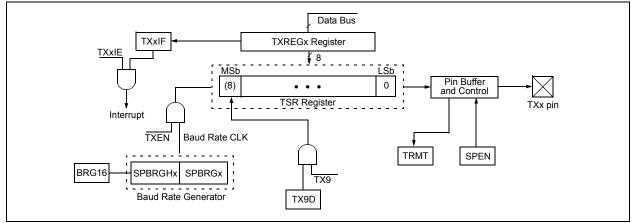

Figure 20-3 displays the EUSART transmitter block diagram.

The heart of the transmitter is the Transmit (Serial) Shift Register (TSR). The Shift register obtains its data from the Read/Write Transmit Buffer register, TXREGx. The TXREGx register is loaded with data in software. The TSR register is not loaded until the Stop bit has been transmitted from the previous load. As soon as the Stop bit is transmitted, the TSR is loaded with new data from the TXREGx register (if available). Once the TXREGx register transfers the data to the TSR register (occurs in one Tcy), the TXREGx register is empty and the TXxIF flag bit is set. This interrupt can be enabled or disabled by setting or clearing the interrupt enable bit, TXxIE. TXxIF will be set regardless of the state of TXxIE; it cannot be cleared in software. TXxIF is also not cleared immediately upon loading TXREGx, but becomes valid in the second instruction cycle following the load instruction. Polling TXxIF immediately following a load of TXREGx will return invalid results.

While TXxIF indicates the status of the TXREGx register; another bit, TRMT (TXSTAx<1>), shows the status of the TSR register. TRMT is a read-only bit, which is set when the TSR register is empty. No interrupt logic is tied to this bit so the user has to poll this bit in order to determine if the TSR register is empty.

| Note 1: | The TSR register is not mapped in data memory, so it is not available to the user. |

|---------|------------------------------------------------------------------------------------|

| 2:      | Flag bit, TXxIF, is set when enable bit, TXEN, is set.                             |

To set up an Asynchronous Transmission:

- 1. Initialize the SPBRGHx:SPBRGx registers for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Enable the asynchronous serial port by clearing bit, SYNC, and setting bit, SPEN.

- 3. If interrupts are desired, set enable bit, TXxIE.

- 4. If 9-bit transmission is desired, set transmit bit, TX9. Can be used as address/data bit.

- 5. Enable the transmission by setting bit, TXEN, which will also set bit, TXxIF.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit, TX9D.

- 7. Load data to the TXREGx register (starts transmission).

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

## FIGURE 20-3: EUSART TRANSMIT BLOCK DIAGRAM

# REGISTER 26-3: CONFIG2L: CONFIGURATION REGISTER 2 LOW (BYTE ADDRESS 300002h)

| R/WO-1          | R/WO-1                                                | U-0                                                                                                     | R/WO-1           | R/WO-1           | R/WO-1           | R/WO-1          | R/WO-1         |  |  |  |

|-----------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------|------------------|------------------|------------------|-----------------|----------------|--|--|--|

| IESO            | FCMEN                                                 | _                                                                                                       | LPT10SC          | T1DIG            | FOSC2            | FOSC1           | FOSC0          |  |  |  |

| bit 7           | •                                                     |                                                                                                         |                  |                  |                  |                 | bit (          |  |  |  |

| <u> </u>        |                                                       |                                                                                                         |                  |                  |                  |                 |                |  |  |  |

| Legend:         |                                                       |                                                                                                         |                  |                  |                  |                 |                |  |  |  |

| R = Readable    |                                                       | WO = Write-C                                                                                            |                  | •                | mented bit, read |                 |                |  |  |  |

| -n = Value at I | Reset                                                 | '1' = Bit is set                                                                                        |                  | '0' = Bit is cle | ared             | x = Bit is unkr | nown           |  |  |  |

| bit 7           |                                                       | nood Start un (                                                                                         | Intornal/Extor   | aal Oacillator S | witchovor) Cor   | stral hit       |                |  |  |  |

| JIL 7           |                                                       | : Two-Speed Start-up (Internal/External Oscillator Switchover) Control bit<br>wo-Speed Start-up enabled |                  |                  |                  |                 |                |  |  |  |

|                 |                                                       | ed Start-up ena                                                                                         |                  |                  |                  |                 |                |  |  |  |

| bit 6           | FCMEN: Fail                                           | -Safe Clock Mc                                                                                          | nitor Enable b   | bit              |                  |                 |                |  |  |  |

|                 | 1 = Fail-Safe                                         | Clock Monitor                                                                                           | enabled          |                  |                  |                 |                |  |  |  |

|                 | 0 = Fail-Safe                                         | Clock Monitor                                                                                           | disabled         |                  |                  |                 |                |  |  |  |

| bit 5           | Unimplemen                                            | ted: Read as '                                                                                          | כ'               |                  |                  |                 |                |  |  |  |

| bit 4           |                                                       | PT1OSC: Low-Power Timer1 Oscillator Enable bit                                                          |                  |                  |                  |                 |                |  |  |  |

|                 |                                                       | scillator configu<br>scillator configu                                                                  | • •              | •                | 1                |                 |                |  |  |  |

| bit 3           | T1DIG: Secondary Clock Source T1OSCEN Enforcement bit |                                                                                                         |                  |                  |                  |                 |                |  |  |  |

|                 |                                                       | ary oscillator cl<br>N (T1CON<3>                                                                        |                  | ay be selecte    | d (OSCCON<1      | :0> = 01) reg   | ardless of the |  |  |  |

|                 |                                                       | ary oscillator clo                                                                                      |                  | y not be select  | ed unless T1C    | ON<3> = 1       |                |  |  |  |

| bit 2-0         | FOSC<2:0>:                                            | Oscillator Sele                                                                                         | ction bits       |                  |                  |                 |                |  |  |  |

|                 |                                                       | 111 = ECPLL oscillator with PLL software controlled, CLKO on RA6                                        |                  |                  |                  |                 |                |  |  |  |

|                 |                                                       | 110 = EC oscillator with CLKO on RA6                                                                    |                  |                  |                  |                 |                |  |  |  |

|                 |                                                       | 101 = HSPLL oscillator with PLL software controlled<br>100 = HS oscillator                              |                  |                  |                  |                 |                |  |  |  |

|                 |                                                       | SCPLLO, intern                                                                                          | al oscillator w  | ith PLL softwa   | re controlled, C | LKO on RA6, p   | ort function o |  |  |  |

|                 |                                                       | SCPLL, interna                                                                                          |                  |                  |                  |                 |                |  |  |  |

|                 |                                                       | SCO internal os                                                                                         |                  | •                | ,                |                 |                |  |  |  |

|                 | 000 = INTOS                                           | SC internal osc                                                                                         | liator block (IN | NIRC/INTOSC      | ), port function | on RA6 and R    | 47             |  |  |  |

| POP         |                                   | Рор Тор о                                                             | f Return                                                      | Stack                                              |                                                                                                         |

|-------------|-----------------------------------|-----------------------------------------------------------------------|---------------------------------------------------------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| Synta       | ax:                               | POP                                                                   |                                                               |                                                    |                                                                                                         |

| Oper        | ands:                             | None                                                                  |                                                               |                                                    |                                                                                                         |

| Oper        | ation:                            | $(TOS) \rightarrow b$                                                 | it bucket                                                     |                                                    |                                                                                                         |

| Statu       | is Affected:                      | None                                                                  |                                                               |                                                    |                                                                                                         |

| Encoding:   |                                   | 0000                                                                  | 0000                                                          | 000                                                | 0 0110                                                                                                  |

| Desc        | ription:                          | stack and i<br>then becor<br>was pushe<br>This instru-<br>the user to | s discard<br>nes the p<br>d onto th<br>ction is p<br>properly | led. Th<br>previou<br>le retur<br>rovideo<br>manag | ff the return<br>e TOS value<br>s value that<br>n stack.<br>d to enable<br>ge the return<br>ware stack. |

| Word        | ds:                               | 1                                                                     |                                                               |                                                    |                                                                                                         |

| Cycle       | es:                               | 1                                                                     |                                                               |                                                    |                                                                                                         |

| QC          | ycle Activity:                    |                                                                       |                                                               |                                                    |                                                                                                         |

|             | Q1                                | Q2                                                                    | Q                                                             | 3                                                  | Q4                                                                                                      |

|             | Decode                            | No                                                                    | POP 1                                                         |                                                    | No                                                                                                      |

|             |                                   | operation                                                             | valu                                                          | ie                                                 | operation                                                                                               |

| <u>Exan</u> | nple:                             | POP<br>GOTO                                                           | NEW                                                           |                                                    |                                                                                                         |

|             | Before Instruc<br>TOS<br>Stack (1 | tion<br>level down)                                                   |                                                               | 0031A2<br>014332                                   |                                                                                                         |

|             | After Instructio<br>TOS<br>PC     | n                                                                     |                                                               | 014332<br>NEW                                      | 2h                                                                                                      |

| PUSH             | 4                                            | Push Top o                          | of Ret                                 | urn Stac                                     | :k                                                   |

|------------------|----------------------------------------------|-------------------------------------|----------------------------------------|----------------------------------------------|------------------------------------------------------|

| Synta            | IX:                                          | PUSH                                |                                        |                                              |                                                      |

| Opera            | ands:                                        | None                                |                                        |                                              |                                                      |

| Opera            | ation:                                       | $(PC + 2) \rightarrow$              | TOS                                    |                                              |                                                      |

| Status           | s Affected:                                  | None                                |                                        |                                              |                                                      |

| Enco             | ding:                                        | 0000                                | 0000                                   | 000                                          | 0 0101                                               |

| Desci            | ription:                                     |                                     | tack. 1<br>shed d<br>tion al<br>ack by | The prev<br>own on t<br>lows imp<br>modifyir | ious TOS<br>the stack.<br>plementing a<br>ng TOS and |

| Word             | s:                                           | 1                                   |                                        |                                              |                                                      |

| Cycle            | s:                                           | 1                                   |                                        |                                              |                                                      |

| QCy              | cle Activity:                                |                                     |                                        |                                              |                                                      |

| -                | Q1                                           | Q2                                  | (                                      | 23                                           | Q4                                                   |

|                  | Decode                                       | PUSH<br>PC + 2 onto<br>return stack | •                                      | No<br>ration                                 | No<br>operation                                      |

|                  |                                              |                                     |                                        |                                              |                                                      |