Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 48MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 34                                                                          |

| Program Memory Size        | 16KB (8K x 16)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 3.8K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.15V ~ 3.6V                                                                |

| Data Converters            | A/D 13x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

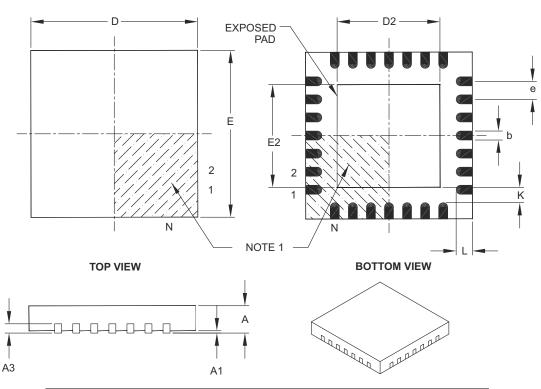

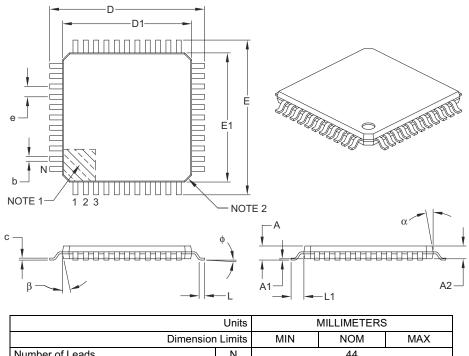

| Package / Case             | 44-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 44-QFN (8x8)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f44j11t-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2.4.1 CONSIDERATIONS FOR CERAMIC CAPACITORS

In recent years, large value, low-voltage, surface-mount ceramic capacitors have become very cost effective in sizes up to a few tens of microfarad. The low-ESR, small physical size and other properties make ceramic capacitors very attractive in many types of applications.

Ceramic capacitors are suitable for use with the VDDCORE voltage regulator of this microcontroller. However, some care is needed in selecting the capacitor to ensure that it maintains sufficient capacitance over the intended operating range of the application.

Typical low-cost, 10  $\mu$ F ceramic capacitors are available in X5R, X7R and Y5V dielectric ratings (other types are also available, but are less common). The initial tolerance specifications for these types of capacitors are often specified as ±10% to ±20% (X5R and X7R), or -20%/+80% (Y5V). However, the effective capacitance that these capacitors provide in an application circuit will also vary based on additional factors, such as the applied DC bias voltage and the temperature. The total in-circuit tolerance is, therefore, much wider than the initial tolerance specification.

The X5R and X7R capacitors typically exhibit satisfactory temperature stability (ex:  $\pm 15\%$  over a wide temperature range, but consult the manufacturer's data sheets for exact specifications). However, Y5V capacitors typically have extreme temperature tolerance specifications of  $\pm 22\%/-82\%$ . Due to the extreme temperature tolerance, a 10 µF nominal rated Y5V type capacitor may not deliver enough total capacitance to meet minimum VDDCORE voltage regulator stability and transient response requirements. Therefore, Y5V capacitors are not recommended for use with the VDDCORE regulator if the application must operate over a wide temperature range.

In addition to temperature tolerance, the effective capacitance of large value ceramic capacitors can vary substantially, based on the amount of DC voltage applied to the capacitor. This effect can be very significant, but is often overlooked or is not always documented.

A typical DC bias voltage vs. capacitance graph for X7R type and Y5V type capacitors is shown in Figure 2-4.

#### FIGURE 2-4: DC BIAS VOLTAGE vs. CAPACITANCE **CHARACTERISTICS** Change (%) 0 -10 6V Capacitor -20 -30 Capacitance -40 10V Capacitor -50 -60 -70 6.3V Capacitor -80 -9 10 11 12 13 0 2 3 7 8 14 15 16 DC Bias Voltage (VDC)

When selecting a ceramic capacitor to be used with the VDDCORE voltage regulator, it is suggested to select a high-voltage rating, so that the operating voltage is a small percentage of the maximum rated capacitor voltage. For example, choose a ceramic capacitor rated at 16V for the 2.5V VDDCORE voltage. Suggested capacitors are shown in Table 2-1.

#### 2.5 ICSP Pins

The PGC and PGD pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of ohms, not to exceed 100 $\Omega$ .

Pull-up resistors, series diodes, and capacitors on the PGC and PGD pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits, and pin input voltage high (VIH) and input low (VIL) requirements.

For device emulation, ensure that the "Communication Channel Select" (i.e., PGCx/PGDx pins), programmed into the device, matches the physical connections for the ICSP to the Microchip debugger/emulator tool.

For more information on available Microchip development tools connection requirements, refer to **Section 28.0 "Development Support"**.

| R/W-0                      |                                               |                                                    |                         |                                                  |                  |                 |       |

|----------------------------|-----------------------------------------------|----------------------------------------------------|-------------------------|--------------------------------------------------|------------------|-----------------|-------|

|                            | R/W-0                                         | R/W-0                                              | R/W-0                   | R/W-0                                            | R/W-0            | R/W-0           | R/W-0 |

| INTSRC                     | PLLEN                                         | TUN5                                               | TUN4                    | TUN3                                             | TUN2             | TUN1            | TUN0  |

| it 7                       |                                               |                                                    |                         |                                                  |                  |                 | bit ( |

| .egend:                    |                                               |                                                    |                         |                                                  |                  |                 |       |

| .egenu.<br>R = Readable bi | •                                             | W = Writable b                                     | <b>.</b> :+             |                                                  | contod bit road  |                 |       |

|                            |                                               |                                                    | JIL                     | •                                                | nented bit, read |                 |       |

| n = Value at PC            | R                                             | '1' = Bit is set                                   |                         | '0' = Bit is clea                                | ared             | x = Bit is unkn | own   |

| :                          | 1 = 31.25 kHz                                 | z device clock d                                   | erived from 8           | cy Source Sele<br>3 MHz INTOSC<br>rom INTRC inte | source (divide-  | by-256 enabled  | I)    |

| :                          | PLLEN: Frequ<br>1 = PLL enab<br>0 = PLL disab |                                                    | <sup>-</sup> Enable bit |                                                  |                  |                 |       |

|                            | 011111 = Ma<br>011110<br>•<br>•<br>•          | requency Tunin<br>ximum frequen<br>nter frequency; | су                      | odule is running                                 | at the calibrate | ed frequency    |       |

#### REGISTER 3-1: OSCTUNE: OSCILLATOR TUNING REGISTER (ACCESS F9Bh)

#### 3.3 Clock Sources and Oscillator Switching

Like previous PIC18 enhanced devices, the PIC18F46J11 family includes a feature that allows the device clock source to be switched from the main oscillator to an alternate, low-frequency clock source. PIC18F46J11 family devices offer two alternate clock sources. When an alternate clock source is enabled, the various power-managed operating modes are available.

Essentially, there are three clock sources for these devices:

- Primary Oscillators

- · Secondary Oscillators

- Internal Oscillator Block

The **Primary Oscillators** include the External Crystal and Resonator modes, the External Clock modes and the internal oscillator block. The particular mode is defined by the FOSC<2:0> Configuration bits. The details of these modes are covered earlier in this chapter. The **Secondary Oscillators** are external sources that are not connected to the OSC1 or OSC2 pins. These sources may continue to operate even after the controller is placed in a power-managed mode.

PIC18F46J11 family devices offer the Timer1 oscillator as a secondary oscillator. This oscillator, in all power-managed modes, is often the time base for functions such as a Real-Time Clock (RTC). Most often, a 32.768 kHz watch crystal is connected between the RC0/T1OSO/T1CKI/RP11 and RC1/T1OSI/RP12 pins. Like the HS Oscillator mode circuits, loading capacitors are also connected from each pin to ground. The Timer1 oscillator is discussed in more detail in **Section 13.5 "Timer1 Oscillator"**.

In addition to being a primary clock source, the **postscaled internal clock** is available as a power-managed mode clock source. The INTRC source is also used as the clock source for several special features, such as the WDT and Fail-Safe Clock Monitor (FSCM).

### 5.2 Master Clear (MCLR)

The Master Clear Reset (MCLR) pin provides a method for triggering a hard external Reset of the device. A Reset is generated by holding the pin low. PIC18 extended microcontroller devices have a noise filter in the MCLR Reset path, which detects and ignores small pulses.

The  $\overline{\text{MCLR}}$  pin is not driven low by any internal Resets, including the WDT.

#### 5.3 Power-on Reset (POR)

A POR condition is generated on-chip whenever VDD rises above a certain threshold. This allows the device to start in the initialized state when VDD is adequate for operation.

To take advantage of the POR circuitry, tie the  $\overline{\text{MCLR}}$  pin through a resistor (1 k $\Omega$  to 10 k $\Omega$ ) to VDD. This will eliminate external RC components usually needed to create a POR delay.

When the device starts normal operation (i.e., exits the Reset condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in Reset until the operating conditions are met.

POR events are captured by the  $\overrightarrow{POR}$  bit (RCON<1>). The state of the bit is set to '0' whenever a Power-on Reset occurs; it does not change for any other Reset event.  $\overrightarrow{POR}$  is not reset to '1' by any hardware event. To capture multiple events, the user manually resets the bit to '1' in software following any POR.

#### 5.4 Brown-out Reset (BOR)

"F" devices incorporate two types of BOR circuits: one which monitors VDDCORE and one which monitors VDD. Only one BOR circuit can be active at a time. When in normal Run mode, Idle or normal Sleep modes, the BOR circuit that monitors VDDCORE is active and will cause the device to be held in BOR if VDDCORE drops below VBOR (parameter D005). Once VDDCORE rises back above VBOR, the device will be held in Reset until the expiration of the Power-up Timer, with period, TPWRT (parameter 33).

During Deep Sleep operation, the on-chip core voltage regulator is disabled and VDDCORE is allowed to drop to ground levels. If the Deep Sleep BOR circuit is enabled by the DSBOREN Configuration bit (CONFIG3L<2> = 1), it will monitor VDD. If VDD drops below the VDSBOR threshold, the device will be held in a Reset state similar to POR. All registers will be set back to their POR Reset values and the contents of the DSGPR0 and DSGPR1 holding registers will be lost.

Additionally, if any I/O pins had been configured as outputs during Deep Sleep, these pins will be tri-stated and the device will no longer be held in Deep Sleep. Once the VDD voltage recovers back above the VDSBOR threshold, and once the core voltage regulator achieves a VDDCORE voltage above VBOR, the device will begin executing code again normally, but the DS bit in the WDTCON register will not be set. The device behavior will be similar to hard cycling all power to the device.

On "LF" devices, the VDDCORE BOR circuit is always disabled because the internal core voltage regulator is disabled. Instead of monitoring VDDCORE, PIC18LF devices in this family can use the VDD BOR circuit to monitor VDD excursions below the VDSBOR threshold. The VDD BOR circuit can be disabled by setting the DSBOREN bit = 0.

The VDD BOR circuit is enabled when DSBOREN = 1 on "LF" devices, or on "F" devices while in Deep Sleep with DSBOREN = 1. When enabled, the VDD BOR circuit is extremely low power (typ. 40 nA) during normal operation above ~2.3V on VDD. If VDD drops below this DSBOR arming level when the VDD BOR circuit is enabled, the device may begin to consume additional current (typ. 50  $\mu$ A) as internal features of the circuit power up. The higher current is necessary to achieve more accurate sensing of the VDD level. However, the device will not enter Reset until VDD falls below the VDSBOR threshold.

#### 5.4.1 DETECTING BOR

The BOR bit always resets to '0' on any VDDCORE, BOR or POR event. This makes it difficult to determine if a Brown-out Reset event has occurred just by reading the state of BOR alone. A more reliable method is to simultaneously check the state of both POR and BOR. This assumes that the POR bit is reset to '1' in software immediately after any Power-on Reset event. If BOR is '0' while POR is '1', it can be reliably assumed that a Brown-out Reset event has occurred.

If the voltage regulator is disabled (LF devices), the VDDCORE BOR functionality is disabled. In this case, the BOR bit cannot be used to determine a Brown-out Reset event. The BOR bit is still cleared by a Power-on Reset event.

#### TABLE 6-3: NON-ACCESS BANK SPECIAL FUNCTION REGISTER MAP

| Address | Name                    | Address | Name    | Address | Name | Address | Name    | Address | Name                  |

|---------|-------------------------|---------|---------|---------|------|---------|---------|---------|-----------------------|

| F5Fh    | PMCONH <sup>(1)</sup>   | F3Fh    | RTCCFG  | F1Fh    | —    | EFFh    | PPSCON  | EDFh    | _                     |

| F5Eh    | PMCONL <sup>(1)</sup>   | F3Eh    | RTCCAL  | F1Eh    | _    | EFEh    | RPINR24 | EDEh    | RPOR24 <sup>(1)</sup> |

| F5Dh    | PMMODEH <sup>(1)</sup>  | F3Dh    | REFOCON | F1Dh    | _    | EFDh    | RPINR23 | EDDh    | RPOR23 <sup>(1)</sup> |

| F5Ch    | PMMODEL <sup>(1)</sup>  | F3Ch    | PADCFG1 | F1Ch    | _    | EFCh    | RPINR22 | EDCh    | RPOR22 <sup>(1)</sup> |

| F5Bh    | PMDOUT2H <sup>(1)</sup> | F3Bh    | _       | F1Bh    | _    | EFBh    | RPINR21 | EDBh    | RPOR21 <sup>(1)</sup> |

| F5Ah    | PMDOUT2L <sup>(1)</sup> | F3Ah    | _       | F1Ah    | _    | EFAh    | _       | EDAh    | RPOR20 <sup>(1)</sup> |

| F59h    | PMDIN2H <sup>(1)</sup>  | F39h    | _       | F19h    | _    | EF9h    | _       | ED9h    | RPOR19 <sup>(1)</sup> |

| F58h    | PMDIN2L <sup>(1)</sup>  | F38h    | _       | F18h    | _    | EF8h    | _       | ED8h    | RPOR18                |

| F57h    | PMEH <sup>(1)</sup>     | F37h    | _       | F17h    | _    | EF7h    | RPINR17 | ED7h    | RPOR17                |

| F56h    | PMEL <sup>(1)</sup>     | F36h    |         | F16h    | —    | EF6h    | RPINR16 | ED6h    | RPOR16                |

| F55h    | PMSTATH <sup>(1)</sup>  | F35h    |         | F15h    | —    | EF5h    | _       | ED5h    | RPOR15                |

| F54h    | PMSTATL <sup>(1)</sup>  | F34h    |         | F14h    | —    | EF4h    | _       | ED4h    | RPOR14                |

| F53h    | CVRCON                  | F33h    |         | F13h    | —    | EF3h    | _       | ED3h    | RPOR13                |

| F52h    | TCLKCON                 | F32h    |         | F12h    | —    | EF2h    | _       | ED2h    | RPOR12                |

| F51h    | -                       | F31h    |         | F11h    | —    | EF1h    | _       | ED1h    | RPOR11                |

| F50h    | -                       | F30h    |         | F10h    | —    | EF0h    | _       | ED0h    | RPOR10                |

| F4Fh    | DSGPR1 <sup>(2)</sup>   | F2Fh    |         | F0Fh    | —    | EEFh    | _       | ECFh    | RPOR9                 |

| F4Eh    | DSGPR0 <sup>(2)</sup>   | F2Eh    | —       | F0Eh    | —    | EEEh    | RPINR8  | ECEh    | RPOR8                 |

| F4Dh    | DSCONH <sup>(2)</sup>   | F2Dh    | —       | F0Dh    | —    | EEDh    | RPINR7  | ECDh    | RPOR7                 |

| F4Ch    | DSCONL <sup>(2)</sup>   | F2Ch    | _       | F0Ch    | —    | EECh    | RPINR6  | ECCh    | RPOR6                 |

| F4Bh    | DSWAKEH <sup>(2)</sup>  | F2Bh    | _       | F0Bh    | —    | EEBh    | —       | ECBh    | RPOR5                 |

| F4Ah    | DSWAKEL <sup>(2)</sup>  | F2Ah    | _       | F0Ah    | —    | EEAh    | RPINR4  | ECAh    | RPOR4                 |

| F49h    | ANCON1                  | F29h    | _       | F09h    | —    | EE9h    | RPINR3  | EC9h    | RPOR3                 |

| F48h    | ANCON0                  | F28h    | _       | F08h    | —    | EE8h    | RPINR2  | EC8h    | RPOR2                 |

| F47h    | —                       | F27h    | _       | F07h    | —    | EE7h    | RPINR1  | EC7h    | RPOR1                 |

| F46h    | —                       | F26h    | _       | F06h    | —    | EE6h    | —       | EC6h    | RPOR0                 |

| F45h    | —                       | F25h    | _       | F05h    | —    | EE5h    | —       | EC5h    | —                     |

| F44h    | —                       | F24h    | _       | F04h    | —    | EE4h    | —       | EC4h    | —                     |

| F43h    | _                       | F23h    | _       | F03h    | _    | EE3h    | _       | EC3h    | _                     |

| F42h    | ODCON1                  | F22h    | —       | F02h    | _    | EE2h    | —       | EC2h    | —                     |

| F41h    | ODCON2                  | F21h    | _       | F01h    | _    | EE1h    | —       | EC1h    | _                     |

| F40h    | ODCON3                  | F20h    | _       | F00h    | _    | EE0h    | _       | EC0h    | —                     |

Note 1: This register is not available on 28-pin devices.

2: Deep Sleep registers are not available on LF devices.

| File Name         Bit 7         Bit 6         Bit 5         Bit 4         Bit 3         Bit 2         Bit 1         Bit 0         Value on<br>POR, BOR           DMACON2         DLYCYC3         DLYCYC2         DLYCYC1         DLYCYC0         INTLVL3         INTLVL2         INTLVL1         INTLVL0         0000         0000           HUVDCON         VDIRMAG         BGVST         IRVST         HLVDLN         HLVDL3         HLVDL2         HLVDL1         HLVDL0         0000         0000           PORTE         RDPU         REPU         —         —         —         RE2         RE1         RE0         00xxxx           PORTD         RD7         RD6         RD5         RD4         RD3         RD2         RD1         RD0         xxxx xxxx           PORTB         RB7         R86         RB5         RE4         RB3         RB2         RB1         RB0         xxxx xxxx           PORTA         RA7         RA6         RA5         —         RA3         RA2         RA1         RA0         xxxx xxxx           SPBRGH1         EUSART1 Baud Rate Generator Register High Byte          0000         0000         0000           BAUDCON2         ABDOVF         RCIDL<                                                                                                                                          | Details<br>on<br>Page:<br>72, 285<br>72<br>72<br>72<br>72<br>72<br>72<br>72<br>72<br>72, 330<br>72<br>72, 330<br>73 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| HLVDCON         VDIRMAG         BGVST         IRVST         HLVDL3         HLVDL3         HLVDL1         HLVDL0         0000         0000           PORTE         RDPU         REPU         —         —         RE2         RE1         RE0         00xxx           PORTD         RD7         RD6         RD5         RD4         RD3         RD2         RD1         RD0         xxxx xxxx           PORTC         RC7         RC6         RC5         RC4         RC4         RC2         RC1         RC0         xxxx xxxx           PORTA         RA7         RA6         RA5         —         RA3         RA2         RA1         RA0         xxx- xxxx           PORTA         RA7         RA6         RA5         —         RA3         RA2         RA1         RA0         xxx- xxxx           SPBRGH1         EUSART1 Bauf Rate Generator Register High Byte         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000                                                                                                                                                  | 72<br>72<br>72<br>72<br>72<br>72<br>72<br>72<br>72, 330<br>72<br>72, 330                                            |

| PORTE         RDPU         REPU         —         —         RE2         RE1         RE0         00xxx           PORTD         RD7         RD6         RD5         RD4         RD3         RD2         RD1         RD0         xxxx         xxxx           PORTC         RC7         RC6         RC5         RC4         RC4         RC2         RC1         RC0         xxxx         xxxx           PORTB         RB7         RB6         RB5         RB4         RB3         RB2         RB1         RB0         xxxx         xxxx           PORTA         RA7         RA6         RA5         —         RA3         RA2         RA1         RA0         xxx-         xxxx           SPBRGH1         EUSART1 Baud Rate Generator Register High Byte         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         00                                                                                                                                                 | 72<br>72<br>72<br>72<br>72<br>72<br>72, 330<br>72<br>72, 330                                                        |

| PORTD         RD7         RD6         RD5         RD4         RD3         RD2         RD1         RD0         xxxx xxxx           PORTC         RC7         RC6         RC5         RC4         RC4         RC2         RC1         RC0         xxxx xxxx           PORTB         RB7         RB6         RB5         RB4         RB3         RB2         RB1         RB0         xxxx xxxx           PORTA         RA7         RA6         RA5         —         RA3         RA2         RA1         RA0         xxx- xxxx           SPBRGH1         EUSART1 Baud Rate Generator Register High Byte         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         <                                                                                                                         | 72<br>72<br>72<br>72<br>72<br>72, 330<br>72<br>72, 330                                                              |

| PORTC         RC7         RC6         RC5         RC4         RC4         RC2         RC1         RC0         xxxx xxxx           PORTB         RB7         RB6         RB5         RB4         RB3         RB2         RB1         RB0         xxxx xxxx           PORTA         RA7         RA6         RA5         —         RA3         RA2         RA1         RA0         xxxx xxxx           SPBRGH1         EUSART1 Baud Rate Generator Register High Byte         0000         0000         0000         0000         0000           BAUDCON1         ABDOVF         RCIDL         RXDTP         TXCKP         BRG16         —         WUE         ABDEN         0100         0-00           SPBRGH2         EUSART2 Baud Rate Generator Register High Byte          0000         0000         0000           BAUDCON2         ABDOVF         RCIDL         RXDTP         TXCKP         BRG16         —         WUE         ABDEN         0100         0-00           TMR3H         Timer3 Register High Byte         xxxx xxxx         xxxx xxxx         xxxx xxxx         Xxxx xxxx           TMR3L         Timer4 Register         V         WUE         ABDEN         0100         0000         0000                                                                                                                               | 72<br>72<br>72<br>72, 330<br>72<br>72, 330                                                                          |

| PORTB         RB7         RB6         RB5         RB4         RB3         RB2         RB1         RB0         xxxx xxxx           PORTA         RA7         RA6         RA5         —         RA3         RA2         RA1         RA0         xxx- xxxx           SPBRGH1         EUSART1 Baud Rate Generator Register High Byte         0000         0000         0000         0000           BAUDCON1         ABDOVF         RCIDL         RXDTP         TXCKP         BRG16         —         WUE         ABDEN         0100         0-00           SPBRGH2         EUSART2 Baud Rate Generator Register High Byte         0000         0000         0000         0000           BAUDCON2         ABDOVF         RCIDL         RXDTP         TXCKP         BRG16         —         WUE         ABDEN         0100         0-00           TMR3H         Timer3 Register High Byte         xxxx xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx           TMR3L         Timer3 Register Low Byte         xxxx xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx           TMR4         Timer4 Register         0000         0000                                                                                                                 | 72<br>72<br>72, 330<br>72<br>72, 330                                                                                |

| PORTA         RA7         RA6         RA5         —         RA3         RA2         RA1         RA0         xxx-xxxx           SPBRGH1         EUSART1 Baud Rate Generator Register High Byte         0000 0000         0000         0000         0000           BAUDCON1         ABDOVF         RCIDL         RXDTP         TXCKP         BRG16         —         WUE         ABDEN         0100 0-00           SPBRGH2         EUSART2 Baud Rate Generator Register High Byte         0000 0000         0000         0000         0000         0000           BAUDCON2         ABDOVF         RCIDL         RXDTP         TXCKP         BRG16         —         WUE         ABDEN         0100 0-00           TMR3H         Timer3 Register High Byte         xxxx xxxx         xxxx xxxx         xxxx xxxx         Xxxx xxxx           T3CON         TMR3CS1         TMR3CS0         T3CKPS1         T3CKPS0         —         T3SYNC         RD16         TMR3ON         0000 -000           TMR4         Timer4 Register         0100 0-00         TMR4         Timer4 Register         1111 1111         1111 1111           T4CON         —         T40UTPS3         T40UTPS2         T40UTPS0         TMR4ON         T4CKPS0         -0000 0000 <t< td=""><td>72<br/>72, 330<br/>72, 330<br/>72<br/>72, 330</td></t<>                   | 72<br>72, 330<br>72, 330<br>72<br>72, 330                                                                           |

| SPBRGH1         EUSART1 Baud Rate Generator Register High Byte         0000         0000           BAUDCON1         ABDOVF         RCIDL         RXDTP         TXCKP         BRG16         —         WUE         ABDEN         0100         0-00           SPBRGH2         EUSART2 Baud Rate Generator Register High Byte          0000         0000         0000           BAUDCON2         ABDOVF         RCIDL         RXDTP         TXCKP         BRG16         —         WUE         ABDEN         0100         0-00           TMR3H         Timer3 Register High Byte         xxxx xxxx         XXXX         XXXX         XXXX         XXXX           TMR3L         Timer3 Register Low Byte         xxxx XXXX         XXXX         XXXX         XXXX           TMR4         Timer4 Register         0000         0000         0000         0000           PR4         Timer4 Period Register         T40UTPS2         T40UTPS1         T40UTPS0         TMR4ON         T4CKPS1         74CKPS0         -0000         0000           SSP2BUF         MSSP2 Address Register (I <sup>2</sup> C™ Slave mode), MSSP2 Baud Rate Reload Register (I <sup>2</sup> C Master mode)         0000         0000         0000           SSP2MSK <sup>(4)</sup> MSK7         MSK6         MSK5         MSK4 <td>72<br/>72, 330<br/>72<br/>72, 330</td> | 72<br>72, 330<br>72<br>72, 330                                                                                      |

| BAUDCON1         ABDOVF         RCIDL         RXDTP         TXCKP         BRG16         —         WUE         ABDEN         0100         0-00           SPBRGH2         EUSART2 Baud Rate Generator Register High Byte         0000         0000         0000         0000           BAUDCON2         ABDOVF         RCIDL         RXDTP         TXCKP         BRG16         —         WUE         ABDEN         0100         0-00           TMR3H         Timer3 Register High Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 72, 330<br>72<br>72, 330                                                                                            |

| SPBRGH2         EUSART2 Baud Rate Generator Register High Byte         0000 0000           BAUDCON2         ABDOVF         RCIDL         RXDTP         TXCKP         BRG16         —         WUE         ABDEN         0100 0-00           TMR3H         Timer3 Register High Byte         xxxx xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx                                                                                 | 72<br>72, 330                                                                                                       |

| BAUDCON2         ABDOVF         RCIDL         RXDTP         TXCKP         BRG16         —         WUE         ABDEN         0100         0-00           TMR3H         Timer3 Register High Byte         xxxx                                                                                                        | 72, 330                                                                                                             |

| TMR3H       Timer3 Register High Byte       xxxx xxxx         TMR3L       Timer3 Register Low Byte       xxxx xxxx         T3CON       TMR3CS1       TMR3CS0       T3CKPS1       T3CKPS0       —       T3SYNC       RD16       TMR3ON       0000       -000         TMR4       Timer4 Register       0000       0000       -       0000       0000       -       0000       0000       -       0000       0000       -       0000       0000       -       0000       0000       -       0000       0000       -       0000       0000       -       0000       0000       -       0000       0000       -       0000       0000       -       0000       0000       -       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000                                                                                                                                                                                                       |                                                                                                                     |

| TMR3L         Timer3 Register Low Byte         xxxx xxxx           T3CON         TMR3CS1         TMR3CS0         T3CKPS1         T3CKPS0         —         T3SYNC         RD16         TMR3ON         0000         -000           TMR4         Timer4 Register         0000         0000         0000         0000         0000         0000           PR4         Timer4 Register         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111                                                                                                           | 73                                                                                                                  |

| T3CON         TMR3CS1         TMR3CS0         T3CKPS1         T3CKPS0         —         T3SYNC         RD16         TMR3ON         0000         -000           TMR4         Timer4 Register         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000 <t< td=""><td></td></t<>                                                                                   |                                                                                                                     |

| TMR4         Timer4 Register         0000         0000           PR4         Timer4 Period Register         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111                                                                                                         | 73                                                                                                                  |

| PR4         Timer4 Period Register         1111 1111           T4CON         —         T40UTPS3         T40UTPS2         T40UTPS1         T40UTPS0         TMR4ON         T4CKPS1         T4CKPS0         -000         0000           SSP2BUF         MSSP2 Receive Buffer/Transmit Register         xxxx xxxx         xxxx xxxx         xxxx xxxx           SSP2ADD/<br>SSP2MSK <sup>(4)</sup> MSK7         MSK6         MSK5         MSK4         MSK3         MSK2         MSK1         MSK0         1111         1111           SSP2STAT         SMP         CKE         D/Ā         P         S         R/W         UA         BF         0000         0000           SSP2CON1         WCOL         SSPOV         SSPEN         CKP         SSPM3         SSPM2         SSPM1         SSPM0         0000         0000           SSP2CON2         GCEN         ACKSTAT         ACKDT         ACKEN         RCEN         PEN         RSEN         SEN         0000         0000           CMSTAT         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         …         …         …                                                                                                                                               | 73, 215                                                                                                             |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 73                                                                                                                  |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 73                                                                                                                  |

| SSP2ADD/<br>SSP2MSK <sup>(4)</sup> MSSP2 Address Register (l <sup>2</sup> C ™ Slave mode), MSSP2 Baud Rate Reload Register (l <sup>2</sup> C Master mode)         0000         0000           SSP2MSK <sup>(4)</sup> MSK7         MSK6         MSK5         MSK4         MSK3         MSK2         MSK1         MSK0         1111         1111           SSP2MSK <sup>(4)</sup> SMP         CKE         D/Ā         P         S         R/₩         UA         BF         0000         0000           SSP2CON1         WCOL         SSPOV         SSPEN         CKP         SSPM3         SSPM2         SSPM1         SSPM0         0000         0000           SSP2CON2         GCEN         ACKSTAT         ACKDT         ACKEN         RCEN         PEN         RSEN         SEN           CMSTAT         —         —         —         —         —         COUT2         COUT1                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 73, 225                                                                                                             |

| SSP2MSK <sup>(4)</sup> MSK7         MSK6         MSK5         MSK4         MSK3         MSK2         MSK1         MSK0         1111         1111           SSP2STAT         SMP         CKE         D/Ā         P         S         R/W         UA         BF         0000         0000           SSP2CON1         WCOL         SSPOV         SSPEN         CKP         SSPM3         SSPM2         SSPM1         SSPM0         0000         0000           SSP2CON2         GCEN         ACKSTAT         ACKDT         ACKEN         RCEN         PEN         RSEN         SEN         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000                                                                                                                              | 73                                                                                                                  |

| Imisko         Imisko<                             | 73, 295                                                                                                             |

| SSP2CON1         WCOL         SSPOV         SSPEN         CKP         SSPM3         SSPM2         SSPM1         SSPM0         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000                                                                                                    | 73, 295                                                                                                             |

| SSP2CON2         GCEN         ACKSTAT         ACKDT         ACKEN         RCEN         PEN         RSEN         SEN         0000         0000           GCEN         ACKSTAT         ADMSK5 <sup>(4)</sup> ADMSK4 <sup>(4)</sup> ADMSK3 <sup>(4)</sup> ADMSK2 <sup>(4)</sup> ADMSK1 <sup>(4)</sup> SEN         0000         0000         0000           CMSTAT         -         -         -         -         -         COUT2         COUT1        11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 73, 273                                                                                                             |

| GCEN         ACKSTAT         ADMSK5 <sup>(4)</sup> ADMSK4 <sup>(4)</sup> ADMSK3 <sup>(4)</sup> ADMSK2 <sup>(4)</sup> ADMSK1 <sup>(4)</sup> SEN           CMSTAT         -         -         -         -         -         COUT2         COUT1        11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 73, 293                                                                                                             |

| CMSTAT         -         -         -         -         COUT2         COUT1        11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 73, 294                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                     |

| PMADDRH/ — CS1 Parallel Master Port Address High Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 73, 363                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 73, 179                                                                                                             |

| PMDOUT1H <sup>(5)</sup> Parallel Port Out Data High Byte (Buffer 1) 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 73, 179                                                                                                             |

| PMADDRL/         Parallel Master Port Address Low Byte         0000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 73, 179                                                                                                             |

| PMDOUT1L <sup>(5)</sup> Parallel Port Out Data Low Byte (Buffer 0) 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 73, 179                                                                                                             |

| PMDIN1H <sup>(5)</sup> Parallel Port In Data High Byte (Buffer 1) 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 73                                                                                                                  |

| PMDIN1L <sup>(5)</sup> Parallel Port In Data Low Byte (Buffer 0) 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 73                                                                                                                  |

| TXADDRL         SPI DMA Transit Data Pointer Low Byte         0000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 73                                                                                                                  |

| TXADDRH — — — SPI DMA Transit Data Pointer High Byte 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 73                                                                                                                  |

| RXADDRL         SPI DMA Receive Data Pointer Low Byte         0000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                     |

| RXADDRH — — — SPI DMA Receive Data Pointer High Byte 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 73                                                                                                                  |

| DMABCL SPI DMA Byte Count Low Byte 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                     |

| DMABCH     —     —     —     —     SPI DMA Receive Data    00       Pointer High Byte     Pointer High Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 73                                                                                                                  |

| PMCONH <sup>(5)</sup> PMPEN — — ADRMUX1 ADRMUX0 PTBEEN PTWREN PTRDEN 00 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 73<br>73                                                                                                            |

| PMCONL <sup>(5)</sup> CSF1 CSF0 ALP — CS1P BEP WRSP RDSP 000-0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 73<br>73<br>73                                                                                                      |