Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 48MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 34                                                                          |

| Program Memory Size        | 16KB (8K x 16)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | <u> </u>                                                                    |

| RAM Size                   | 3.8K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.15V ~ 3.6V                                                                |

| Data Converters            | A/D 13x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

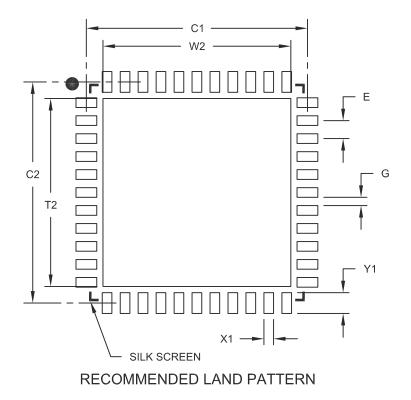

| Package / Case             | 44-TQFP                                                                     |

| Supplier Device Package    | 44-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f44j11t-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

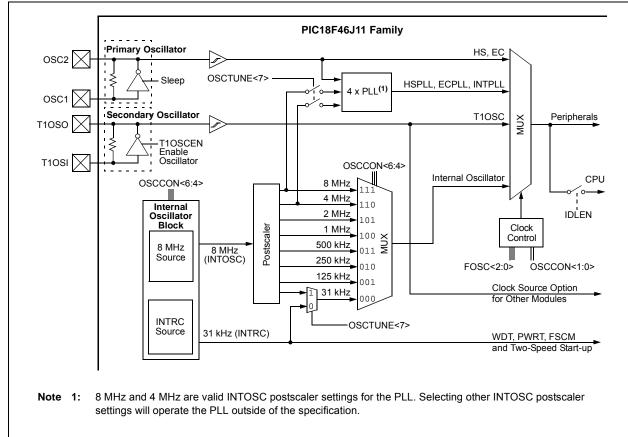

## 3.2.1 OSCILLATOR MODES

Figure 3-1 helps in understanding the oscillator structure of the PIC18F46J11 family of devices.

### FIGURE 3-1: PIC18F46J11 FAMILY CLOCK DIAGRAM

## 7.4 Erasing Flash Program Memory

The minimum erase block is 512 words or 1024 bytes. Only through the use of an external programmer, or through ICSP control, can larger blocks of program memory be bulk erased. Word erase in the Flash array is not supported.

When initiating an erase sequence from the microcontroller itself, a block of 1024 bytes of program memory is erased. The Most Significant 12 bits of the TBLPTR<21:10> point to the block being erased. TBLPTR<9:0> are ignored.

The EECON1 register commands the erase operation. The WREN bit must be set to enable write operations. The FREE bit is set to select an erase operation. For protection, the write initiate sequence for EECON2 must be used.

A long write is necessary for erasing the internal Flash. Instruction execution is halted while in a long write cycle. The long write will be terminated by the internal programming timer.

### 7.4.1 FLASH PROGRAM MEMORY ERASE SEQUENCE

The sequence of events for erasing a block of internal program memory location is:

- 1. Load Table Pointer register with address of row being erased.

- 2. Set the WREN and FREE bits (EECON1<2,4>) to enable the erase operation.

- 3. Disable interrupts.

- 4. Write 55h to EECON2.

- 5. Write 0AAh to EECON2.

- 6. Set the WR bit; this will begin the erase cycle.

- The CPU will stall for the duration of the erase for TIE (see parameter D133B).

- 8. Re-enable interrupts.

### EXAMPLE 7-2: ERASING FLASH PROGRAM MEMORY

|           | MOVLW<br>MOVWF<br>MOVLW<br>MOVWF<br>MOVLW | CODE_ADDR_UPPER<br>TBLPTRU<br>CODE_ADDR_HIGH<br>TBLPTRH<br>CODE ADDR LOW | ; load TBLPTR with the base<br>; address of the memory block |

|-----------|-------------------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------|

|           | MOVWF                                     | TBLPTRL                                                                  |                                                              |

| ERASE_ROW |                                           |                                                                          |                                                              |

|           | BSF                                       | EECON1, WREN                                                             | ; enable write to memory                                     |

|           | BSF                                       | EECON1, FREE                                                             | ; enable Erase operation                                     |

|           | BCF                                       | INTCON, GIE                                                              | ; disable interrupts                                         |

| Required  | MOVLW                                     | 0x55                                                                     |                                                              |

| Sequence  | MOVWF                                     | EECON2                                                                   | ; write 55h                                                  |

|           | MOVLW                                     | 0xAA                                                                     |                                                              |

|           | MOVWF                                     | EECON2                                                                   | ; write OAAh                                                 |

|           | BSF                                       | EECON1, WR                                                               | ; start erase (CPU stall)                                    |

|           | BSF                                       | INTCON, GIE                                                              | ; re-enable interrupts                                       |

# PIC18F46J11 FAMILY

## 9.0 INTERRUPTS

Devices of the PIC18F46J11 family have multiple interrupt sources and an interrupt priority feature that allows most interrupt sources to be assigned a high-priority level or a low-priority level. The high-priority interrupt vector is at 0008h and the low-priority interrupt vector is at 0018h. High-priority interrupt events will interrupt any low-priority interrupts that may be in progress.

There are 13 registers, which are used to control interrupt operation. These registers are:

- RCON

- INTCON

- INTCON2

- INTCON3

- PIR1, PIR2, PIR3

- PIE1, PIE2, PIE3

- IPR1, IPR2, IPR3

It is recommended that the Microchip header files supplied with MPLAB<sup>®</sup> IDE be used for the symbolic bit names in these registers. This allows the assembler/compiler to automatically take care of the placement of these bits within the specified register.

In general, interrupt sources have three bits to control their operation. They are:

- Flag bit to indicate that an interrupt event occurred

- Enable bit that allows program execution to branch to the interrupt vector address when the flag bit is set

- **Priority bit** to select high priority or low priority

The interrupt priority feature is enabled by setting the IPEN bit (RCON<7>). When interrupt priority is enabled, there are two bits which enable interrupts globally. Setting the GIEH bit (INTCON<7>) enables all interrupts that have the priority bit set (high priority). Setting the GIEH and GIEL bits (INTCON<76>) enables interrupts that have the priority bit cleared (low priority). When the interrupt flag, enable bit and appropriate Global Interrupt Enable (GIE) bit are set, the interrupt will vector immediately to address 0008h or 0018h, depending on the priority bit setting. Individual interrupts can be disabled through their corresponding enable bits.

When the IPEN bit is cleared (default state), the interrupt priority feature is disabled and interrupts are compatible with PIC<sup>®</sup> mid-range devices. In Compatibility mode, the interrupt priority bits for each source have no effect. INTCON<6> is the PEIE bit, which enables/disables all peripheral interrupt sources. INTCON<7> is the GIE bit, which enables/disables all interrupt sources. All interrupts branch to address 0008h in Compatibility mode.

When an interrupt is responded to, the Global Interrupt Enable bit is cleared to disable further interrupts. If the IPEN bit is cleared, this is the GIE bit. If interrupt priority levels are used, this will be either the GIEH or GIEL bit. High-priority interrupt sources can interrupt a low-priority interrupt. Low-priority interrupts are not processed while high-priority interrupts are in progress.

The return address is pushed onto the stack and the PC is loaded with the interrupt vector address (0008h or 0018h). Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bits must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine and sets the GIE bit (GIEH or GIEL if priority levels are used), which re-enables interrupts.

For external interrupt events, such as the INTx pins or the PORTB input change interrupt, the interrupt latency will be three to four instruction cycles. The exact latency is the same for one or two-cycle instructions. Individual interrupt flag bits are set regardless of the status of their corresponding enable bit or the GIE bit.

Note: Do not use the MOVFF instruction to modify any of the interrupt control registers while **any** interrupt is enabled. Doing so may cause erratic microcontroller behavior.

## 9.3 PIE Registers

The PIE registers contain the individual enable bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are three Peripheral Interrupt Enable registers (PIE1, PIE2, PIE3). When IPEN = 0, the PEIE bit must be set to enable any of these peripheral interrupts.

#### REGISTER 9-7: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1 (ACCESS F9Dh)

| R/W-0                | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|----------------------|-------|-------|-------|--------|--------|--------|--------|

| PMPIE <sup>(1)</sup> | ADIE  | RC1IE | TX1IE | SSP1IE | CCP1IE | TMR2IE | TMR1IE |

| bit 7                |       |       |       |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7   | PMPIE: Parallel Master Port Read/Write Interrupt Enable bit <sup>(1)</sup> |

|---------|----------------------------------------------------------------------------|

|         | 1 = Enables the PMP read/write interrupt                                   |

|         | 0 = Disables the PMP read/write interrupt                                  |

| bit 6   | ADIE: A/D Converter Interrupt Enable bit                                   |

|         | 1 = Enables the A/D interrupt                                              |

|         | 0 = Disables the A/D interrupt                                             |

| bit 5   | RC1IE: EUSART1 Receive Interrupt Enable bit                                |

|         | 1 = Enables the EUSART1 receive interrupt                                  |

|         | 0 = Disables the EUSART1 receive interrupt                                 |

| bit 4   | TX1IE: EUSART1 Transmit Interrupt Enable bit                               |

|         | 1 = Enables the EUSART1 transmit interrupt                                 |

|         | 0 = Disables the EUSART1 transmit interrupt                                |

| bit 3   | SSP1IE: Master Synchronous Serial Port 1 Interrupt Enable bit              |

|         | 1 = Enables the MSSP1 interrupt                                            |

|         | 0 = Disables the MSSP1 interrupt                                           |

| bit 2   | CCP1IE: ECCP1 Interrupt Enable bit                                         |

|         | 1 = Enables the ECCP1 interrupt                                            |

|         | 0 = Disables the ECCP1 interrupt                                           |

| bit 1   | TMR2IE: TMR2 to PR2 Match Interrupt Enable bit                             |

|         | 1 = Enables the TMR2 to PR2 match interrupt                                |

|         | 0 = Disables the TMR2 to PR2 match interrupt                               |

| bit 0   | TMR1IE: TMR1 Overflow Interrupt Enable bit                                 |

|         | 1 = Enables the TMR1 overflow interrupt                                    |

|         | 0 = Disables the TMR1 overflow interrupt                                   |

| Note 1: | These bits are unimplemented on 28-pin devices.                            |

|         |                                                                            |

### 10.7.3.2 Output Mapping

In contrast to inputs, the outputs of the PPS options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPORx registers are used to control output mapping. The value of the bit field corresponds to one of the peripherals and that peripheral's output is mapped to the pin (see Table 10-14).

Because of the mapping technique, the list of peripherals for output mapping also includes a null value of '00000'. This permits any given pin to remain disconnected from the output of any of the pin selectable peripherals.

| Function | Output Function<br>Number <sup>(1)</sup> | Output Name                                             |

|----------|------------------------------------------|---------------------------------------------------------|

| NULL     | 0                                        | NULL <sup>(2)</sup>                                     |

| C10UT    | 1                                        | Comparator 1 Output                                     |

| C2OUT    | 2                                        | Comparator 2 Output                                     |

| TX2/CK2  | 5                                        | EUSART2 Asynchronous Transmit/Asynchronous Clock Output |

| DT2      | 6                                        | EUSART2 Synchronous Transmit                            |

| SDO2     | 9                                        | SPI2 Data Output                                        |

| SCK2     | 10                                       | SPI2 Clock Output                                       |

| SSDMA    | 12                                       | SPI DMA Slave Select                                    |

| ULPOUT   | 13                                       | Ultra Low-Power Wake-up Event                           |

| CCP1/P1A | 14                                       | ECCP1 Compare or PWM Output Channel A                   |

| P1B      | 15                                       | ECCP1 Enhanced PWM Output, Channel B                    |

| P1C      | 16                                       | ECCP1 Enhanced PWM Output, Channel C                    |

| P1D      | 17                                       | ECCP1 Enhanced PWM Output, Channel D                    |

| CCP2/P2A | 18                                       | ECCP2 Compare or PWM Output                             |

| P2B      | 19                                       | ECCP2 Enhanced PWM Output, Channel B                    |

| P2C      | 20                                       | ECCP2 Enhanced PWM Output, Channel C                    |

| P2D      | 21                                       | ECCP2 Enhanced PWM Output, Channel D                    |

## TABLE 10-14: SELECTABLE OUTPUT SOURCES (MAPS FUNCTION TO OUTPUT)

**Note 1:** Value assigned to the RPn<4:0> pins corresponds to the peripheral output function number.

2: The NULL function is assigned to all RPn outputs at device Reset and disables the RPn output function.

NOTES:

## 13.2 Timer1 Operation

The Timer1 module is an 8-bit or 16-bit incrementing counter, which is accessed through the TMR1H:TMR1L register pair.

When used with an internal clock source, the module is a timer and increments on every instruction cycle. When used with an external clock source, the module can be used as either a timer or counter and increments on every selected edge of the external source.

Timer1 is enabled by configuring the TMR1ON and TMR1GE bits in the T1CON and T1GCON registers, respectively.

When Timer1 is enabled, the RC1/T1OSI/RP12 and RC0/T1OSO/T1CKI/RP11 pins become inputs. This means the values of TRISC<1:0> are ignored and the pins are read as '0'.

## 13.3 Clock Source Selection

The TMR1CS<1:0> and T1OSCEN bits of the T1CON register are used to select the clock source for Timer1. Register 13-1 displays the clock source selections.

When switching clock sources and using the clock prescaler, write to TMR1L afterwards to reset the internal prescaler count to 0.

### 13.3.1 INTERNAL CLOCK SOURCE

When the internal clock source is selected, the TMR1H:TMR1L register pair will increment on multiples of Fosc as determined by the Timer1 prescaler.

### 13.3.2 EXTERNAL CLOCK SOURCE

When the external clock source is selected, the Timer1 module may work as a timer or a counter.

When enabled to count, Timer1 is incremented on the rising edge of the external clock input, T1CKI, or the capacitive sensing oscillator signal. Either of these external clock sources can be synchronized to the microcontroller system clock or they can run asynchronously.

When used as a timer with a clock oscillator, an external 32.768 kHz crystal can be used in conjunction with the dedicated internal oscillator circuit.

| Note: | In Counter mode, a falling edge must be<br>registered by the counter prior to the first<br>incrementing rising edge after any one or<br>more of the following conditions: |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>Timer1 enabled after POR Reset</li> <li>Write to TMR1H or TMR1L</li> <li>Timer1 is disabled</li> <li>Timer1 is disabled (TMR1ON = 0)</li> </ul>                  |

|       | when T1CKI is high, then Timer1 is<br>enabled (TMR1ON = 1) when T1CKI is<br>low.                                                                                          |

| TMR1CS1 | TMR1CS0 | T1OSCEN Clock Source          |                                       |

|---------|---------|-------------------------------|---------------------------------------|

| 0       | 1       | x                             | Clock Source (Fosc)                   |

| 0       | 0       | x                             | Instruction Clock (Fosc/4)            |

| 1       | 0       | 0 External Clock on T1CKI Pin |                                       |

| 1       | 0       | 1                             | Oscillator Circuit on T1OSI/T1OSO Pin |

TABLE 13-1: TIMER1 CLOCK SOURCE SELECTION

## TABLE 17-3:RTCVALH AND RTCVALLREGISTER MAPPING

| RTCPTR<1:0> | RTCC Value Register Window |              |  |

|-------------|----------------------------|--------------|--|

|             | RTCVALH<15:8>              | RTCVALL<7:0> |  |

| 00          | MINUTES                    | SECONDS      |  |

| 01          | WEEKDAY                    | HOURS        |  |

| 10          | MONTH                      | DAY          |  |

| 11          | _                          | YEAR         |  |

The Alarm Value register window (ALRMVALH and ALRMVALL) uses the ALRMPTR bits (ALRMCFG<1:0>) to select the desired Alarm register pair.

By reading or writing to the ALRMVALH register, the Alarm Pointer value, ALRMPTR<1:0>, decrements by 1 until it reaches '00'. Once it reaches '00', the ALRMMIN and ALRMSEC value will be accessible through ALRMVALH and ALRMVALL until the pointer value is manually changed.

| TABLE 17-4: | ALRMVAL REGISTER |

|-------------|------------------|

|             | MAPPING          |

| ALRMPTR<1:0> | Alarm Value Register Window |               |  |

|--------------|-----------------------------|---------------|--|

|              | ALRMVALH<15:8>              | ALRMVALL<7:0> |  |

| 0.0          | ALRMMIN                     | ALRMSEC       |  |

| 01           | ALRMWD                      | ALRMHR        |  |

| 10           | ALRMMNTH                    | ALRMDAY       |  |

| 11           | _                           |               |  |

### 17.2.9 CALIBRATION

The real-time crystal input can be calibrated using the periodic auto-adjust feature. When properly calibrated, the RTCC can provide an error of less than three seconds per month.

To perform this calibration, find the number of error clock pulses and store the value in the lower half of the RTCCAL register. The 8-bit, signed value – loaded into RTCCAL – is multiplied by '4' and will either be added or subtracted from the RTCC timer, once every minute.

To calibrate the RTCC module:

- 1. Use another timer resource on the device to find the error of the 32.768 kHz crystal.

- 2. Convert the number of error clock pulses per minute (see Equation 17-1).

### EQUATION 17-1: CONVERTING ERROR CLOCK PULSES

(Ideal Frequency (32,768) – Measured Frequency) \* 60 = Error Clocks per Minute

- If the oscillator is *faster* than ideal (negative result from step 2), the RTCCALL register value needs to be negative. This causes the specified number of clock pulses to be subtracted from the timer counter once every minute.

- If the oscillator is *slower* than ideal (positive result from step 2), the RTCCALL register value needs to be positive. This causes the specified number of clock pulses to be added to the timer counter once every minute.

- 3. Load the RTCCAL register with the correct value.

Writes to the RTCCAL register should occur only when the timer is turned off, or immediately after the rising edge of the seconds pulse.

| Note: | In determining the crystal's error value, it |

|-------|----------------------------------------------|

|       | is the user's responsibility to include the  |

|       | crystal's initial error from drift due to    |

|       | temperature or crystal aging.                |

### 17.6 Register Maps

Table 17-5, Table 17-6 and Table 17-7 summarize the registers associated with the RTCC module.

| File Name | Bit 7  | Bit 6  | Bit 5   | Bit 4   | Bit 3   | Bit 2     | Bit 1     | Bit 0    | All<br>Resets |

|-----------|--------|--------|---------|---------|---------|-----------|-----------|----------|---------------|

| RTCCFG    | RTCEN  | _      | RTCWREN | RTCSYNC | HALFSEC | RTCOE     | RTCPTR1   | RTCPTR0  | 0000          |

| RTCCAL    | CAL7   | CAL6   | CAL5    | CAL4    | CAL3    | CAL2      | CAL1      | CAL0     | 0000          |

| PADCFG1   | _      |        | _       | —       | _       | RTSECSEL1 | RTSECSEL0 | PMPTTL   | 0000          |

| ALRMCFG   | ALRMEN | CHIME  | AMASK3  | AMASK2  | AMASK1  | AMASK0    | ALRMPTR1  | ALRMPTR0 | 0000          |

| ALRMRPT   | ARPT7  | ARPT6  | ARPT5   | ARPT4   | ARPT3   | ARPT2     | ARPT1     | ARPT0    | 0000          |

| IPR3      | SSP2IP | BCL2IP | RC2IP   | TX2IP   | TMR4IP  | CTMUIP    | TMR3GIP   | RTCCIP   | 1111          |

| PIR3      | SSP2IF | BCL2IF | RC2IF   | TX2IF   | TMR4IF  | CTMUIF    | TMR3GIF   | RTCCIF   | 0000          |

| PIE3      | SSP2IE | BCL2IE | RC2IE   | TX2IE   | TMR4IE  | CTMUIE    | TMR3GIE   | RTCCIE   | 0000          |

### TABLE 17-5: RTCC CONTROL REGISTERS

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal for 44-pin devices.

### TABLE 17-6: RTCC VALUE REGISTERS

| File Name | Bit 7                                                             | Bit 6       | Bit 5       | Bit 4        | Bit 3    | Bit 2  | Bit 1    | Bit 0    | All Resets |

|-----------|-------------------------------------------------------------------|-------------|-------------|--------------|----------|--------|----------|----------|------------|

| RTCVALH   | TCVALH RTCC Value Register Window High Byte, Based on RTCPTR<1:0> |             |             |              |          |        |          | xxxx     |            |

| RTCVALL   | RTCC Value Register Window Low Byte, Based on RTCPTR<1:0>         |             |             |              |          |        |          |          | xxxx       |

| RTCCFG    | RTCEN                                                             | _           | RTCWREN     | RTCSYNC      | HALFSEC  | RTCOE  | RTCPTR1  | RTCPTR0  | 0000       |

| ALRMCFG   | ALRMEN                                                            | CHIME       | AMASK3      | AMASK2       | AMASK1   | AMASK0 | ALRMPTR1 | ALRMPTR0 | 0000       |

| ALRMVALH  | H Alarm Value Register Window High Byte, Based on ALRMPTR<1:0>    |             |             |              |          |        |          | xxxx     |            |

| ALRMVALL  | Alarm Value                                                       | Register Wi | ndow Low By | te, Based on | ALRMPTR< | <1:0>  |          |          | xxxx       |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal for 44-pin devices.

### TABLE 17-7: ALARM VALUE REGISTERS

| File Name | Bit 7                                                            | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|---------------|

| ALRMRPT   | ARPT7                                                            | ARPT6 | ARPT5 | ARPT4 | ARPT3 | ARPT2 | ARPT1 | ARPT0 | 0000          |

| ALRMVALH  | ALH Alarm Value Register Window High Byte, Based on ALRMPTR<1:0> |       |       |       |       |       |       |       | xxxx          |

| ALRMVALL  | Alarm Value Register Window Low Byte, Based on ALRMPTR<1:0>      |       |       |       |       |       |       | xxxx  |               |

| RTCCAL    | CAL7                                                             | CAL6  | CAL5  | CAL4  | CAL3  | CAL2  | CAL1  | CAL0  | 0000          |

| RTCVALH   | ALH RTCC Value Register Window High Byte, Based on RTCPTR<1:0>   |       |       |       |       |       |       | xxxx  |               |

| RTCVALL   | ALL RTCC Value Register Window Low Byte, Based on RTCPTR<1:0>    |       |       |       |       |       |       | xxxx  |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal for 44-pin devices.

NOTES:

| Name                  | Bit 7                | Bit 6        | Bit 5       | Bit 4   | Bit 3  | Bit 2  | Bit 1   | Bit 0  | Reset<br>Values<br>on Page: |

|-----------------------|----------------------|--------------|-------------|---------|--------|--------|---------|--------|-----------------------------|

| INTCON                | GIE/GIEH             | PEIE/GIEL    | TMR0IE      | INT0IE  | RBIE   | TMR0IF | INT0IF  | RBIF   | 69                          |

| PIR1                  | PMPIF <sup>(2)</sup> | ADIF         | RC1IF       | TX1IF   | SSP1IF | CCP1IF | TMR2IF  | TMR1IF | 72                          |

| PIE1                  | PMPIE <sup>(2)</sup> | ADIE         | RC1IE       | TX1IE   | SSP1IE | CCP1IE | TMR2IE  | TMR1IE | 72                          |

| IPR1                  | PMPIP <sup>(2)</sup> | ADIP         | RC1IP       | TX1IP   | SSP1IP | CCP1IP | TMR2IP  | TMR1IP | 72                          |

| PIR3                  | SSP2IF               | BCL2IF       | RC2IF       | TX2IF   | TMR4IF | CTMUIF | TMR3GIF | RTCCIF | 72                          |

| PIE3                  | SSP2IE               | BCL2IE       | RC2IE       | TX2IE   | TMR4IE | CTMUIE | TMR3GIE | RTCCIE | 72                          |

| IPR3                  | SSP2IP               | BCL2IP       | RC2IP       | TX2IP   | TMR4IP | CTMUIP | TMR3GIP | RTCCIP | 72                          |

| TRISB                 | TRISB7               | TRISB6       | TRISB5      | TRISB4  | TRISB3 | TRISB2 | TRISB1  | TRISB0 | 72                          |

| TRISC                 | TRISC7               | TRISC6       | TRISC5      | TRISC4  | TRISC3 | TRISC2 | TRISC1  | TRISC0 | 72                          |

| SSP1BUF               | MSSP1 Re             | ceive Buffer | /Transmit R | egister |        |        |         |        | 70                          |

| SSPxCON1              | WCOL                 | SSPOV        | SSPEN       | CKP     | SSPM3  | SSPM2  | SSPM1   | SSPM0  | 70                          |

| SSPxSTAT              | SMP                  | CKE          | D/Ā         | Р       | S      | R/W    | UA      | BF     | 70                          |

| SSP2BUF               | MSSP2 Re             | ceive Buffer | /Transmit R | egister | •      | •      | •       |        | 73                          |

| ODCON3 <sup>(1)</sup> | —                    | —            |             | —       | —      | —      | SPI2OD  | SPI10D | 74                          |

Legend: Shaded cells are not used by the MSSP module in SPI mode.

**Note 1:** Configuration SFR overlaps with default SFR at this address; available only when WDTCON<4> = 1.

2: These bits are only available on 44-pin devices.

I<sup>2</sup>C<sup>™</sup> SLAVE MODE TIMING WITH SEN = 0 AND ADMSK<5:1> = 01001 **FIGURE 19-11:** (RECEPTION, 10-BIT ADDRESS) SSPOV is set because <u>SSPxBUF</u> is still full. <u>ACK</u> is not sent. Bus master terminates transfer ٩ ACK 6 *ji*<sup>1</sup>/2/3/4/5/6/7/84/94/1/2/3/4/5/6/7/84 Cleared in software Receive Data Byte In this example, an address equal to A9.A8.A7.A6.A5.X.A3.A2.X.X will be Acknowledged and cause an interrupt. Cleared by hardware when SSPxADD is updated with high byte of address Cleared in software Receive Data Byte Clock is held low until update of SSPxADD has taken place Note that the Most Significant bits of the address are not affected by the bit masking. 6 ACK Xa6 Xa5 X X Xa3 Xa2 X X X X UA is set indicating that – SSPxADD needs to be updated Receive Second Byte of Address when SSPxADD is updated with low byte of address Cleared in software Dummy read of SSPxBUF to clear BF flag x = Don't care (i.e., address bit can either be a '1' or a '0'). Cleared by hardware Clock is held low until update of SSPxADD has taken place A7  $R\overline{W} = 0$ ACK 6 (CKP does not reset to '0' when SEN = 0) UA is set indicating that \_\_\_\_\_ the SSPxADD needs to be updated SSPxBUF is written with\_ contents of SSPxSR 1 X 1 X 0 X 49 X A8 Receive First Byte of Address Cleared in software SSPXIF (PIR1<3> or PIR3<7>) SSPOV (SSPxCON1<6>) CKP (SSPxCON1<4>) ~ UA (SSPxSTAT<1>) BF (SSPxSTAT<0>) Note 1: ä ä ſ, SDAX SCLX

PIC18F46J11 FAMILY

© 2011 Microchip Technology Inc.

# PIC18F46J11 FAMILY

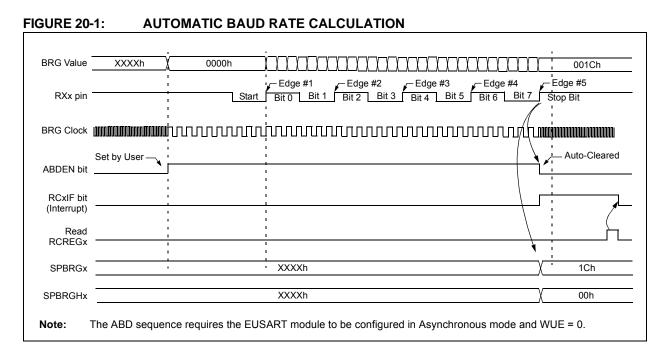

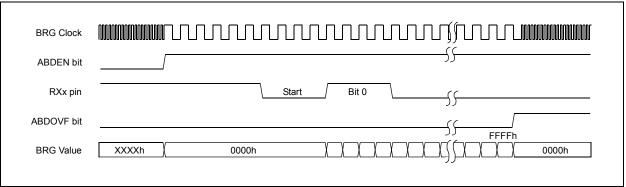

### FIGURE 20-2: BRG OVERFLOW SEQUENCE

# 22.5 Comparator Control and Configuration

Each comparator has up to eight possible combinations of inputs: up to four external analog inputs, and one of two internal voltage references.

Both comparators allow a selection of the signal from pin, CxINA, or the voltage from the comparator reference (CVREF) on the non-inverting channel. This is compared to either CxINB, CTMU or the microcontroller's fixed internal reference voltage (VIRV, 0.6V nominal) on the inverting channel.

Table 22-1 provides the comparator inputs and outputs tied to fixed I/O pins.

Figure 22-4 illustrates the available comparator configurations and their corresponding bit settings.

| TABLE 22-1: | COMPARATOR INPUTS AND |

|-------------|-----------------------|

|             | OUTPUTS               |

| Comparator | Input or Output | I/O Pin         |  |  |  |  |

|------------|-----------------|-----------------|--|--|--|--|

|            | C1INA (VIN+)    | RA0             |  |  |  |  |

| 1          | C1INB (VIN-)    | RA3             |  |  |  |  |

| I          | C1OUT           | Remapped<br>RPn |  |  |  |  |

|            | C2INA(VIN+)     | RA1             |  |  |  |  |

| 2          | C2INB(VIN-)     | RA2             |  |  |  |  |

| 2          | C2OUT           | Remapped<br>RPn |  |  |  |  |

## 22.5.1 COMPARATOR ENABLE AND INPUT SELECTION

Setting the CON bit of the CMxCON register (CMxCON<7>) enables the comparator for operation. Clearing the CON bit disables the comparator, resulting in minimum current consumption.

The CCH<1:0> bits in the CMxCON register (CMxCON<1:0>) direct either one of three analog input pins, or the Internal Reference Voltage (VIRV), to the comparator VIN-. Depending on the comparator operating mode, either an external or internal voltage reference may be used. The analog signal present at VIN- is compared to the signal at VIN+ and the digital output of the comparator is adjusted accordingly.

The external reference is used when CREF = 0 (CMxCON<2>) and VIN+ is connected to the CxINA pin. When external voltage references are used, the comparator module can be configured to have the reference sources externally. The reference signal must be between VSs and VDD, and can be applied to either pin of the comparator.

The comparator module also allows the selection of an internally generated voltage reference (CVREF) from the comparator voltage reference module. This module is described in more detail in **Section 22.0 "Comparator Module"**. The reference from the comparator voltage reference module is only available when CREF = 1. In this mode, the internal voltage reference is applied to the comparator's VIN+ pin.

| Note: | The comparator input pin selected by    |

|-------|-----------------------------------------|

|       | CCH<1:0> must be configured as an input |

|       | by setting both the corresponding TRIS  |

|       | and PCFG bits in the ANCON1 register.   |

## 22.5.2 COMPARATOR ENABLE AND OUTPUT SELECTION

The comparator outputs are read through the CMSTAT register. The CMSTAT<0> reads the Comparator 1 output and CMSTAT<1> reads the Comparator 2 output. These bits are read-only.

The comparator outputs may also be directly output to the RPn I/O pins by setting the COE bit (CMxCON<6>). When enabled, multiplexers in the output path of the pins switch to the output of the comparator.

By default, the comparator's output is at logic high whenever the voltage on VIN+ is greater than on VIN-. The polarity of the comparator outputs can be inverted using the CPOL bit (CMxCON<5>).

The uncertainty of each of the comparators is related to the input offset voltage and the response time given in the specifications, as discussed in **Section 22.2 "Comparator Operation"**.

## 24.6 Operation During Sleep

When enabled, the HLVD circuitry continues to operate during Sleep. If the device voltage crosses the trip point, the LVDIF bit will be set and the device will wakeup from Sleep. Device execution will continue from the interrupt vector address if interrupts have been globally enabled.

## 24.7 Effects of a Reset

A device Reset forces all registers to their Reset state. This forces the HLVD module to be turned off.

| Name    | Bit 7    | Bit 6     | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|---------|----------|-----------|--------|--------|--------|--------|--------|--------|----------------------------|

| HLVDCON | VDIRMAG  | BGVST     | IRVST  | HLVDEN | HLVDL3 | HLVDL2 | HLVDL1 | HLVDL0 | 72                         |

| INTCON  | GIE/GIEH | PEIE/GIEL | TMR0IE | INT0IE | RBIE   | TMR0IF | INT0IF | RBIF   | 69                         |

| PIR2    | OSCFIF   | CM1IF     | CM2IF  | —      | BCLIF  | LVDIF  | TMR3IF | CCP2IF | 71                         |

| PIE2    | OSCFIE   | CM1IE     | CM2IE  | —      | BCLIE  | LVDIE  | TMR3IE | CCP2IE | 71                         |

| IPR2    | OSCFIP   | CM1IP     | CM2IP  | _      | BCLIP  | LVDIP  | TMR3IP | CCP2IP | 71                         |

### TABLE 24-1: REGISTERS ASSOCIATED WITH HIGH/LOW-VOLTAGE DETECT MODULE

Legend: — = unimplemented, read as '0'. Shaded cells are unused by the HLVD module.

# PIC18F46J11 FAMILY

| ADDWF                                                                                                             | ADD W to Indexed<br>(Indexed Literal Offset mode)                |                            |                    |                        |  |  |  |

|-------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|----------------------------|--------------------|------------------------|--|--|--|

| Syntax:                                                                                                           | ADDWF                                                            | [k] {,d}                   |                    |                        |  |  |  |

| Operands:                                                                                                         | $\begin{array}{l} 0 \leq k \leq 95 \\ d  \in  [0,1] \end{array}$ |                            |                    |                        |  |  |  |

| Operation:                                                                                                        | (W) + ((FS                                                       | SR2) + k) -                | $\rightarrow$ dest |                        |  |  |  |

| Status Affected:                                                                                                  | N, OV, C,                                                        | DC, Z                      |                    |                        |  |  |  |

| Encoding:                                                                                                         | 0010                                                             | 01d0                       | kkkk               | kkkk                   |  |  |  |

| Description:                                                                                                      | The conte<br>contents o<br>FSR2, offs                            | f the regis                | ster indica        |                        |  |  |  |

|                                                                                                                   | If 'd' is '0',<br>is '1', the r<br>register 'f'                  | esult is st                |                    |                        |  |  |  |

| Words:                                                                                                            | 1                                                                |                            |                    |                        |  |  |  |

| Cycles:                                                                                                           | 1                                                                |                            |                    |                        |  |  |  |

| Q Cycle Activity:                                                                                                 |                                                                  |                            |                    |                        |  |  |  |

| Q1                                                                                                                | Q2                                                               | Q3                         | 3                  | Q4                     |  |  |  |

| Decode                                                                                                            | Read 'k'                                                         | Proce<br>Data              |                    | Write to<br>estination |  |  |  |

| Example:                                                                                                          | ADDWF                                                            | [OFST]                     | ,0                 |                        |  |  |  |

| Before Instruction<br>W<br>OFST<br>FSR2<br>Contents<br>of 0A2Ch<br>After Instruction<br>W<br>Contents<br>of 0A2Ch | =<br>=<br>=<br>=                                                 | 2Ch<br>0A00r<br>20h<br>37h | ı                  |                        |  |  |  |

| BSF                                                                                                                                                                                                                                      | Bit Set Inde<br>(Indexed L                                                                                                                                                                     | exed<br>iteral Offset r                                                                                                              | node)                                                   |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|--|--|--|--|--|

| Syntax:                                                                                                                                                                                                                                  | BSF [k], b                                                                                                                                                                                     |                                                                                                                                      |                                                         |  |  |  |  |  |

| Operands:                                                                                                                                                                                                                                | $\begin{array}{l} 0 \leq f \leq 95 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                             |                                                                                                                                      |                                                         |  |  |  |  |  |

| Operation:                                                                                                                                                                                                                               | $1 \rightarrow$ ((FSR2                                                                                                                                                                         | $1 \rightarrow ((FSR2) + k) < b >$                                                                                                   |                                                         |  |  |  |  |  |

| Status Affected:                                                                                                                                                                                                                         | None                                                                                                                                                                                           |                                                                                                                                      |                                                         |  |  |  |  |  |

| Encoding:                                                                                                                                                                                                                                | 1000                                                                                                                                                                                           | bbb0 kkk                                                                                                                             | k kkkk                                                  |  |  |  |  |  |

| Description:                                                                                                                                                                                                                             |                                                                                                                                                                                                | e register indic<br>et by the value                                                                                                  |                                                         |  |  |  |  |  |

| Words:                                                                                                                                                                                                                                   | 1                                                                                                                                                                                              |                                                                                                                                      |                                                         |  |  |  |  |  |

| Cycles:                                                                                                                                                                                                                                  | 1                                                                                                                                                                                              |                                                                                                                                      |                                                         |  |  |  |  |  |

| Q Cycle Activity:                                                                                                                                                                                                                        |                                                                                                                                                                                                |                                                                                                                                      |                                                         |  |  |  |  |  |

| Q1                                                                                                                                                                                                                                       | Q2                                                                                                                                                                                             | Q3                                                                                                                                   | Q4                                                      |  |  |  |  |  |

| Decode                                                                                                                                                                                                                                   | Read                                                                                                                                                                                           | Process                                                                                                                              | Write to                                                |  |  |  |  |  |

|                                                                                                                                                                                                                                          | register 'f'                                                                                                                                                                                   | Data                                                                                                                                 | destination                                             |  |  |  |  |  |

| Example:                                                                                                                                                                                                                                 | BSF [                                                                                                                                                                                          | FLAG_OFST]                                                                                                                           | , 7                                                     |  |  |  |  |  |

| Before Instruct<br>FLAG OF                                                                                                                                                                                                               |                                                                                                                                                                                                | 0Ah                                                                                                                                  |                                                         |  |  |  |  |  |

| FSR2                                                                                                                                                                                                                                     | =                                                                                                                                                                                              | 0A00h                                                                                                                                |                                                         |  |  |  |  |  |

| Contents<br>of 0A0Ah                                                                                                                                                                                                                     | =                                                                                                                                                                                              | 55h                                                                                                                                  |                                                         |  |  |  |  |  |

| After Instructio                                                                                                                                                                                                                         | n                                                                                                                                                                                              |                                                                                                                                      |                                                         |  |  |  |  |  |

| Contents<br>of 0A0Ah                                                                                                                                                                                                                     | =                                                                                                                                                                                              | D5h                                                                                                                                  |                                                         |  |  |  |  |  |

| 01 UAUAII                                                                                                                                                                                                                                | -                                                                                                                                                                                              | DOII                                                                                                                                 |                                                         |  |  |  |  |  |

|                                                                                                                                                                                                                                          |                                                                                                                                                                                                |                                                                                                                                      |                                                         |  |  |  |  |  |

| SETF                                                                                                                                                                                                                                     | Set Indexe<br>(Indexed L                                                                                                                                                                       | d<br>iteral Offset r                                                                                                                 | node)                                                   |  |  |  |  |  |

| SETF<br>Syntax:                                                                                                                                                                                                                          |                                                                                                                                                                                                |                                                                                                                                      | node)                                                   |  |  |  |  |  |

| -                                                                                                                                                                                                                                        | (Indexed L                                                                                                                                                                                     |                                                                                                                                      | node)                                                   |  |  |  |  |  |

| Syntax:                                                                                                                                                                                                                                  | (Indexed L<br>SETF [k]                                                                                                                                                                         | iteral Offset r                                                                                                                      | node)                                                   |  |  |  |  |  |

| Syntax:<br>Operands:                                                                                                                                                                                                                     | (Indexed L<br>SETF [k]<br>0 ≤ k ≤ 95                                                                                                                                                           | iteral Offset r                                                                                                                      | node)                                                   |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:                                                                                                                                                                                   | (Indexed Links SETF [k]<br>$0 \le k \le 95$<br>FFh $\rightarrow$ ((FS)                                                                                                                         | iteral Offset r                                                                                                                      |                                                         |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:                                                                                                                                                                      | (Indexed L<br>SETF [k]<br>$0 \le k \le 95$<br>FFh $\rightarrow$ ((FS<br>None<br>0110                                                                                                           | iteral Offset r<br>GR2) + k)                                                                                                         | kk kkkk                                                 |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:                                                                                                                                                                                   | (Indexed L<br>SETF [k]<br>$0 \le k \le 95$<br>FFh $\rightarrow$ ((FS<br>None<br>0110<br>The content                                                                                            | iteral Offset r<br>SR2) + k)                                                                                                         | kk kkkk<br>er indicated                                 |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:                                                                                                                                                                      | (Indexed L<br>SETF [k]<br>$0 \le k \le 95$<br>FFh $\rightarrow$ ((FS<br>None<br>0110<br>The content                                                                                            | BR2) + k)                                                                                                                            | kk kkkk<br>er indicated                                 |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:                                                                                                                                                      | (Indexed L<br>SETF [k]<br>$0 \le k \le 95$<br>FFh $\rightarrow$ ((FS<br>None<br>0110<br>The content<br>by FSR2, or                                                                             | BR2) + k)                                                                                                                            | kk kkkk<br>er indicated                                 |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:                                                                                                                                            | (Indexed L<br>SETF [k]<br>$0 \le k \le 95$<br>FFh $\rightarrow$ ((FS<br>None<br>0110<br>The content<br>by FSR2, of<br>1                                                                        | BR2) + k)                                                                                                                            | kk kkkk<br>er indicated                                 |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles:                                                                                                                                 | (Indexed L<br>SETF [k]<br>$0 \le k \le 95$<br>FFh $\rightarrow$ ((FS<br>None<br>0110<br>The content<br>by FSR2, of<br>1                                                                        | BR2) + k)                                                                                                                            | kk kkkk<br>er indicated                                 |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles:<br>Q Cycle Activity:                                                                                                            | (Indexed Li<br>SETF [k]<br>$0 \le k \le 95$<br>FFh $\rightarrow$ ((FS<br>None<br>0110<br>The content<br>by FSR2, of<br>1<br>1                                                                  | iteral Offset r<br>SR2) + k)<br>1000 kkł<br>ts of the regist<br>ffset by 'k', are<br>Q3<br>Process                                   | kk kkkk<br>er indicated<br>e set to FFh.<br>Q4<br>Write |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles:<br>Q Cycle Activity:<br>Q1                                                                                                      | (Indexed L<br>SETF [k]<br>$0 \le k \le 95$<br>FFh $\rightarrow$ ((FS<br>None<br>0110<br>The content<br>by FSR2, of<br>1<br>1<br>2                                                              | iteral Offset r<br>SR2) + k)<br>1000 kkH<br>ts of the regist<br>ffset by 'k', are<br>Q3                                              | kk kkkk<br>er indicated<br>e set to FFh.<br>Q4          |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles:<br>Q Cycle Activity:<br>Q1<br>Decode                                                                                            | (Indexed Li<br>SETF [k]<br>$0 \le k \le 95$<br>FFh $\rightarrow$ ((FS<br>None<br>0110<br>The content<br>by FSR2, of<br>1<br>1<br>Q2<br>Read 'k'                                                | R2) + k)<br>1000 kkk<br>ts of the regist<br>ffset by 'k', are<br>Q3<br>Process<br>Data                                               | kk kkkk<br>er indicated<br>e set to FFh.<br>Q4<br>Write |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles:<br>Q Cycle Activity:<br>Q1<br>Decode<br>Example:                                                                                | (Indexed L<br>SETF [k]<br>$0 \le k \le 95$<br>FFh $\rightarrow$ ((FS<br>None<br>0110<br>The content<br>by FSR2, of<br>1<br>1<br>2<br>Read 'k'<br>SETF [                                        | iteral Offset r<br>SR2) + k)<br>1000 kkł<br>ts of the regist<br>ffset by 'k', are<br>Q3<br>Process                                   | kk kkkk<br>er indicated<br>e set to FFh.<br>Q4<br>Write |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles:<br>Q Cycle Activity:<br>Q1<br>Decode                                                                                            | (Indexed L<br>SETF [k]<br>$0 \le k \le 95$<br>FFh $\rightarrow$ ((FS<br>None<br>0110<br>The content<br>by FSR2, of<br>1<br>1<br>2<br>Read 'k'<br>SETF [                                        | iteral Offset r<br>(R2) + k)<br>1000 kkk<br>ts of the regist<br>ffset by 'k', are<br>Q3<br>Process<br>Data<br>OFST]                  | kk kkkk<br>er indicated<br>e set to FFh.<br>Q4<br>Write |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles:<br>Q Cycle Activity:<br>Q1<br>Decode<br>Example:<br>Before Instruct<br>OFST<br>FSR2                                             | (Indexed Li<br>SETF [k]<br>$0 \le k \le 95$<br>FFh $\rightarrow$ ((FS<br>None<br>0110<br>The content<br>by FSR2, of<br>1<br>1<br>Q2<br>Read 'k'<br>SETF [<br>ion<br>= 2C                       | iteral Offset r<br>(R2) + k)<br>1000 kkk<br>ts of the regist<br>ffset by 'k', are<br>Q3<br>Process<br>Data<br>OFST]                  | kk kkkk<br>er indicated<br>e set to FFh.<br>Q4<br>Write |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles:<br>Q Cycle Activity:<br>Q1<br>Decode<br>Example:<br>Before Instruct<br>OFST                                                     | (Indexed Li<br>SETF [k]<br>$0 \le k \le 95$<br>FFh $\rightarrow$ ((FS<br>None<br>0110<br>The content<br>by FSR2, of<br>1<br>1<br>2<br>Read 'k'<br>SETF [<br>ion<br>= 2C<br>= 0A                | iteral Offset r<br>SR2) + k)<br>1000 kkH<br>ts of the regist<br>ffset by 'k', are<br>Q3<br>Process<br>Data<br>OFST]<br>h<br>00h      | kk kkkk<br>er indicated<br>e set to FFh.<br>Q4<br>Write |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles:<br>Q Cycle Activity:<br>Q1<br>Decode<br>Example:<br>Before Instruct<br>OFST<br>FSR2<br>Contents<br>of 0A2Ch<br>After Instructio | (Indexed Li<br>SETF [k]<br>$0 \le k \le 95$<br>FFh $\rightarrow$ ((FS<br>None<br>0110<br>The content<br>by FSR2, of<br>1<br>1<br>2<br>Read 'k'<br>SETF [<br>ion<br>= 2C<br>= 0A<br>= 00        | iteral Offset r<br>SR2) + k)<br>1000 kkH<br>ts of the regist<br>ffset by 'k', are<br>Q3<br>Process<br>Data<br>OFST]<br>h<br>00h      | kk kkkk<br>er indicated<br>e set to FFh.<br>Q4<br>Write |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles:<br>Q Cycle Activity:<br>Q1<br>Decode<br>Example:<br>Before Instruct<br>OFST<br>FSR2<br>Contents<br>of 0A2Ch                     | (Indexed Li<br>SETF [k]<br>$0 \le k \le 95$<br>FFh $\rightarrow$ ((FS<br>None<br>0110<br>The content<br>by FSR2, of<br>1<br>1<br>Q2<br>Read 'k'<br>SETF [<br>ion<br>= 2C<br>= 0A<br>= 000<br>n | iteral Offset r<br>SR2) + k)<br>1000 kkk<br>ts of the regist<br>ffset by 'k', are<br>Q3<br>Process<br>Data<br>OFST]<br>h<br>00h<br>h | kk kkkk<br>er indicated<br>e set to FFh.<br>Q4<br>Write |  |  |  |  |  |

## 28.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB® IDE Software

- Assemblers/Compilers/Linkers

- MPASM<sup>™</sup> Assembler

- MPLAB C18 and MPLAB C30 C Compilers

- MPLINK™ Object Linker/

- MPLIB™ Object Librarian

- MPLAB ASM30 Assembler/Linker/Library

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB ICE 2000 In-Circuit Emulator

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debugger

- MPLAB ICD 2

- Device Programmers

- PICSTART® Plus Development Programmer

- MPLAB PM3 Device Programmer

- PICkit<sup>™</sup> 2 Development Programmer

- Low-Cost Demonstration and Development Boards and Evaluation Kits

## 28.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> operating system-based application that contains:

- A single graphical interface to all debugging tools

- Simulator

- Programmer (sold separately)

- Emulator (sold separately)

- In-Circuit Debugger (sold separately)

- · A full-featured editor with color-coded context

- A multiple project manager

- Customizable data windows with direct edit of contents

- · High-level source code debugging

- Visual device initializer for easy register initialization

- · Mouse over variable inspection

- Drag and drop variables from source to watch windows

- · Extensive online help

- Integration of select third party tools, such as HI-TECH Software C Compilers and IAR C Compilers

The MPLAB IDE allows you to:

- Edit your source files (either assembly or C)

- One touch assemble (or compile) and download to PIC MCU emulator and simulator tools (automatically updates all project information)

- · Debug using:

- Source files (assembly or C)

- Mixed assembly and C

- Machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost-effective simulators, through low-cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increased flexibility and power.

## 29.4 AC (Timing) Characteristics

### 29.4.1 TIMING PARAMETER SYMBOLOGY

The timing parameter symbols have been created following one of the following formats:

| 1. TppS2ppS                | 6                               | 3. Tcc:st | (I <sup>2</sup> C specifications only) |

|----------------------------|---------------------------------|-----------|----------------------------------------|

| 2. TppS                    |                                 | 4. Ts     | (I <sup>2</sup> C specifications only) |

| Т                          |                                 |           |                                        |

| F                          | Frequency                       | Т         | Time                                   |

| Lowercase le               | etters (pp) and their meanings: |           |                                        |

| рр                         |                                 |           |                                        |

| сс                         | CCP1                            | osc       | OSC1                                   |

| ck                         | CLKO                            | rd        | RD                                     |

| cs                         | CS                              | rw        | RD or WR                               |

| di                         | SDI                             | sc        | SCK                                    |

| do                         | SDO                             | SS        | SS                                     |

| dt                         | Data in                         | tO        | TOCKI                                  |

| io                         | I/O port                        | t1        | T13CKI                                 |

| mc                         | MCLR                            | wr        | WR                                     |

| Uppercase le               | etters and their meanings:      |           |                                        |

| S                          |                                 |           |                                        |

| F                          | Fall                            | Р         | Period                                 |

| н                          | High                            | R         | Rise                                   |

| I                          | Invalid (High-impedance)        | V         | Valid                                  |

| L                          | Low                             | Z         | High-impedance                         |

| I <sup>2</sup> C only      |                                 |           |                                        |

| AA                         | output access                   | High      | High                                   |

| BUF                        | Bus free                        | Low       | Low                                    |

| TCC:ST (I <sup>2</sup> C s | specifications only)            |           |                                        |

| CC                         |                                 |           |                                        |

| HD                         | Hold                            | SU        | Setup                                  |

| ST                         |                                 |           |                                        |

| DAT                        | DATA input hold                 | STO       | Stop condition                         |

| STA                        | Start condition                 |           |                                        |

## **30.0 PACKAGING INFORMATION**

## **30.1** Package Marking Information

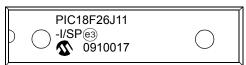

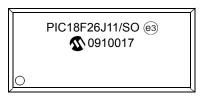

#### 28-Lead SPDIP

#### 28-Lead SSOP

### 28-Lead SOIC (.300")

#### 28-Lead QFN

Example

### Example

### Example

## Example

| Legend | d: XXX Customer-specific information                                                                                  |                                                                |  |  |  |  |

|--------|-----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--|--|--|--|

|        | Y                                                                                                                     | Year code (last digit of calendar year)                        |  |  |  |  |

|        | ΥY                                                                                                                    | Year code (last 2 digits of calendar year)                     |  |  |  |  |

|        | WW                                                                                                                    | Week code (week of January 1 is week '01')                     |  |  |  |  |

|        | NNN Alphanumeric traceability code                                                                                    |                                                                |  |  |  |  |

|        | Pb-free JEDEC designator for Matte Tin (Sn)                                                                           |                                                                |  |  |  |  |

|        | * This package is Pb-free. The Pb-free JEDEC designator ((e3))                                                        |                                                                |  |  |  |  |

|        |                                                                                                                       | can be found on the outer packaging for this package. $\smile$ |  |  |  |  |