Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 48MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 34                                                                          |

| Program Memory Size        | 32KB (16K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 3.8K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.15V ~ 3.6V                                                                |

| Data Converters            | A/D 13x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 44-QFN (8x8)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f45j11t-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

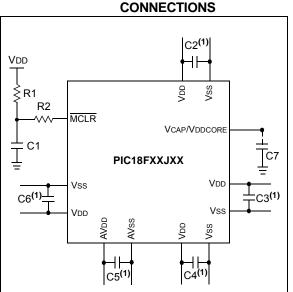

#### 2.0 GUIDELINES FOR GETTING STARTED WITH PIC18FJ MICROCONTROLLERS

#### 2.1 Basic Connection Requirements

Getting started with the PIC18F46J11 family of 8-bit microcontrollers requires attention to a minimal set of device pin connections before proceeding with development.

The following pins must always be connected:

- All VDD and Vss pins (see Section 2.2 "Power Supply Pins")

- All AVDD and AVss pins, regardless of whether or not the analog device features are used (see Section 2.2 "Power Supply Pins")

- MCLR pin

(see Section 2.3 "Master Clear (MCLR) Pin")

- VCAP/VDDCORE pins (see Section 2.4 "Voltage Regulator Pins (VCAP/VDDCORE)")

These pins must also be connected if they are being used in the end application:

- PGC/PGD pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.5 "ICSP Pins**")

- OSCI and OSCO pins when an external oscillator source is used

(see Section 2.6 "External Oscillator Pins")

Additionally, the following pins may be required:

• VREF+/VREF- pins are used when external voltage reference for analog modules is implemented

**Note:** The AVDD and AVss pins must always be connected, regardless of whether any of the analog modules are being used.

The minimum mandatory connections are shown in Figure 2-1.

### FIGURE 2-1: RECOMMENDED MINIMUM

#### Key (all values are recommendations):

C1 through C6: 0.1 µF, 20V ceramic

C7: 10 µF, 6.3V or greater, tantalum or ceramic

R1: 10 kΩ

R2: 100Ω to 470Ω

**Note 1:** The example shown is for a PIC18F device with five VDD/VSs and AVDD/AVSs pairs. Other devices may have more or less pairs; adjust the number of decoupling capacitors appropriately.

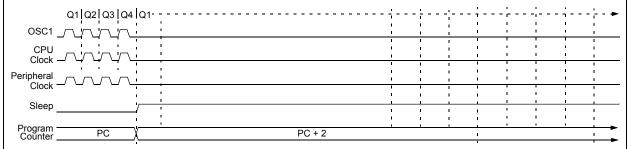

#### 4.3 Sleep Mode

The power-managed Sleep mode is identical to the legacy Sleep mode offered in all other PIC devices. It is entered by clearing the IDLEN bit (the default state on device Reset) and executing the SLEEP instruction. This shuts down the selected oscillator (Figure 4-5). All clock source status bits are cleared.

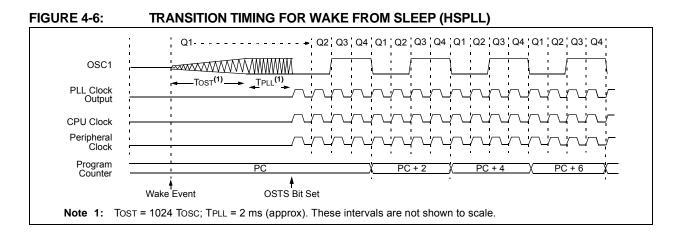

Entering the Sleep mode from any other mode does not require a clock switch. This is because no clocks are needed once the controller has entered Sleep mode. If the WDT is selected, the INTRC source will continue to operate. If the Timer1 oscillator is enabled, it will also continue to run. When a wake event occurs in Sleep mode (by interrupt, Reset or WDT time-out), the device will not be clocked until the clock source selected by the SCS<1:0> bits becomes ready (see Figure 4-6), or it will be clocked from the internal oscillator if either the Two-Speed Start-up or the FSCM is enabled (see Section 26.0 "Special Features of the CPU"). In either case, the OSTS bit is set when the primary clock is providing the device clocks. The IDLEN and SCS bits are not affected by the wake-up.

| TABLE 5-2:          | 2: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED) |             |                                                                |                                                                            |                                 |  |  |

|---------------------|------------------------------------------------------------|-------------|----------------------------------------------------------------|----------------------------------------------------------------------------|---------------------------------|--|--|

| Register            | Applicable Devices                                         |             | Power-on Reset,<br>Brown-out Reset,<br>Wake From<br>Deep Sleep | MCLR Resets<br>WDT Reset<br>RESET Instruction<br>Stack Resets<br>CM Resets | Wake-up via WDT<br>or Interrupt |  |  |

| INDF2               | PIC18F2XJ11                                                | PIC18F4XJ11 | N/A                                                            | N/A                                                                        | N/A                             |  |  |

| POSTINC2            | PIC18F2XJ11                                                | PIC18F4XJ11 | N/A                                                            | N/A                                                                        | N/A                             |  |  |

| POSTDEC2            | PIC18F2XJ11                                                | PIC18F4XJ11 | N/A                                                            | N/A                                                                        | N/A                             |  |  |

| PREINC2             | PIC18F2XJ11                                                | PIC18F4XJ11 | N/A                                                            | N/A                                                                        | N/A                             |  |  |

| PLUSW2              | PIC18F2XJ11                                                | PIC18F4XJ11 | N/A                                                            | N/A                                                                        | N/A                             |  |  |

| FSR2H               | PIC18F2XJ11                                                | PIC18F4XJ11 | 0000                                                           | 0000                                                                       | uuuu                            |  |  |

| FSR2L               | PIC18F2XJ11                                                | PIC18F4XJ11 | xxxx xxxx                                                      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |

| STATUS              | PIC18F2XJ11                                                | PIC18F4XJ11 | x xxxx                                                         | u uuuu                                                                     | u uuuu                          |  |  |

| TMR0H               | PIC18F2XJ11                                                | PIC18F4XJ11 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |

| TMR0L               | PIC18F2XJ11                                                | PIC18F4XJ11 | xxxx xxxx                                                      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |

| T0CON               | PIC18F2XJ11                                                | PIC18F4XJ11 | 1111 1111                                                      | 1111 1111                                                                  | uuuu uuuu                       |  |  |

| OSCCON              | PIC18F2XJ11                                                | PIC18F4XJ11 | 0110 q100                                                      | 0110 q100                                                                  | 0110 qluu                       |  |  |

| CM1CON              | PIC18F2XJ11                                                | PIC18F4XJ11 | 0001 1111                                                      | 0001 1111                                                                  | uuuu uuuu                       |  |  |

| CM2CON              | PIC18F2XJ11                                                | PIC18F4XJ11 | 0001 1111                                                      | 0001 1111                                                                  | uuuu uuuu                       |  |  |

| RCON <sup>(4)</sup> | PIC18F2XJ11                                                | PIC18F4XJ11 | 0-11 11qq                                                      | 0-qq qquu                                                                  | u-qq qquu                       |  |  |

| TMR1H               | PIC18F2XJ11                                                | PIC18F4XJ11 | xxxx xxxx                                                      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |

| TMR1L               | PIC18F2XJ11                                                | PIC18F4XJ11 | xxxx xxxx                                                      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |

| T1CON               | PIC18F2XJ11                                                | PIC18F4XJ11 | 0000 0000                                                      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |

| TMR2                | PIC18F2XJ11                                                | PIC18F4XJ11 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |

| PR2                 | PIC18F2XJ11                                                | PIC18F4XJ11 | 1111 1111                                                      | 1111 1111                                                                  | uuuu uuuu                       |  |  |

| T2CON               | PIC18F2XJ11                                                | PIC18F4XJ11 | -000 0000                                                      | -000 0000                                                                  | -uuu uuuu                       |  |  |

| SSP1BUF             | PIC18F2XJ11                                                | PIC18F4XJ11 | xxxx xxxx                                                      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |

| SSP1ADD             | PIC18F2XJ11                                                | PIC18F4XJ11 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |

| SSP1MSK             | PIC18F2XJ11                                                | PIC18F4XJ11 | 1111 1111                                                      | 1111 1111                                                                  | uuuu uuuu                       |  |  |

| SSP1STAT            | PIC18F2XJ11                                                | PIC18F4XJ11 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |

| SSP1CON1            | PIC18F2XJ11                                                | PIC18F4XJ11 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |

| SSP1CON2            | PIC18F2XJ11                                                | PIC18F4XJ11 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |

| ADRESH              | PIC18F2XJ11                                                | PIC18F4XJ11 | xxxx xxxx                                                      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |

| ADRESL              | PIC18F2XJ11                                                | PIC18F4XJ11 | xxxx xxxx                                                      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |

| ADCON0              | PIC18F2XJ11                                                | PIC18F4XJ11 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |

| ADCON1              | PIC18F2XJ11                                                | PIC18F4XJ11 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |

| WDTCON              | PIC18F2XJ11                                                | PIC18F4XJ11 | 1qq- q000                                                      | 1qq- 0000                                                                  | uqq- uuuu                       |  |  |

#### TABLE 5-2: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition.

**Note 1:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

**2:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

3: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

- 4: See Table 5-1 for Reset value for specific condition.

- 5: Not implemented for PIC18F2XJ11 devices.

- 6: Not implemented on "LF" devices.

#### 6.3.4.1 Context Defined SFRs

There are several registers that share the same address in the SFR space. The register's definition and usage depends on the operating mode of its associated peripheral. These registers are:

- SSPxADD and SSPxMSK: These are two separate hardware registers, accessed through a single SFR address. The operating mode of the MSSP modules determines which register is being accessed. See Section 19.5.3.4 "7-Bit Address Masking Mode" for additional details.

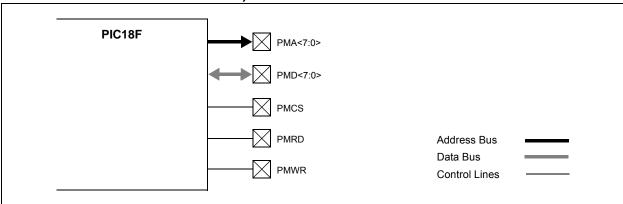

- PMADDRH/L and PMDOUT2H/L: In this case, these named buffer pairs are actually the same physical registers. The Parallel Master Port (PMP) module's operating mode determines what function the registers take on. See Section 11.1.2 "Data Registers" for additional details.

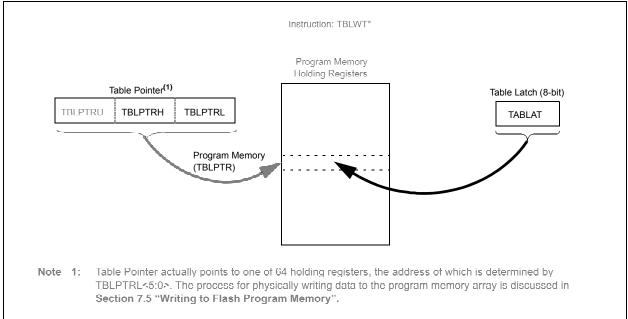

#### FIGURE 7-2: TABLE WRITE OPERATION

### 7.2 Control Registers

Several control registers are used in conjunction with the TBLRD and TBLWT instructions. Those are:

- EECON1 register

- · EECON2 register

- TABLAT register

- TBLPTR registers

#### 7.2.1 EECON1 AND EECON2 REGISTERS

The EECON1 register (Register 7-1) is the control register for memory accesses. The EECON2 register is not a physical register; it is used exclusively in the memory write and erase sequences. Reading EECON2 will read all '0's.

The WPROG bit, when set, will allow programming two bytes per word on the execution of the WR command. If this bit is cleared, the WR command will result in programming on a block of 64 bytes. The FREE bit, when set, will allow a program memory erase operation. When FREE is set, the erase operation is initiated on the next WR command. When FREE is clear, only writes are enabled.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. The WRERR bit is set in hardware when the WR bit is set, and cleared when the internal programming timer expires and the write operation is complete.

| Note: | During normal operation, the WRERR is       |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|

|       | read as '1'. This can indicate that a write |  |  |  |  |

|       | operation was prematurely terminated by     |  |  |  |  |

|       | a Reset, or a write operation was           |  |  |  |  |

|       | attempted improperly.                       |  |  |  |  |

The WR control bit initiates write operations. The bit cannot be cleared, only set, in software. It is cleared in hardware at the completion of the write operation.

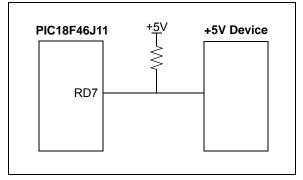

#### 10.1.3 INTERFACING TO A 5V SYSTEM

Though the VDDMAX of the PIC18F46J11 family is 3.6V, these devices are still capable of interfacing with 5V systems, even if the VIH of the target system is above 3.6V. This is accomplished by adding a pull-up resistor to the port pin (Figure 10-2), clearing the LAT bit for that pin and manipulating the corresponding TRIS bit (Figure 10-1) to either allow the line to be pulled high or to drive the pin low. Only port pins that are tolerant of voltages up to 5.5V can be used for this type of interface (refer to Section 10.1.2 "Input Pins and Voltage Considerations").

FIGURE 10-2: +5V SYSTEM HARDWARE INTERFACE

#### EXAMPLE 10-1: COMMUNICATING WITH THE +5V SYSTEM

| BCF LATD, | 7 | ; set up LAT register so<br>; changing TRIS bit will<br>; drive line low |

|-----------|---|--------------------------------------------------------------------------|

|           |   | ; send a 0 to the 5V system<br>; send a 1 to the 5V system               |

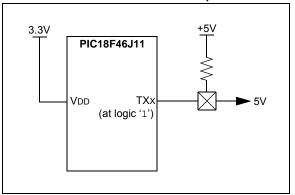

#### 10.1.4 OPEN-DRAIN OUTPUTS

The output pins for several peripherals are also equipped with a configurable open-drain output option. This allows the peripherals to communicate with external digital logic operating at a higher voltage level, without the use of level translators. The open-drain option is implemented on port pins specifically associated with the data and clock outputs of the EUSARTs, the MSSP modules (in SPI mode) and the ECCP modules. It is selectively enabled by setting the open-drain control bit for the corresponding module in the ODCON registers (Register 10-1, Register 10-2 and Register 10-3). Their configuration is discussed in more detail with the individual port where these peripherals are multiplexed.

When the open-drain option is required, the output pin must also be tied through an external pull-up resistor provided by the user to a higher voltage level, up to 5.5V (Figure 10-3). When a digital logic high signal is output, it is pulled up to the higher voltage level.

#### FIGURE 10-3: USING THE OPEN-DRAIN OUTPUT (USART SHOWN AS EXAMPLE)

#### 10.1.5 TTL INPUT BUFFER OPTION

Many of the digital I/O ports use Schmitt Trigger (ST) input buffers. While this form of buffering works well with many types of input, some applications may require TTL level signals to interface with external logic devices. This is particularly true for the Parallel Master Port (PMP), which is likely to be interfaced to TTL level logic or memory devices.

The inputs for the PMP can be optionally configured for TTL buffers with the PMPTTL bit in the PADCFG1 register (Register 10-4). Setting this bit configures all data and control input pins for the PMP to use TTL buffers. By default, these PMP inputs use the port's ST buffers.

Choosing the configuration requires the review of all PPSs and their pin assignments, especially those that will not be used in the application. In all cases, unused pin selectable peripherals should be disabled completely. Unused peripherals should have their inputs assigned to an unused RPn pin function. I/O pins with unused RPn functions should be configured with the null peripheral output.

The assignment of a peripheral to a particular pin does not automatically perform any other configuration of the pin's I/O circuitry. In theory, this means adding a pin selectable output to a pin may mean inadvertently driving an existing peripheral input when the output is driven. Users must be familiar with the behavior of other fixed peripherals that share a remappable pin and know when to enable or disable them. To be safe, fixed digital peripherals that share the same pin should be disabled when not in use.

Along these lines, configuring a remappable pin for a specific peripheral does not automatically turn that feature on. The peripheral must be specifically configured for operation and enabled, as if it were tied to a fixed pin. Where this happens in the application code (immediately following device Reset and peripheral configuration or inside the main application routine) depends on the peripheral and its use in the application.

A final consideration is that the PPS functions neither override analog inputs nor reconfigure pins with analog functions for digital I/O. If a pin is configured as an analog input on device Reset, it must be explicitly reconfigured as digital I/O when used with a PPS.

Example 10-7 provides a configuration for bidirectional communication with flow control using EUSART2. The following input and output functions are used:

- Input Function RX2

- Output Function TX2

#### EXAMPLE 10-7: CONFIGURING EUSART2 INPUT AND OUTPUT FUNCTIONS

```

;*******

; Unlock Registers

; PPS registers are in BANK 14

MOVLB

0 \times 0 E

BCF

INTCON, GIE ; Disable interrupts

MOVLW

0x55

MOVWF

EECON2, 0

MOVLW

0xAA

MOVWF

EECON2, 0

; Turn off PPS Write Protect

PPSCON, IOLOCK, BANKED

BCF

********

; Configure Input Functions

; (See Table 9-13)

;************************

; Assign RX2 To Pin RP0

MOVLW

0x00

MOVWF

RPINR16, BANKED

********

; Configure Output Functions

; (See Table 9-14)

; Assign TX2 To Pin RP1

MOVLW

0 \ge 0.5

MOVWF

RPOR1, BANKED

; Lock Registers

MOVLW

0x55

MOVWF

EECON2. 0

MOVLW

0xAA

MOVWF

EECON2, 0

; Write Protect PPS

BSF PPSCON, IOLOCK, BANKED

```

Note: If the Configuration bit, IOL1WAY = 1, once the IOLOCK bit is set, it cannot be cleared, preventing any future RP register changes. The IOLOCK bit is cleared back to '0' on any device Reset.

| R = Readable b | bit                                                 | W = Writable bit U = |       |       | mented bit, read | as '0' |       |

|----------------|-----------------------------------------------------|----------------------|-------|-------|------------------|--------|-------|

| Legend:        | $R/\overline{W}$ = Readable, Writable if IOLOCK = 0 |                      |       |       |                  |        |       |

| bit 7 bit 0    |                                                     |                      |       |       |                  | bit 0  |       |

|                |                                                     | _                    | RP9R4 | RP9R3 | RP9R2            | RP9R1  | RP9R0 |

| U-0            | U-0                                                 | U-0                  | R/W-0 | R/W-0 | R/W-0            | R/W-0  | R/W-0 |

'0' = Bit is cleared

x = Bit is unknown

#### REGISTER 10-30: RPOR9: PERIPHERAL PIN SELECT OUTPUT REGISTER 9 (BANKED ECFh)

bit 7-5 Unimplemented: Read as '0'

-n = Value at POR

bit 4-0 **RP9R<4:0>:** Peripheral Output Function is Assigned to RP9 Output Pin bits (see Table 10-14 for peripheral function numbers)

'1' = Bit is set

#### REGISTER 10-31: RPOR10: PERIPHERAL PIN SELECT OUTPUT REGISTER 10 (BANKED ED0h)

| U-0   | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-----|--------|--------|--------|--------|--------|

| —     | —   |     | RP10R4 | RP10R3 | RP10R2 | RP10R1 | RP10R0 |

| bit 7 |     |     |        |        |        |        | bit 0  |

| Legend:           | $R/\overline{W}$ = Readable, Writable if IOLOCK = 0 |                      |                    |  |  |

|-------------------|-----------------------------------------------------|----------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared | x = Bit is unknown |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP10R<4:0>:** Peripheral Output Function is Assigned to RP10 Output Pin bits (see Table 10-14 for peripheral function numbers)

#### REGISTER 10-32: RPOR11: PERIPHERAL PIN SELECT OUTPUT REGISTER 11 (BANKED ED1h)

| U-0   | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-----|--------|--------|--------|--------|--------|

| —     | —   | —   | RP11R4 | RP11R3 | RP11R2 | RP11R1 | RP11R0 |

| bit 7 |     |     |        |        |        |        | bit 0  |

| Legend:           | $R/\overline{W}$ = Readable, Writable if IOLOCK = 0 |                             |                    |  |

|-------------------|-----------------------------------------------------|-----------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit                                    | U = Unimplemented bit, read | d as '0'           |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared        | x = Bit is unknown |  |

#### bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP11R<4:0>:** Peripheral Output Function is Assigned to RP11 Output Pin bits (see Table 10-14 for peripheral function numbers)

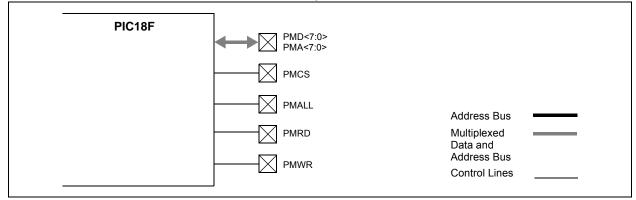

## FIGURE 11-9: DEMULTIPLEXED ADDRESSING MODE (SEPARATE READ AND WRITE STROBES WITH CHIP SELECT)

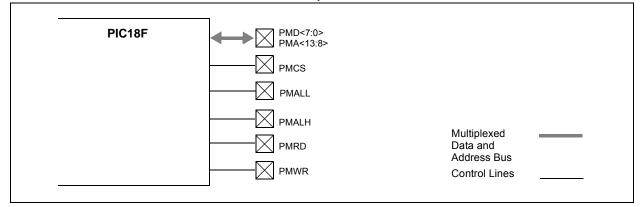

## FIGURE 11-10: PARTIALLY MULTIPLEXED ADDRESSING MODE (SEPARATE READ AND WRITE STROBES WITH CHIP SELECT)

## FIGURE 11-11: FULLY MULTIPLEXED ADDRESSING MODE (SEPARATE READ AND WRITE STROBES WITH CHIP SELECT)

#### 12.3 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module. The prescaler is not directly readable or writable. Its value is set by the PSA and T0PS<2:0> bits (T0CON<3:0>), which determine the prescaler assignment and prescale ratio.

Clearing the PSA bit assigns the prescaler to the Timer0 module. When it is assigned, prescale values from 1:2 through 1:256 in power-of-2 increments are selectable.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF TMR0, MOVWF TMR0, BSF TMR0, etc.) clear the prescaler count.

| Note: | Writing to TMR0 when the prescaler is       |

|-------|---------------------------------------------|

|       | assigned to Timer0 will clear the prescaler |

|       | count but will not change the prescaler     |

|       | assignment.                                 |

#### 12.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control and can be changed "on-the-fly" during program execution.

#### 12.4 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h in 8-bit mode, or from FFFFh to 0000h in 16-bit mode. This overflow sets the TMR0IF flag bit. The interrupt can be masked by clearing the TMR0IE bit (INTCON<5>). Before re-enabling the interrupt, the TMR0IF bit must be cleared in software by the Interrupt Service Routine (ISR).

Since Timer0 is shut down in Sleep mode, the TMR0 interrupt cannot awaken the processor from Sleep.

| Name   | Bit 7                     | Bit 6     | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0 | Reset<br>Values<br>on Page: |

|--------|---------------------------|-----------|--------|--------|-------|--------|--------|-------|-----------------------------|

| TMR0L  | Timer0 Register Low Byte  |           |        |        |       |        | 91     |       |                             |

| TMR0H  | Timer0 Register High Byte |           |        |        |       | 91     |        |       |                             |

| INTCON | GIE/GIEH                  | PEIE/GIEL | TMR0IE | INT0IE | RBIE  | TMR0IF | INT0IF | RBIF  | 90                          |

| T0CON  | TMR0ON                    | T08BIT    | TOCS   | T0SE   | PSA   | T0PS2  | T0PS1  | T0PS0 | 91                          |

TABLE 12-1:

REGISTERS ASSOCIATED WITH TIMER0

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by Timer0.

#### 15.5.2 TIMER3 GATE SOURCE SELECTION

The Timer3 gate source can be selected from one of four different sources. Source selection is controlled by the T3GSSx bits of the T3GCON register. The polarity for each available source is also selectable. Polarity selection is controlled by the T3GPOL bit of the T3GCON register.

TABLE 15-2: TIMER3 GATE SOURCES

| T3GSS<1:0> | Timer3 Gate Source                                      |

|------------|---------------------------------------------------------|

| 00         | Timer3 Gate Pin                                         |

| 01         | Overflow of Timer0<br>(TMR0 increments from FFh to 00h) |

| 10         | TMR2 to Match PR2<br>(TMR2 increments to match PR2)     |

| 11         | Reserved                                                |

#### 15.5.2.1 T3G Pin Gate Operation

The T3G pin is one source for Timer3 gate control. It can be used to supply an external source to the Timer3 gate circuitry.

#### 15.5.2.2 Timer0 Overflow Gate Operation

When Timer0 increments from FFh to 00h, a low-to-high pulse will automatically be generated and internally supplied to the Timer3 gate circuitry.

## 15.5.2.3 Timer2 Match Gate Operation

The TMR2 register will increment until it matches the value in the PR2 register. On the very next increment cycle, TMR2 will be reset to 00h. When this Reset occurs, a low-to-high pulse will automatically be generated and internally supplied to the Timer3 gate circuitry.

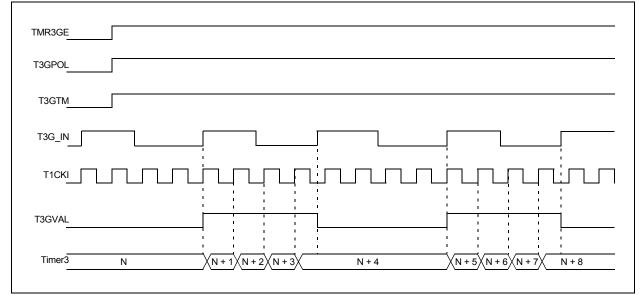

#### 15.5.3 TIMER3 GATE TOGGLE MODE

When Timer3 Gate Toggle mode is enabled, it is possible to measure the full cycle length of a Timer3 gate signal, as opposed to the duration of a single level pulse.

The Timer1 gate source is routed through a flip-flop that changes state on every incrementing edge of the signal. See Figure 15-3 for timing details.

The T3GVAL bit will indicate when the Toggled mode is active and the timer is counting.

Timer3 Gate Toggle mode is enabled by setting the T3GTM bit of the T3GCON register. When the T3GTM bit is cleared, the flip-flop is cleared and held clear. This is necessary in order to control which edge is measured.

#### FIGURE 15-3: TIMER3 GATE TOGGLE MODE

#### 16.2 **Timer4 Interrupt**

The Timer4 module has an 8-bit Period register, PR4, which is both readable and writable. Timer4 increments from 00h until it matches PR4 and then resets to 00h on the next increment cycle. The PR4 register is initialized to FFh upon Reset.

#### **FIGURE 16-1: TIMER4 BLOCK DIAGRAM**

#### 4 1:1 to 1:16 T4OUTPS<3:0> Set TMR4IF Postscaler 2 TMR4 Output T4CKPS<1:0> (to PWM) TMR4/PR4 Reset Match 1:1, 1:4, 1:16 Comparator Fosc/4 TMR4 PR4 Prescaler ₽¥ ₽₹₽ 8 Internal Data Bus

16.3

is the Timer2 output.

**Output of TMR4**

The output of TMR4 (before the postscaler) is used

only as a PWM time base for the ECCP modules. It is

not used as a baud rate clock for the MSSP modules as

#### TABLE 16-1: REGISTERS ASSOCIATED WITH TIMER4 AS A TIMER/COUNTER

| Name   | Bit 7                  | Bit 6     | Bit 5    | Bit 4    | Bit 3    | Bit 2  | Bit 1   | Bit 0   | Reset<br>Values<br>on Page: |

|--------|------------------------|-----------|----------|----------|----------|--------|---------|---------|-----------------------------|

| INTCON | GIE/GIEH               | PEIE/GIEL | TMR0IE   | INT0IE   | RBIE     | TMR0IF | INT0IF  | RBIF    | 90                          |

| IPR3   | SSP2IP                 | BCL2IP    | RC2IP    | TX2IP    | TMR4IP   | CTMUIP | TMR3GIP | RTCIP   | 92                          |

| PIR3   | SSP2IF                 | BCL2IF    | RC2IF    | TX2IF    | TMR4IF   | CTMUIF | TMR3GIF | RTCIF   | 92                          |

| PIE3   | SSP2IE                 | BCL2IE    | RC2IE    | TX2IE    | TMR4IE   | CTMUIE | TMR3GIE | RTCIE   | 92                          |

| TMR4   | Timer4 Register        |           |          |          |          |        | 93      |         |                             |

| T4CON  | _                      | T4OUTPS3  | T4OUTPS2 | T4OUTPS1 | T4OUTPS0 | TMR4ON | T4CKPS1 | T4CKPS0 | 93                          |

| PR4    | Timer4 Period Register |           |          |          |          |        | 93      |         |                             |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the Timer4 module.

### REGISTER 17-16: ALRMWD: ALARM WEEKDAY VALUE REGISTER (ACCESS F8Fh, PTR 01b)<sup>(1)</sup>

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-x | R/W-x | R/W-x |

|-------|-----|-----|-----|-----|-------|-------|-------|

| —     | —   | —   | —   | —   | WDAY2 | WDAY1 | WDAY0 |

| bit 7 |     |     |     |     |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-3 Unimplemented: Read as '0'

bit 2-0 **WDAY<2:0>:** Binary Coded Decimal Value of Weekday Digit bits Contains a value from 0 to 6.

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

### REGISTER 17-17: ALRMHR: ALARM HOURS VALUE REGISTER (ACCESS F8Eh, PTR 01b)<sup>(1)</sup>

| U-0   | U-0 | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | _   | HRTEN1 | HRTEN0 | HRONE3 | HRONE2 | HRONE1 | HRONE0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7-6 | Unimplemented: Read as '0'                                                                                  |

|---------|-------------------------------------------------------------------------------------------------------------|

| bit 5-4 | <b>HRTEN&lt;1:0&gt;:</b> Binary Coded Decimal Value of Hour's Tens Digit bits Contains a value from 0 to 2. |

| bit 3-0 | <b>HRONE3:HRONE0:</b> Binary Coded Decimal Value of Hour's Ones Digit bits Contains a value from 0 to 9.    |

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

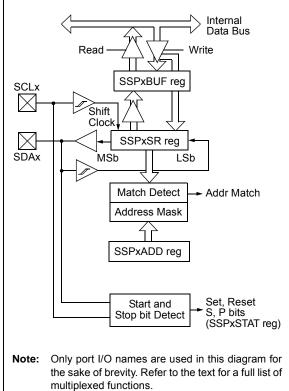

### 19.5 I<sup>2</sup>C Mode

The MSSP module in I<sup>2</sup>C mode fully implements all master and slave functions (including general call support), and provides interrupts on Start and Stop bits in hardware to determine a free bus (multi-master function). The MSSP module implements the standard mode specifications and 7-bit and 10-bit addressing.

Two pins are used for data transfer:

- Serial Clock (SCLx) RC3/SCK1/SCL1/RP14 or RD0/PMD0/SCL2

- Serial Data (SDAx) RC4/SDI1/SDA1/RP15 or RD1/PMD1/SDA2

The user must configure these pins as inputs by setting the associated TRIS bits.

#### FIGURE 19-7: MSSPx BLOCK DIAGRAM (I<sup>2</sup>C™ MODE)

#### 19.5.1 REGISTERS

The MSSP module has six registers for  $\mathsf{I}^2\mathsf{C}$  operation. These are:

- MSSPx Control Register 1 (SSPxCON1)

- MSSPx Control Register 2 (SSPxCON2)

- MSSPx Status Register (SSPxSTAT)

- Serial Receive/Transmit Buffer Register (SSPxBUF)

- MSSPx Shift Register (SSPxSR) Not directly accessible

- MSSPx Address Register (SSPxADD)

- MSSPx 7-Bit Address Mask Register (SSPxMSK)

SSPxCON1, SSPxCON2 and SSPxSTAT are the control and status registers in I<sup>2</sup>C mode operation. The SSPxCON1 and SSPxCON2 registers are readable and writable. The lower six bits of the SSPxSTAT are read-only. The upper two bits of the SSPxSTAT are read/write.

SSPxSR is the shift register used for shifting data in or out. SSPxBUF is the buffer register to which data bytes are written to or read from.

SSPxADD contains the slave device address when the MSSP is configured in I<sup>2</sup>C Slave mode. When the MSSP is configured in Master mode, the lower seven bits of SSPxADD act as the Baud Rate Generator (BRG) reload value.

SSPxMSK holds the slave address mask value when the module is configured for 7-Bit Address Masking mode. While it is a separate register, it shares the same SFR address as SSPxADD; it is only accessible when the SSPM<3:0> bits are specifically set to permit access. Additional details are provided in Section 19.5.3.4 "7-Bit Address Masking Mode".

In receive operations, SSPxSR and SSPxBUF together, create a double-buffered receiver. When SSPxSR receives a complete byte, it is transferred to SSPxBUF and the SSPxIF interrupt is set.

During transmission, the SSPxBUF is not double-buffered. A write to SSPxBUF will write to both SSPxBUF and SSPxSR.

# 25.4 Measuring Capacitance with the CTMU

There are two separate methods of measuring capacitance with the CTMU. The first is the absolute method, in which the actual capacitance value is desired. The second is the relative method, in which the actual capacitance is not needed, rather an indication of a change in capacitance is required.

#### 25.4.1 ABSOLUTE CAPACITANCE MEASUREMENT

For absolute capacitance measurements, both the current and capacitance calibration steps found in **Section 25.3 "Calibrating the CTMU Module"** should be followed. Capacitance measurements are then performed using the following steps:

- 1. Initialize the A/D Converter.

- 2. Initialize the CTMU.

- 3. Set EDG1STAT.

- 4. Wait for a fixed delay, *T*.

- 5. Clear EDG1STAT.

- 6. Perform an A/D conversion.

- 7. Calculate the total capacitance, CTOTAL = (I \* T)/V, where *I* is known from the current source measurement step (see **Section 25.3.1 "Current Source Calibration"**), *T* is a fixed delay and *V* is measured by performing an A/D conversion.

- 8. Subtract the stray and A/D capacitance (*C*OFFSET from **Section 25.3.2** "**Capacitance Calibration**") from *CTOTAL* to determine the measured capacitance.

#### 25.4.2 RELATIVE CHARGE MEASUREMENT

An application may not require precise capacitance measurements. For example, when detecting a valid press of a capacitance-based switch, detecting a relative change of capacitance is of interest. In this type of application, when the switch is open (or not touched), the total capacitance is the capacitance of the combination of the board traces, the A/D Converter, etc. A larger voltage will be measured by the A/D Converter. When the switch is closed (or is touched), the total capacitance is larger due to the addition of the capacitance of the human body to the above listed capacitances, and a smaller voltage will be measured by the A/D Converter.

Detecting capacitance changes is easily accomplished with the CTMU using these steps:

- 1. Initialize the A/D Converter and the CTMU.

- 2. Set EDG1STAT.

- 3. Wait for a fixed delay.

- 4. Clear EDG1STAT.

- 5. Perform an A/D conversion.

The voltage measured by performing the A/D conversion is an indication of the relative capacitance. Note that in this case, no calibration of the current source or circuit capacitance measurement is needed. See Example 25-4 for a sample software routine for a capacitive touch switch.

#### REGISTER 26-6: CONFIG3H: CONFIGURATION REGISTER 3 HIGH (BYTE ADDRESS 300005h)

| U-1   | U-1 | U-1 | U-1 | R/WO-1  | U-0 | U-0 | R/WO-1  |

|-------|-----|-----|-----|---------|-----|-----|---------|

|       |     |     | _   | MSSPMSK | —   | _   | IOL1WAY |

| bit 7 |     |     |     |         |     |     | bit 0   |

|       |     |     |     |         |     |     |         |

| Legend:             |                     |                        |                    |

|---------------------|---------------------|------------------------|--------------------|

| R = Readable bit    | WO = Write-Once bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at Reset | '1' = Bit is set    | '0' = Bit is cleared   | x = Bit is unknown |

| bit 7-4 | Unimplemented: Program the corresponding Flash Configuration bit to '1'                                                                                                                                                                                                                                                                  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3   | MSSPMSK: MSSP 7-Bit Address Masking Mode Enable bit                                                                                                                                                                                                                                                                                      |

|         | 1 = 7-Bit Address Masking mode enabled                                                                                                                                                                                                                                                                                                   |

|         | 0 = 5-Bit Address Masking mode enabled                                                                                                                                                                                                                                                                                                   |

| bit 2-1 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                               |

| bit 0   | IOL1WAY: IOLOCK One-Way Set Enable bit                                                                                                                                                                                                                                                                                                   |

|         | <ul> <li>1 = IOLOCK bit (PPSCON&lt;0&gt;) can be set once, provided the unlock sequence has been completed.<br/>Once set, the Peripheral Pin Select registers cannot be written to a second time.</li> <li>0 = IOLOCK bit (PPSCON&lt;0&gt;) can be set and cleared as needed, provided the unlock sequence has been completed</li> </ul> |

#### REGISTER 26-7: CONFIG4L: CONFIGURATION REGISTER 4 LOW (BYTE ADDRESS 300006h)

| R/WO-1 | R/WO-1 | R/WO-1               | R/WO-1               | R/WO-1 | R/WO-1 | R/WO-1 | R/WO-1 |

|--------|--------|----------------------|----------------------|--------|--------|--------|--------|

| WPCFG  | WPEND  | WPFP5 <sup>(2)</sup> | WPFP4 <sup>(3)</sup> | WPFP3  | WPFP2  | WPFP1  | WPFP0  |

| bit 7  |        |                      |                      |        |        |        | bit 0  |

| Legend:             |                     |                             |                    |

|---------------------|---------------------|-----------------------------|--------------------|

| R = Readable bit    | WO = Write-Once bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at Reset | '1' = Bit is set    | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7   | <ul> <li>WPCFG: Write/Erase Protect Configuration Region Select bit</li> <li>1 = Configuration Words page is not erase/write-protected, unless WPEND and WPFP&lt;5:0&gt; settings protect the Configuration Words page<sup>(1)</sup></li> <li>0 = Configuration Words page is erase/write-protected, regardless of WPEND and WPFP&lt;5:0&gt;<sup>(1)</sup></li> </ul> |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | WPEND: Write/Erase Protect Region Select bit<br>1 = Flash pages WPFP<5:0> through Configuration Words page are erase/write-protected<br>0 = Flash pages 0 through WPFP<5:0> are erase/write-protected                                                                                                                                                                 |

| bit 5-0 | <b>WPFP&lt;5:0&gt;:</b> Write/Erase Protect Page Start/End Location bits Used with WPEND bit to define which pages in Flash will be erase/write-protected.                                                                                                                                                                                                            |

| Note 1: | The "Configuration Words page" contains the FCWs and is the last page of implemented Flash memory on a given device. Each page consists of 1,024 bytes. For example, on a device with 64 Kbytes of Flash, the first page is 0 and the last page (Configuration Words page) is 63 (3Fh).                                                                               |

- 2: Not available on 32K and 16K devices.

- **3:** Not available on 16K devices.

| РОР                                      |        | Рор Тор о                                                             | Pop Top of Return Stack                                                                                                                                                                                                                                                                    |               |           |  |  |  |

|------------------------------------------|--------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----------|--|--|--|

| Synta                                    | ax:    | POP                                                                   | POP                                                                                                                                                                                                                                                                                        |               |           |  |  |  |

| Oper                                     | ands:  | None                                                                  | None                                                                                                                                                                                                                                                                                       |               |           |  |  |  |

| Operation:                               |        | $(TOS) \rightarrow b$                                                 | $(TOS) \rightarrow bit bucket$                                                                                                                                                                                                                                                             |               |           |  |  |  |

| Status Affected:                         |        | None                                                                  | None                                                                                                                                                                                                                                                                                       |               |           |  |  |  |

| Encoding:                                |        | 0000                                                                  | 0000                                                                                                                                                                                                                                                                                       | 000           | 0 0110    |  |  |  |

| Description:                             |        | stack and i<br>then becor<br>was pushe<br>This instru-<br>the user to | The TOS value is pulled off the return<br>stack and is discarded. The TOS value<br>then becomes the previous value that<br>was pushed onto the return stack.<br>This instruction is provided to enable<br>the user to properly manage the return<br>stack to incorporate a software stack. |               |           |  |  |  |

| Words:                                   |        | 1                                                                     |                                                                                                                                                                                                                                                                                            |               |           |  |  |  |

| Cycles:                                  |        | 1                                                                     |                                                                                                                                                                                                                                                                                            |               |           |  |  |  |

| Q Cycle Activity:                        |        |                                                                       |                                                                                                                                                                                                                                                                                            |               |           |  |  |  |

|                                          | Q1     | Q2                                                                    | Q3                                                                                                                                                                                                                                                                                         |               | Q4        |  |  |  |

|                                          | Decode | No                                                                    | POP 1                                                                                                                                                                                                                                                                                      |               | No        |  |  |  |

|                                          |        | operation                                                             | valu                                                                                                                                                                                                                                                                                       | ie            | operation |  |  |  |

| <u>Exan</u>                              | nple:  | POP<br>GOTO                                                           | NEW                                                                                                                                                                                                                                                                                        |               |           |  |  |  |

| Before Instructio<br>TOS<br>Stack (1 lev |        | tion<br>level down)                                                   | = 0031A2h<br>= 014332h                                                                                                                                                                                                                                                                     |               |           |  |  |  |

| After Instruction<br>TOS<br>PC           |        | n                                                                     |                                                                                                                                                                                                                                                                                            | 014332<br>NEW | ?h        |  |  |  |

| PUSH             |                                              | Push Top o                                                                                | Push Top of Return Stack               |                                              |                                         |                              |  |

|------------------|----------------------------------------------|-------------------------------------------------------------------------------------------|----------------------------------------|----------------------------------------------|-----------------------------------------|------------------------------|--|

| Synta            | IX:                                          | PUSH                                                                                      |                                        |                                              |                                         |                              |  |

| Operands:        |                                              | None                                                                                      | None                                   |                                              |                                         |                              |  |

| Opera            | ation:                                       | $(PC + 2) \rightarrow$                                                                    | $(PC + 2) \rightarrow TOS$             |                                              |                                         |                              |  |

| Status Affected: |                                              | None                                                                                      | None                                   |                                              |                                         |                              |  |

| Encoding:        |                                              | 0000                                                                                      | 0000                                   | 000                                          | 0 0                                     | 101                          |  |

| Desci            | ription:                                     | The PC + 2<br>the return s<br>value is pus<br>This instruc<br>software sta<br>then pushin | tack. 1<br>shed d<br>tion al<br>ack by | The prev<br>own on t<br>lows imp<br>modifyir | ious TO<br>the stac<br>plemen<br>ng TOS | DS<br>ck.<br>ting a<br>s and |  |

| Words:           |                                              | 1                                                                                         |                                        |                                              |                                         |                              |  |

| Cycles:          |                                              | 1                                                                                         |                                        |                                              |                                         |                              |  |

| QCy              | cle Activity:                                |                                                                                           |                                        |                                              |                                         |                              |  |

| -                | Q1                                           | Q2                                                                                        | (                                      | 23                                           | Q                                       | 4                            |  |

|                  | Decode                                       | PUSH<br>PC + 2 onto<br>return stack                                                       | No<br>operation                        |                                              | No<br>opera                             | •                            |  |

|                  |                                              |                                                                                           |                                        |                                              |                                         |                              |  |

| Exam             | iple:                                        | PUSH                                                                                      |                                        |                                              |                                         |                              |  |

| <u>Exam</u><br>I | i <u>ple:</u><br>Before Instruc<br>TOS<br>PC |                                                                                           | =<br>=                                 | 345Ah<br>0124h                               |                                         |                              |  |

#### 29.4.2 TIMING CONDITIONS

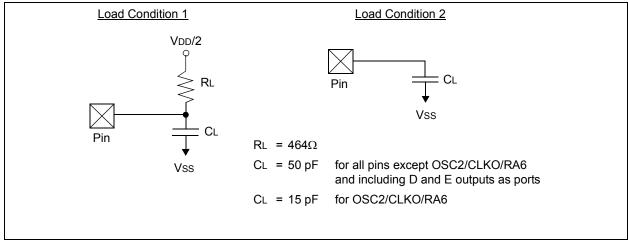

The temperature and voltages specified in Table 29-8 apply to all timing specifications unless otherwise noted. Figure 29-4 specifies the load conditions for the timing specifications.

#### TABLE 29-8: TEMPERATURE AND VOLTAGE SPECIFICATIONS – AC

|                    | Standard Operating Conditions (unless otherwise stated)                                   |

|--------------------|-------------------------------------------------------------------------------------------|

| AC CHARACTERISTICS | Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial               |

|                    | Operating voltage VDD range as described in <b>Section 29.1</b> and <b>Section 29.3</b> . |

#### FIGURE 29-4: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

#### 29.4.3 TIMING DIAGRAMS AND SPECIFICATIONS

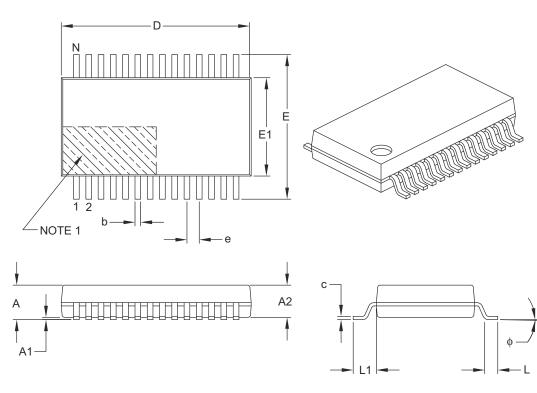

#### 28-Lead Plastic Shrink Small Outline (SS) – 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units    |          | MILLIMETERS | 6     |

|--------------------------|----------|----------|-------------|-------|

| Dimensior                | n Limits | MIN      | NOM         | MAX   |

| Number of Pins           | Ν        |          | 28          |       |

| Pitch                    | е        | 0.65 BSC |             |       |

| Overall Height           | Α        | -        | -           | 2.00  |

| Molded Package Thickness | A2       | 1.65     | 1.75        | 1.85  |

| Standoff                 | A1       | 0.05     | -           | -     |

| Overall Width            | E        | 7.40     | 7.80        | 8.20  |

| Molded Package Width     | E1       | 5.00     | 5.30        | 5.60  |

| Overall Length           | D        | 9.90     | 10.20       | 10.50 |

| Foot Length              | L        | 0.55     | 0.75        | 0.95  |

| Footprint                | L1       | 1.25 REF |             |       |

| Lead Thickness           | с        | 0.09     | -           | 0.25  |

| Foot Angle               | ¢        | 0°       | 4°          | 8°    |

| Lead Width               | b        | 0.22     | _           | 0.38  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-073B

| Automatic Baud Rate Calculation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Auto-Wake-up Bit (WUE) During Normal Operation 341                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Auto-Wake-up Bit (WUE) During Sleep                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Baud Rate Generator with Clock Arbitration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| BRG Overflow Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| BRG Reset Due to SDAx Arbitration During Start                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |