Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 48MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 34                                                                          |

| Program Memory Size        | 32KB (16K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | <u> </u>                                                                    |

| RAM Size                   | 3.8K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.15V ~ 3.6V                                                                |

| Data Converters            | A/D 13x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

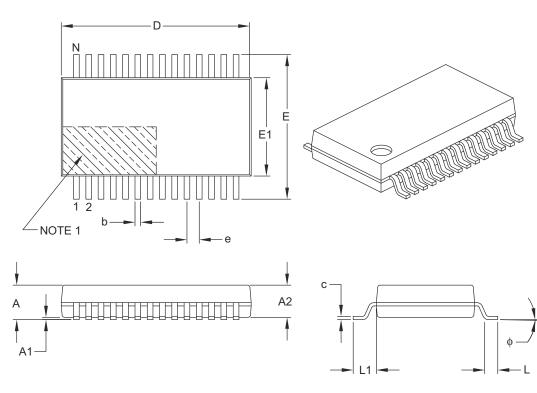

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-TQFP                                                                     |

| Supplier Device Package    | 44-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f45j11t-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                                | Pin N      | umber       | Pin    | Buffer |                                                  |  |  |  |

|--------------------------------|------------|-------------|--------|--------|--------------------------------------------------|--|--|--|

| Pin Name                       | 44-<br>QFN | 44-<br>TQFP |        |        | Description                                      |  |  |  |

|                                |            |             |        |        | PORTC (continued)                                |  |  |  |

| RC6/PMA5/TX1/CK1/RP17          | 44         | 44          |        |        |                                                  |  |  |  |

| RC6                            |            |             | I/O    | ST     | Digital I/O.                                     |  |  |  |

| PMA5                           |            |             | 0      | DIG    | Parallel Master Port address.                    |  |  |  |

| TX1                            |            |             | 0      | DIG    | EUSART1 asynchronous transmit.                   |  |  |  |

| CK1                            |            |             | I/O    | ST     | EUSART1 synchronous clock (see related RX1/DT1). |  |  |  |

| RP17                           |            |             | I/O    | DIG    | Remappable peripheral pin 17.                    |  |  |  |

| RC7/PMA4/RX1/DT1/RP18          | 1          | 1           |        |        |                                                  |  |  |  |

| RC7                            |            |             | I/O    | ST     | Digital I/O.                                     |  |  |  |

| PMA4                           |            |             | 0      | DIG    | Parallel Master Port address.                    |  |  |  |

| RX1                            |            |             | I      | ST     | EUSART1 asynchronous receive.                    |  |  |  |

| DT1                            |            |             | I/O    | ST     | EUSART1 synchronous data (see related TX1/CK1)   |  |  |  |

| RP18                           |            |             | I/O    | DIG    | Remappable peripheral pin 18.                    |  |  |  |

| Legend: TTL = TTL compatible i | nput       |             |        | (      | CMOS = CMOS compatible input or output           |  |  |  |

| ST = Schmitt Trigger i         | nput with  | n CMOS      | levels | A      | Analog = Analog input                            |  |  |  |

| I = Input                      |            |             |        | (      | O = Output                                       |  |  |  |

| P = Power                      |            |             |        | (      | DD = Open-Drain (no P diode to VDD)              |  |  |  |

| DIG = Digital output           |            |             |        |        |                                                  |  |  |  |

#### TABLE 1-4: PIC18F4XJ11 PINOUT I/O DESCRIPTIONS (CONTINUED)

Note 1: RA7 and RA6 will be disabled if OSC1 and OSC2 are used for the clock function.

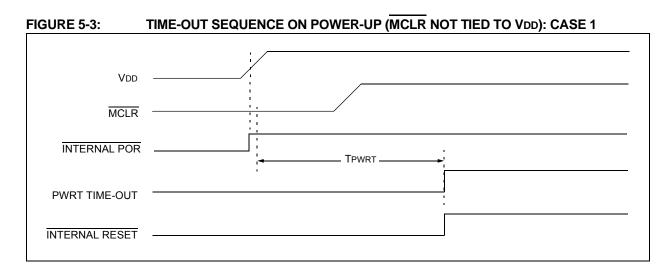

### FIGURE 5-4: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

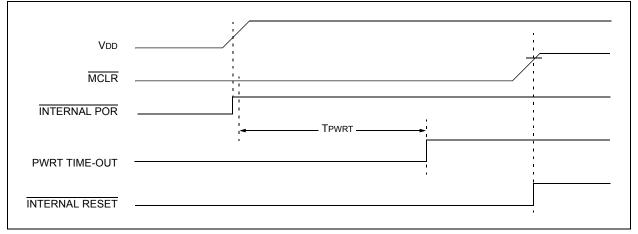

FIGURE 5-5:

#### SLOW RISE TIME (MCLR TIED TO VDD, VDD RISE > TPWRT)

NOTES:

#### 6.4 Data Addressing Modes

| Note: | The execution of some instructions in the  |  |  |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|--|--|

|       | core PIC18 instruction set is changed      |  |  |  |  |  |  |  |  |  |

|       | when the PIC18 extended instruction set is |  |  |  |  |  |  |  |  |  |

|       | enabled. See Section 6.6 "Data Memory      |  |  |  |  |  |  |  |  |  |

|       | and the Extended Instruction Set" for      |  |  |  |  |  |  |  |  |  |

|       | more information.                          |  |  |  |  |  |  |  |  |  |

While the program memory can be addressed in only one way, through the PC, information in the data memory space can be addressed in several ways. For most instructions, the addressing mode is fixed. Other instructions may use up to three modes, depending on which operands are used and whether or not the extended instruction set is enabled.

The addressing modes are:

- Inherent

- Literal

- Direct

- Indirect

An additional addressing mode, Indexed Literal Offset, is available when the extended instruction set is enabled (XINST Configuration bit = 1). Its operation is discussed in more detail in **Section 6.6.1 "Indexed Addressing with Literal Offset**".

## 6.4.1 INHERENT AND LITERAL ADDRESSING

Many PIC18 control instructions do not need any argument at all; they either perform an operation that globally affects the device, or they operate implicitly on one register. This addressing mode is known as Inherent Addressing. Examples include SLEEP, RESET and DAW.

Other instructions work in a similar way, but require an additional explicit argument in the opcode. This is known as Literal Addressing mode, because they require some literal value as an argument. Examples include ADDLW and MOVLW, which respectively, add or move a literal value to the W register. Other examples include CALL and GOTO, which include a 20-bit program memory address.

#### 6.4.2 DIRECT ADDRESSING

Direct Addressing specifies all or part of the source and/or destination address of the operation within the opcode itself. The options are specified by the arguments accompanying the instruction.

In the core PIC18 instruction set, bit-oriented and byte-oriented instructions use some version of Direct Addressing by default. All of these instructions include some 8-bit Literal Address as their LSB. This address specifies either a register address in one of the banks of data RAM (Section 6.3.3 "General Purpose

**Register File**"), or a location in the Access Bank (Section 6.3.2 "Access Bank") as the data source for the instruction.

The Access RAM bit, 'a', determines how the address is interpreted. When 'a' is '1', the contents of the BSR (Section 6.3.1 "Bank Select Register") are used with the address to determine the complete 12-bit address of the register. When 'a' is '0', the address is interpreted as being a register in the Access Bank. Addressing that uses the Access RAM is sometimes also known as Direct Forced Addressing mode.

A few instructions, such as MOVFF, include the entire 12-bit address (either source or destination) in their opcodes. In these cases, the BSR is ignored entirely.

The destination of the operation's results is determined by the destination bit, 'd'. When 'd' is '1', the results are stored back in the source register, overwriting its original contents. When 'd' is '0', the results are stored in the W register. Instructions without the 'd' argument have a destination that is implicit in the instruction; their destination is either the target register being operated on or the W register.

#### 6.4.3 INDIRECT ADDRESSING

Indirect Addressing allows the user to access a location in data memory without giving a fixed address in the instruction. This is done by using File Select Registers (FSRs) as pointers to the locations to be read or written to. Since the FSRs are themselves located in RAM as SFRs, they can also be directly manipulated under program control. This makes FSRs very useful in implementing data structures such as tables and arrays in data memory.

The registers for Indirect Addressing are also implemented with Indirect File Operands (INDFs) that permit automatic manipulation of the pointer value with auto-incrementing, auto-decrementing or offsetting with another value. This allows for efficient code using loops, such as the example of clearing an entire RAM bank in Example 6-5. It also enables users to perform Indexed Addressing and other Stack Pointer operations for program memory in data memory.

#### EXAMPLE 6-5: HOW TO CLEAR RAM (BANK 1) USING INDIRECT ADDRESSING

|         | LFSR  | FSR0, 0x100 | ; ( |                |

|---------|-------|-------------|-----|----------------|

| NEXT    | CLRF  | POSTINC0    | ;   | Clear INDF     |

|         |       |             | ;   | register then  |

|         |       |             | ;   | inc pointer    |

|         | BTFSS | FSROH, 1    | ;   | All done with  |

|         |       |             | ;   | Bank1?         |

|         | BRA   | NEXT        | ;   | NO, clear next |

| CONTINU | E     |             | ;   | YES, continue  |

|         |       |             |     |                |

| R/W-1        | R/W-1                                                                  | R/W-1                                   | R/W-1            | R/W-1             | R/W-1            | R/W-1           | R/W-1  |  |  |  |  |  |

|--------------|------------------------------------------------------------------------|-----------------------------------------|------------------|-------------------|------------------|-----------------|--------|--|--|--|--|--|

| SSP2IP       | BCL2IP                                                                 | RC2IP                                   | TX2IP            | TMR4IP            | CTMUIP           | TMR3GIP         | RTCCIP |  |  |  |  |  |

| bit 7        | •                                                                      | •                                       | ·                |                   | •                |                 | bit C  |  |  |  |  |  |

| <del></del>  |                                                                        |                                         |                  |                   |                  |                 |        |  |  |  |  |  |

| Legend:      |                                                                        |                                         |                  |                   |                  |                 |        |  |  |  |  |  |

| R = Readab   |                                                                        | W = Writable                            |                  |                   | nented bit, read |                 |        |  |  |  |  |  |

| -n = Value a | t POR                                                                  | '1' = Bit is set                        |                  | '0' = Bit is clea | ared             | x = Bit is unkn | own    |  |  |  |  |  |

| bit 7        | SSDOID, Ma                                                             | ster Synchronou                         | a Sorial Dort    | 2 Interrunt Drier | ity bit          |                 |        |  |  |  |  |  |

|              | 1 = High privations                                                    | ,                                       |                  |                   |                  |                 |        |  |  |  |  |  |

|              | 0 = Low price                                                          | •                                       |                  |                   |                  |                 |        |  |  |  |  |  |

| bit 6        | BCL2IP: Bus                                                            | s Collision Interr                      | upt Priority bit | (MSSP2 modu       | le)              |                 |        |  |  |  |  |  |

|              | 1 = High pri                                                           |                                         |                  | ,                 | ,                |                 |        |  |  |  |  |  |

|              | 0 = Low pric                                                           | ority                                   |                  |                   |                  |                 |        |  |  |  |  |  |

| bit 5        | RC2IP: EUSART2 Receive Interrupt Priority bit                          |                                         |                  |                   |                  |                 |        |  |  |  |  |  |

|              | 1 = High priority                                                      |                                         |                  |                   |                  |                 |        |  |  |  |  |  |

| 1.11.4       | 0 = Low price                                                          | •                                       |                  |                   |                  |                 |        |  |  |  |  |  |

| bit 4        |                                                                        | EUSART2 Transmit Interrupt Priority bit |                  |                   |                  |                 |        |  |  |  |  |  |

|              | 1 = High pri-0 = Low price                                             | •                                       |                  |                   |                  |                 |        |  |  |  |  |  |

| bit 3        |                                                                        | •                                       | rupt Priority b  | it                |                  |                 |        |  |  |  |  |  |

|              | <b>TMR4IE:</b> TMR4 to PR4 Interrupt Priority bit<br>1 = High priority |                                         |                  |                   |                  |                 |        |  |  |  |  |  |

|              | 0 = Low price                                                          | •                                       |                  |                   |                  |                 |        |  |  |  |  |  |

| bit 2        | CTMUIP: Ch                                                             | arge Time Mea                           | surement Unit    | (CTMU) Interru    | pt Priority bit  |                 |        |  |  |  |  |  |

|              | 1 = High priority                                                      |                                         |                  |                   |                  |                 |        |  |  |  |  |  |

|              | -                                                                      | 0 = Low priority                        |                  |                   |                  |                 |        |  |  |  |  |  |

| bit 1        |                                                                        | ïmer3 Gate Inte                         | rrupt Priority b | bit               |                  |                 |        |  |  |  |  |  |

|              | 1 = High pri-0 = Low price                                             |                                         |                  |                   |                  |                 |        |  |  |  |  |  |

| bit 0        | -                                                                      | CC Interrupt Pri                        | ority bit        |                   |                  |                 |        |  |  |  |  |  |

|              | 1 = High pri                                                           |                                         | only bit         |                   |                  |                 |        |  |  |  |  |  |

|              | 0 = Low price                                                          | •                                       |                  |                   |                  |                 |        |  |  |  |  |  |

#### REGISTER 9-12: IPR3: PERIPHERAL INTERRUPT PRIORITY REGISTER 3 (ACCESS FA5h)

#### REGISTER 10-21: RPOR0: PERIPHERAL PIN SELECT OUTPUT REGISTER 0 (BANKED EC6h)<sup>(1)</sup>

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-------|-------|-------|

| —     | _   |     | RP0R4 | RP0R3 | RP0R2 | RP0R1 | RP0R0 |

| bit 7 |     |     |       |       |       |       | bit 0 |

| Legend:           | $R/\overline{W}$ = Readable, Writable | $R/\overline{W}$ = Readable, Writable if IOLOCK = 0 |                    |  |  |  |  |  |  |

|-------------------|---------------------------------------|-----------------------------------------------------|--------------------|--|--|--|--|--|--|

| R = Readable bit  | W = Writable bit                      | /ritable bit U = Unimplemented bit, read as '0'     |                    |  |  |  |  |  |  |

| -n = Value at POR | '1' = Bit is set                      | '0' = Bit is cleared                                | x = Bit is unknown |  |  |  |  |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP0R<4:0>:** Peripheral Output Function is Assigned to RP0 Output Pin bits (see Table 10-14 for peripheral function numbers)

**Note 1:** Register values can be changed only if PPSCON<IOLOCK> = 0.

#### REGISTER 10-22: RPOR1: PERIPHERAL PIN SELECT OUTPUT REGISTER 1 (BANKED EC7h)

| U-0   | U-0 | U-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| —     | —   | — — R |       | RP1R3 | RP1R2 | RP1R1 | RP1R0 |

| bit 7 |     |       |       |       |       |       | bit 0 |

| Legend:           | $R/\overline{W}$ = Readable, Writable if IOLOCK = 0 |                                    |                    |  |  |  |  |  |

|-------------------|-----------------------------------------------------|------------------------------------|--------------------|--|--|--|--|--|

| R = Readable bit  | W = Writable bit                                    | U = Unimplemented bit, read as '0' |                    |  |  |  |  |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP1R<4:0>:** Peripheral Output Function is Assigned to RP1 Output Pin bits (see Table 10-14 for peripheral function numbers)

#### REGISTER 10-23: RPOR2: PERIPHERAL PIN SELECT OUTPUT REGISTER 2 (BANKED EC8h)

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-------|-------|-------|

| —     | _   |     | RP2R4 | RP2R3 | RP2R2 | RP2R1 | RP2R0 |

| bit 7 |     |     |       |       |       |       | bit 0 |

| Legend:           | $R/\overline{W}$ = Readable, Writable | $R/\overline{W}$ = Readable, Writable if IOLOCK = 0 |                    |  |  |  |  |  |  |

|-------------------|---------------------------------------|-----------------------------------------------------|--------------------|--|--|--|--|--|--|

| R = Readable bit  | W = Writable bit                      | U = Unimplemented bit, read as '0'                  |                    |  |  |  |  |  |  |

| -n = Value at POR | '1' = Bit is set                      | '0' = Bit is cleared                                | x = Bit is unknown |  |  |  |  |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP2R<4:0>:** Peripheral Output Function is Assigned to RP2 Output Pin bits (see Table 10-14 for peripheral function numbers)

### 11.1.2 DATA REGISTERS

The PMP module uses eight registers for transferring data into and out of the microcontroller. They are arranged as four pairs to allow the option of 16-bit data operations:

- PMDIN1H and PMDIN1L

- PMDIN2H and PMDIN2L

- PMADDRH/PMDOUT1H and PMADDRL/PMDOUT1L

- PMDOUT2H and PMDOUT2L

The PMDIN1 register is used for incoming data in Slave modes and both input and output data in Master modes. The PMDIN2 register is used for buffering input data in select Slave modes.

The PMADDR/PMDOUT1 registers are actually a single register pair; the name and function are dictated by the module's operating mode. In Master modes, the registers function as the PMADDRH and PMADDRL registers and contain the address of any incoming or outgoing data. In Slave modes, the registers function as PMDOUT1H and PMDOUT1L and are used for outgoing data.

PMADDRH differs from PMADDRL in that it can also have limited PMP control functions. When the module is operating in select Master mode configurations, the upper two bits of the register can be used to determine the operation of chip select signals. If these are not used, PMADDR simply functions to hold the upper 8 bits of the address. Register 11-9 provides the function of the individual bits in PMADDRH.

The PMDOUT2H and PMDOUT2L registers are only used in Buffered Slave modes and serve as a buffer for outgoing data.

#### 11.1.3 PAD CONFIGURATION CONTROL REGISTER

In addition to the module level configuration options, the PMP module can also be configured at the I/O pin for electrical operation. This option allows users to select either the normal Schmitt Trigger input buffer on digital I/O pins shared with the PMP, or use TTL level compatible buffers instead. Buffer configuration is controlled by the PMPTTL bit in the PADCFG1 register.

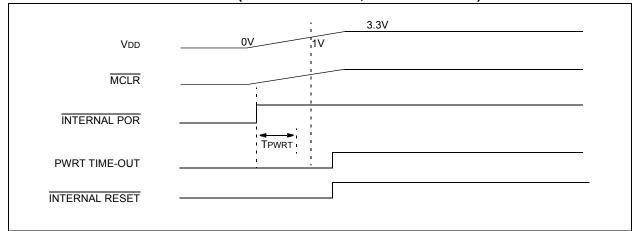

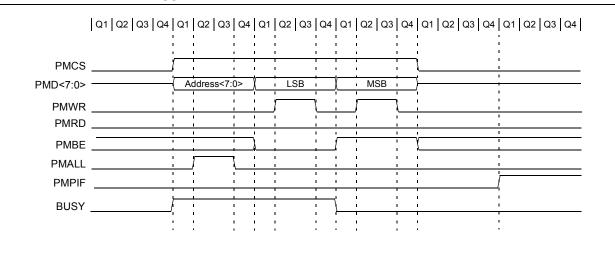

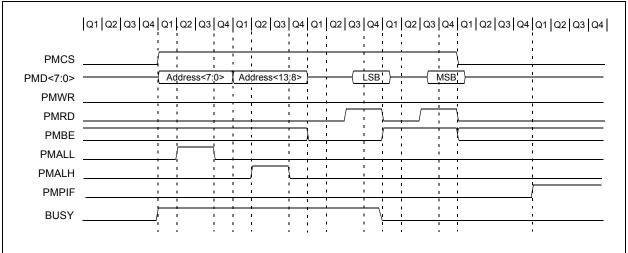

## FIGURE 11-24: WRITE TIMING, 16-BIT MULTIPLEXED DATA, PARTIALLY MULTIPLEXED ADDRESS

## FIGURE 11-25: READ TIMING, 16-BIT MULTIPLEXED DATA, FULLY MULTIPLEXED 16-BIT ADDRESS

#### FIGURE 11-26: WRITE TIMING, 16-BIT MULTIPLEXED DATA, FULLY MULTIPLEXED 16-BIT ADDRESS

|                  | Q1 Q2 Q3 Q4 | Q1 Q2 Q3         | Q4                                    | Q1   Q2   Q | 3 Q4 Q     | 1 Q2 Q3     | Q4 Q     | 1 Q2 Q3                  | Q4 Q1                      | Q2 Q3 Q4 | Q1 Q2 Q3 Q4    |

|------------------|-------------|------------------|---------------------------------------|-------------|------------|-------------|----------|--------------------------|----------------------------|----------|----------------|

| PMCS             | /           | Address<7:       |                                       | Address<    |            | LSB         |          | MSB                      | ;<br>;                     |          |                |

| PMD<7:0><br>PMWR |             | Auuress<7.       | <u>- 1</u>                            | Address<    | 13.0-2     |             | i A<br>İ |                          |                            |          |                |

| PMRD<br>PMBE     |             | ,<br>,<br>,<br>, |                                       |             |            |             |          | 1<br>1<br>1              | ι<br>ι<br>ι<br>ι<br>ι<br>γ |          | <br> <br> <br> |

| PMALL            | i<br>i      |                  |                                       |             | - A<br>    |             |          | 1<br>1<br>1              | 1 k<br>1 1<br>1 1          |          | I<br>I         |

| PMALH<br>PMPIF   |             |                  |                                       |             |            | 1<br>1<br>1 |          | 1<br>                    | 1 1<br>+ +                 |          | ·<br>•         |

| BUSY             |             |                  | · · · · · · · · · · · · · · · · · · · |             |            |             |          | - I<br>- I<br>- I<br>- I | 1 1<br>1 1<br>1 1<br>1 1   |          | /<br> <br>     |

|                  | i           | 1                |                                       | 1           | 1 I<br>1 I | 1           |          | 1                        |                            |          | 1              |

#### 12.3 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module. The prescaler is not directly readable or writable. Its value is set by the PSA and T0PS<2:0> bits (T0CON<3:0>), which determine the prescaler assignment and prescale ratio.

Clearing the PSA bit assigns the prescaler to the Timer0 module. When it is assigned, prescale values from 1:2 through 1:256 in power-of-2 increments are selectable.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF TMR0, MOVWF TMR0, BSF TMR0, etc.) clear the prescaler count.

| Note: | Writing to TMR0 when the prescaler is       |

|-------|---------------------------------------------|

|       | assigned to Timer0 will clear the prescaler |

|       | count but will not change the prescaler     |

|       | assignment.                                 |

#### 12.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control and can be changed "on-the-fly" during program execution.

#### 12.4 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h in 8-bit mode, or from FFFFh to 0000h in 16-bit mode. This overflow sets the TMR0IF flag bit. The interrupt can be masked by clearing the TMR0IE bit (INTCON<5>). Before re-enabling the interrupt, the TMR0IF bit must be cleared in software by the Interrupt Service Routine (ISR).

Since Timer0 is shut down in Sleep mode, the TMR0 interrupt cannot awaken the processor from Sleep.

| Name   | Bit 7                     | Bit 6                    | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0 | Reset<br>Values<br>on Page: |

|--------|---------------------------|--------------------------|--------|--------|-------|--------|--------|-------|-----------------------------|

| TMR0L  | Timer0 Reg                | Timer0 Register Low Byte |        |        |       |        |        | 91    |                             |

| TMR0H  | Timer0 Register High Byte |                          |        |        |       |        | 91     |       |                             |

| INTCON | GIE/GIEH                  | PEIE/GIEL                | TMR0IE | INT0IE | RBIE  | TMR0IF | INT0IF | RBIF  | 90                          |

| T0CON  | TMR0ON                    | T08BIT                   | TOCS   | T0SE   | PSA   | T0PS2  | T0PS1  | T0PS0 | 91                          |

TABLE 12-1:

REGISTERS ASSOCIATED WITH TIMER0

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by Timer0.

### REGISTER 17-11: HOURS: HOURS VALUE REGISTER (ACCESS F98h, PTR 01b)<sup>(1)</sup>

| U-0   | U-0 | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | HRTEN1 | HRTEN0 | HRONE3 | HRONE2 | HRONE1 | HRONE0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7-6 | Unimplemented: Read as '0'                                                                                  |

|---------|-------------------------------------------------------------------------------------------------------------|

| bit 5-4 | HRTEN<1:0>: Binary Coded Decimal Value of Hour's Tens Digit bits<br>Contains a value from 0 to 2.           |

| bit 3-0 | <b>HRONE&lt;3:0&gt;:</b> Binary Coded Decimal Value of Hour's Ones Digit bits Contains a value from 0 to 9. |

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

#### REGISTER 17-12: MINUTES: MINUTES VALUE REGISTER (ACCESS F99h, PTR 00b)

| U-0   | R/W-x   |

|-------|---------|---------|---------|---------|---------|---------|---------|

| —     | MINTEN2 | MINTEN1 | MINTEN0 | MINONE3 | MINONE2 | MINONE1 | MINONE0 |

| bit 7 |         |         |         |         |         |         | bit 0   |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7   | Unimplemented: Read as '0'                                                                                     |

|---------|----------------------------------------------------------------------------------------------------------------|

| bit 6-4 | <b>MINTEN&lt;2:0&gt;:</b> Binary Coded Decimal Value of Minute's Tens Digit bits Contains a value from 0 to 5. |

| bit 3-0 | MINONE<3:0>: Binary Coded Decimal Value of Minute's Ones Digit bits<br>Contains a value from 0 to 9.           |

#### REGISTER 17-13: SECONDS: SECONDS VALUE REGISTER (ACCESS F98h, PTR 00b)

| U-0   | R/W-x   |

|-------|---------|---------|---------|---------|---------|---------|---------|

| —     | SECTEN2 | SECTEN1 | SECTEN0 | SECONE3 | SECONE2 | SECONE1 | SECONE0 |

| bit 7 |         |         |         |         |         |         | bit 0   |

| Legend:    |                                                                                                                   |                     |                        |                    |

|------------|-------------------------------------------------------------------------------------------------------------------|---------------------|------------------------|--------------------|

| R = Reada  | ble bit                                                                                                           | W = Writable bit    | U = Unimplemented bit, | read as '0'        |

| -n = Value | at POR                                                                                                            | '1' = Bit is set    | '0' = Bit is cleared   | x = Bit is unknown |

| bit 7      | Unimple                                                                                                           | mented: Read as '0' |                        |                    |

| bit 6-4    | <b>SECTEN&lt;2:0&gt;:</b> Binary Coded Decimal Value of Second's Tens Digit bits<br>Contains a value from 0 to 5. |                     |                        |                    |

|            |                                                                                                                   |                     |                        |                    |

bit 3-0 SECONE<3:0>: Binary Coded Decimal Value of Second's Ones Digit bits Contains a value from 0 to 9. In addition to the expanded range of modes available through the CCPxCON and ECCPxAS registers, the ECCP modules have two additional registers associated with Enhanced PWM operation and auto-shutdown features. They are:

- ECCPxDEL (Enhanced PWM Control)

- PSTRxCON (Pulse Steering Control)

#### **18.1 ECCP Outputs and Configuration**

The Enhanced CCP module may have up to four PWM outputs, depending on the selected operating mode. These outputs, designated PxA through PxD, are routed through the Peripheral Pin Select (PPS) module. Therefore, individual functions may be mapped to any of the remappable I/O pins, RPn. The outputs that are active depend on the ECCP operating mode selected. The pin assignments are summarized in Table 18-4.

To configure the I/O pins as PWM outputs, the proper PWM mode must be selected by setting the PxM<1:0> and CCPxM<3:0> bits. The appropriate TRIS direction bits for the port pins must also be set as outputs and the output functions need to be assigned to I/O pins in the PPS module. (For details on configuring the module, see **Section 10.7 "Peripheral Pin Select (PPS)"**.)

#### 18.1.1 ECCP MODULE AND TIMER RESOURCES

The ECCP modules utilize Timers 1, 2, 3 or 4, depending on the mode selected. Timer1 and Timer3 are available to modules in Capture or Compare modes, while Timer2 and Timer4 are available for modules in PWM mode.

## TABLE 18-1:ECCP MODE – TIMER<br/>RESOURCE

| ECCP Mode | Timer Resource   |

|-----------|------------------|

| Capture   | Timer1 or Timer3 |

| Compare   | Timer1 or Timer3 |

| PWM       | Timer2 or Timer4 |

The assignment of a particular timer to a module is determined by the Timer-to-ECCP enable bits in the TCLKCON register (Register 13-3). The interactions between the two modules are depicted in Figure 18-1. Capture operations are designed to be used when the timer is configured for Synchronous Counter mode. Capture operations may not work as expected if the associated timer is configured for Asynchronous Counter mode.

#### 18.2 Capture Mode

In Capture mode, the CCPRxH:CCPRxL register pair captures the 16-bit value of the TMR1 or TMR3 registers when an event occurs on the corresponding ECCPx pin. An event is defined as one of the following:

- · Every falling edge

- · Every rising edge

- Every 4<sup>th</sup> rising edge

- Every 16<sup>th</sup> rising edge

The event is selected by the mode select bits, CCPxM<3:0>, of the CCPxCON register. When a capture is made, the interrupt request flag bit, CCPxIF, is set; it must be cleared by software. If another capture occurs before the value in register CCPRx is read, the old captured value is overwritten by the new captured value.

#### 18.2.1 ECCP PIN CONFIGURATION

In Capture mode, the appropriate ECCPx pin should be configured as an input by setting the corresponding TRIS direction bit.

Additionally, the ECCPx input function needs to be assigned to an I/O pin through the Peripheral Pin Select module. For details on setting up the remappable pins, see Section 10.7 "Peripheral Pin Select (PPS)".

| Note: | If the ECCPx pin is configured as an out-    |

|-------|----------------------------------------------|

|       | put, a write to the port can cause a capture |

|       | condition.                                   |

#### 18.2.2 TIMER1/TIMER3 MODE SELECTION

The timers that are to be used with the capture feature (Timer1 and/or Timer3) must be running in Timer mode or Synchronized Counter mode. In Asynchronous Counter mode, the capture operation may not work. The timer to be used with each ECCP module is selected in the TCLKCON register (Register 13-3).

#### 18.2.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCPxIE interrupt enable bit clear to avoid false interrupts. The interrupt flag bit, CCPxIF, should also be cleared following any such change in operating mode.

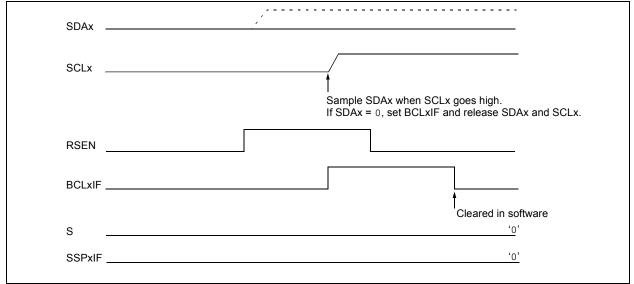

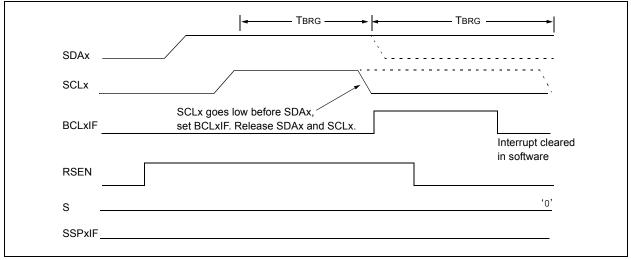

### 19.5.17.2 Bus Collision During a Repeated Start Condition

During a Repeated Start condition, a bus collision occurs if:

- a) A low level is sampled on SDAx when SCLx goes from a low level to a high level.

- SCLx goes low before SDAx is asserted low, indicating that another master is attempting to transmit a data '1'.

When the user deasserts SDAx and the pin is allowed to float high, the BRG is loaded with SSPxADD<6:0> and counts down to 0. The SCLx pin is then deasserted and when sampled high, the SDAx pin is sampled.

If SDAx is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0', see Figure 19-31). If SDAx is sampled high, the BRG is reloaded and begins counting. If SDAx goes from high-to-low before the BRG times out, no bus collision occurs because no two masters can assert SDAx at exactly the same time.

If SCLx goes from high-to-low before the BRG times out and SDAx has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated Start condition (see Figure 19-32).

If, at the end of the BRG time-out, both SCLx and SDAx are still high, the SDAx pin is driven low and the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCLx pin, the SCLx pin is driven low and the Repeated Start condition is complete.

FIGURE 19-31: BUS COLLISION DURING A REPEATED START CONDITION (CASE 1)

The ANCON0 and ANCON1 registers are used to configure the operation of the I/O pin associated with each analog channel. Setting any one of the PCFG bits configures the corresponding pin to operate as a digital only I/O. Clearing a bit configures the pin to operate as an analog input for either the A/D Converter or the comparator module; all digital peripherals are disabled and digital inputs read as '0'. As a rule, I/O pins that are multiplexed with analog inputs default to analog operation on device Resets.

In order to correctly perform A/D conversions on the VBG band gap reference (ADCON0<5:2> = 1111), the reference circuit must be powered on first. The VBGEN bit in the ANCON1 register allows the firmware to manually

request that the band gap reference circuit should be enabled. For best accuracy, firmware should allow a settling time of at least 10 ms prior to performing the first acquisition on this channel after enabling the band gap reference.

The reference circuit may already have been turned on if some other hardware module (such as comparators or HLVD) has already requested it. In this case, the initial turn-on settling time may have already elapsed and firmware does not need to wait as long before measuring VBG. Once the acquisition is complete, firmware may clear the VBGEN bit, which will save a small amount of power if no other modules are still requesting the VBG reference.

| REGISTER 21-3: | ANCON0: A/D PORT CONFIGURATION REGISTER 2 (BANKED F48h) |

|----------------|---------------------------------------------------------|

|----------------|---------------------------------------------------------|

| R/W-0                | R/W-0                | R/W-0                | R/W-0 | R/W-0        | R/W-0           | R/W-0  | R/W-0 |

|----------------------|----------------------|----------------------|-------|--------------|-----------------|--------|-------|

| PCFG7 <sup>(1)</sup> | PCFG6 <sup>(1)</sup> | PCFG5 <sup>(1)</sup> | PCFG4 | PCFG3        | PCFG2           | PCFG1  | PCFG0 |

| bit 7                |                      |                      |       |              |                 |        | bit 0 |

|                      |                      |                      |       |              |                 |        |       |

| Legend:              |                      |                      |       |              |                 |        |       |

| R = Readable         | bit                  | W = Writable I       | hit   | U = Unimplem | nented bit read | as '0' |       |

| -n = Value at POR | '1' = Bit is set   | '0' = Bit is cleared        | x = Bit is unknown |

|-------------------|--------------------|-----------------------------|--------------------|

| R = Readable bit  | vv = vvritable bit | U = Unimplemented bit, read | as '0'             |

bit 7-0 **PCFG<7:0>:** Analog Port Configuration bits (AN<7:0>) 1 = Pin configured as a digital port 0 = Pin configured as an analog channel – digital input disabled and reads '0'

**Note 1:** These bits are not implemented on 28-pin devices.

#### REGISTER 21-4: ANCON1: A/D PORT CONFIGURATION REGISTER 1 (BANKED F49h)

| R/W-0 | r | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0 | R/W-0 |

|-------|---|-----|--------|--------|--------|-------|-------|

| VBGEN | — | —   | PCFG12 | PCFG11 | PCFG10 | PCFG9 | PCFG8 |

| bit 7 |   |     |        |        |        |       | bit 0 |

| Legend:           | r = Reserved     |                       |                    |  |

|-------------------|------------------|-----------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |  |

| bit 7   | <b>VBGEN:</b> 1.2V Band Gap Reference Enable bit<br>1 = 1.2V band gap reference is powered on<br>0 = 1.2V band gap reference is turned off to save power (if no other modules are requesting it) |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | Reserved: Always maintain as '0' for lowest power consumption                                                                                                                                    |

| bit 5   | Unimplemented: Read as '0'                                                                                                                                                                       |

| bit 4-0 | PCFG<12:8>: Analog Port Configuration bits (AN<12:8>)                                                                                                                                            |

|         | <ul> <li>1 = Pin configured as a digital port</li> <li>0 = Pin configured as an analog channel – digital input disabled and reads '0'</li> </ul>                                                 |

#### 23.2 Voltage Reference Accuracy/Error

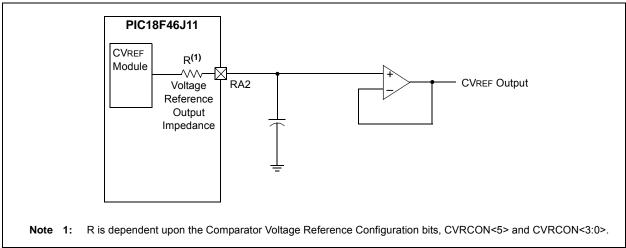

The full range of voltage reference cannot be realized due to the construction of the module. The transistors on the top and bottom of the resistor ladder network (see Figure 23-1) keep CVREF from approaching the reference source rails. The voltage reference is derived from the reference source; therefore, the CVREF output changes with fluctuations in that source. The tested absolute accuracy of the voltage reference can be found in **Section 29.0 "Electrical Characteristics"**.

#### 23.3 Connection Considerations

The voltage reference module operates independently of the comparator module. The output of the reference generator may be connected to the RA2 pin if the CVROE bit is set. Enabling the voltage reference output onto RA2 when it is configured as a digital input will increase current consumption. Connecting RA2 as a digital output with CVRSS enabled will also increase current consumption. The RA2 pin can be used as a simple D/A output with limited drive capability. Due to the limited current drive capability, a buffer must be used on the voltage reference output for external connections to VREF. See Figure 23-2 for an example buffering technique.

### 23.4 Operation During Sleep

When the device wakes up from Sleep through an interrupt or a Watchdog Timer time-out, the contents of the CVRCON register are not affected. To minimize current consumption in Sleep mode, the voltage reference should be disabled.

#### 23.5 Effects of a Reset

A device Reset disables the voltage reference by clearing bit, CVREN (CVRCON<7>). This Reset also disconnects the reference from the RA2 pin by clearing bit, CVROE (CVRCON<6>) and selects the high-voltage range by clearing bit, CVRR (CVRCON<5>). The CVR value select bits are also cleared.

| TABLE 23-1: REGISTERS ASSOCIATED WITH COMPARATOR VOLTAGE REFERENCE |

|--------------------------------------------------------------------|

|--------------------------------------------------------------------|

| Name   | Bit 7                | Bit 6                | Bit 5                | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on Page: |

|--------|----------------------|----------------------|----------------------|--------|--------|--------|--------|--------|-----------------------------|

| CVRCON | CVREN                | CVROE                | CVRR                 | CVRSS  | CVR3   | CVR2   | CVR1   | CVR0   | 74                          |

| CM1CON | CON                  | COE                  | CPOL                 | EVPOL1 | EVPOL0 | CREF   | CCH1   | CCH0   | 70                          |

| CM2CON | CON                  | COE                  | CPOL                 | EVPOL1 | EVPOL0 | CREF   | CCH1   | CCH0   | 70                          |

| TRISA  | TRISA7               | TRISA6               | TRISA5               | —      | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 72                          |

| ANCON0 | PCFG7 <sup>(1)</sup> | PCFG6 <sup>(1)</sup> | PCFG5 <sup>(1)</sup> | PCFG4  | PCFG3  | PCFG2  | PCFG1  | PCFG0  | 74                          |

| ANCON1 | VBGEN                | r                    | _                    | PCFG12 | PCFG11 | PCFG10 | PCFG9  | PCFG8  | 74                          |

**Legend:** — = unimplemented, read as '0', r = reserved. Shaded cells are not used with the comparator voltage reference.

Note 1: These bits are only available on 44-pin devices.

| BCF               | Bit Clear f                                                            |                                                                                                                                     |                                                                                      | BN                             |

|-------------------|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--------------------------------|

| Syntax:           | BCF f, b                                                               | {,a}                                                                                                                                |                                                                                      | Syntax:                        |

| Operands:         | $0 \leq f \leq 255$                                                    |                                                                                                                                     |                                                                                      | Operands                       |

|                   | 0 ≤ b ≤ 7<br>a ∈ [0,1]                                                 |                                                                                                                                     |                                                                                      | Operation                      |

| Operation:        | $0 \rightarrow f \le b >$                                              |                                                                                                                                     |                                                                                      | Status Affe                    |

| Status Affected:  | None                                                                   |                                                                                                                                     |                                                                                      | Encoding:                      |

| Encoding:         | 1001                                                                   | bbba ff:                                                                                                                            | ff ffff                                                                              | Descriptio                     |

| Description:      | Bit 'b' in reg                                                         | jister 'f' is clea                                                                                                                  | red.                                                                                 |                                |

|                   |                                                                        | he BSR is use                                                                                                                       | nk is selected.<br>d to select the                                                   |                                |

|                   | set is enabl<br>in Indexed I<br>mode when<br>Section 27<br>Bit-Oriente | nd the extended<br>ed, this instruc-<br>Literal Offset A<br>lever $f \le 95$ (5<br>.2.3 "Byte-Or<br>ed Instruction<br>set Mode" for | ction operates<br>Addressing<br>Fh). See<br><b>iented and</b><br><b>s in Indexed</b> | Words:<br>Cycles:<br>Q Cycle A |

| Words:            | 1                                                                      |                                                                                                                                     |                                                                                      | If Jump:                       |

| Cycles:           | 1                                                                      |                                                                                                                                     |                                                                                      | De                             |

| Q Cycle Activity: |                                                                        |                                                                                                                                     |                                                                                      |                                |

| Q1                | Q2                                                                     | Q3                                                                                                                                  | Q4                                                                                   |                                |

| Decode            | Read<br>register 'f'                                                   | Process<br>Data                                                                                                                     | Write<br>register 'f'                                                                | ope<br>If No Jum               |

|                   | register i                                                             | Data                                                                                                                                | register i                                                                           | ii No Suii                     |

| Example:          |                                                                        | LAG_REG,                                                                                                                            | 7, 0                                                                                 | De                             |

| Before Instruc    | tion<br>EG = C7h                                                       |                                                                                                                                     |                                                                                      |                                |

| After Instruction |                                                                        |                                                                                                                                     |                                                                                      | Example:                       |

| FLAG_R            | EG = 47h                                                               |                                                                                                                                     |                                                                                      | Befor                          |

|                   |                                                                        |                                                                                                                                     |                                                                                      | After                          |

| BN           |                                                              | Branch if N                                | legative                                                                                                 |                                      |

|--------------|--------------------------------------------------------------|--------------------------------------------|----------------------------------------------------------------------------------------------------------|--------------------------------------|

| Synta        | ax:                                                          | BN n                                       |                                                                                                          |                                      |

| Oper         | ands:                                                        | -128 ≤ n ≤ 1                               | 27                                                                                                       |                                      |

| Oper         | ation:                                                       | if Negative<br>(PC) + 2 + 2                |                                                                                                          |                                      |

| Statu        | s Affected:                                                  | None                                       |                                                                                                          |                                      |

| Enco         | ding:                                                        | 1110                                       | 0110 nnn                                                                                                 | in nnnn                              |

| Desc         | ription:                                                     | If the Negat<br>program wi                 | ive bit is '1', th<br>I branch.                                                                          | ien the                              |

|              |                                                              | added to th<br>have incren<br>instruction, | nplement numl<br>e PC. Since the<br>nented to fetch<br>the new addree<br>n. This instruct<br>istruction. | e PC will<br>the next<br>ess will be |

| Word         | ls:                                                          | 1                                          |                                                                                                          |                                      |

| Cycle        | es:                                                          | 1(2)                                       |                                                                                                          |                                      |

| Q C<br>If Ju | ycle Activity:<br>mp:                                        |                                            |                                                                                                          |                                      |

| i            | Q1                                                           | Q2                                         | Q3                                                                                                       | Q4                                   |

|              | Decode                                                       | Read literal<br>'n'                        | Process<br>Data                                                                                          | Write to<br>PC                       |

|              | No<br>operation                                              | No<br>operation                            | No<br>operation                                                                                          | No<br>operation                      |

| If No        | y Jump:                                                      |                                            |                                                                                                          |                                      |

|              | Q1                                                           | Q2                                         | Q3                                                                                                       | Q4                                   |

|              | Decode                                                       | Read literal                               | Process                                                                                                  | No                                   |

|              |                                                              | 'n'                                        | Data                                                                                                     | operation                            |

| <u>Exam</u>  | <u>nple:</u>                                                 | HERE                                       | BN Jump                                                                                                  |                                      |

|              | Before Instruc<br>PC<br>After Instructio<br>If Negativ<br>PC | = ade<br>on<br>ve = 1;                     | dress (HERE)                                                                                             |                                      |

|              | If Negativ<br>PC                                             | ve = 0;                                    | dress (HERE                                                                                              | + 2)                                 |

| SLEEP                                                               | Enter Sle                                                                                                                  | ep Mode              |                       |                |

|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------------|----------------|

| Syntax:                                                             | SLEEP                                                                                                                      |                      |                       |                |

| Operands:                                                           | None                                                                                                                       |                      |                       |                |

| Operation:                                                          | $\begin{array}{l} 00h \rightarrow WI \\ 0 \rightarrow WDT \\ 1 \rightarrow \overline{TO}, \\ 0 \rightarrow PD \end{array}$ | ,                    | er,                   |                |

| Status Affected:                                                    | TO, PD                                                                                                                     |                      |                       |                |

| Encoding:                                                           | 0000                                                                                                                       | 0000                 | 0000                  | 0011           |

| Description:                                                        | The Powe<br>cleared. T<br>is set. The<br>postscaler                                                                        | he Time-o<br>Watchdo | out statu<br>og Timer | s bit (TO)     |

|                                                                     | The proce with the os                                                                                                      | •                    |                       | eep mode       |

| Words:                                                              | 1                                                                                                                          |                      |                       |                |

| Cycles:                                                             | 1                                                                                                                          |                      |                       |                |

| Q Cycle Activity:                                                   |                                                                                                                            |                      |                       |                |

| Q1                                                                  | Q2                                                                                                                         | Q3                   |                       | Q4             |

| Decode                                                              | No<br>operation                                                                                                            | Proces<br>Data       |                       | Go to<br>Sleep |

| Example:                                                            | SLEEP                                                                                                                      |                      |                       |                |

| Before Instruct<br>TO =<br>PD =<br>After Instructio<br>TO =<br>PD = | ?<br>?<br>on<br>1 †                                                                                                        |                      |                       |                |

| + If WDT causes                                                     | 0<br>wake-up, this I                                                                                                       | oit is clea          | red.                  |                |

| SUBFWB                                                                                                                                                                                                                                  | Subtract f fi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | om W with Bo                                                                                                     | orrow                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| Syntax:                                                                                                                                                                                                                                 | SUBFWB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | f {,d {,a}}                                                                                                      |                                                         |

| Operands:                                                                                                                                                                                                                               | $0 \le f \le 255$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                  |                                                         |