Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 34                                                                         |

| Program Memory Size        | 64KB (32K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 3.8K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.15V ~ 3.6V                                                               |

| Data Converters            | A/D 13x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 44-QFN (8x8)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f46j11-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

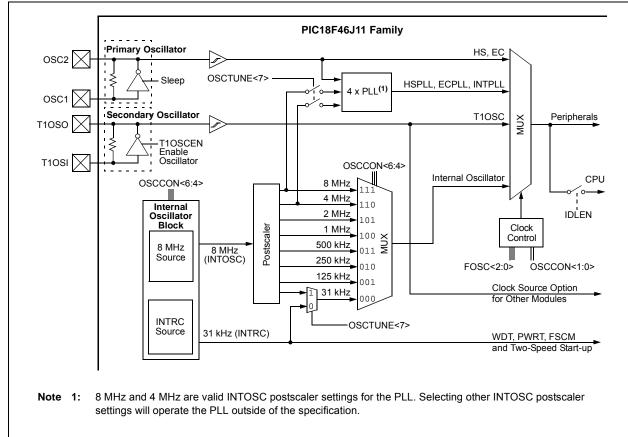

# 3.2.1 OSCILLATOR MODES

Figure 3-1 helps in understanding the oscillator structure of the PIC18F46J11 family of devices.

# FIGURE 3-1: PIC18F46J11 FAMILY CLOCK DIAGRAM

# 3.5 Effects of Power-Managed Modes on Various Clock Sources

When the PRI\_IDLE mode is selected, the designated primary oscillator continues to run without interruption. In secondary clock modes (SEC\_RUN and SEC\_IDLE), the Timer1 oscillator is operating and providing the device clock. The Timer1 oscillator may also run in all power-managed modes if required to clock Timer1 or Timer3.

In internal oscillator modes (RC RUN and RC IDLE), the internal oscillator block provides the device clock source. The 31 kHz INTRC output can be used directly to provide the clock and may be enabled to support various special features regardless of the power-managed mode (see Section 26.2 "Watchdog Timer (WDT)", Section 26.4 "Two-Speed Start-up" and Section 26.5 "Fail-Safe Clock Monitor" for more information on WDT, FSCM and Two-Speed Start-up). The INTOSC output at 8 MHz may be used directly to clock the device or may be divided down by the postscaler. The INTOSC output is disabled if the clock is provided directly from the INTRC output.

If Sleep mode is selected, all clock sources, which are no longer required, are stopped. Since all the transistor switching currents have been stopped, Sleep mode achieves the lowest current consumption of the device (only leakage currents) outside of Deep Sleep mode.

Enabling any on-chip feature that will operate during Sleep mode increases the current consumed during Sleep mode. The INTRC is required to support WDT operation. The Timer1 oscillator may be operating to support an RTC. Other features may be operating that do not require a device clock source (i.e., MSSP slave, PMP, INTx pins, etc.). Peripherals that may add significant current consumption are listed in **Section 29.2 "DC Characteristics: Power-Down and Supply Current PIC18F46J11 Family (Industrial)"**.

# 3.6 Power-up Delays

Power-up delays are controlled by two timers so that no external Reset circuitry is required for most applications. The delays ensure that the device is kept in Reset until the device power supply is stable under normal circumstances and the primary clock is operating and stable. For additional information on power-up delays, see **Section 5.6 "Power-up Timer (PWRT)**".

The first timer is the Power-up Timer (PWRT), which provides a fixed delay on power-up (parameter 33, Table 29-15).

The second timer is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable (HS mode). The OST does this by counting 1024 oscillator cycles before allowing the oscillator to clock the device.

There is a delay of interval, TCSD (parameter 38, Table 29-15), following POR, while the controller becomes ready to execute instructions. This delay runs concurrently with any other delays. This may be the only delay that occurs when any of the internal oscillator or EC modes are used as the primary clock source.

# PIC18F46J11 FAMILY

| TABLE 5-2:         INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED) |                    |             |                 |        |        |                                                                            |                                 |  |

|----------------------------------------------------------------------------|--------------------|-------------|-----------------|--------|--------|----------------------------------------------------------------------------|---------------------------------|--|

| Register                                                                   | Applicable Devices |             | Brown-out Reset |        |        | MCLR Resets<br>WDT Reset<br>RESET Instruction<br>Stack Resets<br>CM Resets | Wake-up via WDT<br>or Interrupt |  |

| RPINR8                                                                     | PIC18F2XJ11        | PIC18F4XJ11 | 1 1111          | 1 1111 | u uuuu |                                                                            |                                 |  |

| RPINR7                                                                     | PIC18F2XJ11        | PIC18F4XJ11 | 1 1111          | 1 1111 | u uuuu |                                                                            |                                 |  |

| RPINR6                                                                     | PIC18F2XJ11        | PIC18F4XJ11 | 1 1111          | 1 1111 | u uuuu |                                                                            |                                 |  |

| RPINR4                                                                     | PIC18F2XJ11        | PIC18F4XJ11 | 1 1111          | 1 1111 | u uuuu |                                                                            |                                 |  |

| RPINR3                                                                     | PIC18F2XJ11        | PIC18F4XJ11 | 1 1111          | 1 1111 | u uuuu |                                                                            |                                 |  |

| RPINR2                                                                     | PIC18F2XJ11        | PIC18F4XJ11 | 1 1111          | 1 1111 | u uuuu |                                                                            |                                 |  |

| RPINR1                                                                     | PIC18F2XJ11        | PIC18F4XJ11 | 1 1111          | 1 1111 | u uuuu |                                                                            |                                 |  |

| RPOR24                                                                     | —                  | PIC18F4XJ11 | 0 0000          | 0 0000 | u uuuu |                                                                            |                                 |  |

| RPOR23                                                                     | —                  | PIC18F4XJ11 | 0 0000          | 0 0000 | u uuuu |                                                                            |                                 |  |

| RPOR22                                                                     | —                  | PIC18F4XJ11 | 0 0000          | 0 0000 | u uuuu |                                                                            |                                 |  |

| RPOR21                                                                     | —                  | PIC18F4XJ11 | 0 0000          | 0 0000 | u uuuu |                                                                            |                                 |  |

| RPOR20                                                                     | _                  | PIC18F4XJ11 | 0 0000          | 0 0000 | u uuuu |                                                                            |                                 |  |

| RPOR19                                                                     |                    | PIC18F4XJ11 | 0 0000          | 0 0000 | u uuuu |                                                                            |                                 |  |

| RPOR18                                                                     | PIC18F2XJ11        | PIC18F4XJ11 | 0 0000          | 0 0000 | u uuuu |                                                                            |                                 |  |

| RPOR17                                                                     | PIC18F2XJ11        | PIC18F4XJ11 | 0 0000          | 0 0000 | u uuuu |                                                                            |                                 |  |

| RPOR16                                                                     | PIC18F2XJ11        | PIC18F4XJ11 | 0 0000          | 0 0000 | u uuuu |                                                                            |                                 |  |

| RPOR15                                                                     | PIC18F2XJ11        | PIC18F4XJ11 | 0 0000          | 0 0000 | u uuuu |                                                                            |                                 |  |

| RPOR14                                                                     | PIC18F2XJ11        | PIC18F4XJ11 | 0 0000          | 0 0000 | u uuuu |                                                                            |                                 |  |

| RPOR13                                                                     | PIC18F2XJ11        | PIC18F4XJ11 | 0 0000          | 0 0000 | u uuuu |                                                                            |                                 |  |

| RPOR12                                                                     | PIC18F2XJ11        | PIC18F4XJ11 | 0 0000          | 0 0000 | u uuuu |                                                                            |                                 |  |

| RPOR11                                                                     | PIC18F2XJ11        | PIC18F4XJ11 | 0 0000          | 0 0000 | u uuuu |                                                                            |                                 |  |

| RPOR10                                                                     | PIC18F2XJ11        | PIC18F4XJ11 | 0 0000          | 0 0000 | u uuuu |                                                                            |                                 |  |

| RPOR9                                                                      | PIC18F2XJ11        | PIC18F4XJ11 | 0 0000          | 0 0000 | u uuuu |                                                                            |                                 |  |

| RPOR8                                                                      | PIC18F2XJ11        | PIC18F4XJ11 | 0 0000          | 0 0000 | u uuuu |                                                                            |                                 |  |

| RPOR7                                                                      | PIC18F2XJ11        | PIC18F4XJ11 | 0 0000          | 0 0000 | u uuuu |                                                                            |                                 |  |

| RPOR6                                                                      | PIC18F2XJ11        | PIC18F4XJ11 | 0 0000          | 0 0000 | u uuuu |                                                                            |                                 |  |

| RPOR5                                                                      | PIC18F2XJ11        | PIC18F4XJ11 | 0 0000          | 0 0000 | u uuuu |                                                                            |                                 |  |

| RPOR4                                                                      | PIC18F2XJ11        | PIC18F4XJ11 | 0 0000          | 0 0000 | u uuuu |                                                                            |                                 |  |

| RPOR3                                                                      | PIC18F2XJ11        | PIC18F4XJ11 | 0 0000          | 0 0000 | u uuuu |                                                                            |                                 |  |

| RPOR2                                                                      | PIC18F2XJ11        | PIC18F4XJ11 | 0 0000          | 0 0000 | u uuuu |                                                                            |                                 |  |

| RPOR1                                                                      | PIC18F2XJ11        | PIC18F4XJ11 | 0 0000          | 0 0000 | u uuuu |                                                                            |                                 |  |

| RPOR0                                                                      | PIC18F2XJ11        | PIC18F4XJ11 | 0 0000          | 0 0000 | u uuuu |                                                                            |                                 |  |

# TABLE 5-2: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition.

**Note 1:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

- **2:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

- 3: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

- 4: See Table 5-1 for Reset value for specific condition.

- 5: Not implemented for PIC18F2XJ11 devices.

- 6: Not implemented on "LF" devices.

# 6.3.4 SPECIAL FUNCTION REGISTERS

The SFRs are registers used by the CPU and peripheral modules for controlling the desired operation of the device. These registers are implemented as static RAM. SFRs start at the top of data memory (FFFh) and extend downward to occupy more than the top half of Bank 15 (F40h to FFFh). Table 6-2 and Table 6-3 provide a list of these registers.

The SFRs can be classified into two sets: those associated with the "core" device functionality (ALU, Resets and interrupts) and those related to the peripheral functions. The Reset and Interrupt registers are described in their corresponding chapters, while the ALU's STATUS register is described later in this section. Registers related to the operation of the peripheral features are described in the chapter for that peripheral.

The SFRs are typically distributed among the peripherals whose functions they control. Unused SFR locations are unimplemented and read as '0's

Note: The SFRs located between EC0h and F5Fh are not part of the Access Bank. Either banked instructions (using BSR) or the MOVFF instruction should be used to access these locations. When programming in MPLAB<sup>®</sup> C18, the compiler will automatically use the appropriate addressing mode.

# TABLE 6-2: ACCESS BANK SPECIAL FUNCTION REGISTER MAP

| Address | Name                    | Address | Name                    | Address | Name     | Address | Name                 | Address | Name                     |

|---------|-------------------------|---------|-------------------------|---------|----------|---------|----------------------|---------|--------------------------|

| FFFh    | TOSU                    | FDFh    | INDF2 <sup>(1)</sup>    | FBFh    | PSTR1CON | F9Fh    | IPR1                 | F7Fh    | SPBRGH1                  |

| FFEh    | TOSH                    | FDEh    | POSTINC2 <sup>(1)</sup> | FBEh    | ECCP1AS  | F9Eh    | PIR1                 | F7Eh    | BAUDCON1                 |

| FFDh    | TOSL                    | FDDh    | POSTDEC2(1)             | FBDh    | ECCP1DEL | F9Dh    | PIE1                 | F7Dh    | SPBRGH2                  |

| FFCh    | STKPTR                  | FDCh    | PREINC2 <sup>(1)</sup>  | FBCh    | CCPR1H   | F9Ch    | RCSTA2               | F7Ch    | BAUDCON2                 |

| FFBh    | PCLATU                  | FDBh    | PLUSW2 <sup>(1)</sup>   | FBBh    | CCPR1L   | F9Bh    | OSCTUNE              | F7Bh    | TMR3H                    |

| FFAh    | PCLATH                  | FDAh    | FSR2H                   | FBAh    | CCP1CON  | F9Ah    | T1GCON               | F7Ah    | TMR3L                    |

| FF9h    | PCL                     | FD9h    | FSR2L                   | FB9h    | PSTR2CON | F99h    | RTCVALH              | F79h    | T3CON                    |

| FF8h    | TBLPTRU                 | FD8h    | STATUS                  | FB8h    | ECCP2AS  | F98h    | RTCVALL              | F78h    | TMR4                     |

| FF7h    | TBLPTRH                 | FD7h    | TMR0H                   | FB7h    | ECCP2DEL | F97h    | T3GCON               | F77h    | PR4                      |

| FF6h    | TBLPTRL                 | FD6h    | TMR0L                   | FB6h    | CCPR2H   | F96h    | TRISE                | F76h    | T4CON                    |

| FF5h    | TABLAT                  | FD5h    | T0CON                   | FB5h    | CCPR2L   | F95h    | TRISD                | F75h    | SSP2BUF                  |

| FF4h    | PRODH                   | FD4h    | (5)                     | FB4h    | CCP2CON  | F94h    | TRISC                | F74h    | SSP2ADD <sup>(3)</sup>   |

| FF3h    | PRODL                   | FD3h    | OSCCON                  | FB3h    | CTMUCONH | F93h    | TRISB                | F73h    | SSP2STAT                 |

| FF2h    | INTCON                  | FD2h    | CM1CON                  | FB2h    | CTMUCONL | F92h    | TRISA                | F72h    | SSP2CON1                 |

| FF1h    | INTCON2                 | FD1h    | CM2CON                  | FB1h    | CTMUICON | F91h    | ALRMCFG              | F71h    | SSP2CON2                 |

| FF0h    | INTCON3                 | FD0h    | RCON                    | FB0h    | SPBRG1   | F90h    | ALRMRPT              | F70h    | CMSTAT                   |

| FEFh    | INDF0 <sup>(1)</sup>    | FCFh    | TMR1H                   | FAFh    | RCREG1   | F8Fh    | ALRMVALH             | F6Fh    | PMADDRH <sup>(2,4)</sup> |

| FEEh    | POSTINC0 <sup>(1)</sup> | FCEh    | TMR1L                   | FAEh    | TXREG1   | F8Eh    | ALRMVALL             | F6Eh    | PMADDRL <sup>(2,4)</sup> |

| FEDh    | POSTDEC0 <sup>(1)</sup> | FCDh    | T1CON                   | FADh    | TXSTA1   | F8Dh    | LATE <sup>(2)</sup>  | F6Dh    | PMDIN1H <sup>(2)</sup>   |

| FECh    | PREINC0 <sup>(1)</sup>  | FCCh    | TMR2                    | FACh    | RCSTA1   | F8Ch    | LATD <sup>(2)</sup>  | F6Ch    | PMDIN1L <sup>(2)</sup>   |

| FEBh    | PLUSW0 <sup>(1)</sup>   | FCBh    | PR2                     | FABh    | SPBRG2   | F8Bh    | LATC                 | F6Bh    | TXADDRL                  |

| FEAh    | FSR0H                   | FCAh    | T2CON                   | FAAh    | RCREG2   | F8Ah    | LATB                 | F6Ah    | TXADDRH                  |

| FE9h    | FSR0L                   | FC9h    | SSP1BUF                 | FA9h    | TXREG2   | F89h    | LATA                 | F69h    | RXADDRL                  |

| FE8h    | WREG                    | FC8h    | SSP1ADD <sup>(3)</sup>  | FA8h    | TXSTA2   | F88h    | DMACON1              | F68h    | RXADDRH                  |

| FE7h    | INDF1 <sup>(1)</sup>    | FC7h    | SSP1STAT                | FA7h    | EECON2   | F87h    | (5)                  | F67h    | DMABCL                   |

| FE6h    | POSTINC1 <sup>(1)</sup> | FC6h    | SSP1CON1                | FA6h    | EECON1   | F86h    | DMACON2              | F66h    | DMABCH                   |

| FE5h    | POSTDEC1 <sup>(1)</sup> | FC5h    | SSP1CON2                | FA5h    | IPR3     | F85h    | HLVDCON              | F65h    | (5)                      |

| FE4h    | PREINC1 <sup>(1)</sup>  | FC4h    | ADRESH                  | FA4h    | PIR3     | F84h    | PORTE <sup>(2)</sup> | F64h    | (5)                      |

| FE3h    | PLUSW1 <sup>(1)</sup>   | FC3h    | ADRESL                  | FA3h    | PIE3     | F83h    | PORTD <sup>(2)</sup> | F63h    | (5)                      |

| FE2h    | FSR1H                   | FC2h    | ADCON0                  | FA2h    | IPR2     | F82h    | PORTC                | F62h    | (5)                      |

| FE1h    | FSR1L                   | FC1h    | ADCON1                  | FA1h    | PIR2     | F81h    | PORTB                | F61h    | (5)                      |

| FE0h    | BSR                     | FC0h    | WDTCON                  | FA0h    | PIE2     | F80h    | PORTA                | F60h    | (5)                      |

Note 1: This is not a physical register.

2: This register is not available on 28-pin devices.

3: SSPxADD and SSPxMSK share the same address.

4: PMADDRH and PMDOUTH share the same address and PMADDRL and PMDOUTL share the same address. PMADDRx is used in Master modes and PMDOUTx is used in Slave modes.

5: Reserved: Do not write to this location.

# PIC18F46J11 FAMILY

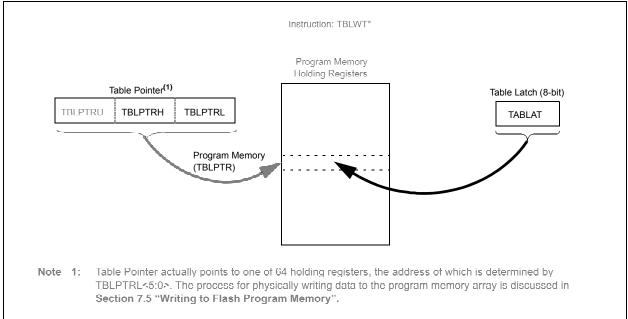

# FIGURE 7-2: TABLE WRITE OPERATION

# 7.2 Control Registers

Several control registers are used in conjunction with the TBLRD and TBLWT instructions. Those are:

- EECON1 register

- · EECON2 register

- TABLAT register

- TBLPTR registers

### 7.2.1 EECON1 AND EECON2 REGISTERS

The EECON1 register (Register 7-1) is the control register for memory accesses. The EECON2 register is not a physical register; it is used exclusively in the memory write and erase sequences. Reading EECON2 will read all '0's.

The WPROG bit, when set, will allow programming two bytes per word on the execution of the WR command. If this bit is cleared, the WR command will result in programming on a block of 64 bytes. The FREE bit, when set, will allow a program memory erase operation. When FREE is set, the erase operation is initiated on the next WR command. When FREE is clear, only writes are enabled.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. The WRERR bit is set in hardware when the WR bit is set, and cleared when the internal programming timer expires and the write operation is complete.

| Note: | During normal operation, the WRERR is       |

|-------|---------------------------------------------|

|       | read as '1'. This can indicate that a write |

|       | operation was prematurely terminated by     |

|       | a Reset, or a write operation was           |

|       | attempted improperly.                       |

The WR control bit initiates write operations. The bit cannot be cleared, only set, in software. It is cleared in hardware at the completion of the write operation.

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |     |     |       |       |       |       |       |

|----------------------------------------------------------------------|-----|-----|-------|-------|-------|-------|-------|

| Legend: $R/\overline{W}$ = Readable, Writable if IOLOCK = 0          |     |     |       |       |       |       |       |

| bit 7                                                                |     |     |       |       |       |       | bit 0 |

|                                                                      |     | _   | RP9R4 | RP9R3 | RP9R2 | RP9R1 | RP9R0 |

| U-0                                                                  | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

'0' = Bit is cleared

x = Bit is unknown

### REGISTER 10-30: RPOR9: PERIPHERAL PIN SELECT OUTPUT REGISTER 9 (BANKED ECFh)

bit 7-5 Unimplemented: Read as '0'

-n = Value at POR

bit 4-0 **RP9R<4:0>:** Peripheral Output Function is Assigned to RP9 Output Pin bits (see Table 10-14 for peripheral function numbers)

'1' = Bit is set

#### REGISTER 10-31: RPOR10: PERIPHERAL PIN SELECT OUTPUT REGISTER 10 (BANKED ED0h)

| U-0   | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-----|--------|--------|--------|--------|--------|

| —     | —   |     | RP10R4 | RP10R3 | RP10R2 | RP10R1 | RP10R0 |

| bit 7 |     |     |        |        |        |        | bit 0  |

| Legend:           | $R/\overline{W}$ = Readable, Writable if IOLOCK = 0 |                             |                    |

|-------------------|-----------------------------------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit                                    | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP10R<4:0>:** Peripheral Output Function is Assigned to RP10 Output Pin bits (see Table 10-14 for peripheral function numbers)

#### REGISTER 10-32: RPOR11: PERIPHERAL PIN SELECT OUTPUT REGISTER 11 (BANKED ED1h)

| U-0   | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-----|--------|--------|--------|--------|--------|

| —     | —   | —   | RP11R4 | RP11R3 | RP11R2 | RP11R1 | RP11R0 |

| bit 7 |     |     |        |        |        |        | bit 0  |

| Legend:           | $R/\overline{W}$ = Readable, Writable if IOLOCK = 0 |                             |                    |

|-------------------|-----------------------------------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit                                    | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared        | x = Bit is unknown |

### bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP11R<4:0>:** Peripheral Output Function is Assigned to RP11 Output Pin bits (see Table 10-14 for peripheral function numbers)

NOTES:

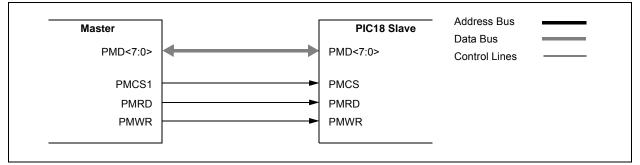

# 11.2 Slave Port Modes

The primary mode of operation for the module is configured using the MODE<1:0> bits in the PMMODEH register. The setting affects whether the module acts as a slave or a master, and it determines the usage of the control pins.

### 11.2.1 LEGACY MODE (PSP)

In Legacy mode (PMMODEH<1:0> = 00 and PMPEN = 1), the module is configured as a Parallel Slave Port (PSP) with the associated enabled module

pins dedicated to the module. In this mode, an external device, such as another microcontroller or microprocessor, can asynchronously read and write data using the 8-bit data bus (PMD<7:0>), the read (PMRD), write (PMWR) and chip select (PMCS1) inputs. It acts as a slave on the bus and responds to the read/write control signals.

Figure 11-2 displays the connection of the PSP. When chip select is active and a write strobe occurs (PMCS = 1 and PMWR = 1), the data from PMD<7:0> is captured into the PMDIN1L register.

### FIGURE 11-2: LEGACY PARALLEL SLAVE PORT EXAMPLE

# 13.0 TIMER1 MODULE

The Timer1 timer/counter module incorporates these features:

- Software selectable operation as a 16-bit timer or counter

- Readable and writable 8-bit registers (TMR1H and TMR1L)

- Selectable clock source (internal or external) with device clock or Timer1 oscillator internal options

- Interrupt-on-overflow

- Reset on ECCP Special Event Trigger

- Device clock status flag (T1RUN)

- · Timer with gated control

Figure 13-1 displays a simplified block diagram of the Timer1 module.

The module incorporates its own low-power oscillator to provide an additional clocking option. The Timer1 oscillator can also be used as a low-power clock source for the microcontroller in power-managed operation.

Timer1 is controlled through the T1CON Control register (Register 13-1). It also contains the Timer1 oscillator Enable bit (T1OSCEN). Timer1 can be enabled or disabled by setting or clearing control bit, TMR1ON (T1CON<0>).

The Fosc clock source (TMR1CS<1:0> = 01) should not be used with the ECCP capture/compare features. If the timer will be used with the capture or compare features, always select one of the other timer clocking options.

| R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0 | R/W-0  |

|---------|---------|---------|---------|---------|--------|-------|--------|

| TMR1CS1 | TMR1CS0 | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | RD16  | TMR10N |

| bit 7   |         |         |         |         |        |       | bit 0  |

# REGISTER 13-1: T1CON: TIMER1 CONTROL REGISTER (ACCESS FCDh)

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7-6 | TMR1CS<1:0>: Timer1 Clock Source Select bits                                                                                                               |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 10 = Timer1 clock source is T1OSC or T1CKI pin                                                                                                             |

|         | 01 = Timer1 clock source is system clock (Fosc) <sup>(1)</sup>                                                                                             |

|         | 00 = Timer1 clock source is instruction clock (Fosc/4)                                                                                                     |

| bit 5-4 | T1CKPS<1:0>: Timer1 Input Clock Prescale Select bits                                                                                                       |

|         | 11 = 1:8 Prescale value                                                                                                                                    |

|         | 10 = 1:4 Prescale value                                                                                                                                    |

|         | 01 = 1:2 Prescale value<br>00 = 1:1 Prescale value                                                                                                         |

| L:1 0   |                                                                                                                                                            |

| bit 3   | T10SCEN: Timer1 Crystal Oscillator Enable bit                                                                                                              |

|         | 1 = Timer1 oscillator circuit enabled                                                                                                                      |

|         | <ul> <li>0 = Timer1 oscillator circuit disabled</li> <li>The oscillator inverter and feedback resistor are turned off to eliminate power drain.</li> </ul> |

| h:1 0   |                                                                                                                                                            |

| bit 2   | T1SYNC: Timer1 External Clock Input Synchronization Select bit                                                                                             |

|         | $\frac{\text{TMR1CS}<1:0>=10:}{1-\text{De net evretered electric input}}$                                                                                  |

|         | <ul> <li>1 = Do not synchronize external clock input</li> <li>0 = Synchronize external clock input</li> </ul>                                              |

|         | TMR1CS<1:0> = $0x$ :                                                                                                                                       |

|         | This bit is ignored. Timer1 uses the internal clock when TMR1CS<1:0> = $0x$ .                                                                              |

| bit 1   | <b>RD16:</b> 16-Bit Read/Write Mode Enable bit                                                                                                             |

|         | 1 = Enables register read/write of Timer1 in one 16-bit operation                                                                                          |

|         | 0 = Enables register read/write of Timer1 in two 8-bit operations                                                                                          |

| bit 0   | TMR1ON: Timer1 On bit                                                                                                                                      |

| DILU    |                                                                                                                                                            |

|         | 1 = Enables Timer1                                                                                                                                         |

|         | 0 = Stops Timer1                                                                                                                                           |

| Note 1  | The Ease clock source should not be selected if the timer will be used with the ECCP capture/comp                                                          |

**Note 1:** The FOSC clock source should not be selected if the timer will be used with the ECCP capture/compare features.

# 13.1 Timer1 Gate Control Register

The Timer1 Gate Control register (T1GCON), displayed in Register 13-2, is used to control the Timer1 gate.

# REGISTER 13-2: T1GCON: TIMER1 GATE CONTROL REGISTER (F9Ah)<sup>(1)</sup>

| R/W-0         | R/W-0                          | R/W-0                               | R/W-0          | R/W-0                                                        | R-x            | R/W-0           | R/W-0         |

|---------------|--------------------------------|-------------------------------------|----------------|--------------------------------------------------------------|----------------|-----------------|---------------|

| TMR1GE        | T1GPOL                         | T1GTM                               | T1GSPM         | T1GGO/T1DONE                                                 | T1GVAL         | T1GSS1          | T1GSS0        |

| bit 7         |                                |                                     |                | • •                                                          |                | •               | bit 0         |

|               |                                |                                     |                |                                                              |                |                 |               |

| Legend:       |                                |                                     |                |                                                              |                | (0)             |               |

| R = Readable  |                                | W = Writable                        |                | U = Unimplemented                                            | d bit, read as |                 |               |

| -n = Value at | POR                            | '1' = Bit is set                    |                | '0' = Bit is cleared                                         |                | x = Bit is unkn | iown          |

| bit 7         | TMR1GE: Ti                     | mer1 Gate Ena                       | able bit       |                                                              |                |                 |               |

|               | If TMR1ON =<br>This bit is ign |                                     |                |                                                              |                |                 |               |

|               | If TMR1ON =                    |                                     |                |                                                              |                |                 |               |

|               |                                | ounting is cont                     |                | Timer1 gate function                                         |                |                 |               |

| bit 6         |                                | ner1 Gate Pola                      | -              |                                                              |                |                 |               |

|               | •                              |                                     | •              | ounts when gate is higunts when gate is low                  | •              |                 |               |

| bit 5         | T1GTM: Tim                     | er1 Gate Togg                       | e Mode bit     |                                                              |                |                 |               |

|               |                                | Gate Toggle mo                      |                |                                                              |                |                 |               |

|               |                                | Gate Toggle mo<br>flip-flop toggles |                | d and toggle flip-flop ng edge.                              | is cleared     |                 |               |

| bit 4         | T1GSPM: Tir                    | mer1 Gate Sin                       | gle Pulse Mo   | de bit                                                       |                |                 |               |

|               |                                | ate Single Pul<br>ate Single Pul    |                | nabled and is controll<br>sabled                             | ing Timer1 ga  | ate             |               |

| bit 3         | T1GGO/T1D                      | ONE: Timer1 (                       | Gate Single P  | ulse Acquisition State                                       | us bit         |                 |               |

|               | 0 = Timer1                     | ate single puls                     | se acquisition | is ready, waiting for a has completed or ha GSPM is cleared. |                | arted           |               |

| bit 2         | T1GVAL: Tin                    | ner1 Gate Curi                      | ent State bit  |                                                              |                |                 |               |

|               |                                | current state<br>Enable (TMR1       |                | gate that could be p                                         | provided to TI | MR1H:TMR1L;     | unaffected by |

| bit 1-0       | T1GSS<1:0>                     | : Timer1 Gate                       | Source Seleo   | ct bits                                                      |                |                 |               |

|               | 00 = Timer1                    | gate pin                            |                |                                                              |                |                 |               |

|               |                                | overflow outpu                      |                |                                                              |                |                 |               |

|               | 10 = TMR2 t                    | o match PR2 c                       | output         |                                                              |                |                 |               |

**Note 1:** Programming the T1GCON prior to T1CON is recommended.

| ECCP Mode            | PxM<1:0> | PxA                | PxB                | PxC                | PxD                |

|----------------------|----------|--------------------|--------------------|--------------------|--------------------|

| Single               | 00       | Yes <sup>(1)</sup> | Yes <sup>(1)</sup> | Yes <sup>(1)</sup> | Yes <sup>(1)</sup> |

| Half-Bridge          | 10       | Yes                | Yes                | No                 | No                 |

| Full-Bridge, Forward | 01       | Yes                | Yes                | Yes                | Yes                |

| Full-Bridge, Reverse | 11       | Yes                | Yes                | Yes                | Yes                |

### TABLE 18-4: EXAMPLE PIN ASSIGNMENTS FOR VARIOUS PWM ENHANCED MODES

Note 1: Outputs are enabled by pulse steering in Single mode (see Register 18-4).

# FIGURE 18-6: EXAMPLE PWM (ENHANCED MODE) OUTPUT RELATIONSHIPS (ACTIVE-HIGH STATE)

|    |                 |               |                      | Period               |             |

|----|-----------------|---------------|----------------------|----------------------|-------------|

| 00 | (Single Output) | PxA Modulated | Delay <sup>(1)</sup> | Delay <sup>(1)</sup> |             |

|    |                 | PxA Modulated |                      |                      |             |

| 10 | (Half-Bridge)   | PxB Modulated | i<br>i               |                      | i           |

|    |                 | PxA Active    | _ <u> </u>           | ·                    | <br>        |

| 01 | (Full-Bridge,   | PxB Inactive  | - ;                  | 1                    | 1<br>1<br>1 |

| 01 | Forward)        | PxC Inactive  | _ ;                  |                      |             |

|    |                 | PxD Modulated |                      |                      |             |

|    |                 | PxA Inactive  | _ ¦                  | 1<br>1               |             |

| 11 | (Full-Bridge,   | PxB Modulated |                      | į                    |             |

|    | Reverse)        | PxC Active    | :<br>- :             |                      | <br><br>I   |

|    |                 | PxD Inactive  |                      |                      |             |

Delay = 4 \* Tosc \* (ECCPxDEL<6:0>)

Note 1: Dead-band delay is programmed using the ECCPxDEL register (Section 18.5.6 "Programmable Dead-Band Delay Mode").

# 18.5.4 ENHANCED PWM AUTO-SHUTDOWN MODE

The PWM mode supports an Auto-Shutdown mode that will disable the PWM outputs when an external shutdown event occurs. Auto-Shutdown mode places the PWM output pins into a predetermined state. This mode is used to help prevent the PWM from damaging the application.

The auto-shutdown sources are selected using the ECCPxAS<2:0> bits of the ECCPAS register. A shutdown event may be generated by:

- A logic '0' on the pin that is assigned the FLT0 input function

- Comparator C1

- Comparator C2

- Setting the ECCPxASE bit in firmware

A shutdown condition is indicated by the ECCPxASE (Auto-Shutdown Event Status) bit of the ECCPxAS register. If the bit is a '0', the PWM pins are operating normally. If the bit is a '1', the PWM outputs are in the shutdown state.

When a shutdown event occurs, two things happen:

The ECCPxASE bit is set to '1'. The ECCPxASE will remain set until cleared in firmware or an auto-restart occurs (see **Section 18.5.5 "Auto-Restart Mode"**).

The enabled PWM pins are asynchronously placed in their shutdown states. The PWM output pins are grouped into pairs [PxA/PxC] and [PxB/PxD]. The state of each pin pair is determined by the PSSxAC and PSSxBD bits of the ECCPxAS register. Each pin pair may be placed into one of three states:

- Drive logic '1'

- Drive logic '0'

- Tri-state (high-impedance)

#### REGISTER 18-2: ECCPxAS: ECCPx AUTO-SHUTDOWN CONTROL REGISTER (ACCESS FBEh/FB8h)

| R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|----------|----------|----------|----------|---------|---------|---------|---------|

| ECCPxASE | ECCPxAS2 | ECCPxAS1 | ECCPxAS0 | PSSxAC1 | PSSxAC0 | PSSxBD1 | PSSxBD0 |

| bit 7    |          |          |          |         |         |         | bit 0   |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7   | ECCPxASE: ECCP Auto-Shutdown Event Status bit<br>1 = A shutdown event has occurred; ECCP outputs are in a shutdown state<br>0 = ECCP outputs are operating                                                                                                                                                                                                                                                                                           |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-4 | ECCPxAS<2:0>: ECCP Auto-Shutdown Source Select bits<br>000 = Auto-shutdown is disabled<br>001 = Comparator C1OUT output is high<br>010 = Comparator C2OUT output is high<br>011 = Either Comparator C1OUT or C2OUT is high<br>100 = VIL on FLT0 pin<br>101 = VIL on FLT0 pin or Comparator C1OUT output is high<br>110 = VIL on FLT0 pin or Comparator C2OUT output is high<br>111 = VIL on FLT0 pin or Comparator C1OUT or Comparator C2OUT is high |

| bit 3-2 | PSSxAC<1:0>: Pins PxA and PxC Shutdown State Control bits<br>00 = Drive pins PxA and PxC to '0'<br>01 = Drive pins PxA and PxC to '1'<br>10 = Pins PxA and PxC tri-state                                                                                                                                                                                                                                                                             |

| bit 1-0 | PSSxBD<1:0>: Pins PxB and PxD Shutdown State Control bits<br>00 = Drive pins PxB and PxD to '0'<br>01 = Drive pins PxB and PxD to '1'<br>10 = Pins PxB and PxD tri-state                                                                                                                                                                                                                                                                             |

| 2:      | The auto-shutdown condition is a level-based signal, not an edge-based signal. As long as the level is present, the auto-shutdown will persist.<br>Writing to the ECCPxASE bit is disabled while an auto-shutdown condition persists.<br>Once the auto-shutdown condition has been removed and the PWM restarted (either through firmware or auto-restart), the PWM signal will always restart at the beginning of the next PWM period.              |

| R/W-0        | R/W-0                                       | R-0                | R-0                                 | R-0              | R-0                  | R-0               | R-0      |

|--------------|---------------------------------------------|--------------------|-------------------------------------|------------------|----------------------|-------------------|----------|

| SMP          | CKE                                         | D/A                | P <sup>(1)</sup>                    | S <sup>(1)</sup> | R/W <sup>(2,3)</sup> | UA                | BF       |

| bit 7        |                                             | 1                  |                                     | ł                |                      |                   | bit      |

|              |                                             |                    |                                     |                  |                      |                   |          |

| Legend:      |                                             |                    |                                     |                  |                      |                   |          |

| R = Readat   | ole bit                                     | W = Writable       | bit                                 | U = Unimple      | mented bit, read     | as '0'            |          |

| -n = Value a | at POR                                      | '1' = Bit is se    | t                                   | '0' = Bit is cle | eared                | x = Bit is unkr   | iown     |

|              |                                             |                    |                                     |                  |                      |                   |          |

| bit 7        |                                             | ate Control bit    | :                                   |                  |                      |                   |          |

|              | In Master or S                              |                    |                                     |                  | (100 1.1.1           |                   |          |

|              |                                             |                    | led for Standar                     |                  | (100 kHz and 1       | MHZ)              |          |

| bit 6        | CKE: SMBus                                  |                    | led for riigh-sp                    |                  | ) KI IZ)             |                   |          |

|              | In Master or S                              |                    |                                     |                  |                      |                   |          |

|              |                                             | MBus specific      | inputs                              |                  |                      |                   |          |

|              |                                             | SMBus specific     |                                     |                  |                      |                   |          |

| bit 5        | D/A: Data/Ad                                | dress bit          |                                     |                  |                      |                   |          |

|              | In Master mo                                | <u>de:</u>         |                                     |                  |                      |                   |          |

|              | Reserved.                                   |                    |                                     |                  |                      |                   |          |

|              | In Slave mode                               |                    |                                     |                  |                      |                   |          |

|              |                                             |                    | yte received or                     |                  |                      |                   |          |

|              | 0 = Indicates<br>P: Stop bit <sup>(1)</sup> | that the last b    | yte received or                     | transmitted wa   | as address           |                   |          |

| bit 4        | •                                           | that a Otan hit    | bee been dete                       | ated leat        |                      |                   |          |

|              |                                             | vas not detecte    | has been dete                       | ected last       |                      |                   |          |

| bit 3        | S: Start bit <sup>(1)</sup>                 |                    |                                     |                  |                      |                   |          |

|              |                                             | that a Start bit   | has been dete                       | ected last       |                      |                   |          |

|              | 0 = Start bit w                             | vas not detecte    | ed last                             |                  |                      |                   |          |

| bit 2        | R/W: Read/W                                 | /rite Informatic   | n bit <sup>(2,3)</sup>              |                  |                      |                   |          |

|              | In Slave mode                               | <u>e:</u>          |                                     |                  |                      |                   |          |

|              | 1 = Read                                    |                    |                                     |                  |                      |                   |          |

|              | 0 = Write                                   |                    |                                     |                  |                      |                   |          |

|              | <u>In Master mo</u><br>1 = Transmit         |                    |                                     |                  |                      |                   |          |

|              |                                             | is not in progress | ess                                 |                  |                      |                   |          |

| bit 1        |                                             |                    | )-Bit Slave mod                     | le only)         |                      |                   |          |

|              | -                                           | -                  |                                     |                  | n the SSPxADD        | reaister          |          |

|              |                                             |                    | to be updated                       |                  |                      |                   |          |

| bit 0        | BF: Buffer Fu                               | Ill Status bit     |                                     |                  |                      |                   |          |

|              | <u>In Transmit m</u>                        | <u>node:</u>       |                                     |                  |                      |                   |          |

|              | 1 = SSPxBUF                                 |                    |                                     |                  |                      |                   |          |

|              | 0 = SSPxBUF                                 |                    |                                     |                  |                      |                   |          |

|              | In Receive me                               |                    | 4                                   |                  | L:4_ )               |                   |          |

|              |                                             |                    | not include the<br>es not include f |                  |                      |                   |          |

| Note 1:      | This bit is cleared                         |                    |                                     |                  | -                    |                   |          |

|              | This bit holds the                          |                    |                                     |                  | ss match. This h     | oit is only valid | from the |

| 6            | address match to                            | the next Start     | bit, Stop bit or                    | not ACK bit.     |                      |                   |          |

|              |                                             |                    |                                     |                  |                      |                   |          |

# REGISTER 19-5: SSPxSTAT: MSSPx STATUS REGISTER – I<sup>2</sup>C<sup>™</sup> MODE (ACCESS FC7h/F73h)

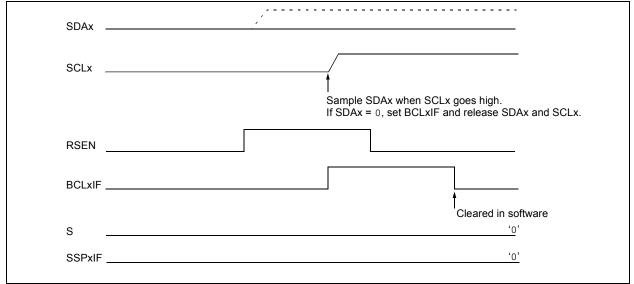

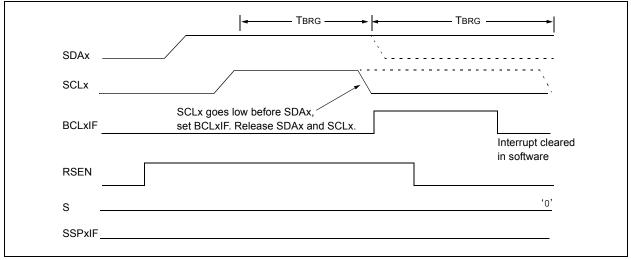

# 19.5.17.2 Bus Collision During a Repeated Start Condition

During a Repeated Start condition, a bus collision occurs if:

- a) A low level is sampled on SDAx when SCLx goes from a low level to a high level.

- b) SCLx goes low before SDAx is asserted low, indicating that another master is attempting to transmit a data '1'.

When the user deasserts SDAx and the pin is allowed to float high, the BRG is loaded with SSPxADD<6:0> and counts down to 0. The SCLx pin is then deasserted and when sampled high, the SDAx pin is sampled.

If SDAx is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0', see Figure 19-31). If SDAx is sampled high, the BRG is reloaded and begins counting. If SDAx goes from high-to-low before the BRG times out, no bus collision occurs because no two masters can assert SDAx at exactly the same time.

If SCLx goes from high-to-low before the BRG times out and SDAx has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated Start condition (see Figure 19-32).

If, at the end of the BRG time-out, both SCLx and SDAx are still high, the SDAx pin is driven low and the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCLx pin, the SCLx pin is driven low and the Repeated Start condition is complete.

FIGURE 19-31: BUS COLLISION DURING A REPEATED START CONDITION (CASE 1)

| Name     | Bit 7                                          | Bit 6        | Bit 5      | Bit 4       | Bit 3  | Bit 2  | Bit 1         | Bit 0  | Reset<br>Values<br>on Page: |

|----------|------------------------------------------------|--------------|------------|-------------|--------|--------|---------------|--------|-----------------------------|

| INTCON   | GIE/GIEH                                       | PEIE/GIEL    | TMR0IE     | INT0IE      | RBIE   | TMR0IF | <b>INT0IF</b> | RBIF   | 69                          |

| PIR1     | PMPIF <sup>(1)</sup>                           | ADIF         | RC1IF      | TX1IF       | SSP1IF | CCP1IF | TMR2IF        | TMR1IF | 72                          |

| PIE1     | PMPIE <sup>(1)</sup>                           | ADIE         | RC1IE      | TX1IE       | SSP1IE | CCP1IE | TMR2IE        | TMR1IE | 72                          |

| IPR1     | PMPIP <sup>(1)</sup>                           | ADIP         | RC1IP      | TX1IP       | SSP1IP | CCP1IP | TMR2IP        | TMR1IP | 72                          |

| PIR3     | SSP2IF                                         | BCL2IF       | RC2IF      | TX2IF       | TMR4IF | CTMUIF | TMR3GIF       | RTCCIF | 72                          |

| PIE3     | SSP2IE                                         | BCL2IE       | RC2IE      | TX2IE       | TMR4IE | CTMUIE | TMR3GIE       | RTCCIE | 72                          |

| IPR3     | SSP2IP                                         | BCL2IP       | RC2IP      | TX2IP       | TMR4IP | CTMUIP | TMR3GIP       | RTCCIP | 72                          |

| RCSTAx   | SPEN                                           | RX9          | SREN       | CREN        | ADDEN  | FERR   | OERR          | RX9D   | 72                          |

| TXREGx   | EUSARTx                                        | Transmit Reo | gister     |             |        |        |               |        | 72                          |

| TXSTAx   | CSRC                                           | TX9          | TXEN       | SYNC        | SENDB  | BRGH   | TRMT          | TX9D   | 72                          |

| BAUDCONx | ABDOVF                                         | RCIDL        | RXDTP      | TXCKP       | BRG16  | _      | WUE           | ABDEN  | 73                          |

| SPBRGHx  | EUSARTx Baud Rate Generator Register High Byte |              |            |             |        |        |               |        | 73                          |

| SPBRGx   | EUSARTx                                        | Baud Rate G  | enerator R | egister Low | Byte   |        |               |        | 72                          |

|          |                                                |              |            |             |        |        |               |        |                             |

#### TABLE 20-9: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

Legend: — = unimplemented, read as '0'. Shaded cells are not used for synchronous slave transmission.

Note 1: These pins are only available on 44-pin devices.

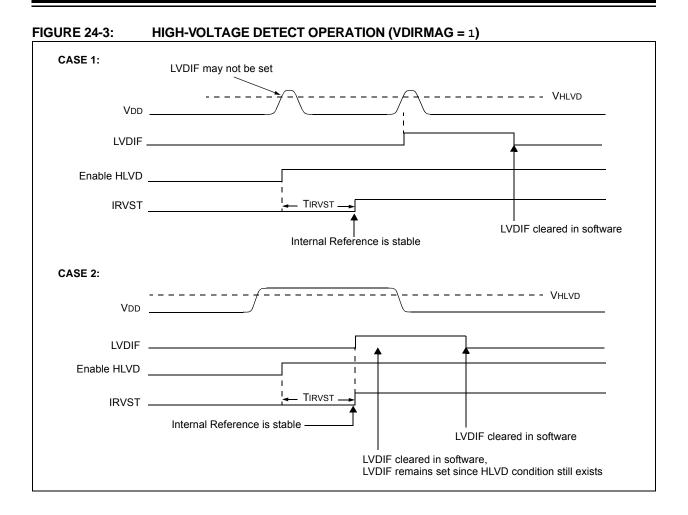

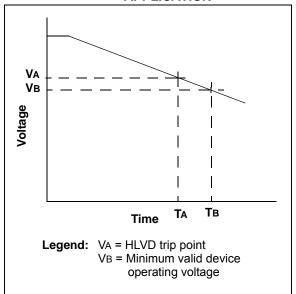

# 24.5 Applications

In many applications, it is desirable to have the ability to detect a drop below, or rise above, a particular threshold. For general battery applications, Figure 24-4 provides a possible voltage curve.

Over time, the device voltage decreases. When the device voltage reaches voltage, VA, the HLVD logic generates an interrupt at time, TA. The interrupt could cause the execution of an ISR, which would allow the application to perform "housekeeping tasks" and perform a controlled shutdown before the device voltage exits the valid operating range at TB.

The HLVD, thus, would give the application a time window, represented by the difference between TA and TB, to safely exit.

TYPICAL HIGH/ LOW-VOLTAGE DETECT APPLICATION

# PIC18F46J11 FAMILY

| CPFSGT                                          | Compare f with W, Skip if f > W                                                                                                                                                                                                                     | CPFSLT                                 | Compare f with W, Skip if f < W                                                     |                                                                   |                                      |  |

|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------|--------------------------------------|--|

| Syntax:                                         | CPFSGT f {,a}                                                                                                                                                                                                                                       | Syntax:                                | CPFSLT f {,a}                                                                       |                                                                   |                                      |  |

| Operands:                                       | 0 ≤ f ≤ 255<br>a ∈ [0,1]                                                                                                                                                                                                                            | Operands:                              | 0 ≤ f ≤ 255<br>a ∈ [0,1]                                                            |                                                                   |                                      |  |

| Operation:                                      | (f) – (W),<br>skip if (f) > (W)<br>(unsigned comparison)                                                                                                                                                                                            | Operation:                             | (f) - (W),<br>skip if (f) < (W)<br>(unsigned comparison)                            |                                                                   |                                      |  |

| Status Affected:                                | None                                                                                                                                                                                                                                                | Status Affected:                       | None                                                                                | mpunoony                                                          |                                      |  |

| Encoding:                                       | 0110 010a ffff ffff                                                                                                                                                                                                                                 | Encoding:                              |                                                                                     | )00a fff                                                          | f ffff                               |  |

| Description:                                    | Compares the contents of data mem-<br>ory location 'f' to the contents of the W<br>by performing an unsigned subtraction.                                                                                                                           | Description:                           | Compares th<br>ory location "<br>performing a                                       | e contents of<br>f' to the conte                                  | f data mem-<br>ents of W by          |  |

|                                                 | If the contents of 'f' are greater than the contents of WREG, then the fetched instruction is discarded and a NOP is executed instead, making this a two-cycle instruction.<br>If 'a' is '0', the Access Bank is selected.                          |                                        | If the content<br>contents of W<br>instruction is<br>executed insi<br>two-cycle ins | s of 'f' are le<br>V, then the fe<br>discarded ar<br>tead, making | ss than the<br>etched<br>nd a NOP is |  |

|                                                 | If 'a' is '1', the BSR is used to select the GPR bank (default).                                                                                                                                                                                    |                                        |                                                                                     | e BSR is used                                                     | ik is selected.<br>d to select the   |  |

|                                                 | If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See<br>Section 27.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed | Words:<br>Cycles:<br>Q Cycle Activity: | 1<br>1(2)<br><b>Note:</b> 3 cyc                                                     | ,                                                                 |                                      |  |

|                                                 | Literal Offset Mode" for details.                                                                                                                                                                                                                   | Q1                                     | Q2                                                                                  | Q3                                                                | Q4                                   |  |

| Words:<br>Cycles:                               | 1<br>1(2)                                                                                                                                                                                                                                           | Decode                                 | Read<br>register 'f'                                                                | Process<br>Data                                                   | No<br>operation                      |  |

|                                                 | <b>Note:</b> 3 cycles if skip and followed by a 2-word instruction.                                                                                                                                                                                 | lf skip:<br>Q1                         | Q2                                                                                  | Q3                                                                | Q4                                   |  |

| Q Cycle Activity:                               | 03 03 04                                                                                                                                                                                                                                            | No                                     | No                                                                                  | No                                                                | No                                   |  |

| Q1<br>Decode                                    | Q2 Q3 Q4<br>Read Process No                                                                                                                                                                                                                         | operation                              | operation                                                                           | operation                                                         | operation                            |  |

| Decode                                          | register 'f' Data operation                                                                                                                                                                                                                         | If skip and followe                    | -                                                                                   |                                                                   |                                      |  |

| lf skip:                                        |                                                                                                                                                                                                                                                     | Q1                                     | Q2                                                                                  | Q3                                                                | Q4                                   |  |

| Q1                                              | Q2 Q3 Q4                                                                                                                                                                                                                                            | No<br>operation                        | No<br>operation                                                                     | No<br>operation                                                   | No<br>operation                      |  |

| No<br>operation                                 | No No No<br>operation operation                                                                                                                                                                                                                     | No                                     | No                                                                                  | No                                                                | No                                   |  |

|                                                 | operation operation operation                                                                                                                                                                                                                       | operation                              | operation                                                                           | operation                                                         | operation                            |  |

| Q1                                              | Q2 Q3 Q4                                                                                                                                                                                                                                            |                                        |                                                                                     |                                                                   |                                      |  |

| No                                              | No No No                                                                                                                                                                                                                                            | Example:                               | HERE CI                                                                             | PFSLT REG,                                                        | 1                                    |  |

| operation                                       | operation operation operation                                                                                                                                                                                                                       |                                        | NLESS :                                                                             |                                                                   |                                      |  |

| No                                              | No No No                                                                                                                                                                                                                                            |                                        | LESS :                                                                              |                                                                   |                                      |  |