Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

EXF

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 48MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 16                                                                          |

| Program Memory Size        | 16KB (8K × 16)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 3.8K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                   |

| Data Converters            | A/D 10x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 28-QFN (6x6)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf24j11-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC18F46J11 FAMILY

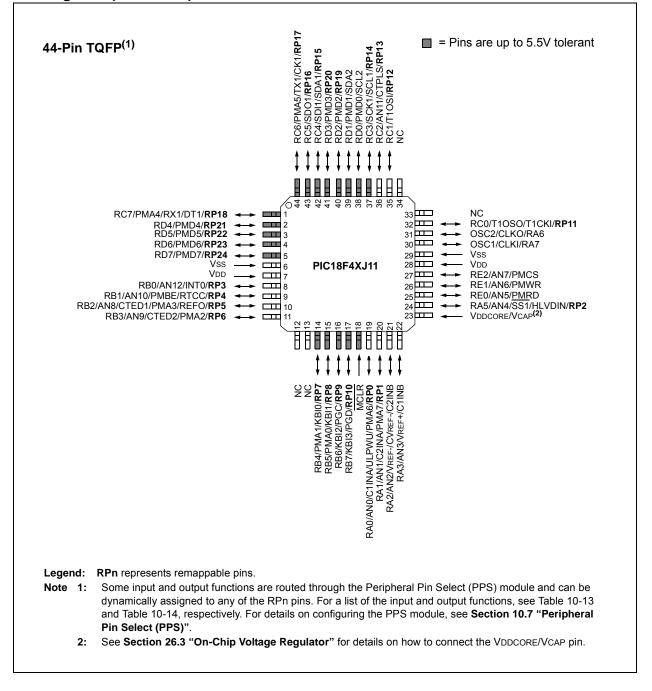

### **Pin Diagrams (Continued)**

| R/W-0                      |                                                                               |                                                    |               |                                                  |                  |                 |       |

|----------------------------|-------------------------------------------------------------------------------|----------------------------------------------------|---------------|--------------------------------------------------|------------------|-----------------|-------|

|                            | R/W-0                                                                         | R/W-0                                              | R/W-0         | R/W-0                                            | R/W-0            | R/W-0           | R/W-0 |

| INTSRC                     | PLLEN                                                                         | TUN5                                               | TUN4          | TUN3                                             | TUN2             | TUN1            | TUN0  |

| it 7                       |                                                                               |                                                    |               |                                                  |                  |                 | bit ( |

| .egend:                    |                                                                               |                                                    |               |                                                  |                  |                 |       |

| .egenu.<br>R = Readable bi | •                                                                             | W = Writable b                                     | <b>.</b> :+   |                                                  | aantad hit raad  |                 |       |

|                            |                                                                               |                                                    | JIL           | •                                                | nented bit, read |                 |       |

| n = Value at PC            | R                                                                             | '1' = Bit is set                                   |               | '0' = Bit is clea                                | ared             | x = Bit is unkn | own   |

| :                          | 1 = 31.25 kHz                                                                 | z device clock d                                   | erived from 8 | cy Source Sele<br>3 MHz INTOSC<br>rom INTRC inte | source (divide-  | by-256 enabled  | I)    |

| :                          | PLLEN: Frequency Multiplier Enable bit<br>1 = PLL enabled<br>0 = PLL disabled |                                                    |               |                                                  |                  |                 |       |

|                            | 011111 = Ma<br>011110<br>000001                                               | requency Tunin<br>ximum frequen<br>nter frequency; | су            | odule is running                                 | at the calibrate | ed frequency    |       |

#### REGISTER 3-1: OSCTUNE: OSCILLATOR TUNING REGISTER (ACCESS F9Bh)

#### 3.3 Clock Sources and Oscillator Switching

Like previous PIC18 enhanced devices, the PIC18F46J11 family includes a feature that allows the device clock source to be switched from the main oscillator to an alternate, low-frequency clock source. PIC18F46J11 family devices offer two alternate clock sources. When an alternate clock source is enabled, the various power-managed operating modes are available.

Essentially, there are three clock sources for these devices:

- Primary Oscillators

- · Secondary Oscillators

- Internal Oscillator Block

The **Primary Oscillators** include the External Crystal and Resonator modes, the External Clock modes and the internal oscillator block. The particular mode is defined by the FOSC<2:0> Configuration bits. The details of these modes are covered earlier in this chapter. The **Secondary Oscillators** are external sources that are not connected to the OSC1 or OSC2 pins. These sources may continue to operate even after the controller is placed in a power-managed mode.

PIC18F46J11 family devices offer the Timer1 oscillator as a secondary oscillator. This oscillator, in all power-managed modes, is often the time base for functions such as a Real-Time Clock (RTC). Most often, a 32.768 kHz watch crystal is connected between the RC0/T1OSO/T1CKI/RP11 and RC1/T1OSI/RP12 pins. Like the HS Oscillator mode circuits, loading capacitors are also connected from each pin to ground. The Timer1 oscillator is discussed in more detail in **Section 13.5 "Timer1 Oscillator"**.

In addition to being a primary clock source, the **postscaled internal clock** is available as a power-managed mode clock source. The INTRC source is also used as the clock source for several special features, such as the WDT and Fail-Safe Clock Monitor (FSCM).

#### 6.1.4.4 Stack Full and Underflow Resets

Device Resets on stack overflow and stack underflow conditions are enabled by setting the STVREN bit in Configuration register 1L. When STVREN is set, a full or underflow condition sets the appropriate STKFUL or STKUNF bit and then causes a device Reset. When STVREN is cleared, a full or underflow condition sets the appropriate STKFUL or STKUNF bit, but does not cause a device Reset. The STKFUL or STKUNF bits are cleared by the user software or a POR.

#### 6.1.5 FAST REGISTER STACK (FRS)

A Fast Register Stack (FRS) is provided for the STATUS, WREG and BSR registers to provide a "fast return" option for interrupts. This stack is only one level deep and is neither readable nor writable. It is loaded with the current value of the corresponding register when the processor vectors for an interrupt. All interrupt sources push values into the Stack registers. The values in the registers are then loaded back into the working registers if the RETFIE, FAST instruction is used to return from the interrupt.

If both low-priority and high-priority interrupts are enabled, the Stack registers cannot be used reliably to return from low-priority interrupts. If a high-priority interrupt occurs while servicing a low-priority interrupt, the Stack register values stored by the low-priority interrupt will be overwritten. In these cases, users must save the key registers in software during a low-priority interrupt.

If interrupt priority is not used, all interrupts may use the FRS for returns from interrupt. If no interrupts are used, the FRS can be used to restore the STATUS, WREG and BSR registers at the end of a subroutine call. To use the Fast Register Stack for a subroutine call, a CALL label, FAST instruction must be executed to save the STATUS, WREG and BSR registers to the Fast Register Stack. A RETURN, FAST instruction is then executed to restore these registers from the FRS.

Example 6-1 provides a source code example that uses the FRS during a subroutine call and return.

#### EXAMPLE 6-1: FAST REGISTER STACK CODE EXAMPLE

| CALL SUB1, FAST     | ;STATUS, WREG, BSR<br>;SAVED IN FAST REGISTER<br>;STACK |

|---------------------|---------------------------------------------------------|

| SUB1<br>RETURN FAST | ;RESTORE VALUES SAVED<br>;IN FAST REGISTER STACK        |

#### 6.1.6 LOOK-UP TABLES IN PROGRAM MEMORY

There may be programming situations that require the creation of data structures or look-up tables in program memory. For PIC18 devices, look-up tables can be implemented in two ways:

- Computed GOTO

- Table Reads

#### 6.1.6.1 Computed GOTO

A computed GOTO is accomplished by adding an offset to the PC. An example is shown in Example 6-2.

A look-up table can be formed with an ADDWF PCL instruction and a group of RETLW nn instructions. The W register is loaded with an offset into the table before executing a call to that table. The first instruction of the called routine is the ADDWF PCL instruction. The next executed instruction will be one of the RETLW nn instructions that returns the value 'nn' to the calling function.

The offset value (in WREG) specifies the number of bytes that the PC should advance and should be multiples of 2 (LSb = 0).

In this method, only one byte may be stored in each instruction location; room on the return address stack is required.

#### EXAMPLE 6-2: COMPUTED GOTO USING AN OFFSET VALUE

|       | MOVF  | OFFSET, W |

|-------|-------|-----------|

|       | CALL  | TABLE     |

| ORG   | nn00h |           |

| TABLE | ADDWF | PCL       |

|       | RETLW | nnh       |

|       | RETLW | nnh       |

|       | RETLW | nnh       |

|       |       |           |

|       |       |           |

|       |       |           |

|       |       |           |

#### 6.1.6.2 Table Reads

A better method of storing data in program memory allows two bytes to be stored in each instruction location.

Look-up table data may be stored two bytes per program word while programming. The Table Pointer (TBLPTR) specifies the byte address and the Table Latch (TABLAT) contains the data that is read from the program memory. Data is transferred from program memory one byte at a time.

Table read operation is discussed further inSection 7.1 "Table Reads and Table Writes".

# 6.2 PIC18 Instruction Cycle

#### 6.2.1 CLOCKING SCHEME

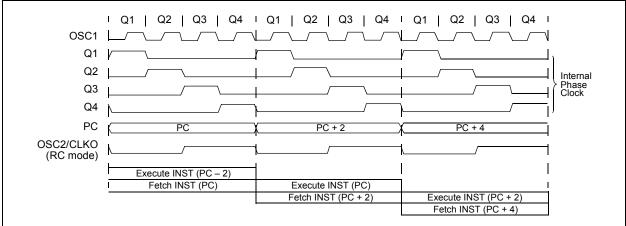

The microcontroller clock input, whether from an internal or external source, is internally divided by '4' to generate four non-overlapping quadrature clocks (Q1, Q2, Q3 and Q4). Internally, the PC is incremented on every Q1; the instruction is fetched from the program memory and latched into the Instruction Register (IR) during Q4. The instruction is decoded and executed during the following Q1 through Q4. Figure 6-4 illustrates the clocks and instruction execution flow.

### 6.2.2 INSTRUCTION FLOW/PIPELINING

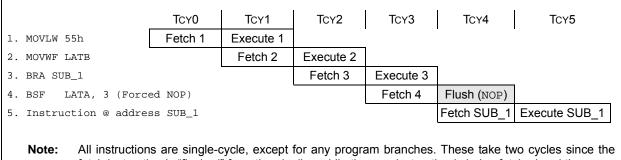

An "Instruction Cycle" consists of four Q cycles, Q1 through Q4. The instruction fetch and execute are pipelined in such a manner that a fetch takes one instruction cycle, while the decode and execute take another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the PC to change (e.g., GOTO), then two cycles are required to complete the instruction (Example 6-3).

A fetch cycle begins with the PC incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the IR in cycle Q1. This instruction is then decoded and executed during the Q2, Q3 and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

#### EXAMPLE 6-3: INSTRUCTION PIPELINE FLOW

**Note:** All instructions are single-cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline while the new instruction is being fetched and then executed.

#### FIGURE 6-4: CLOCK/INSTRUCTION CYCLE

## 6.3.2 ACCESS BANK

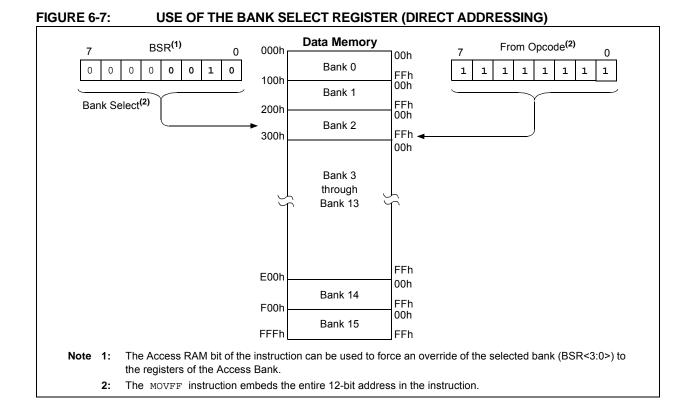

While the use of the BSR with an embedded 8-bit address allows users to address the entire range of data memory, it also means that the user must always ensure that the correct bank is selected. Otherwise, data may be read from or written to the wrong location. This can be disastrous if a GPR is the intended target of an operation, but an SFR is written to instead. Verifying and/or changing the BSR for each read or write to data memory can become very inefficient.

To streamline access for the most commonly used data memory locations, the data memory is configured with an Access Bank, which allows users to access a mapped block of memory without specifying a BSR. The Access Bank consists of the first 96 bytes of memory (00h-5Fh) in Bank 0 and the last 160 bytes of memory (60h-FFh) in Bank 15. The lower half is known as the Access RAM and is composed of GPRs. The upper half is where the device's SFRs are mapped. These two areas are mapped contiguously in the Access Bank and can be addressed in a linear fashion by an 8-bit address (Figure 6-6).

The Access Bank is used by core PIC18 instructions that include the Access RAM bit (the 'a' parameter in the instruction). When 'a' is equal to '1', the instruction uses the BSR and the 8-bit address included in the opcode for the data memory address. When 'a' is '0', however, the instruction is forced to use the Access Bank address map; the current value of the BSR is ignored entirely.

Using this "forced" addressing allows the instruction to operate on a data address in a single cycle without updating the BSR first. For 8-bit addresses of 60h and above, this means that users can evaluate and operate on SFRs more efficiently. The Access RAM below 60h is a good place for data values that the user might need to access rapidly, such as immediate computational results or common program variables. Access RAM also allows for faster and more code efficient context saving and switching of variables.

The mapping of the Access Bank is slightly different when the extended instruction set is enabled (XINST Configuration bit = 1). This is discussed in more detail in Section 6.6.3 "Mapping the Access Bank in Indexed Literal Offset Mode".

#### 6.3.3 GENERAL PURPOSE REGISTER FILE

PIC18 devices may have banked memory in the GPR area. This is data RAM, which is available for use by all instructions. GPRs start at the bottom of Bank 0 (address 000h) and grow upward toward the bottom of the SFR area. GPRs are not initialized by a POR and are unchanged on all other Resets.

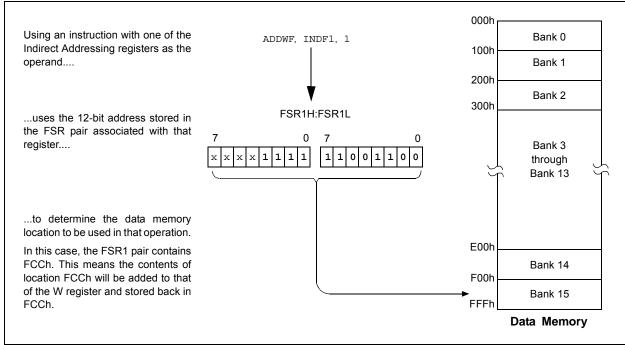

#### 6.4.3.1 FSR Registers and the INDF Operand (INDF)

At the core of Indirect Addressing are three sets of registers: FSR0, FSR1 and FSR2. Each represents a pair of 8-bit registers, FSRnH and FSRnL. The four upper bits of the FSRnH register are not used, so each FSR pair holds a 12-bit value. This represents a value that can address the entire range of the data memory in a linear fashion. The FSR register pairs, then, serve as pointers to data memory locations.

Indirect Addressing is accomplished with a set of INDF operands, INDF0 through INDF2. These can be presumed to be "virtual" registers: they are mapped in the

FIGURE 6-8: INDIRECT ADDRESSING

SFR space but are not physically implemented. Reading or writing to a particular INDF register actually accesses its corresponding FSR register pair. A read from INDF1, for example, reads the data at the address indicated by FSR1H:FSR1L. Instructions that use the INDF registers as operands actually use the contents of their corresponding FSR as a pointer to the instruction's target. The INDF operand is just a convenient way of using the pointer.

Because Indirect Addressing uses a full 12-bit address, data RAM banking is not necessary. Thus, the current contents of the BSR and the Access RAM bit have no effect on determining the target address.

### 10.2 PORTA, TRISA and LATA Registers

PORTA is a 7-bit wide, bidirectional port. It may function as a 5-bit port, depending on the oscillator mode selected. Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., put the contents of the output latch on the selected pin).

Reading the PORTA register reads the status of the pins, whereas writing to it, will write to the port latch.

The Data Latch (LATA) register is also memory mapped. Read-modify-write operations on the LATA register read and write the latched output value for PORTA.

The other PORTA pins are multiplexed with analog inputs, the analog VREF+ and VREF- inputs and the comparator voltage reference output. The operation of pins, RA<3:0> and RA5, as A/D converter inputs is selected by clearing or setting the control bits in the ANCON0 register (A/D Port Configuration Register 0).

Pins, RA0 and RA3, may also be used as comparator inputs by setting the appropriate bits in the CMCON register. To use RA<3:0> as digital inputs, it is also necessary to turn off the comparators.

Note: On a Power-on Reset (POR), RA5 and RA<3:0> are configured as analog inputs and read as '0'.

All PORTA pins have TTL input levels and full CMOS output drivers.

The TRISA register controls the direction of the PORTA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

#### EXAMPLE 10-2: INITIALIZING PORTA

| CLRF  | LATA   | ; | Initialize LATA        |

|-------|--------|---|------------------------|

|       |        | ; | to clear output        |

|       |        | ; | data latches           |

| MOVLB | 0x0F   | ; | ANCONx register not in |

|       |        | ; | Access Bank            |

| MOVLW | 0x0F   | ; | Configure A/D          |

| MOVWF | ANCON0 | ; | for digital inputs     |

| MOVLW | 0xCF   | ; | Value used to          |

|       |        | ; | initialize data        |

|       |        | ; | direction              |

| MOVWF | TRISA  | ; | Set RA<3:0> as inputs  |

|       |        | ; | RA<5:4> as outputs     |

|       |        |   |                        |

| Name                       | Bit 7                | Bit 6         | Bit 5      | Bit 4         | Bit 3       | Bit 2     | Bit 1     | Bit 0  | Reset<br>Values<br>on Page: |

|----------------------------|----------------------|---------------|------------|---------------|-------------|-----------|-----------|--------|-----------------------------|

| INTCON                     | GIE/GIEH             | PEIE/GIEL     | TMR0IE     | INT0IE        | RBIE        | TMR0IF    | INT0IF    | RBIF   | 69                          |

| PIR1                       | PMPIF <sup>(2)</sup> | ADIF          | RC1IF      | TX1IF         | SSP1IF      | CCP1IF    | TMR2IF    | TMR1IF | 72                          |

| PIE1                       | PMPIE <sup>(2)</sup> | ADIE          | RC1IE      | TX1IE         | SSP1IE      | CCP1IE    | TMR2IE    | TMR1IE | 72                          |

| IPR1                       | PMPIP <sup>(2)</sup> | ADIP          | RC1IP      | TX1IP         | SSP1IP      | CCP1IP    | TMR2IP    | TMR1IP | 72                          |

| PMCONH <sup>(2)</sup>      | PMPEN                | _             | _          | ADRMUX1       | ADRMUX0     | PTBEEN    | PTWREN    | PTRDEN | 73                          |

| PMCONL <sup>(2)</sup>      | CSF1                 | CSF0          | ALP        | _             | CS1P        | BEP       | WRSP      | RDSP   | 73                          |

| PMADDRH <sup>(1,2)</sup> / | _                    | CS1           | Parallel M | laster Port A | ddress High | Byte      |           |        | 73                          |

| PMDOUT1H <sup>(1,2)</sup>  | Parallel Po          | rt Out Data I | -ligh Byte | (Buffer 1)    |             |           |           |        | 73                          |

| PMADDRL <sup>(1,2)</sup> / | Parallel Ma          | ster Port Ad  | dress Low  | / Byte        |             |           |           |        | 73                          |

| PMDOUT1L <sup>(1,2)</sup>  | Parallel Po          | rt Out Data I | _ow Byte ( | Buffer 0)     |             |           |           |        | 73                          |

| PMDOUT2H <sup>(2)</sup>    | Parallel Po          | rt Out Data I | -ligh Byte | (Buffer 3)    |             |           |           |        | 73                          |

| PMDOUT2L <sup>(2)</sup>    | Parallel Po          | rt Out Data I | _ow Byte ( | Buffer 2)     |             |           |           |        | 73                          |

| PMDIN1H <sup>(2)</sup>     | Parallel Po          | rt In Data Hi | gh Byte (E | Buffer 1)     |             |           |           |        | 73                          |

| PMDIN1L <sup>(2)</sup>     | Parallel Po          | rt In Data Lo | w Byte (B  | uffer 0)      |             |           |           |        | 73                          |

| PMDIN2H <sup>(2)</sup>     | Parallel Po          | rt In Data Hi | gh Byte (E | Buffer 3)     |             |           |           |        | 73                          |

| PMDIN2L <sup>(2)</sup>     | Parallel Po          | rt In Data Lo | w Byte (B  | uffer 2)      |             |           |           |        | 73                          |

| PMMODEH <sup>(2)</sup>     | BUSY                 | IRQM1         | IRQM0      | INCM1         | INCM0       | MODE16    | MODE1     | MODE0  | 73                          |

| PMMODEL <sup>(2)</sup>     | WAITB1               | WAITB0        | WAITM3     | WAITM2        | WAITM1      | WAITM0    | WAITE1    | WAITE0 | 73                          |

| PMEH <sup>(2)</sup>        | —                    | PTEN14        | —          | —             | —           | —         | -         | —      | 74                          |

| PMEL <sup>(2)</sup>        | PTEN7                | PTEN6         | PTEN5      | PTEN4         | PTEN3       | PTEN2     | PTEN1     | PTEN0  | 74                          |

| PMSTATH <sup>(2)</sup>     | IBF                  | IBOV          | —          | —             | IB3F        | IB2F      | IB1F      | IB0F   | 74                          |

| PMSTATL <sup>(2)</sup>     | OBE                  | OBUF          | —          |               | OB3E        | OB2E      | OB1E      | OB0E   | 74                          |

| PADCFG1                    | —                    | —             | _          | _             | _           | RTSECSEL1 | RTSECSEL0 | PMPTTL | 74                          |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used during PMP operation.

**Note 1:** The PMADDRH/PMDOUT1H and PMADDRL/PMDOUT1L register pairs share the physical registers and addresses, but have different functions determined by the module's operating mode.

2: These bits and/or registers are only available in 44-pin devices.

# 13.2 Timer1 Operation

The Timer1 module is an 8-bit or 16-bit incrementing counter, which is accessed through the TMR1H:TMR1L register pair.

When used with an internal clock source, the module is a timer and increments on every instruction cycle. When used with an external clock source, the module can be used as either a timer or counter and increments on every selected edge of the external source.

Timer1 is enabled by configuring the TMR1ON and TMR1GE bits in the T1CON and T1GCON registers, respectively.

When Timer1 is enabled, the RC1/T1OSI/RP12 and RC0/T1OSO/T1CKI/RP11 pins become inputs. This means the values of TRISC<1:0> are ignored and the pins are read as '0'.

# 13.3 Clock Source Selection

The TMR1CS<1:0> and T1OSCEN bits of the T1CON register are used to select the clock source for Timer1. Register 13-1 displays the clock source selections.

When switching clock sources and using the clock prescaler, write to TMR1L afterwards to reset the internal prescaler count to 0.

# 13.3.1 INTERNAL CLOCK SOURCE

When the internal clock source is selected, the TMR1H:TMR1L register pair will increment on multiples of Fosc as determined by the Timer1 prescaler.

#### 13.3.2 EXTERNAL CLOCK SOURCE

When the external clock source is selected, the Timer1 module may work as a timer or a counter.

When enabled to count, Timer1 is incremented on the rising edge of the external clock input, T1CKI, or the capacitive sensing oscillator signal. Either of these external clock sources can be synchronized to the microcontroller system clock or they can run asynchronously.

When used as a timer with a clock oscillator, an external 32.768 kHz crystal can be used in conjunction with the dedicated internal oscillator circuit.

| Note: | In Counter mode, a falling edge must be<br>registered by the counter prior to the first<br>incrementing rising edge after any one or<br>more of the following conditions: |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>Timer1 enabled after POR Reset</li> <li>Write to TMR1H or TMR1L</li> <li>Timer1 is disabled</li> <li>Timer1 is disabled (TMR1ON = 0)</li> </ul>                  |

|       | when T1CKI is high, then Timer1 is<br>enabled (TMR1ON = 1) when T1CKI is<br>low.                                                                                          |

| TMR1CS1 | TMR1CS0 | T1OSCEN | Clock Source                          |

|---------|---------|---------|---------------------------------------|

| 0       | 1       | x       | Clock Source (Fosc)                   |

| 0       | 0       | x       | Instruction Clock (Fosc/4)            |

| 1       | 0       | 0       | External Clock on T1CKI Pin           |

| 1       | 0       | 1       | Oscillator Circuit on T1OSI/T1OSO Pin |

TABLE 13-1: TIMER1 CLOCK SOURCE SELECTION

In addition to the expanded range of modes available through the CCPxCON and ECCPxAS registers, the ECCP modules have two additional registers associated with Enhanced PWM operation and auto-shutdown features. They are:

- ECCPxDEL (Enhanced PWM Control)

- PSTRxCON (Pulse Steering Control)

# **18.1 ECCP Outputs and Configuration**

The Enhanced CCP module may have up to four PWM outputs, depending on the selected operating mode. These outputs, designated PxA through PxD, are routed through the Peripheral Pin Select (PPS) module. Therefore, individual functions may be mapped to any of the remappable I/O pins, RPn. The outputs that are active depend on the ECCP operating mode selected. The pin assignments are summarized in Table 18-4.

To configure the I/O pins as PWM outputs, the proper PWM mode must be selected by setting the PxM<1:0> and CCPxM<3:0> bits. The appropriate TRIS direction bits for the port pins must also be set as outputs and the output functions need to be assigned to I/O pins in the PPS module. (For details on configuring the module, see **Section 10.7 "Peripheral Pin Select (PPS)"**.)

#### 18.1.1 ECCP MODULE AND TIMER RESOURCES

The ECCP modules utilize Timers 1, 2, 3 or 4, depending on the mode selected. Timer1 and Timer3 are available to modules in Capture or Compare modes, while Timer2 and Timer4 are available for modules in PWM mode.

# TABLE 18-1:ECCP MODE – TIMER<br/>RESOURCE

| ECCP Mode | Timer Resource   |

|-----------|------------------|

| Capture   | Timer1 or Timer3 |

| Compare   | Timer1 or Timer3 |

| PWM       | Timer2 or Timer4 |

The assignment of a particular timer to a module is determined by the Timer-to-ECCP enable bits in the TCLKCON register (Register 13-3). The interactions between the two modules are depicted in Figure 18-1. Capture operations are designed to be used when the timer is configured for Synchronous Counter mode. Capture operations may not work as expected if the associated timer is configured for Asynchronous Counter mode.

### 18.2 Capture Mode

In Capture mode, the CCPRxH:CCPRxL register pair captures the 16-bit value of the TMR1 or TMR3 registers when an event occurs on the corresponding ECCPx pin. An event is defined as one of the following:

- Every falling edge

- · Every rising edge

- Every 4<sup>th</sup> rising edge

- Every 16<sup>th</sup> rising edge

The event is selected by the mode select bits, CCPxM<3:0>, of the CCPxCON register. When a capture is made, the interrupt request flag bit, CCPxIF, is set; it must be cleared by software. If another capture occurs before the value in register CCPRx is read, the old captured value is overwritten by the new captured value.

#### 18.2.1 ECCP PIN CONFIGURATION

In Capture mode, the appropriate ECCPx pin should be configured as an input by setting the corresponding TRIS direction bit.

Additionally, the ECCPx input function needs to be assigned to an I/O pin through the Peripheral Pin Select module. For details on setting up the remappable pins, see Section 10.7 "Peripheral Pin Select (PPS)".

| Note: | If the ECCPx pin is configured as an out-    |

|-------|----------------------------------------------|

|       | put, a write to the port can cause a capture |

|       | condition.                                   |

#### 18.2.2 TIMER1/TIMER3 MODE SELECTION

The timers that are to be used with the capture feature (Timer1 and/or Timer3) must be running in Timer mode or Synchronized Counter mode. In Asynchronous Counter mode, the capture operation may not work. The timer to be used with each ECCP module is selected in the TCLKCON register (Register 13-3).

#### 18.2.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCPxIE interrupt enable bit clear to avoid false interrupts. The interrupt flag bit, CCPxIF, should also be cleared following any such change in operating mode.

# PIC18F46J11 FAMILY

| R/W-0                        | R/W-0                                                | R/W-0                                            | R/W-0         | R/W-0             | R/W-0            | R-1             | R/W-0 |  |  |

|------------------------------|------------------------------------------------------|--------------------------------------------------|---------------|-------------------|------------------|-----------------|-------|--|--|

| CSRC                         | TX9                                                  | TXEN <sup>(1)</sup>                              | SYNC          | SENDB             | BRGH             | TRMT            | TX9D  |  |  |

| oit 7                        |                                                      |                                                  |               |                   | 1                | 1               | bit   |  |  |

|                              |                                                      |                                                  |               |                   |                  |                 |       |  |  |

| L <b>egend:</b><br>R = Reada | ble bit                                              | W = Writable                                     | hit           | II = I Inimplem   | nented bit, read | l as 'N'        |       |  |  |

| -n = Value                   |                                                      | '1' = Bit is set                                 |               | '0' = Bit is clea |                  | x = Bit is unkr | NOWD  |  |  |

|                              |                                                      | 1 Dit lo oot                                     |               |                   |                  |                 |       |  |  |

| bit 7                        | CSRC: Clock                                          | Source Select                                    | bit           |                   |                  |                 |       |  |  |

|                              | <u>Asynchronous</u><br>Don't care.                   | <u>s mode:</u>                                   |               |                   |                  |                 |       |  |  |

|                              |                                                      | <u>mode:</u><br>ode (clock gen<br>de (clock from |               |                   |                  |                 |       |  |  |

| bit 6                        | 1 = Selects 9-                                       | ansmit Enable I<br>-bit transmissio              | n             |                   |                  |                 |       |  |  |

| bit 5                        |                                                      | -bit transmissic<br>mit Enable bit <sup>(1</sup> |               |                   |                  |                 |       |  |  |

|                              | 1 = Transmit<br>0 = Transmit                         |                                                  | the TXx/CKx   | pin is configure  | d as an output   |                 |       |  |  |

| bit 4                        | SYNC: EUSA                                           | SYNC: EUSART Mode Select bit                     |               |                   |                  |                 |       |  |  |

|                              | 1 = Synchron<br>0 = Asynchro                         |                                                  |               |                   |                  |                 |       |  |  |

| bit 3                        | SENDB: Sen                                           | d Break Chara                                    | cter bit      |                   |                  |                 |       |  |  |

|                              |                                                      |                                                  |               | n (cleared by ha  | rdware upon co   | ompletion)      |       |  |  |

|                              | <u>Synchronous</u><br>Don't care.                    |                                                  | ·             |                   |                  |                 |       |  |  |

| bit 2                        | BRGH: High                                           | Baud Rate Sel                                    | ect bit       |                   |                  |                 |       |  |  |

|                              | <u>Asynchronous</u><br>1 = High spee<br>0 = Low spee | ed                                               |               |                   |                  |                 |       |  |  |

|                              | Synchronous<br>Unused in this                        | mode:                                            |               |                   |                  |                 |       |  |  |

| bit 1                        | TRMT: Transı                                         | mit Shift Regist                                 | er Status bit |                   |                  |                 |       |  |  |

|                              | 1 = TSR emp<br>0 = TSR full                          | ty                                               |               |                   |                  |                 |       |  |  |

| bit 0                        | TX9D: 9 <sup>th</sup> bit                            | of Transmit Da                                   | ta            |                   |                  |                 |       |  |  |

|                              |                                                      |                                                  |               |                   |                  |                 |       |  |  |

|             | SYNC = 0, BRGH = 0, BRG16 = 0 |            |                             |                       |                   |                             |                       |                  |                             |                       |            |                             |

|-------------|-------------------------------|------------|-----------------------------|-----------------------|-------------------|-----------------------------|-----------------------|------------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD        | Fosc = 40.000 MHz             |            | Fosc = 20.000 MHz           |                       | Fosc = 10.000 MHz |                             |                       | Fosc = 8.000 MHz |                             |                       |            |                             |

| RATE<br>(K) | Actual<br>Rate<br>(K)         | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error        | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error       | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3         | _                             |            |                             |                       |                   |                             |                       |                  | _                           | _                     | _          | _                           |

| 1.2         | —                             | —          | —                           | 1.221                 | 1.73              | 255                         | 1.202                 | 0.16             | 129                         | 1.201                 | -0.16      | 103                         |

| 2.4         | 2.441                         | 1.73       | 255                         | 2.404                 | 0.16              | 129                         | 2.404                 | 0.16             | 64                          | 2.403                 | -0.16      | 51                          |

| 9.6         | 9.615                         | 0.16       | 64                          | 9.766                 | 1.73              | 31                          | 9.766                 | 1.73             | 15                          | 9.615                 | -0.16      | 12                          |

| 19.2        | 19.531                        | 1.73       | 31                          | 19.531                | 1.73              | 15                          | 19.531                | 1.73             | 7                           | _                     | _          | _                           |

| 57.6        | 56.818                        | -1.36      | 10                          | 62.500                | 8.51              | 4                           | 52.083                | -9.58            | 2                           | —                     | _          | _                           |

| 115.2       | 125.000                       | 8.51       | 4                           | 104.167               | -9.58             | 2                           | 78.125                | -32.18           | 1                           | —                     | _          | _                           |

#### TABLE 20-3: BAUD RATES FOR ASYNCHRONOUS MODES

|              | SYNC = 0, BRGH = 0, BRG16 = 0 |            |                             |                       |            |                             |                       |            |                             |  |

|--------------|-------------------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|--|

| BAUD<br>RATE | Fosc = 4.000 MHz              |            |                             | Fosc = 2.000 MHz      |            |                             | Fosc = 1.000 MHz      |            |                             |  |

| (K)          | Actual<br>Rate<br>(K)         | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |  |

| 0.3          | 0.300                         | 0.16       | 207                         | 0.300                 | -0.16      | 103                         | 0.300                 | -0.16      | 51                          |  |

| 1.2          | 1.202                         | 0.16       | 51                          | 1.201                 | -0.16      | 25                          | 1.201                 | -0.16      | 12                          |  |

| 2.4          | 2.404                         | 0.16       | 25                          | 2.403                 | -0.16      | 12                          | _                     | _          | _                           |  |

| 9.6          | 8.929                         | -6.99      | 6                           | _                     | _          | _                           | _                     | _          | _                           |  |

| 19.2         | 20.833                        | 8.51       | 2                           | —                     | _          | _                           | —                     | _          | _                           |  |

| 57.6         | 62.500                        | 8.51       | 0                           | —                     | _          | _                           | —                     | _          | _                           |  |

| 115.2        | 62.500                        | -45.75     | 0                           | _                     | _          | —                           | _                     | _          | —                           |  |

|              | SYNC = 0, BRGH = 1, BRG16 = 0 |            |                             |                       |                   |                             |                       |                  |                             |                       |            |                             |

|--------------|-------------------------------|------------|-----------------------------|-----------------------|-------------------|-----------------------------|-----------------------|------------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD<br>RATE | Fosc = 40.000 MHz             |            | Fosc = 20.000 MHz           |                       | Fosc = 10.000 MHz |                             |                       | Fosc = 8.000 MHz |                             |                       |            |                             |

| (K)          | Actual<br>Rate<br>(K)         | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error        | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error       | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3          | —                             | _          | _                           | —                     | _                 | _                           | _                     | _                | _                           | _                     | _          | _                           |

| 1.2          | —                             | —          | —                           | —                     | —                 | —                           | —                     | —                | —                           | —                     | —          | —                           |

| 2.4          | —                             | _          | _                           | —                     | _                 | _                           | 2.441                 | 1.73             | 255                         | 2.403                 | -0.16      | 207                         |

| 9.6          | 9.766                         | 1.73       | 255                         | 9.615                 | 0.16              | 129                         | 9.615                 | 0.16             | 64                          | 9615.                 | -0.16      | 51                          |

| 19.2         | 19.231                        | 0.16       | 129                         | 19.231                | 0.16              | 64                          | 19.531                | 1.73             | 31                          | 19.230                | -0.16      | 25                          |

| 57.6         | 58.140                        | 0.94       | 42                          | 56.818                | -1.36             | 21                          | 56.818                | -1.36            | 10                          | 55.555                | 3.55       | 8                           |

| 115.2        | 113.636                       | -1.36      | 21                          | 113.636               | -1.36             | 10                          | 125.000               | 8.51             | 4                           | —                     | _          | _                           |

|              | SYNC = 0, BRGH = 1, BRG16 = 0 |            |                             |                       |            |     |                       |            |                             |  |

|--------------|-------------------------------|------------|-----------------------------|-----------------------|------------|-----|-----------------------|------------|-----------------------------|--|

| BAUD<br>RATE | Fosc = 4.000 MHz              |            |                             | Fosc = 2.000 MHz      |            |     | Fosc = 1.000 MHz      |            |                             |  |

| (K)          | Actual<br>Rate<br>(K)         | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | Rate Frror |     | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |  |

| 0.3          |                               |            | _                           |                       |            | _   | 0.300                 | -0.16      | 207                         |  |

| 1.2          | 1.202                         | 0.16       | 207                         | 1.201                 | -0.16      | 103 | 1.201                 | -0.16      | 51                          |  |

| 2.4          | 2.404                         | 0.16       | 103                         | 2.403                 | -0.16      | 51  | 2.403                 | -0.16      | 25                          |  |

| 9.6          | 9.615                         | 0.16       | 25                          | 9.615                 | -0.16      | 12  | _                     | _          | _                           |  |

| 19.2         | 19.231                        | 0.16       | 12                          | _                     | _          | _   | _                     | _          | _                           |  |

| 57.6         | 62.500                        | 8.51       | 3                           | _                     | _          | _   | _                     | _          | _                           |  |

| 115.2        | 125.000                       | 8.51       | 1                           | _                     | _          | —   | _                     | _          | _                           |  |

© 2011 Microchip Technology Inc.

- 10. If any error occurred, clear the CREN bit.

- 11. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and interrupt the CPU.

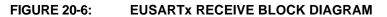

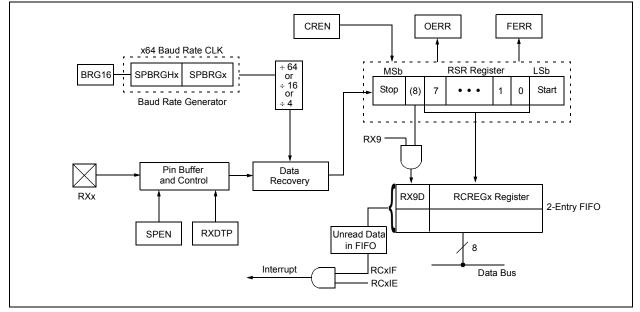

#### FIGURE 20-7: ASYNCHRONOUS RECEPTION

# 22.0 COMPARATOR MODULE

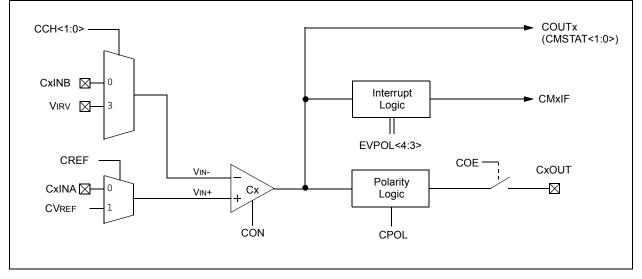

The analog comparator module contains two comparators that can be independently configured in a variety of ways. The inputs can be selected from the analog inputs and two internal voltage references. The digital outputs are available at the pin level and can also be read through the control register. Multiple output and interrupt event generation is also available. Figure 22-1 provides a generic single comparator from the module.

Key features of the module are:

- Independent comparator control

- Programmable input configuration

- Output to both pin and register levels

- · Programmable output polarity

- Independent interrupt generation for each comparator with configurable interrupt-on-change

# 22.1 Registers

The CMxCON registers (Register 22-1) select the input and output configuration for each comparator, as well as the settings for interrupt generation.

The CMSTAT register (Register 22-2) provides the output results of the comparators. The bits in this register are read-only.

## FIGURE 22-1: COMPARATOR SIMPLIFIED BLOCK DIAGRAM

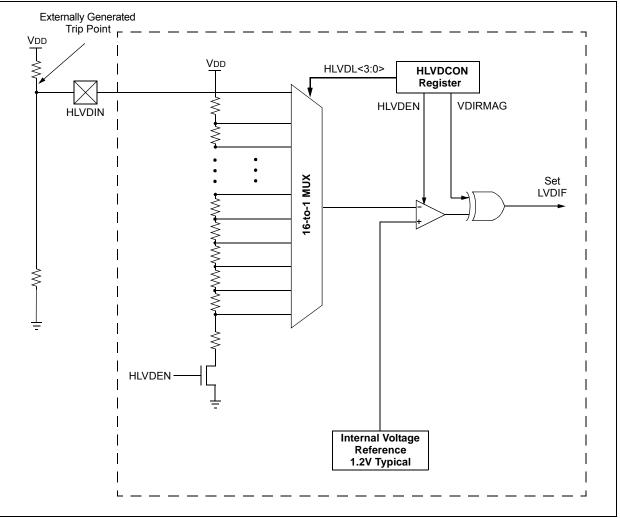

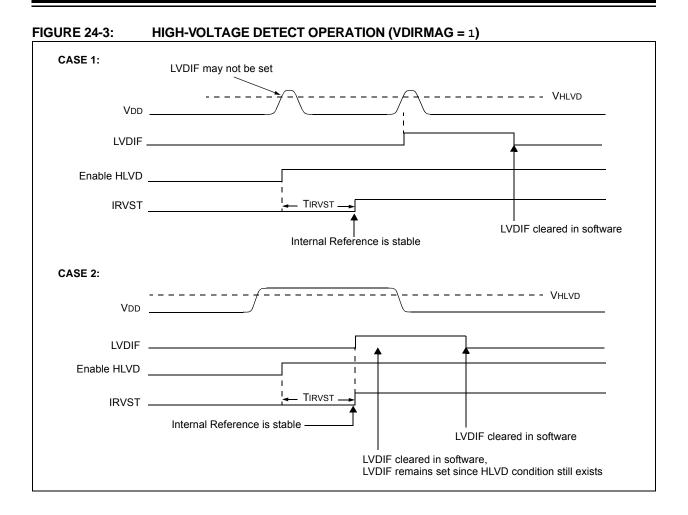

# 24.1 Operation

When the HLVD module is enabled, a comparator uses an internally generated reference voltage as the set point. The set point is compared with the trip point, where each node in the resistor divider represents a trip point voltage. The "trip point" voltage is the voltage level at which the device detects a high or low-voltage event, depending on the configuration of the module.

When the supply voltage is equal to the trip point, the voltage tapped off of the resistor array is equal to the internal reference voltage generated by the voltage reference module. The comparator then generates an interrupt signal by setting the LVDIF bit.

The trip point voltage is software programmable to any one of 8 values. The trip point is selected by programming the HLVDL<3:0> bits (HLVDCON<3:0>).

Additionally, the HLVD module allows the user to supply the trip voltage to the module from an external source. This mode is enabled when bits, HLVDL<3:0>, are set to '1111'. In this state, the comparator input is multiplexed from the external input pin, HLVDIN. This gives users flexibility because it allows them to configure the HLVD interrupt to occur at any voltage in the valid operating range.

#### FIGURE 24-1: HLVD MODULE BLOCK DIAGRAM (WITH EXTERNAL INPUT)

# 24.5 Applications

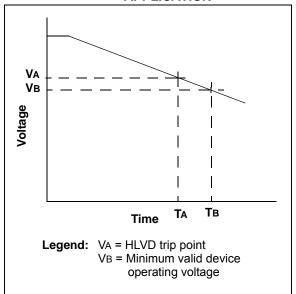

In many applications, it is desirable to have the ability to detect a drop below, or rise above, a particular threshold. For general battery applications, Figure 24-4 provides a possible voltage curve.

Over time, the device voltage decreases. When the device voltage reaches voltage, VA, the HLVD logic generates an interrupt at time, TA. The interrupt could cause the execution of an ISR, which would allow the application to perform "housekeeping tasks" and perform a controlled shutdown before the device voltage exits the valid operating range at TB.

The HLVD, thus, would give the application a time window, represented by the difference between TA and TB, to safely exit.

TYPICAL HIGH/ LOW-VOLTAGE DETECT APPLICATION

# EXAMPLE 25-4: ROUTINE FOR CAPACITIVE TOUCH SWITCH

```

#include <pl8cxxx.h>

#define COUNT 500

//@ 8MHz = 125uS.

#define DELAY for(i=0;i<COUNT;i++)</pre>

#define OPENSW 1000

//Un-pressed switch value

#define TRIP 300

//Difference between pressed

//and un-pressed switch

#define HYST 65

//amount to change

//from pressed to un-pressed

#define PRESSED 1

#define UNPRESSED 0

int main(void)

{

unsigned int Vread;

//storage for reading

unsigned int switchState;

int i;

//assume CTMU and A/D have been setup correctly

//see Example 25-1 for CTMU & A/D setup

setup();

CTMUCONHbits.CTMUEN = 1;

// Enable the CTMU

CTMUCONLbits.EDG1STAT = 0;

// Set Edge status bits to zero

CTMUCONLbits.EDG2STAT = 0;

//drain charge on the circuit

CTMUCONHbits.IDISSEN = 1;

DELAY;

//wait 125us

CTMUCONHbits.IDISSEN = 0;

//end drain of circuit

CTMUCONLbits.EDG1STAT = 1;

//Begin charging the circuit

//using CTMU current source

//wait for 125us

DELAY;

CTMUCONLbits.EDG1STAT = 0;

//Stop charging circuit

PIR1bits.ADIF = 0;

//make sure A/D Int not set

ADCON0bits.GO=1;

//and begin A/D conv.

while(!PIR1bits.ADIF);

//Wait for A/D convert complete

Vread = ADRES;

//Get the value from the A/D

if(Vread < OPENSW - TRIP)

{

switchState = PRESSED;

}

else if(Vread > OPENSW - TRIP + HYST)

{

switchState = UNPRESSED;

}

}

```

# PIC18F46J11 FAMILY

| TBLWT                                  | Table Wri                                                                                                                                                                                                                                                                                                                                                                       | te                                                                            |                                                                              |                                                               |  |  |  |

|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------------|---------------------------------------------------------------|--|--|--|

| Syntax:                                | TBLWT ( '                                                                                                                                                                                                                                                                                                                                                                       | *; *+; *-; +*                                                                 | r)                                                                           |                                                               |  |  |  |

| Operands:                              | None                                                                                                                                                                                                                                                                                                                                                                            |                                                                               |                                                                              |                                                               |  |  |  |

| Operation:                             | if TBLWT*,<br>(TABLAT) $\rightarrow$ Holding Register,<br>TBLPTR – No Change;<br>if TBLWT*+,<br>(TABLAT) $\rightarrow$ Holding Register,<br>(TBLPTR) + 1 $\rightarrow$ TBLPTR;<br>if TBLWT*-,<br>(TABLAT) $\rightarrow$ Holding Register,<br>(TBLPTR) – 1 $\rightarrow$ TBLPTR;<br>if TBLWT+*,<br>(TBLPTR) + 1 $\rightarrow$ TBLPTR,<br>(TABLAT) $\rightarrow$ Holding Register |                                                                               |                                                                              |                                                               |  |  |  |

| Status Affected:                       | None                                                                                                                                                                                                                                                                                                                                                                            | ,                                                                             | 5                                                                            |                                                               |  |  |  |

| Encoding:                              | 0000                                                                                                                                                                                                                                                                                                                                                                            | 0000                                                                          | 0000                                                                         | 11nn<br>nn=0 *<br>=1 *+<br>=2 *-<br>=3 +*                     |  |  |  |

| Description:                           | This instruction uses the 3 LSBs of<br>TBLPTR to determine which of the<br>8 holding registers the TABLAT is written<br>to. The holding registers are used to<br>program the contents of Program Memory<br>(P.M.). (Refer to <b>Section 6.0 "Memory</b><br><b>Organization"</b> for additional details on<br>programming Flash memory.)                                         |                                                                               |                                                                              |                                                               |  |  |  |

|                                        | The TBLP<br>each byte<br>TBLPTR I<br>The LSb c<br>byte of the<br>access.                                                                                                                                                                                                                                                                                                        | TR (a 21-<br>in the pro<br>has a 2-Mt<br>of the TBL<br>e program<br>0> = 0: L | bit pointer<br>gram men<br>byte addre<br>PTR selec<br>memory l<br>east Signi | nory.<br>ess range.<br>ets which<br>ocation to<br>ficant Byte |  |  |  |

|                                        |                                                                                                                                                                                                                                                                                                                                                                                 |                                                                               | of Program Memory<br>Word                                                    |                                                               |  |  |  |

|                                        | TBLPTR<                                                                                                                                                                                                                                                                                                                                                                         |                                                                               |                                                                              | icant Byte of<br>emory Word                                   |  |  |  |

|                                        | The TBLWT instruction can modify the<br>value of TBLPTR as follows:<br>• no change<br>• post-increment<br>• post-decrement                                                                                                                                                                                                                                                      |                                                                               |                                                                              |                                                               |  |  |  |

|                                        | <ul> <li>pre-incr</li> </ul>                                                                                                                                                                                                                                                                                                                                                    | rement                                                                        |                                                                              |                                                               |  |  |  |

| Words:<br>Cycles:<br>Q Cycle Activity: | 1<br>2                                                                                                                                                                                                                                                                                                                                                                          |                                                                               |                                                                              |                                                               |  |  |  |

| ,,,                                    | Q1                                                                                                                                                                                                                                                                                                                                                                              | Q2                                                                            | Q3                                                                           | Q4                                                            |  |  |  |

|                                        | Decode                                                                                                                                                                                                                                                                                                                                                                          | No                                                                            | No<br>operation                                                              | No<br>operation                                               |  |  |  |

|                                        | No                                                                                                                                                                                                                                                                                                                                                                              | No                                                                            | No                                                                           | No                                                            |  |  |  |

|                                        | _                                                                                                                                                                                                                                                                                                                                                                               | operation<br>(Read<br>TABLAT)                                                 | -                                                                            | operation<br>(Write to<br>Holding<br>Register)                |  |  |  |

#### TBLWT Table Write (Continued)

|                                                   | ••••   |                |

|---------------------------------------------------|--------|----------------|

| Example 1: TBLWT *+                               |        |                |

| Before Instruction                                |        |                |

| TABLAT<br>TBLPTR<br>HOLDING REGISTER              | =<br>= | 55h<br>00A356h |

| (00A356h)                                         | =      | FFh            |

| After Instructions (table write                   | e comp | letion)        |

| TABLAT<br>TBLPTR<br>HOLDING REGISTER              | =      | 55h<br>00A357h |

| (00A356h)                                         | =      | 55h            |

| Example 2: TBLWT +*                               |        |                |

| Before Instruction                                |        |                |

| TABLAT<br>TBLPTR                                  | =      | 34h<br>01389Ah |

| HOLDING REGISTER<br>(01389Ah)<br>HOLDING REGISTER | =      | FFh            |

| (01389Bh)                                         | =      | FFh            |

| After Instruction (table write                    | comple | etion)         |

| TABLAT<br>TBLPTR                                  | =<br>= | 34h<br>01389Bh |

| HOLDING REGISTER<br>(01389Ah)<br>HOLDING REGISTER | =      | FFh            |

| (01389Bh)                                         | =      | 34h            |

#### 27.2.2 EXTENDED INSTRUCTION SET

| ADD                 | FSR            | Add Liter        | Add Literal to FSR                    |        |          |  |  |  |  |

|---------------------|----------------|------------------|---------------------------------------|--------|----------|--|--|--|--|

| Syntax: ADDFSR f, k |                |                  |                                       |        |          |  |  |  |  |

| Oper                | ands:          | $0 \le k \le 63$ | $0 \le k \le 63$                      |        |          |  |  |  |  |

|                     |                | f ∈ [ 0, 1,      | 2]                                    |        |          |  |  |  |  |

| Oper                | ation:         | FSR(f) + I       | $s \rightarrow FSR($                  | f)     |          |  |  |  |  |

| Statu               | s Affected:    | None             | None                                  |        |          |  |  |  |  |

| Enco                | oding:         | 1110             | 1000 ffkk                             |        | kkkk     |  |  |  |  |

| Desc                | ription:       | The 6-bit        | iteral 'k' i                          | s adde | d to the |  |  |  |  |

|                     |                | contents of      | contents of the FSR specified by 'f'. |        |          |  |  |  |  |

| Word                | ls:            | 1                |                                       |        |          |  |  |  |  |

| Cycle               | es:            | 1                | 1                                     |        |          |  |  |  |  |

| QC                  | ycle Activity: |                  |                                       |        |          |  |  |  |  |

|                     | Q1             | Q2               | Q3                                    |        | Q4       |  |  |  |  |

|                     | Decode         | Read             | Process W                             |        | Write to |  |  |  |  |

|                     |                | literal 'k'      | Data                                  |        | FSR      |  |  |  |  |

|                     |                |                  | 2 410                                 |        |          |  |  |  |  |

ADDFSR 2, 0x23

03FFh

0422h

Example:

Before Instruction FSR2

After Instruction

FSR2

=

=

| ADDULNK Add Literal to FSR2 and Return |                                                                                                                   |      |      |      |  |  |  |

|----------------------------------------|-------------------------------------------------------------------------------------------------------------------|------|------|------|--|--|--|

| Syntax:                                | ADDULN                                                                                                            | Kk   |      |      |  |  |  |

| Operands:                              | $0 \le k \le 63$                                                                                                  |      |      |      |  |  |  |

| Operation:                             | $FSR2 + k \rightarrow FSR2$ ,                                                                                     |      |      |      |  |  |  |

|                                        | $(TOS) \rightarrow PC$                                                                                            |      |      |      |  |  |  |

| Status Affected:                       | None                                                                                                              |      | -    |      |  |  |  |

| Encoding:                              | 1110                                                                                                              | 1000 | 11kk | kkkk |  |  |  |

| Description:                           | The 6-bit literal 'k' is added to the contents of FSR2. A RETURN is then executed by loading the PC with the TOS. |      |      |      |  |  |  |

|                                        | The instruction takes two cycles to<br>execute; a NOP is performed during<br>the second cycle.                    |      |      |      |  |  |  |

|                                        | ht of as a<br>R instructio<br>'11'); it op                                                                        | on,  |      |      |  |  |  |

| Words:                                 | 1                                                                                                                 |      |      |      |  |  |  |

| Cycles:                                | 2                                                                                                                 |      |      |      |  |  |  |

Q Cycle Activity:

| Q1        | Q2          | Q3        | Q4        |

|-----------|-------------|-----------|-----------|

| Decode    | Read        | Process   | Write to  |

|           | literal 'k' | Data      | FSR       |

| No        | No          | No        | No        |

| Operation | Operation   | Operation | Operation |

| Example:         | AD   | DULNK 0x23 |  |

|------------------|------|------------|--|

| Before Instruc   | tion |            |  |

| FSR2             | =    | 03FFh      |  |

| PC               | =    | 0100h      |  |

| After Instructio | n    |            |  |

=

=

0422h

(TOS)

FSR2

PC

Note: All PIC18 instructions may take an optional label argument preceding the instruction mnemonic for use in symbolic addressing. If a label is used, the instruction format then becomes: {label} instruction argument(s).

| Param<br>No. | Symbol        | Characteristic                                    | Min        | Тур                       | Мах        | Units    | Conditions                                                  |

|--------------|---------------|---------------------------------------------------|------------|---------------------------|------------|----------|-------------------------------------------------------------|

| A01          | NR            | Resolution                                        | —          |                           | 10         | bit      | $\Delta VREF \ge 3.0V$                                      |

| A03          | EIL           | Integral Linearity Error                          | —          | _                         | <±1        | LSb      | $\Delta VREF \ge 3.0V$                                      |

| A04          | Edl           | Differential Linearity Error                      | —          | _                         | <±1        | LSb      | $\Delta VREF \ge 3.0V$                                      |

| A06          | EOFF          | Offset Error                                      | —          | _                         | <±3        | LSb      | $\Delta VREF \ge 3.0V$                                      |

| A07          | Egn           | Gain Error                                        | —          | _                         | <±3.5      | LSb      | $\Delta VREF \ge 3.0V$                                      |

| A10          |               | Monotonicity                                      | Gi         | Guaranteed <sup>(1)</sup> |            | -        | $VSS \leq VAIN \leq VREF$                                   |

| A20          | $\Delta VREF$ | Reference Voltage Range<br>(VREFH – VREFL)        | 2.0<br>3   |                           |            | V<br>V   | $\begin{array}{l} VDD < 3.0V \\ VDD \geq 3.0V \end{array}$  |

| A21          | Vrefh         | Reference Voltage High                            | VREFL      | _                         | VDD + 0.3V | V        |                                                             |

| A22          | Vrefl         | Reference Voltage Low                             | Vss – 0.3V | _                         | VREFH      | V        |                                                             |

| A25          | VAIN          | Analog Input Voltage                              | VREFL      | _                         | VREFH      | V        |                                                             |

| A30          | ZAIN          | Recommended Impedance of<br>Analog Voltage Source | —          |                           | 2.5        | kΩ       |                                                             |

| A50          | IREF          | VREF Input Current <sup>(2)</sup>                 |            | _                         | 5<br>150   | μΑ<br>μΑ | During VAIN acquisition.<br>During A/D conversion<br>cycle. |

#### TABLE 29-30: A/D CONVERTER CHARACTERISTICS: PIC18F46J11 FAMILY (INDUSTRIAL)

Note 1: The A/D conversion result never decreases with an increase in the input voltage and has no missing codes.

2: VREFH current is from RA3/AN3/VREF+/C1INB pin or VDD, whichever is selected as the VREFH source. VREFL current is from RA2/AN2/VREF-/CVREF/C2INB pin or VSS, whichever is selected as the VREFL source.